Thiết kế khối tăng tốc đồng bộ dữ liệu từ máy thu số trên nền tảng FPGA

Hiện nay, mật độ tích hợp trên các vi mạch số đã đạt đến hàng tỷ transistor

trên một chip đơn, cho phép tạo ra những thiết bị phần cứng chuyên dụng nhằm tăng tốc

cho các bài toán xử lý, phân tích và tìm kiếm dữ liệu lớn. Bài toán xử lý dữ liệu lớn thu

được từ các máy thu số thường gặp các vấn đề như tạp nhiễu và sai lệch pha, dẫn đến

phải phân tích và sắp xếp lại chúng theo trật tự để thuận tiện cho các giai đoạn xử lý tiếp

theo. Công việc này nếu thực hiện trên phần mềm thường kém hiệu quả do tốc độ xử lý

không đáp ứng được yêu cầu. Bài báo đề xuất một thiết kế cho bộ tăng tốc tìm kiếm và xử

lý từ luồng dữ liệu lớn nhận từ các máy thu thông tin số, sử dụng kết hợp kỹ thuật xử lý

song song và phương pháp đường ống. Tiếp đó, tiến hành đánh giá các yếu tố ảnh hưởng

đến tốc độ tìm kiếm và tài nguyên sử dụng để đưa ra giải pháp thiết kế tối ưu. Chúng tôi

đã thực thi thiết kế trên mạch FPGA Kintex 7-XC7K325T áp dụng cho bài toán tìm kiếm

song song dữ liệu có độ dài mẫu 128 bit, sử dụng tối đa 512 khối so sánh ở tần số xung

nhịp 100 MHz và các kiểu điều chế PSK và QAM. Kết quả thực thi trên phần cứng nhanh

gấp khoảng 945 lần so với thực thi trên phần mềm với giá trị băng thông đạt được khoảng

800 Mbps.

Trang 1

Trang 2

Trang 3

Trang 4

Trang 5

Trang 6

Trang 7

Trang 8

Trang 9

Trang 10

Tóm tắt nội dung tài liệu: Thiết kế khối tăng tốc đồng bộ dữ liệu từ máy thu số trên nền tảng FPGA

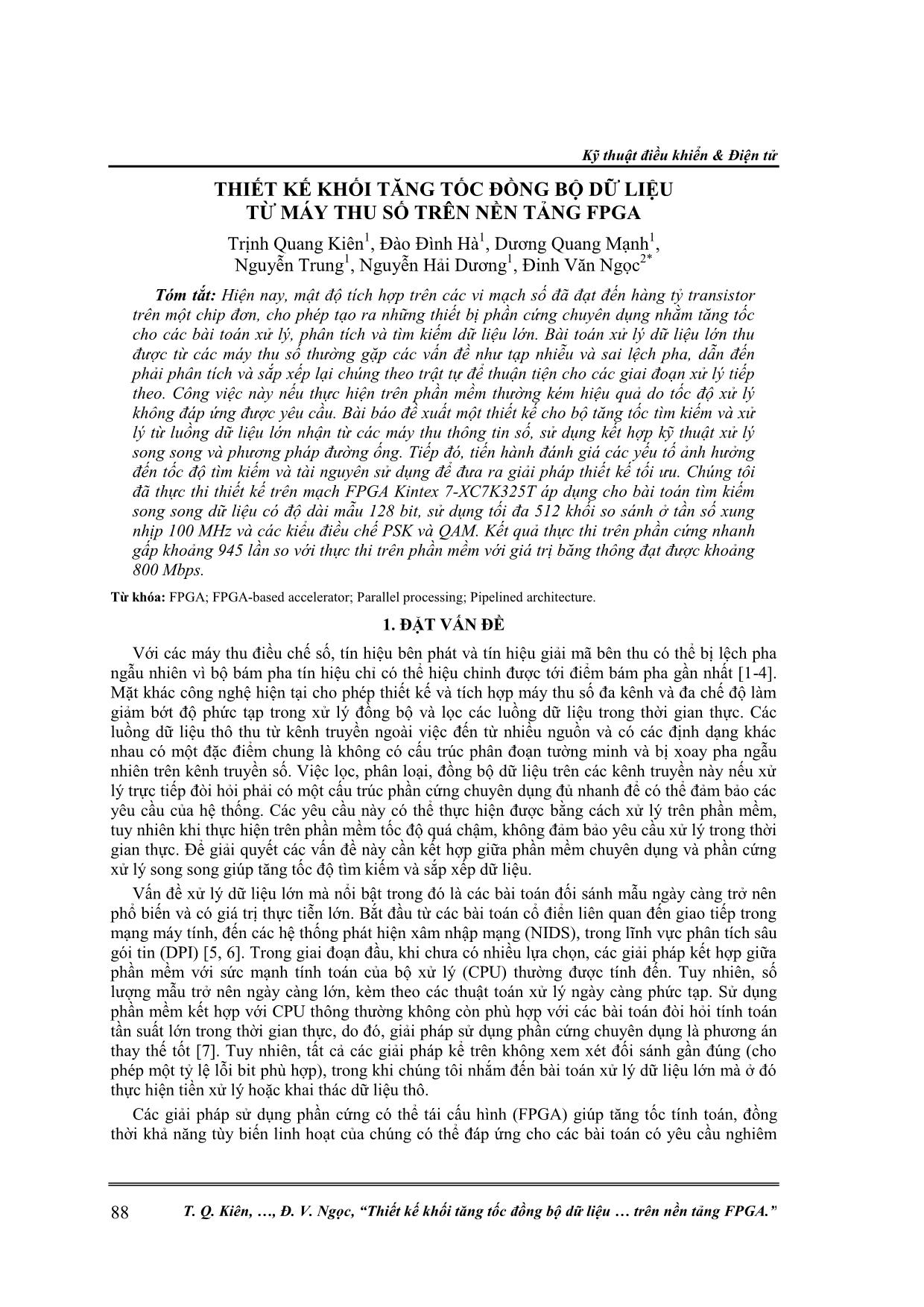

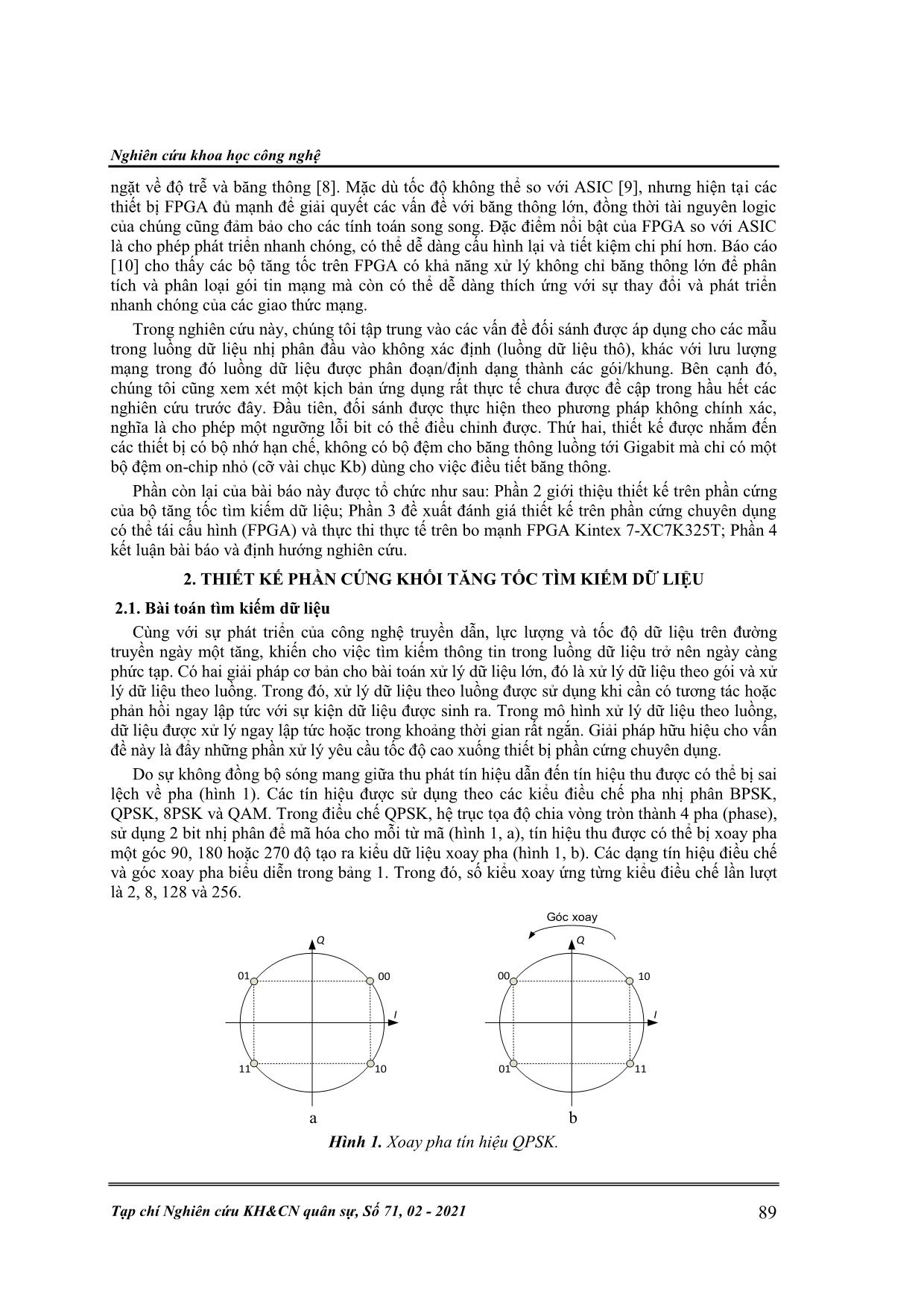

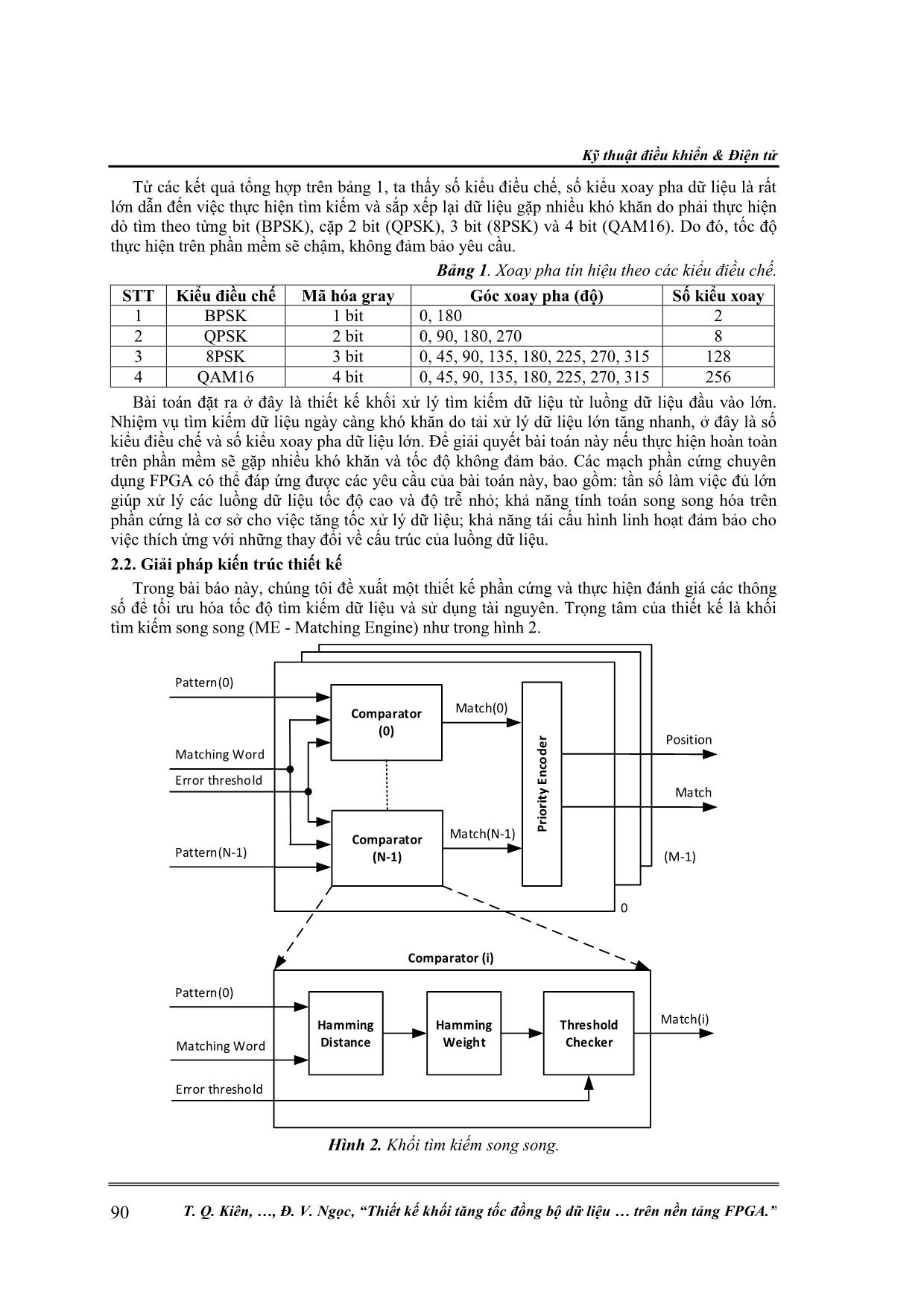

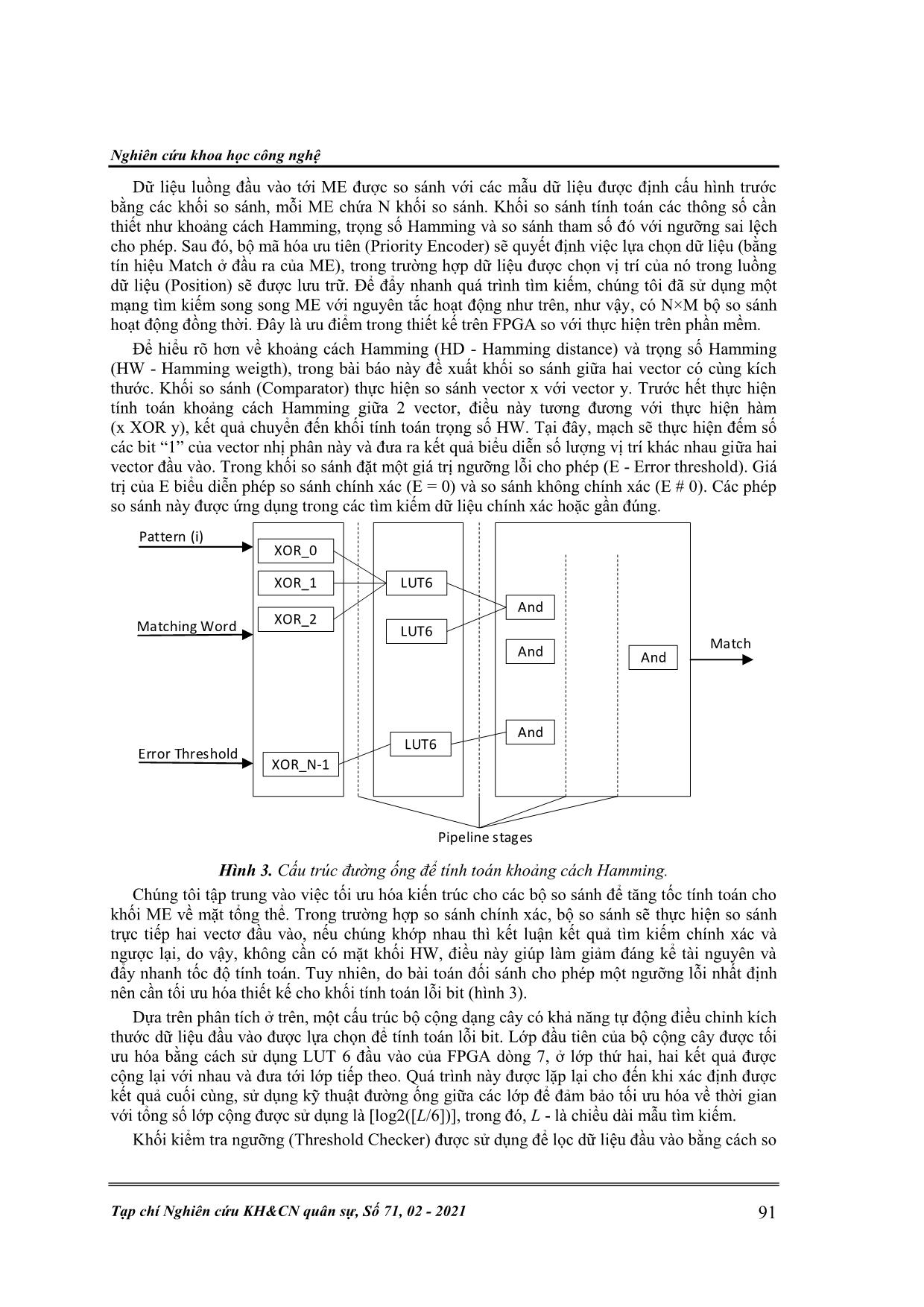

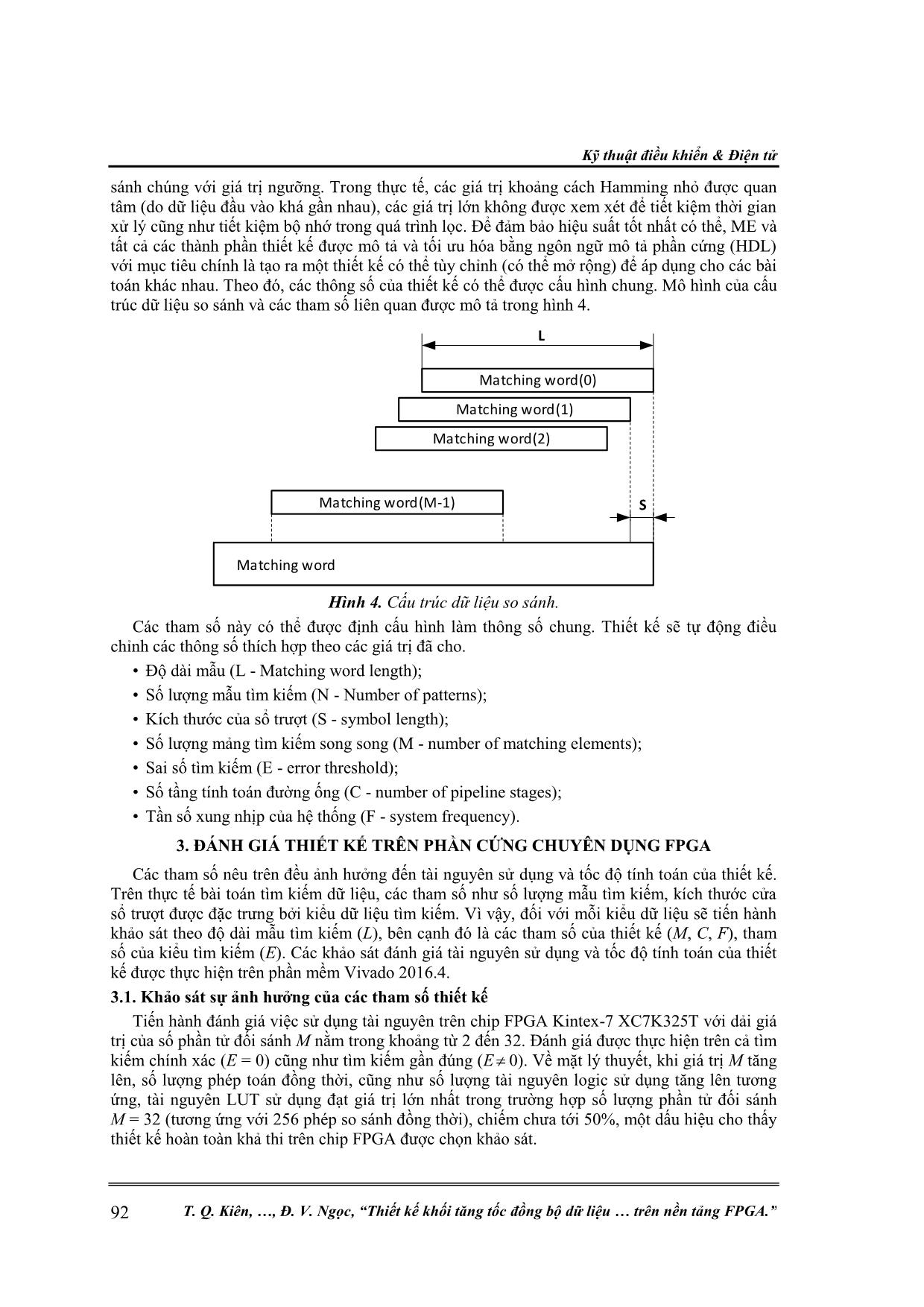

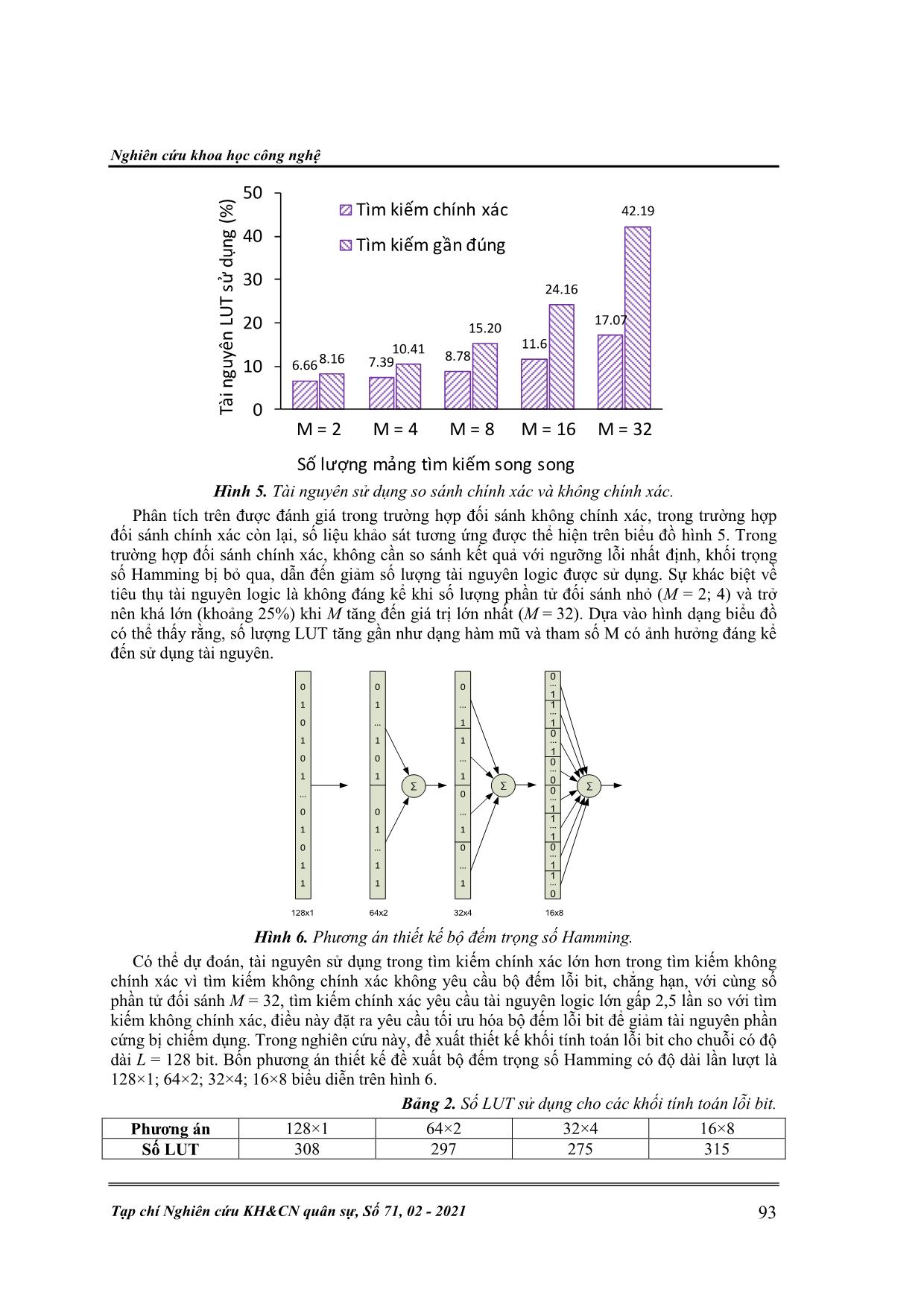

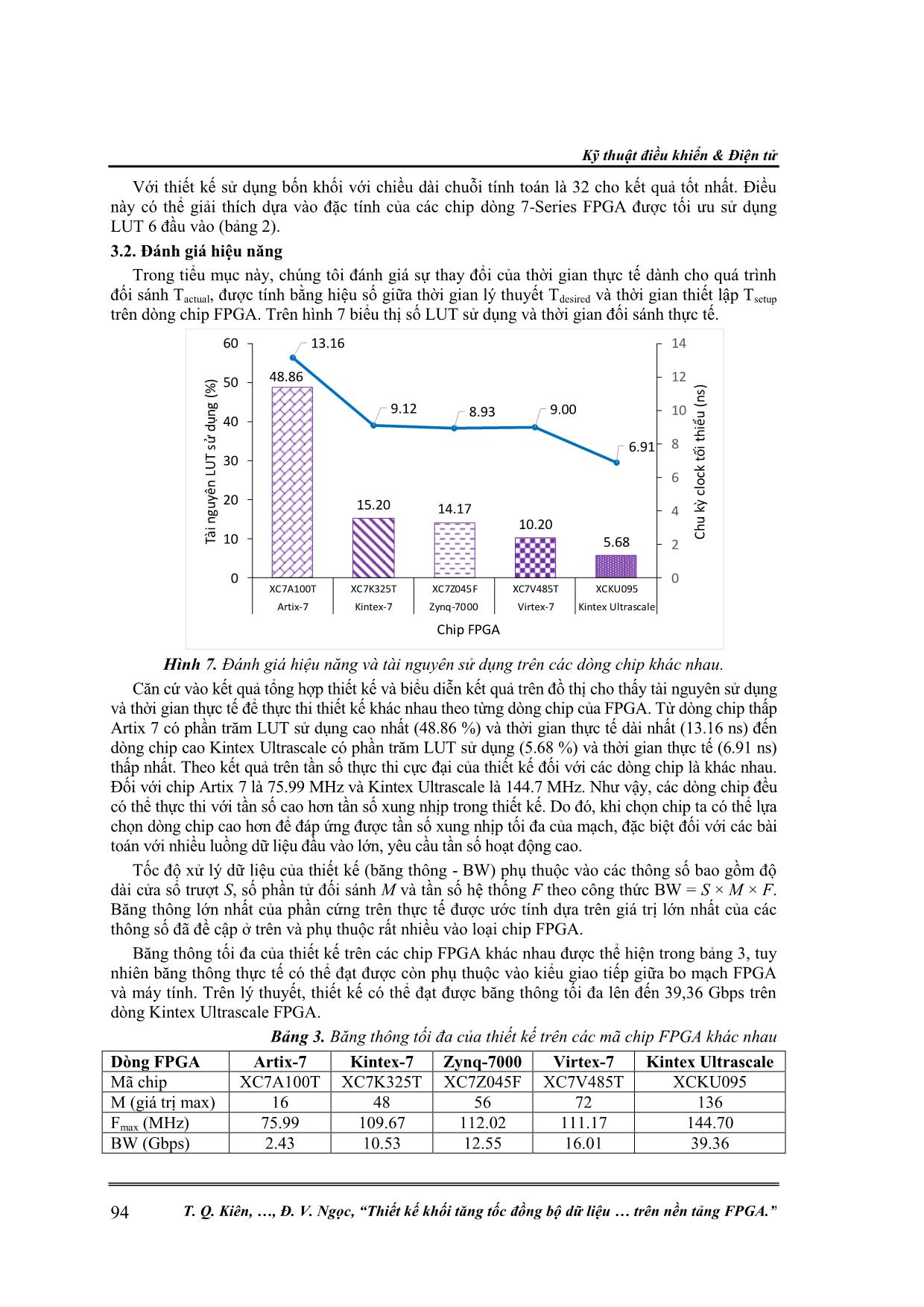

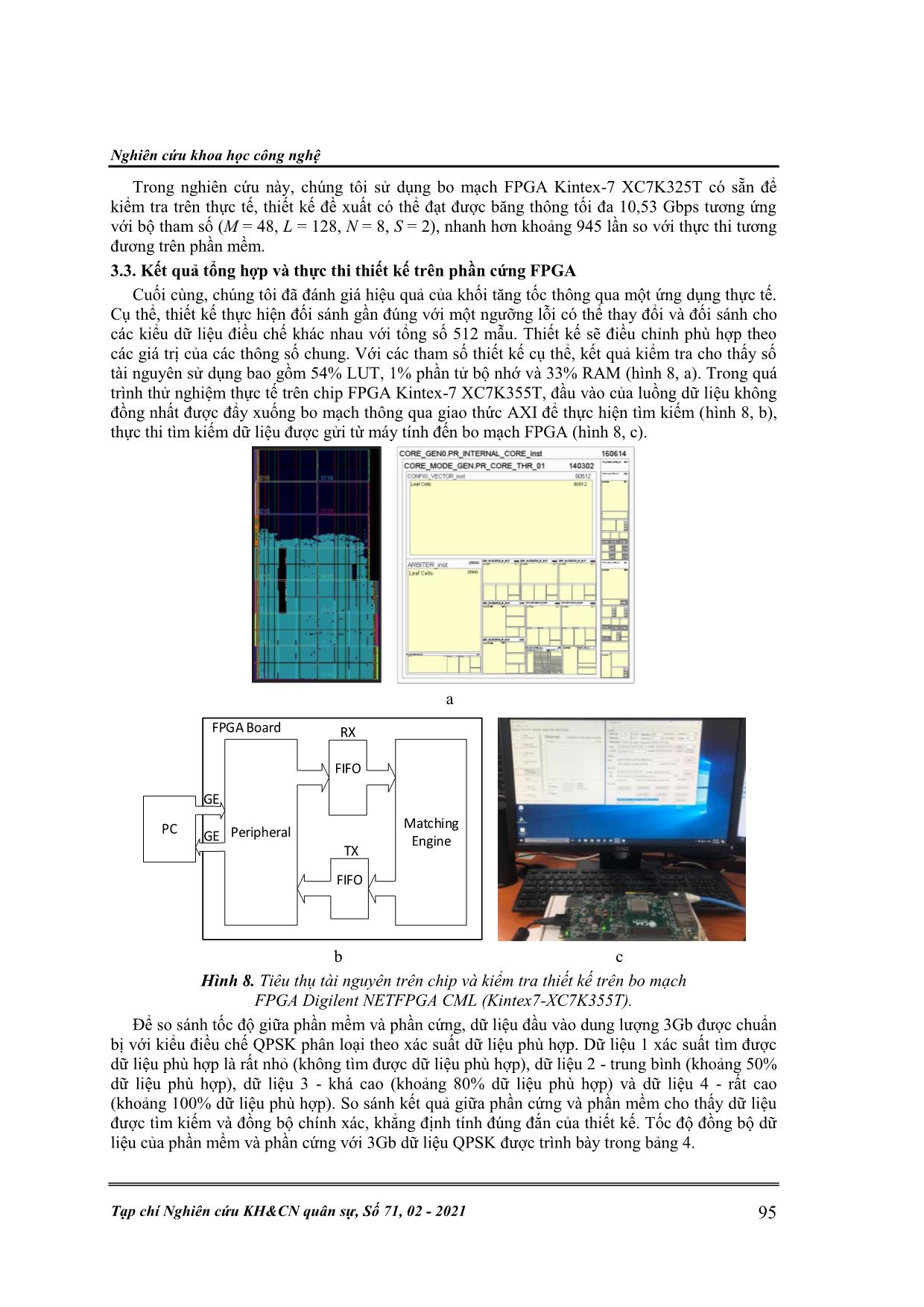

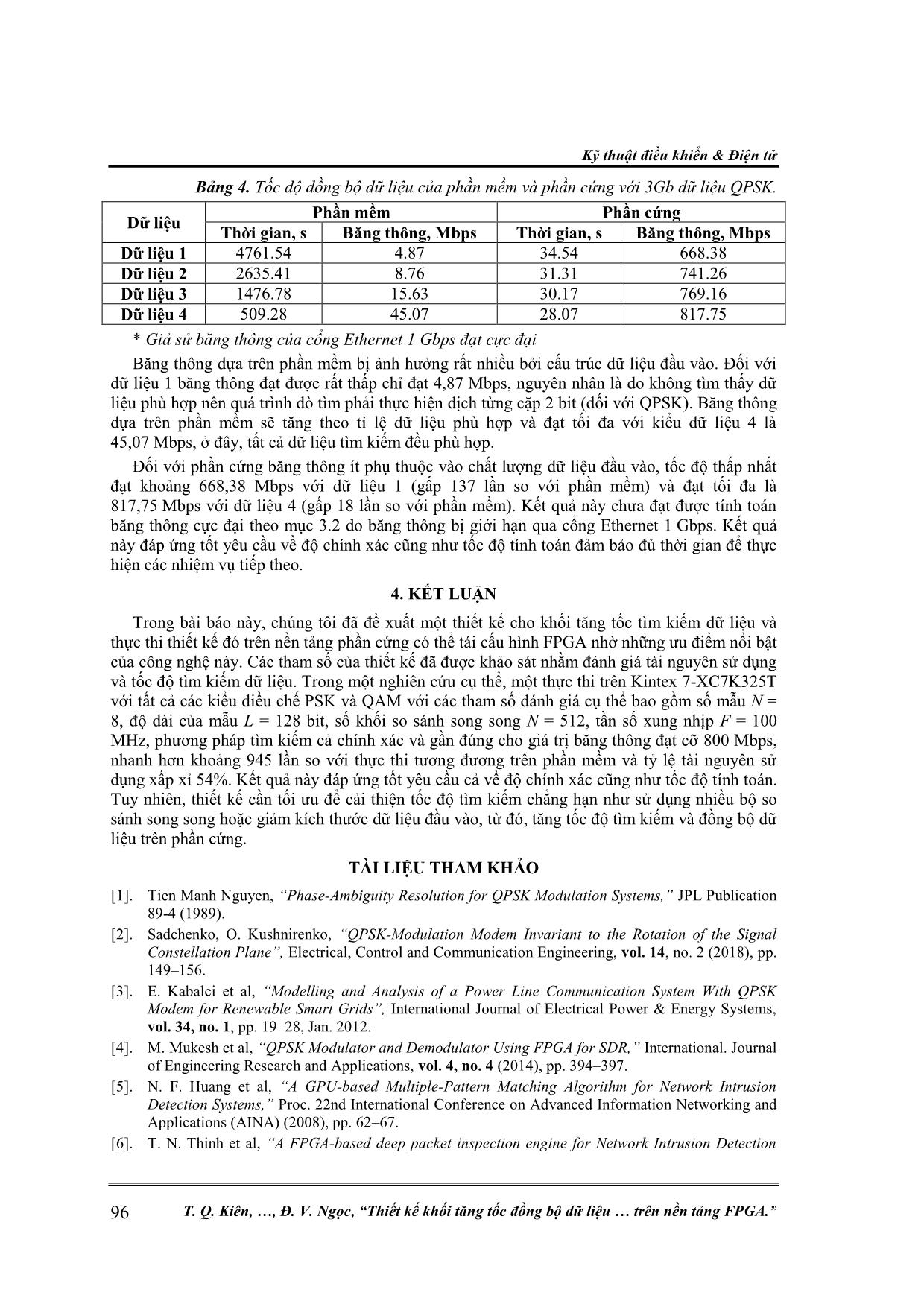

oán đường ống (C - number of pipeline stages); • Tần số xung nhịp của hệ thống (F - system frequency). 3. ĐÁNH GIÁ THIẾT KẾ TRÊN PHẦN CỨNG CHUYÊN DỤNG FPGA Các tham số nêu trên đều ảnh hưởng đến tài nguyên sử dụng và tốc độ tính toán của thiết kế. Trên thực tế bài toán tìm kiếm dữ liệu, các tham số như số lượng mẫu tìm kiếm, kích thước cửa sổ trượt được đặc trưng bởi kiểu dữ liệu tìm kiếm. Vì vậy, đối với mỗi kiểu dữ liệu sẽ tiến hành khảo sát theo độ dài mẫu tìm kiếm (L), bên cạnh đó là các tham số của thiết kế (M, C, F), tham số của kiểu tìm kiếm (E). Các khảo sát đánh giá tài nguyên sử dụng và tốc độ tính toán của thiết kế được thực hiện trên phần mềm Vivado 2016.4. 3.1. Khảo sát sự ảnh hưởng của các tham số thiết kế Tiến hành đánh giá việc sử dụng tài nguyên trên chip FPGA Kintex-7 XC7K325T với dải giá trị của số phần tử đối sánh M nằm trong khoảng từ 2 đến 32. Đánh giá được thực hiện trên cả tìm kiếm chính xác (E = 0) cũng như tìm kiếm gần đúng (E 0). Về mặt lý thuyết, khi giá trị M tăng lên, số lượng phép toán đồng thời, cũng như số lượng tài nguyên logic sử dụng tăng lên tương ứng, tài nguyên LUT sử dụng đạt giá trị lớn nhất trong trường hợp số lượng phần tử đối sánh M = 32 (tương ứng với 256 phép so sánh đồng thời), chiếm chưa tới 50%, một dấu hiệu cho thấy thiết kế hoàn toàn khả thi trên chip FPGA được chọn khảo sát. 92 T. Q. Kiên, , Đ. V. Ngọc, “Thiết kế khối tăng tốc đồng bộ dữ liệu trên nền tảng FPGA.” Nghiên cứu khoa học công nghệ 50 Tìm kiếm chính xác 42.19 40 Tìm kiếm gần đúng 30 24.16 17.07 20 15.20 11.6 10.41 8.78 10 6.668.16 7.39 Tài nguyên LUT sử dụng sử(%) LUTdụng nguyên Tài 0 M = 2 M = 4 M = 8 M = 16 M = 32 Số lượng mảng tìm kiếm song song Hình 5. Tài nguyên sử dụng so sánh chính xác và không chính xác. Phân tích trên được đánh giá trong trường hợp đối sánh không chính xác, trong trường hợp đối sánh chính xác còn lại, số liệu khảo sát tương ứng được thể hiện trên biểu đồ hình 5. Trong trường hợp đối sánh chính xác, không cần so sánh kết quả với ngưỡng lỗi nhất định, khối trọng số Hamming bị bỏ qua, dẫn đến giảm số lượng tài nguyên logic được sử dụng. Sự khác biệt về tiêu thụ tài nguyên logic là không đáng kể khi số lượng phần tử đối sánh nhỏ (M = 2; 4) và trở nên khá lớn (khoảng 25%) khi M tăng đến giá trị lớn nhất (M = 32). Dựa vào hình dạng biểu đồ có thể thấy rằng, số lượng LUT tăng gần như dạng hàm mũ và tham số M có ảnh hưởng đáng kể đến sử dụng tài nguyên. 0 0 0 0 1 1 1 1 0 1 1 0 1 1 1 1 0 0 0 1 1 1 0 0 0 0 0 1 1 1 1 1 1 0 0 0 1 1 1 1 1 1 1 0 128x1 64x2 32x4 16x8 Hình 6. Phương án thiết kế bộ đếm trọng số Hamming. Có thể dự đoán, tài nguyên sử dụng trong tìm kiếm chính xác lớn hơn trong tìm kiếm không chính xác vì tìm kiếm không chính xác không yêu cầu bộ đếm lỗi bit, chẳng hạn, với cùng số phần tử đối sánh M = 32, tìm kiếm chính xác yêu cầu tài nguyên logic lớn gấp 2,5 lần so với tìm kiếm không chính xác, điều này đặt ra yêu cầu tối ưu hóa bộ đếm lỗi bit để giảm tài nguyên phần cứng bị chiếm dụng. Trong nghiên cứu này, đề xuất thiết kế khối tính toán lỗi bit cho chuỗi có độ dài L = 128 bit. Bốn phương án thiết kế đề xuất bộ đếm trọng số Hamming có độ dài lần lượt là 128×1; 64×2; 32×4; 16×8 biểu diễn trên hình 6. Bảng 2. Số LUT sử dụng cho các khối tính toán lỗi bit. Phương án 128×1 64×2 32×4 16×8 Số LUT 308 297 275 315 Tạp chí Nghiên cứu KH&CN quân sự, Số 71, 02 - 2021 93 Kỹ thuật điều khiển & Điện tử Với thiết kế sử dụng bốn khối với chiều dài chuỗi tính toán là 32 cho kết quả tốt nhất. Điều này có thể giải thích dựa vào đặc tính của các chip dòng 7-Series FPGA được tối ưu sử dụng LUT 6 đầu vào (bảng 2). 3.2. Đánh giá hiệu năng Trong tiểu mục này, chúng tôi đánh giá sự thay đổi của thời gian thực tế dành cho quá trình đối sánh Tactual, được tính bằng hiệu số giữa thời gian lý thuyết Tdesired và thời gian thiết lập Tsetup trên dòng chip FPGA. Trên hình 7 biểu thị số LUT sử dụng và thời gian đối sánh thực tế. 60 13.16 14 50 48.86 12 9.12 8.93 9.00 10 40 6.91 8 30 6 20 15.20 14.17 4 10.20 Chu kỳ Chu clockkỳ (ns)thiểu tối Tài nguyên LUT sử dụng sử(%) LUTdụng nguyên Tài 10 5.68 2 0 0 XC7A100T XC7K325T XC7Z045F XC7V485T XCKU095 Artix-7 Kintex-7 Zynq-7000 Virtex-7 Kintex Ultrascale Chip FPGA Hình 7. Đánh giá hiệu năng và tài nguyên sử dụng trên các dòng chip khác nhau. Căn cứ vào kết quả tổng hợp thiết kế và biểu diễn kết quả trên đồ thị cho thấy tài nguyên sử dụng và thời gian thực tế để thực thi thiết kế khác nhau theo từng dòng chip của FPGA. Từ dòng chip thấp Artix 7 có phần trăm LUT sử dụng cao nhất (48.86 %) và thời gian thực tế dài nhất (13.16 ns) đến dòng chip cao Kintex Ultrascale có phần trăm LUT sử dụng (5.68 %) và thời gian thực tế (6.91 ns) thấp nhất. Theo kết quả trên tần số thực thi cực đại của thiết kế đối với các dòng chip là khác nhau. Đối với chip Artix 7 là 75.99 MHz và Kintex Ultrascale là 144.7 MHz. Như vậy, các dòng chip đều có thể thực thi với tần số cao hơn tần số xung nhịp trong thiết kế. Do đó, khi chọn chip ta có thể lựa chọn dòng chip cao hơn để đáp ứng được tần số xung nhịp tối đa của mạch, đặc biệt đối với các bài toán với nhiều luồng dữ liệu đầu vào lớn, yêu cầu tần số hoạt động cao. Tốc độ xử lý dữ liệu của thiết kế (băng thông - BW) phụ thuộc vào các thông số bao gồm độ dài cửa sổ trượt S, số phần tử đối sánh M và tần số hệ thống F theo công thức BW = S × M × F. Băng thông lớn nhất của phần cứng trên thực tế được ước tính dựa trên giá trị lớn nhất của các thông số đã đề cập ở trên và phụ thuộc rất nhiều vào loại chip FPGA. Băng thông tối đa của thiết kế trên các chip FPGA khác nhau được thể hiện trong bảng 3, tuy nhiên băng thông thực tế có thể đạt được còn phụ thuộc vào kiểu giao tiếp giữa bo mạch FPGA và máy tính. Trên lý thuyết, thiết kế có thể đạt được băng thông tối đa lên đến 39,36 Gbps trên dòng Kintex Ultrascale FPGA. Bảng 3. Băng thông tối đa của thiết kế trên các mã chip FPGA khác nhau Dòng FPGA Artix-7 Kintex-7 Zynq-7000 Virtex-7 Kintex Ultrascale Mã chip XC7A100T XC7K325T XC7Z045F XC7V485T XCKU095 M (giá trị max) 16 48 56 72 136 Fmax (MHz) 75.99 109.67 112.02 111.17 144.70 BW (Gbps) 2.43 10.53 12.55 16.01 39.36 94 T. Q. Kiên, , Đ. V. Ngọc, “Thiết kế khối tăng tốc đồng bộ dữ liệu trên nền tảng FPGA.” Nghiên cứu khoa học công nghệ Trong nghiên cứu này, chúng tôi sử dụng bo mạch FPGA Kintex-7 XC7K325T có sẵn để kiểm tra trên thực tế, thiết kế đề xuất có thể đạt được băng thông tối đa 10,53 Gbps tương ứng với bộ tham số (M = 48, L = 128, N = 8, S = 2), nhanh hơn khoảng 945 lần so với thực thi tương đương trên phần mềm. 3.3. Kết quả tổng hợp và thực thi thiết kế trên phần cứng FPGA Cuối cùng, chúng tôi đã đánh giá hiệu quả của khối tăng tốc thông qua một ứng dụng thực tế. Cụ thể, thiết kế thực hiện đối sánh gần đúng với một ngưỡng lỗi có thể thay đổi và đối sánh cho các kiểu dữ liệu điều chế khác nhau với tổng số 512 mẫu. Thiết kế sẽ điều chỉnh phù hợp theo các giá trị của các thông số chung. Với các tham số thiết kế cụ thể, kết quả kiểm tra cho thấy số tài nguyên sử dụng bao gồm 54% LUT, 1% phần tử bộ nhớ và 33% RAM (hình 8, a). Trong quá trình thử nghiệm thực tế trên chip FPGA Kintex-7 XC7K355T, đầu vào của luồng dữ liệu không đồng nhất được đẩy xuống bo mạch thông qua giao thức AXI để thực hiện tìm kiếm (hình 8, b), thực thi tìm kiếm dữ liệu được gửi từ máy tính đến bo mạch FPGA (hình 8, c). a FPGA Board RX FIFO GE Matching PC Peripheral GE Engine TX FIFO b c Hình 8. Tiêu thụ tài nguyên trên chip và kiểm tra thiết kế trên bo mạch FPGA Digilent NETFPGA CML (Kintex7-XC7K355T). Để so sánh tốc độ giữa phần mềm và phần cứng, dữ liệu đầu vào dung lượng 3Gb được chuẩn bị với kiểu điều chế QPSK phân loại theo xác suất dữ liệu phù hợp. Dữ liệu 1 xác suất tìm được dữ liệu phù hợp là rất nhỏ (không tìm được dữ liệu phù hợp), dữ liệu 2 - trung bình (khoảng 50% dữ liệu phù hợp), dữ liệu 3 - khá cao (khoảng 80% dữ liệu phù hợp) và dữ liệu 4 - rất cao (khoảng 100% dữ liệu phù hợp). So sánh kết quả giữa phần cứng và phần mềm cho thấy dữ liệu được tìm kiếm và đồng bộ chính xác, khẳng định tính đúng đắn của thiết kế. Tốc độ đồng bộ dữ liệu của phần mềm và phần cứng với 3Gb dữ liệu QPSK được trình bày trong bảng 4. Tạp chí Nghiên cứu KH&CN quân sự, Số 71, 02 - 2021 95 Kỹ thuật điều khiển & Điện tử Bảng 4. Tốc độ đồng bộ dữ liệu của phần mềm và phần cứng với 3Gb dữ liệu QPSK. Phần mềm Phần cứng Dữ liệu Thời gian, s Băng thông, Mbps Thời gian, s Băng thông, Mbps Dữ liệu 1 4761.54 4.87 34.54 668.38 Dữ liệu 2 2635.41 8.76 31.31 741.26 Dữ liệu 3 1476.78 15.63 30.17 769.16 Dữ liệu 4 509.28 45.07 28.07 817.75 * Giả sử băng thông của cổng Ethernet 1 Gbps đạt cực đại Băng thông dựa trên phần mềm bị ảnh hưởng rất nhiều bởi cấu trúc dữ liệu đầu vào. Đối với dữ liệu 1 băng thông đạt được rất thấp chỉ đạt 4,87 Mbps, nguyên nhân là do không tìm thấy dữ liệu phù hợp nên quá trình dò tìm phải thực hiện dịch từng cặp 2 bit (đối với QPSK). Băng thông dựa trên phần mềm sẽ tăng theo tỉ lệ dữ liệu phù hợp và đạt tối đa với kiểu dữ liệu 4 là 45,07 Mbps, ở đây, tất cả dữ liệu tìm kiếm đều phù hợp. Đối với phần cứng băng thông ít phụ thuộc vào chất lượng dữ liệu đầu vào, tốc độ thấp nhất đạt khoảng 668,38 Mbps với dữ liệu 1 (gấp 137 lần so với phần mềm) và đạt tối đa là 817,75 Mbps với dữ liệu 4 (gấp 18 lần so với phần mềm). Kết quả này chưa đạt được tính toán băng thông cực đại theo mục 3.2 do băng thông bị giới hạn qua cổng Ethernet 1 Gbps. Kết quả này đáp ứng tốt yêu cầu về độ chính xác cũng như tốc độ tính toán đảm bảo đủ thời gian để thực hiện các nhiệm vụ tiếp theo. 4. KẾT LUẬN Trong bài báo này, chúng tôi đã đề xuất một thiết kế cho khối tăng tốc tìm kiếm dữ liệu và thực thi thiết kế đó trên nền tảng phần cứng có thể tái cấu hình FPGA nhờ những ưu điểm nổi bật của công nghệ này. Các tham số của thiết kế đã được khảo sát nhằm đánh giá tài nguyên sử dụng và tốc độ tìm kiếm dữ liệu. Trong một nghiên cứu cụ thể, một thực thi trên Kintex 7-XC7K325T với tất cả các kiểu điều chế PSK và QAM với các tham số đánh giá cụ thể bao gồm số mẫu N = 8, độ dài của mẫu L = 128 bit, số khối so sánh song song N = 512, tần số xung nhịp F = 100 MHz, phương pháp tìm kiếm cả chính xác và gần đúng cho giá trị băng thông đạt cỡ 800 Mbps, nhanh hơn khoảng 945 lần so với thực thi tương đương trên phần mềm và tỷ lệ tài nguyên sử dụng xấp xỉ 54%. Kết quả này đáp ứng tốt yêu cầu cả về độ chính xác cũng như tốc độ tính toán. Tuy nhiên, thiết kế cần tối ưu để cải thiện tốc độ tìm kiếm chẳng hạn như sử dụng nhiều bộ so sánh song song hoặc giảm kích thước dữ liệu đầu vào, từ đó, tăng tốc độ tìm kiếm và đồng bộ dữ liệu trên phần cứng. TÀI LIỆU THAM KHẢO [1]. Tien Manh Nguyen, “Phase-Ambiguity Resolution for QPSK Modulation Systems,” JPL Publication 89-4 (1989). [2]. Sadchenko, O. Kushnirenko, “QPSK-Modulation Modem Invariant to the Rotation of the Signal Constellation Plane”, Electrical, Control and Communication Engineering, vol. 14, no. 2 (2018), pp. 149–156. [3]. E. Kabalci et al, “Modelling and Analysis of a Power Line Communication System With QPSK Modem for Renewable Smart Grids”, International Journal of Electrical Power & Energy Systems, vol. 34, no. 1, pp. 19–28, Jan. 2012. [4]. M. Mukesh et al, “QPSK Modulator and Demodulator Using FPGA for SDR,” International. Journal of Engineering Research and Applications, vol. 4, no. 4 (2014), pp. 394–397. [5]. N. F. Huang et al, “A GPU-based Multiple-Pattern Matching Algorithm for Network Intrusion Detection Systems,” Proc. 22nd International Conference on Advanced Information Networking and Applications (AINA) (2008), pp. 62–67. [6]. T. N. Thinh et al, “A FPGA-based deep packet inspection engine for Network Intrusion Detection 96 T. Q. Kiên, , Đ. V. Ngọc, “Thiết kế khối tăng tốc đồng bộ dữ liệu trên nền tảng FPGA.” Nghiên cứu khoa học công nghệ System,” 9th International Conference on Electrical Engineering/Electronics, Computer, Telecommunications and Information Technology, Phetchaburi (2012), pp. 1-4. [7]. Fiessler et al, “HyPaFilter+: Enhanced Hybrid Packet Filtering Using Hardware Assisted Classification and Header Space Analysis,” IEEE/ACM Transactions on Networking, Vol. 25 (2017), pp. 3655-3669. [8]. F. Wang et al, “Research on Regular Expression Data Packet Matching Algorithm Based on Three State Content Addressable Memory,” International Journal of Simulation - Systems, Science and Technology, Vol. 16 (5A) (2015), pp. 8.1-8.5. [9]. R. Clark et al, “A hardware platform for network intrusion detection and prevention”, Proc. of Workshop on Network Processors and Applications (2005), pp. 136–145. [10]. P. Benácek et al, “P4-to-VHDL: Automatic Generation of 100 Gbps Packet Parsers,” Proc. IEEE 24th Annual International Symposium on Field-Programmable Custom Computing Machines (2016). ABSTRACT AN FPGA-BASED HARDWARE ACCELERATOR DATA SYNCHRONIZATION FROM DIGITAL RECEIVERS At present, the integrated density on digital integrated circuits has reached billions of transistors on a single chip, allowing the creation of dedicated hardware devices to accelerate the data processing, analysis, and searching of the large stream-based input data. The problem of processing big data obtained from digital receivers often encounters noise interference and phase deviation, leading to the need to analyze and rearrange them in the correct order for the next processing stages. If performed on software, these works are often inefficient because the processing speed does not meet the requirements. This paper proposes a searching and processing accelerator design for large stream-based data obtained from digital receivers, using a combination of parallel processing algorithms and pipeline techniques; conducts evaluations of the factors affecting the searching speed, and utilized resources to come up with the optimal design solution. We implemented the design on the Kintex 7-XC7K325T FPGA board for parallel data searching with a pattern length of 128 bits, using up to 512 comparison blocks at 100 MHz clock frequency and different modulation types such as PSK and QAM. Hardware performance is about 945 times faster than on the software with a maximum bandwidth of 800 Mbps. Keywords: FPGA; FPGA-based Accelerator; Parallel processing; Pipelined architecture. Nhận bài ngày 25 tháng 12 năm 2020 Hoàn thiện ngày 29 tháng 01 năm 2021 Chấp nhận đăng ngày 05 tháng 02 năm 2021 Địa chỉ: 1Học viện Kỹ thuật quân sự; 2Viện Khoa học Công nghệ quân sự. *Email: ngocqn@gmail.com. Tạp chí Nghiên cứu KH&CN quân sự, Số 71, 02 - 2021 97

File đính kèm:

thiet_ke_khoi_tang_toc_dong_bo_du_lieu_tu_may_thu_so_tren_ne.pdf

thiet_ke_khoi_tang_toc_dong_bo_du_lieu_tu_may_thu_so_tren_ne.pdf