Đề thi cuối học kỳ II môn Nhập môn mạch số - Năm học 2016-2017 - Đại học Công nghệ Thông tin

1. Câu hỏi 1 (2 điểm)

a. Thế nào là mạch tổ hợp và cho ví dụ? Thế nào là mạch tuần tự, khi nào ta cần

sử dụng mạch tuần tự và cho ví dụ? (1 điểm)

b. Nêu ưu điểm và khuyết điểm của mạch cộng Carry Look-Ahead (CLA) so với

mạch cộng Carrier Ripple Adder (CRA)(1 điểm)

Trang 1

Trang 2

Bạn đang xem tài liệu "Đề thi cuối học kỳ II môn Nhập môn mạch số - Năm học 2016-2017 - Đại học Công nghệ Thông tin", để tải tài liệu gốc về máy hãy click vào nút Download ở trên

Tóm tắt nội dung tài liệu: Đề thi cuối học kỳ II môn Nhập môn mạch số - Năm học 2016-2017 - Đại học Công nghệ Thông tin

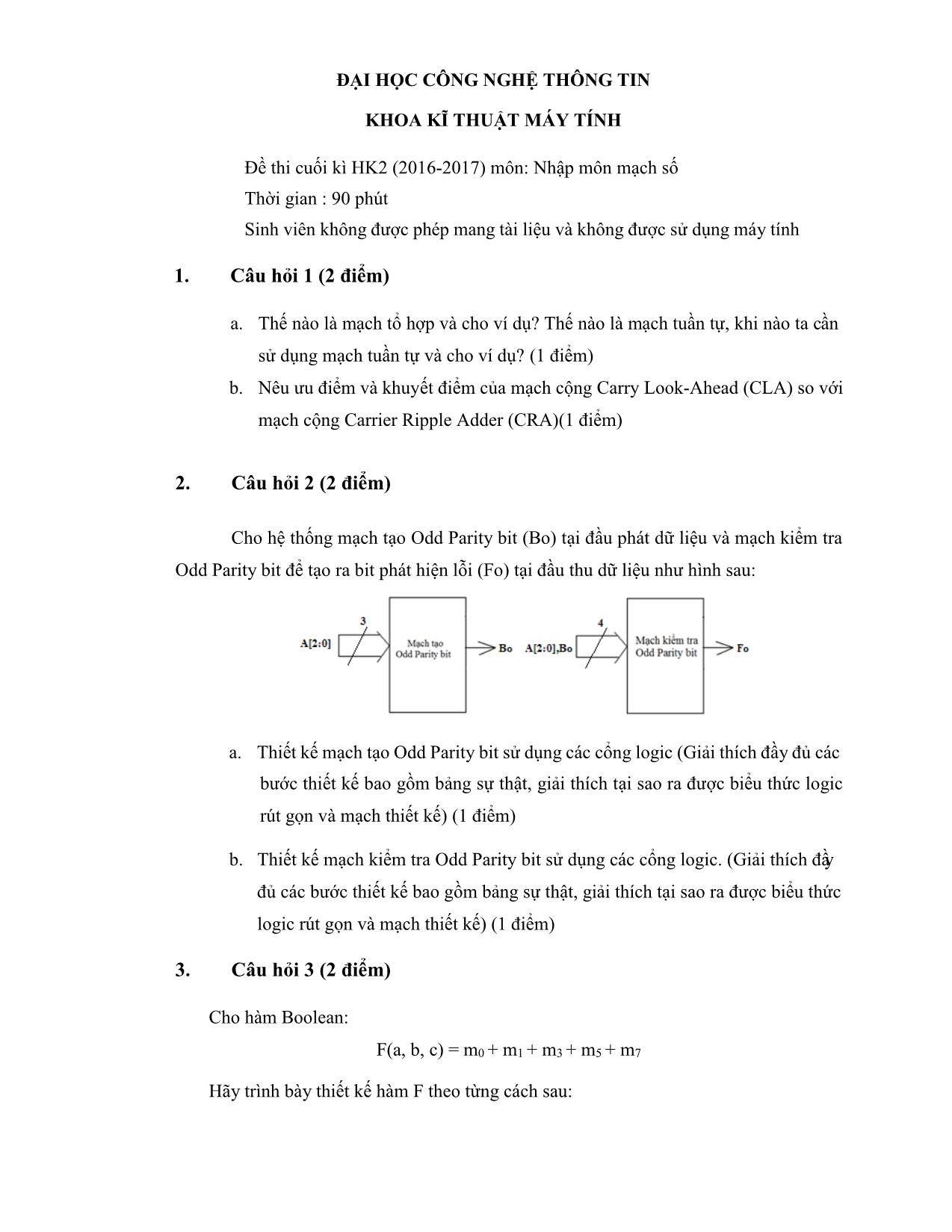

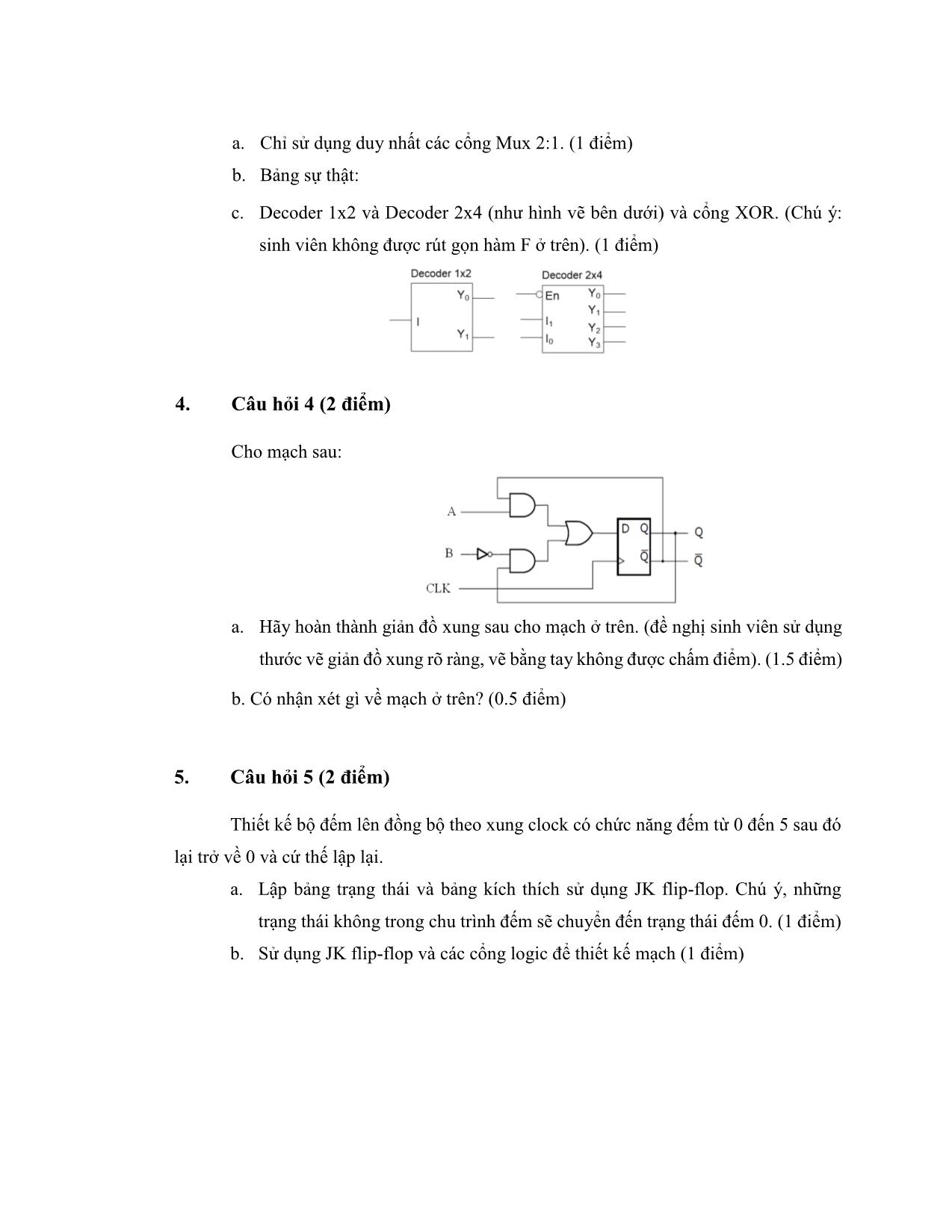

ĐẠI HỌC CÔNG NGHỆ THÔNG TIN KHOA KĨ THUẬT MÁY TÍNH Đề thi cuối kì HK2 (2016-2017) môn: Nhập môn mạch số Thời gian : 90 phút Sinh viên không được phép mang tài liệu và không được sử dụng máy tính 1. Câu hỏi 1 (2 điểm) a. Thế nào là mạch tổ hợp và cho ví dụ? Thế nào là mạch tuần tự, khi nào ta cần sử dụng mạch tuần tự và cho ví dụ? (1 điểm) b. Nêu ưu điểm và khuyết điểm của mạch cộng Carry Look-Ahead (CLA) so với mạch cộng Carrier Ripple Adder (CRA)(1 điểm) 2. Câu hỏi 2 (2 điểm) Cho hệ thống mạch tạo Odd Parity bit (Bo) tại đầu phát dữ liệu và mạch kiểm tra Odd Parity bit để tạo ra bit phát hiện lỗi (Fo) tại đầu thu dữ liệu như hình sau: a. Thiết kế mạch tạo Odd Parity bit sử dụng các cổng logic (Giải thích đầy đủ các bước thiết kế bao gồm bảng sự thật, giải thích tại sao ra được biểu thức logic rút gọn và mạch thiết kế) (1 điểm) b. Thiết kế mạch kiểm tra Odd Parity bit sử dụng các cổng logic. (Giải thích đầy đủ các bước thiết kế bao gồm bảng sự thật, giải thích tại sao ra được biểu thức logic rút gọn và mạch thiết kế) (1 điểm) 3. Câu hỏi 3 (2 điểm) Cho hàm Boolean: F(a, b, c) = m0 + m1 + m3 + m5 + m7 Hãy trình bày thiết kế hàm F theo từng cách sau: a. Chỉ sử dụng duy nhất các cổng Mux 2:1. (1 điểm) b. Bảng sự thật: c. Decoder 1x2 và Decoder 2x4 (như hình vẽ bên dưới) và cổng XOR. (Chú ý: sinh viên không được rút gọn hàm F ở trên). (1 điểm) 4. Câu hỏi 4 (2 điểm) Cho mạch sau: a. Hãy hoàn thành giản đồ xung sau cho mạch ở trên. (đề nghị sinh viên sử dụng thước vẽ giản đồ xung rõ ràng, vẽ bằng tay không được chấm điểm). (1.5 điểm) b. Có nhận xét gì về mạch ở trên? (0.5 điểm) 5. Câu hỏi 5 (2 điểm) Thiết kế bộ đếm lên đồng bộ theo xung clock có chức năng đếm từ 0 đến 5 sau đó lại trở về 0 và cứ thế lập lại. a. Lập bảng trạng thái và bảng kích thích sử dụng JK flip-flop. Chú ý, những trạng thái không trong chu trình đếm sẽ chuyển đến trạng thái đếm 0. (1 điểm) b. Sử dụng JK flip-flop và các cổng logic để thiết kế mạch (1 điểm)

File đính kèm:

de_thi_cuoi_hoc_ky_ii_mon_nhap_mon_mach_so_nam_hoc_2016_2017.pdf

de_thi_cuoi_hoc_ky_ii_mon_nhap_mon_mach_so_nam_hoc_2016_2017.pdf