Bài giảng Thiết kế hệ thống nhúng - Chương 6: Tổng hợp phần cứng và phần mềm - Bài 12: Công nghệ thiết kế

Tổng quan

• Tự động: tổng hợp

• Kiểm thử: đồng mô phỏng phần cứng/phần mềm

• Sử dụng lại: nền tảng dựa trên sở hữu trí tuệ

intellectual property (IP)

• Mô hình quá trình thiết kế3

• Nhiệm vụ thiết kế

– Định nghĩa chức năng của hệ thống

– Biến đổi các chức năng thành việc thực hiện vật lý, trong khi phải

• Đảm bảo các thông số ràng buộc

• Tối ƣu các thông số thiết kế khác

• Thiết kế hệ thống nhúng là một việc khó

– Phức tạp về chức năng

• Hàng triệu điều kiện làm việc khác nhau

• Nhiều ràng buộc

– Khoảng cách về tính sản xuất

• Khoảng 10 dòng code hoặc 100 transistors đƣợc sản xuất mỗi ngày

Trang 1

Trang 2

Trang 3

Trang 4

Trang 5

Trang 6

Trang 7

Trang 8

Trang 9

Trang 10

Tải về để xem bản đầy đủ

Bạn đang xem 10 trang mẫu của tài liệu "Bài giảng Thiết kế hệ thống nhúng - Chương 6: Tổng hợp phần cứng và phần mềm - Bài 12: Công nghệ thiết kế", để tải tài liệu gốc về máy hãy click vào nút Download ở trên

Tóm tắt nội dung tài liệu: Bài giảng Thiết kế hệ thống nhúng - Chương 6: Tổng hợp phần cứng và phần mềm - Bài 12: Công nghệ thiết kế

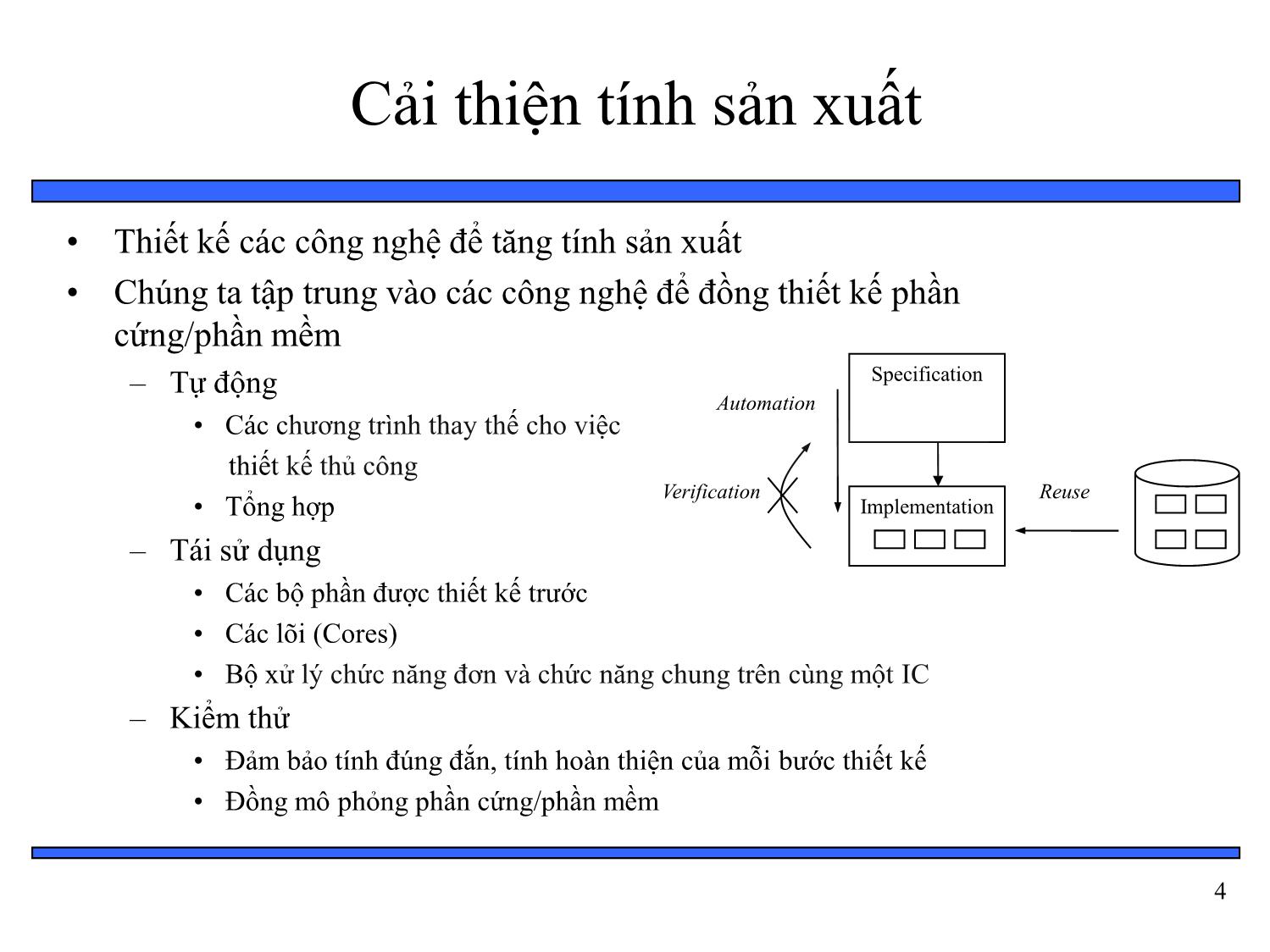

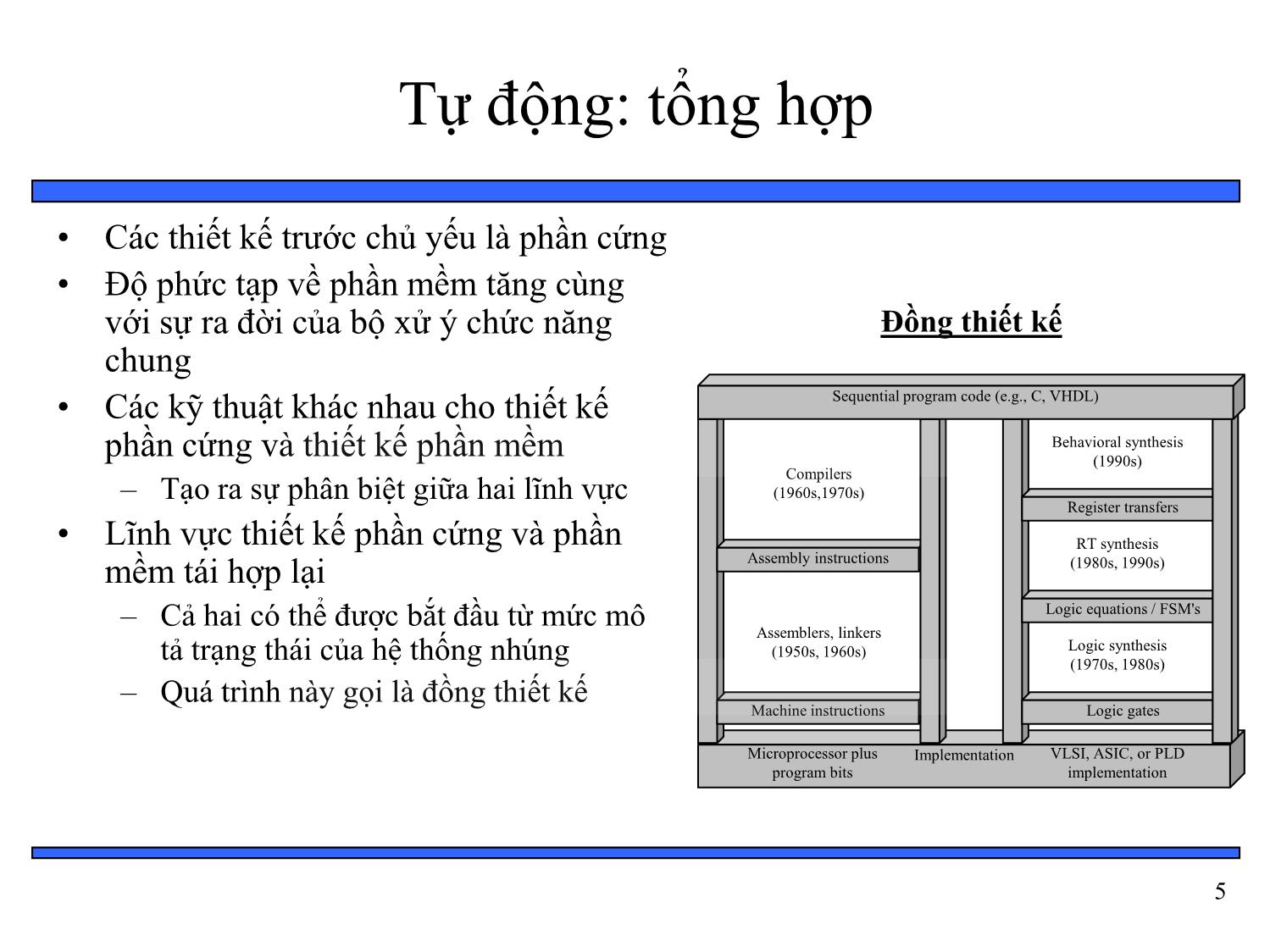

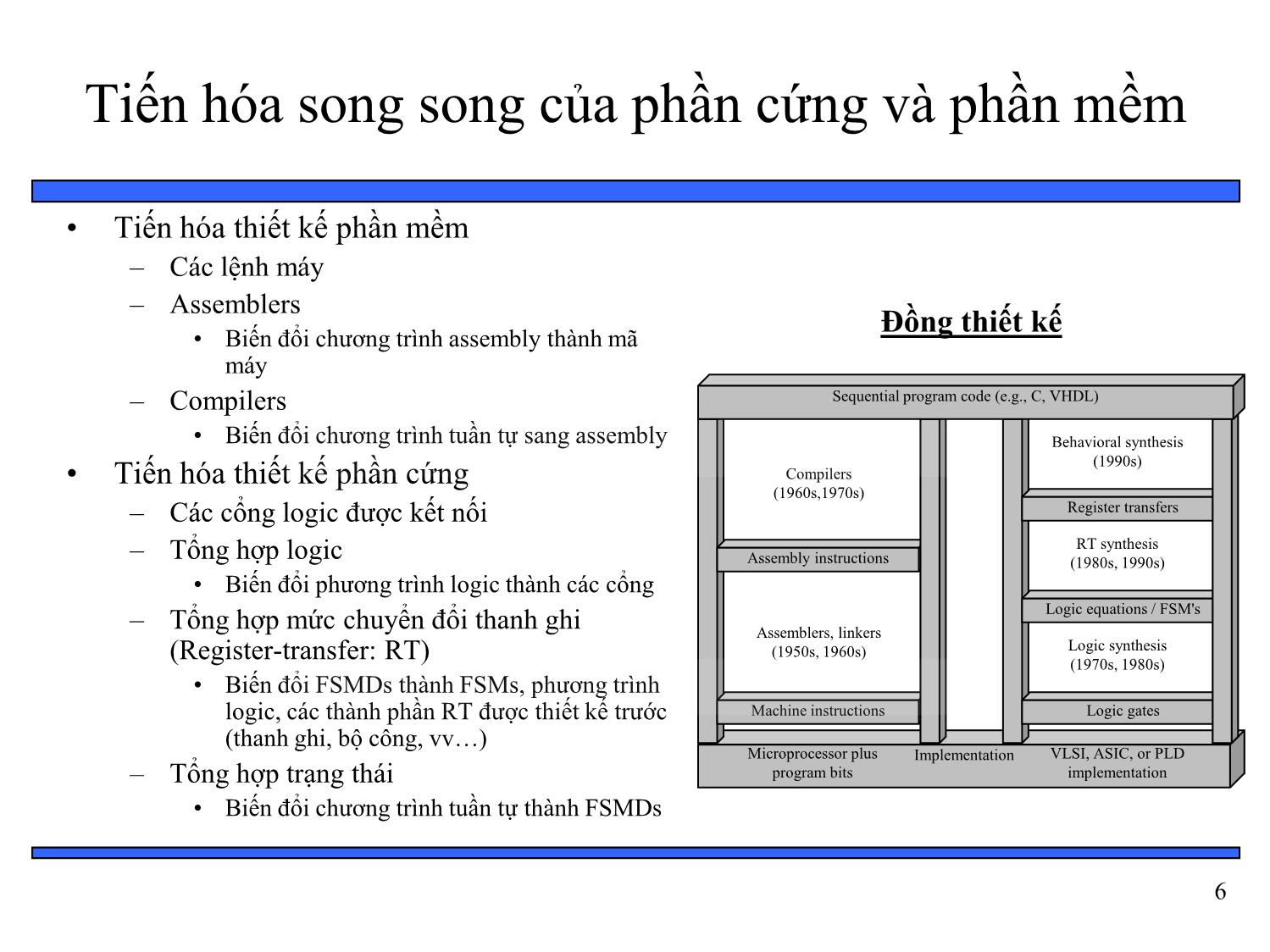

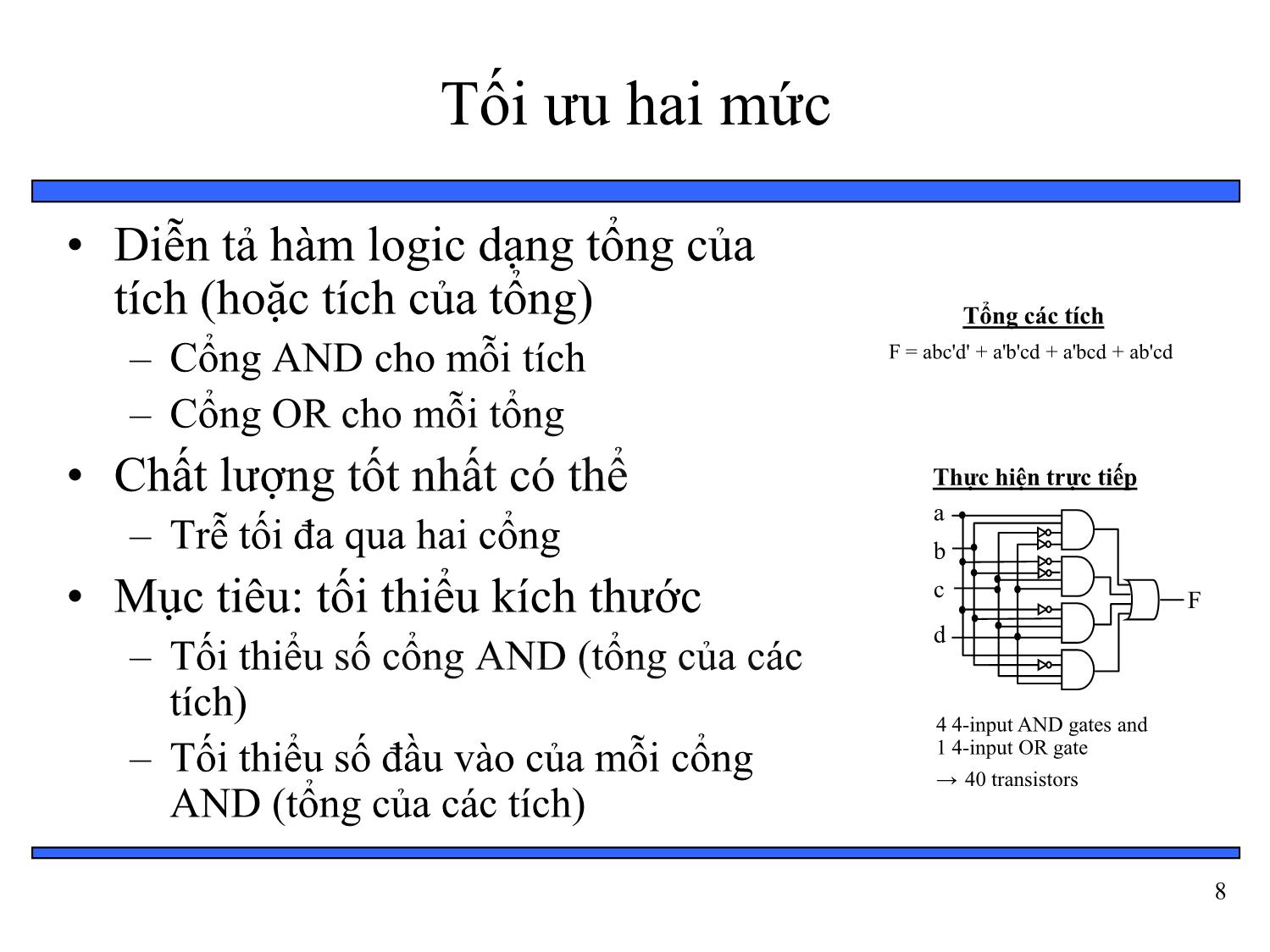

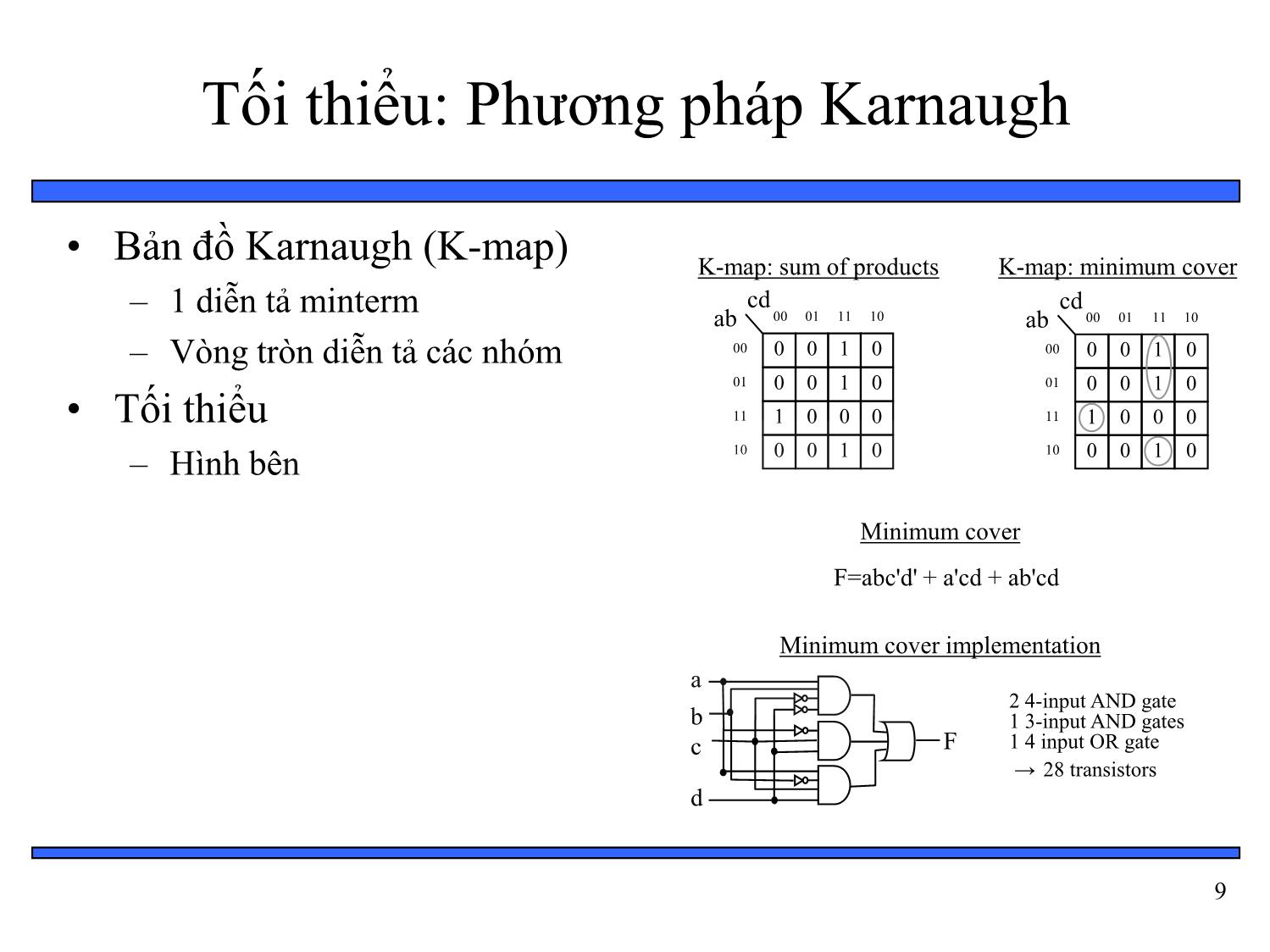

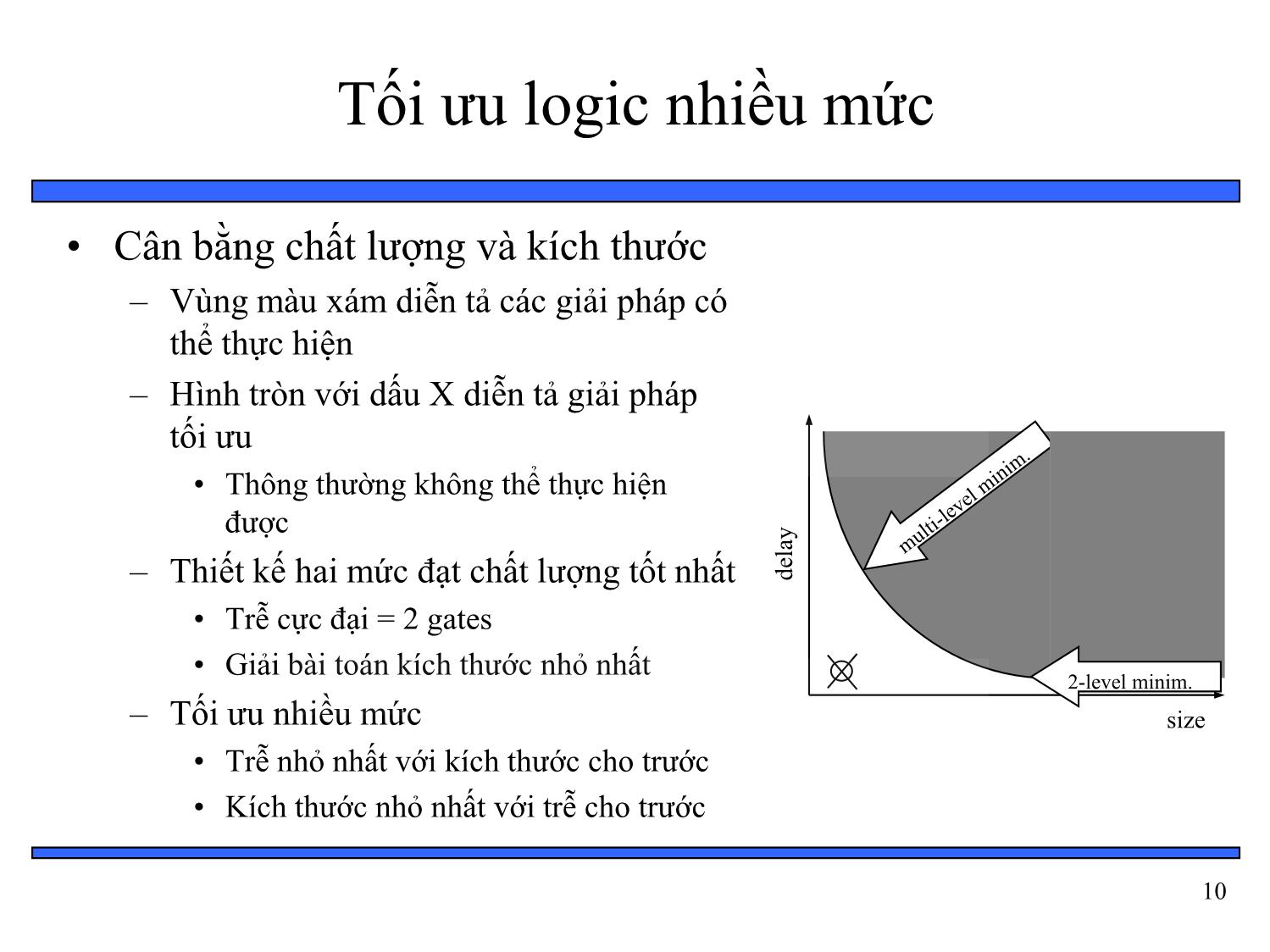

CHƢƠNGEmbedded 6 :Systems TỔNG HỢPDesign: PHẦN A Unified CỨNG Hardware/SoftwareVÀ PHẦN MỀM Introduction Bài 12: Công nghệ thiết kế 1 Tổng quan • Tự động: tổng hợp • Kiểm thử: đồng mô phỏng phần cứng/phần mềm • Sử dụng lại: nền tảng dựa trên sở hữu trí tuệ intellectual property (IP) • Mô hình quá trình thiết kế 2 Giới thiệu • Nhiệm vụ thiết kế – Định nghĩa chức năng của hệ thống – Biến đổi các chức năng thành việc thực hiện vật lý, trong khi phải • Đảm bảo các thông số ràng buộc • Tối ƣu các thông số thiết kế khác • Thiết kế hệ thống nhúng là một việc khó – Phức tạp về chức năng • Hàng triệu điều kiện làm việc khác nhau • Nhiều ràng buộc – Khoảng cách về tính sản xuất • Khoảng 10 dòng code hoặc 100 transistors đƣợc sản xuất mỗi ngày 3 Cải thiện tính sản xuất • Thiết kế các công nghệ để tăng tính sản xuất • Chúng ta tập trung vào các công nghệ để đồng thiết kế phần cứng/phần mềm – Tự động Specification Automation • Các chƣơng trình thay thế cho việc thiết kế thủ công Verification Reuse • Tổng hợp Implementation – Tái sử dụng • Các bộ phần đƣợc thiết kế trƣớc • Các lõi (Cores) • Bộ xử lý chức năng đơn và chức năng chung trên cùng một IC – Kiểm thử • Đảm bảo tính đúng đắn, tính hoàn thiện của mỗi bƣớc thiết kế • Đồng mô phỏng phần cứng/phần mềm 4 Tự động: tổng hợp • Các thiết kế trƣớc chủ yếu là phần cứng • Độ phức tạp về phần mềm tăng cùng với sự ra đời của bộ xử ý chức năng Đồng thiết kế chung • Các kỹ thuật khác nhau cho thiết kế Sequential program code (e.g., C, VHDL) Behavioral synthesis phần cứng và thiết kế phần mềm (1990s) Compilers – Tạo ra sự phân biệt giữa hai lĩnh vực (1960s,1970s) Register transfers • Lĩnh vực thiết kế phần cứng và phần RT synthesis mềm tái hợp lại Assembly instructions (1980s, 1990s) – Cả hai có thể đƣợc bắt đầu từ mức mô Logic equations / FSM's Assemblers, linkers (1950s, 1960s) Logic synthesis tả trạng thái của hệ thống nhúng (1970s, 1980s) – Quá trình này gọi là đồng thiết kế Machine instructions Logic gates Microprocessor plus Implementation VLSI, ASIC, or PLD program bits implementation 5 Tiến hóa song song của phần cứng và phần mềm • Tiến hóa thiết kế phần mềm – Các lệnh máy – Assemblers Đồng thiết kế • Biến đổi chƣơng trình assembly thành mã máy – Compilers Sequential program code (e.g., C, VHDL) • Biến đổi chƣơng trình tuần tự sang assembly Behavioral synthesis (1990s) • Tiến hóa thiết kế phần cứng Compilers (1960s,1970s) – Các cổng logic đƣợc kết nối Register transfers RT synthesis – Tổng hợp logic Assembly instructions (1980s, 1990s) • Biến đổi phƣơng trình logic thành các cổng Logic equations / FSM's – Tổng hợp mức chuyển đổi thanh ghi Assemblers, linkers (1950s, 1960s) Logic synthesis (Register-transfer: RT) (1970s, 1980s) • Biến đổi FSMDs thành FSMs, phƣơng trình logic, các thành phần RT đƣợc thiết kế trƣớc Machine instructions Logic gates (thanh ghi, bộ công, vv) Microprocessor plus Implementation VLSI, ASIC, or PLD – Tổng hợp trạng thái program bits implementation • Biến đổi chƣơng trình tuần tự thành FSMDs 6 Tổng hợp logic • Trạng thái mức logic sang cấu trúc thực hiện – Phƣơng trình logic và/hoặc FSM sang các cổng logic • Tổng hợp logic tổ hợp – Tối ƣu hai mức (Tổng các tích/tích các tổng) • Chất lƣợng tốt nhất có thể – Tuyến dài nhất = 2 cổng (cổng AND + cổng OR/cổng OR + cổng AND) • Kích cỡ tối thiểu – Tổi thiểu đầu vào/ra – Tối ƣu nhiều mức • Bù chất lƣợng và kích thƣớc • Tối ƣu – Tìm kiếm tối ƣu • Tổng hợp FSM – Tối ƣu trạng thái – Mã hóa trạng thái 7 Tối ƣu hai mức • Diễn tả hàm logic dạng tổng của tích (hoặc tích của tổng) Tổng các tích – Cổng AND cho mỗi tích F = abc'd' + a'b'cd + a'bcd + ab'cd – Cổng OR cho mỗi tổng • Chất lƣợng tốt nhất có thể Thực hiện trực tiếp a – Trễ tối đa qua hai cổng b • Mục tiêu: tối thiểu kích thƣớc c F d – Tối thiểu số cổng AND (tổng của các tích) 4 4-input AND gates and 1 4-input OR gate – Tối thiểu số đầu vào của mỗi cổng → 40 transistors AND (tổng của các tích) 8 Tối thiểu: Phƣơng pháp Karnaugh • Bản đồ Karnaugh (K-map) K-map: sum of products K-map: minimum cover – 1 diễn tả minterm cd cd ab 00 01 11 10 ab 00 01 11 10 – Vòng tròn diễn tả các nhóm 00 0 0 1 0 00 0 0 1 0 01 0 0 1 0 01 0 0 1 0 • Tối thiểu 11 1 0 0 0 11 1 0 0 0 – Hình bên 10 0 0 1 0 10 0 0 1 0 Minimum cover F=abc'd' + a'cd + ab'cd Minimum cover implementation a 2 4-input AND gate b 1 3-input AND gates c F 1 4 input OR gate → 28 transistors d 9 Tối ƣu logic nhiều mức • Cân bằng chất lƣợng và kích thƣớc – Vùng màu xám diễn tả các giải pháp có thể thực hiện – Hình tròn với dấu X diễn tả giải pháp tối ƣu • Thông thƣờng không thể thực hiện đƣợc – Thiết kế hai mức đạt chất lƣợng tốt nhất delay • Trễ cực đại = 2 gates • Giải bài toán kích thƣớc nhỏ nhất 2-level minim. – Tối ƣu nhiều mức size • Trễ nhỏ nhất với kích thƣớc cho trƣớc • Kích thƣớc nhỏ nhất với trễ cho trƣớc 10 Ví dụ • Tối thiểu hàm logic hai mức: – F = adef + bdef + cdef + gh 2-level minimized – Yêu cầu 5 cổng với tổng số 18 đầu vào cổng a d • 4 AND và 1 OR b e • Sau khi biến đổi đại số: c F – F = (a + b + c)def + gh f – Chỉ yêu cầu 4 cổng với tổng số 11 đầu vào g cổng h • 2 AND và 2 OR multilevel minimized – Ít đầu vào/cổng hơn a b – Giả sử mỗi đầu vào cổng = 2 transistors c • Giảm đƣợc 14 transistors d e – 36 (18 * 2) xuống còn 22 (11 * 2) f – Hy sinh chất lƣợng để đạt kích thƣớc g F • Đầu vào a, b, và c có mức trễ 3 cổng h 11 Tổng hợp FSM • Chuyển FSM sang cổng • Tối thiểu trạng thái – Giảm số trạng thái • Nhận dạng và ghép các trạng thái tƣơng đƣơng – Cùng đầu ra, trạng thái tiếp theo đối với tất cả các đầu vào – Dùng bảng • Lập bảng tất cả các cặp trạng thái có thể • Nếu có n trạng thái, bảng có n2 tham số • Mã hóa trạng thái – Tuần tự bit duy nhất cho mỗi trạng thái – Nếu có n trạng thái, cần log2(n) bits – n! phƣơng pháp mã hóa 12 Mô phỏng • Tạo ra mô hình máy tính cho thiết kế – Cung cấp đầu vào mẫu – Kiểm tra đầu ra • Ví dụ kiểm tra tính đúng đắn – ALU • Cung cấp tất cả các đầu vào có thể (kết hợp) • Kiểm tra tính đúng đắn của kết quả đầu ra • Ví dụ về tính hoàn thiện – Cửa thang máy đóng khi di chuyển • Cung cấp tất cả các đầu vào tuần tự có thể • Kiểm tra cửa luôn đóng khi thang máy di chuyển 13 Tái sử dụng: Sử dụng các sản phẩm sở hữu trí tuệ (intellectual property – IP) • Các thành phần có sẵn (COST) – Đƣợc thiết kế trƣớc, IC đƣợc đóng gói trƣớc – Thực hiện GPP hoặc SPP – Giảm thời gian thiết kế • Hệ on-chip (SOC) – Tất cả các thành phần của hệ đƣợc thực hiện trên một chip đơn – Làm tăng khả năng của IC 14 Các thách thức với nhà cung cấp bộ xử lý • “Lõi đã làm thay đổi đáng kể mô hình kinh doanh – Mô hình giá • Quá khứ – Các nhà sản xuất bán sản phẩm IC cho ngƣời thiết kế – Nhà thiết kế phải mua thêm các bản copy • Hiện tại – Các nhà sản xuất bán sản phẩm là các IP – Nhà thiết kế có thể tạo nhiều bản copy • Các nhà sản xuất có thể dùng mô hình giá khác nhau – Mô hình dựa trên bản quyền • Tƣơng tự mô hình IC cũ • Nhà thiết kế trả tiền cho các model bổ sung – Mô hình giá cố định • Giá duy nhất cho IP và các bản copy cần thiết khác – Nhiều mô hình khác 15 Các thách thức với ngƣời sử dụng bộ xử lý • Đàm phán về cấp phép – Không đơn giản nhƣ mua IC – Mô hình giá và bảo vệ IP • Yêu cầu trợ giúp của pháp luật, bản quyền • Nỗ lực thiết kế bổ sung – Đặc biệt với soft cores • Phải đƣợc tổng hợp và kiểm tra • Sự thay đổi nhỏ trong thiết kế có thể gây vấn đề lớn • Yêu cầu kiểm tra khó khăn hơn – Extensive testing for synthesized soft cores and soft/firm cores mapped to particular technology • Ensure correct synthesis • Timing and power vary between implementations – Early verification critical • Cores buried within IC • Cannot simply replace bad core 16 Tóm tắt • Công nghệ thiết kế nhằm giảm khoảng cách giữa khả năng của IC và tính sản xuất • Quá trình tổng hợp đã thay đổi thiết kế số • Tăng khả năng của IC có nghĩa các thành phần sw/hw cùng tồn tại trên một chip • Quá trình thiết kế dịch chuyển sang thiết kế dựa trên “lõi” • Mô phỏng là cần thiết nhƣng rất khó • Thiết kế quá trình xoắn ốc là phổ biến 17

File đính kèm:

bai_giang_thiet_ke_he_thong_nhung_chuong_6_tong_hop_phan_cun.pdf

bai_giang_thiet_ke_he_thong_nhung_chuong_6_tong_hop_phan_cun.pdf