Bài giảng Thiết kế hệ thống nhúng - Chương 2: Cấu trúc phần cứng hệ thống nhúng - Bài 4: Bộ nhớ

Tổng quan

• Khả năng ghi dữ liệu và chất lƣợng lƣu trữ của bộ nhớ

• Các kiểu bộ nhớ chung

• Ghép bộ nhớ

• Phân cấp bộ nhớ và Cache

• RAM cải tiến3

Giới thiệu

• Chức năng của các hệ nhúng

– Xử lý

• Bộ xử lý

• Biến đổi dữ liệu

– Lƣu trữ

• Bộ nhớ

• Khôi phục dữ liệu

– Truyền thông

• Bus

• Chuyển dữ liệu

Trang 1

Trang 2

Trang 3

Trang 4

Trang 5

Trang 6

Trang 7

Trang 8

Trang 9

Trang 10

Tải về để xem bản đầy đủ

Bạn đang xem 10 trang mẫu của tài liệu "Bài giảng Thiết kế hệ thống nhúng - Chương 2: Cấu trúc phần cứng hệ thống nhúng - Bài 4: Bộ nhớ", để tải tài liệu gốc về máy hãy click vào nút Download ở trên

Tóm tắt nội dung tài liệu: Bài giảng Thiết kế hệ thống nhúng - Chương 2: Cấu trúc phần cứng hệ thống nhúng - Bài 4: Bộ nhớ

CHƢƠNGEmbedded 2 Systems: CẤU TRÚC Design: PHẦN A Unified CỨNG

Hardware/SoftwareHỆ THỐNG NHÚNG Introduction

Bài 4: Bộ nhớ

1

Tổng quan

• Khả năng ghi dữ liệu và chất lƣợng lƣu trữ của bộ nhớ

• Các kiểu bộ nhớ chung

• Ghép bộ nhớ

• Phân cấp bộ nhớ và Cache

• RAM cải tiến

2

Giới thiệu

• Chức năng của các hệ nhúng

– Xử lý

• Bộ xử lý

• Biến đổi dữ liệu

– Lƣu trữ

• Bộ nhớ

• Khôi phục dữ liệu

– Truyền thông

• Bus

• Chuyển dữ liệu

3

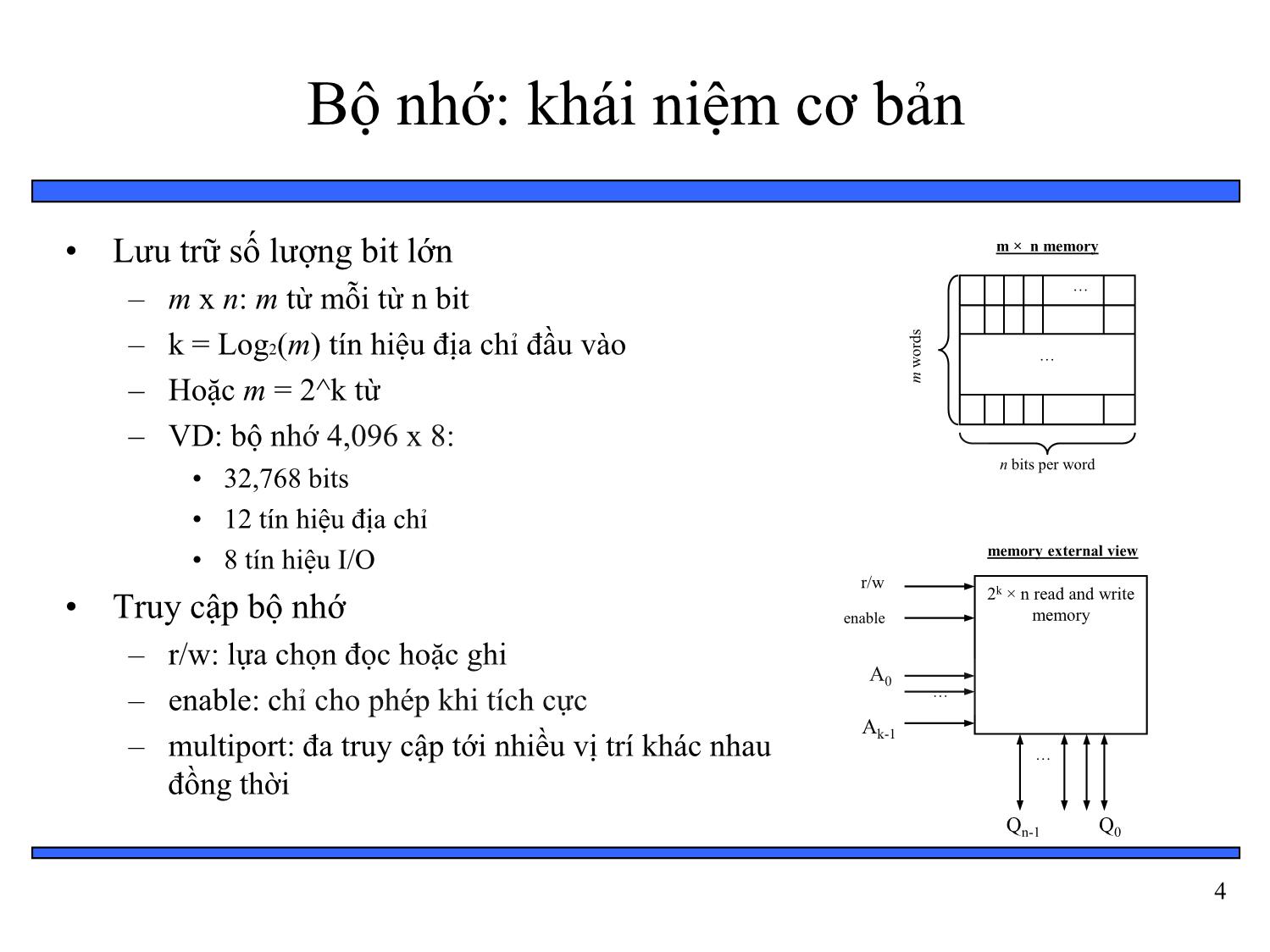

Bộ nhớ: khái niệm cơ bản

• Lƣu trữ số lƣợng bit lớn m × n memory

– m x n: m từ mỗi từ n bit

– k = Log2(m) tín hiệu địa chỉ đầu vào

words

– Hoặc m = 2^k từ m

– VD: bộ nhớ 4,096 x 8:

n bits per word

• 32,768 bits

• 12 tín hiệu địa chỉ

• 8 tín hiệu I/O memory external view

r/w

2k × n read and write

• Truy cập bộ nhớ enable memory

– r/w: lựa chọn đọc hoặc ghi

A0

– enable: chỉ cho phép khi tích cực

Ak-1

– multiport: đa truy cập tới nhiều vị trí khác nhau

đồng thời

Qn-1 Q0

4

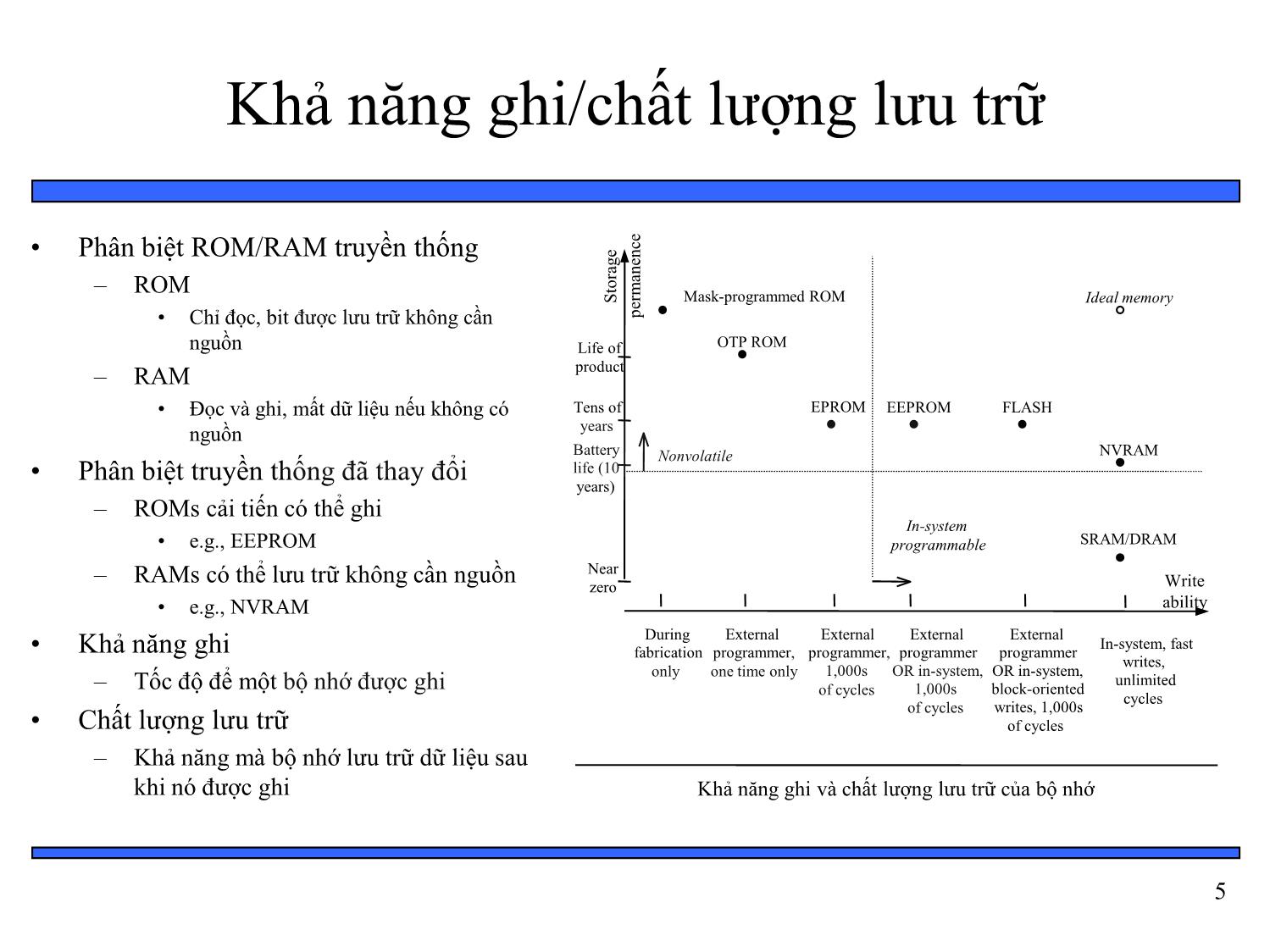

Khả năng ghi/chất lƣợng lƣu trữ

• Phân biệt ROM/RAM truyền thống

– ROM

Storage Mask-programmed ROM Ideal memory

• Chỉ đọc, bit đƣợc lƣu trữ không cần permanence

nguồn Life of OTP ROM

– RAM product

• Đọc và ghi, mất dữ liệu nếu không có Tens of EPROM EEPROM FLASH

nguồn years

Battery Nonvolatile NVRAM

• Phân biệt truyền thống đã thay đổi life (10

years)

– ROMs cải tiến có thể ghi

In-system

• e.g., EEPROM programmable SRAM/DRAM

– RAMs có thể lƣu trữ không cần nguồn Near

zero Write

• e.g., NVRAM ability

During External External External External

In-system, fast

• Khả năng ghi fabrication programmer, programmer, programmer programmer

writes,

only one time only 1,000s OR in-system, OR in-system,

unlimited

– Tốc độ để một bộ nhớ đƣợc ghi of cycles 1,000s block-oriented

cycles

of cycles writes, 1,000s

• Chất lƣợng lƣu trữ of cycles

– Khả năng mà bộ nhớ lƣu trữ dữ liệu sau

khi nó đƣợc ghi Khả năng ghi và chất lƣợng lƣu trữ của bộ nhớ

5

Khả năng ghi

• Phạm vi của “khả năng ghi”

– Mức cao

• Bộ xử lý ghi vào bộ nhớ một cách đơn giản và nhanh chóng

• e.g., RAM

– Mức trung bình

• Bộ xử lý ghi vào bộ nhớ, nhƣng chậm

• e.g., FLASH, EEPROM

– Mức thấp hơn

• Các thiết bị đặc biệt, “bộ lập trình” phải đƣợc sử dụng để ghi bộ nhớ

• e.g., EPROM, OTP ROM

– Mức thấp

• bits chỉ đƣợc lƣu trữ trong quá trình sản xuất

• VD: ROM lập trình đƣợc bằng mặt nạ

• Bộ nhớ có thể lập trình đƣợc trong hệ thống

– Có thể đƣợc ghi bởi bộ xử lý trong hệ thống nhúng

– Các bộ nhớ loại này có khả năng ghi cao hoặc trung bình

6

Chất lƣợng lƣu trữ

• Phạm vi chất lƣợng lƣu trữ

– Loại cao

• Loại không bao giờ mất bit

• VD: mask-programmed ROM

– Loại trung bình

• Có khả năng lƣu trữ bit nhiều ngày, nhiều tháng, hoặc nhiều năm sau khi tắt nguồn

• VD: NVRAM

– Loại trung bình thấp

• Có khả năng lƣu trữ bit khi có nguồn cung cấp

• VD: SRAM

– Loại thấp

• Mất bít gần nhƣ ngay sau khi đƣợc ghi

• VD: DRAM

• Bộ nhớ không thay đổi đƣợc

– Lƣu trữ bit ngay cả khi không đƣợc cấp nguồn

– Chất lƣợng lƣu trữ cao hoặc trung bình

7

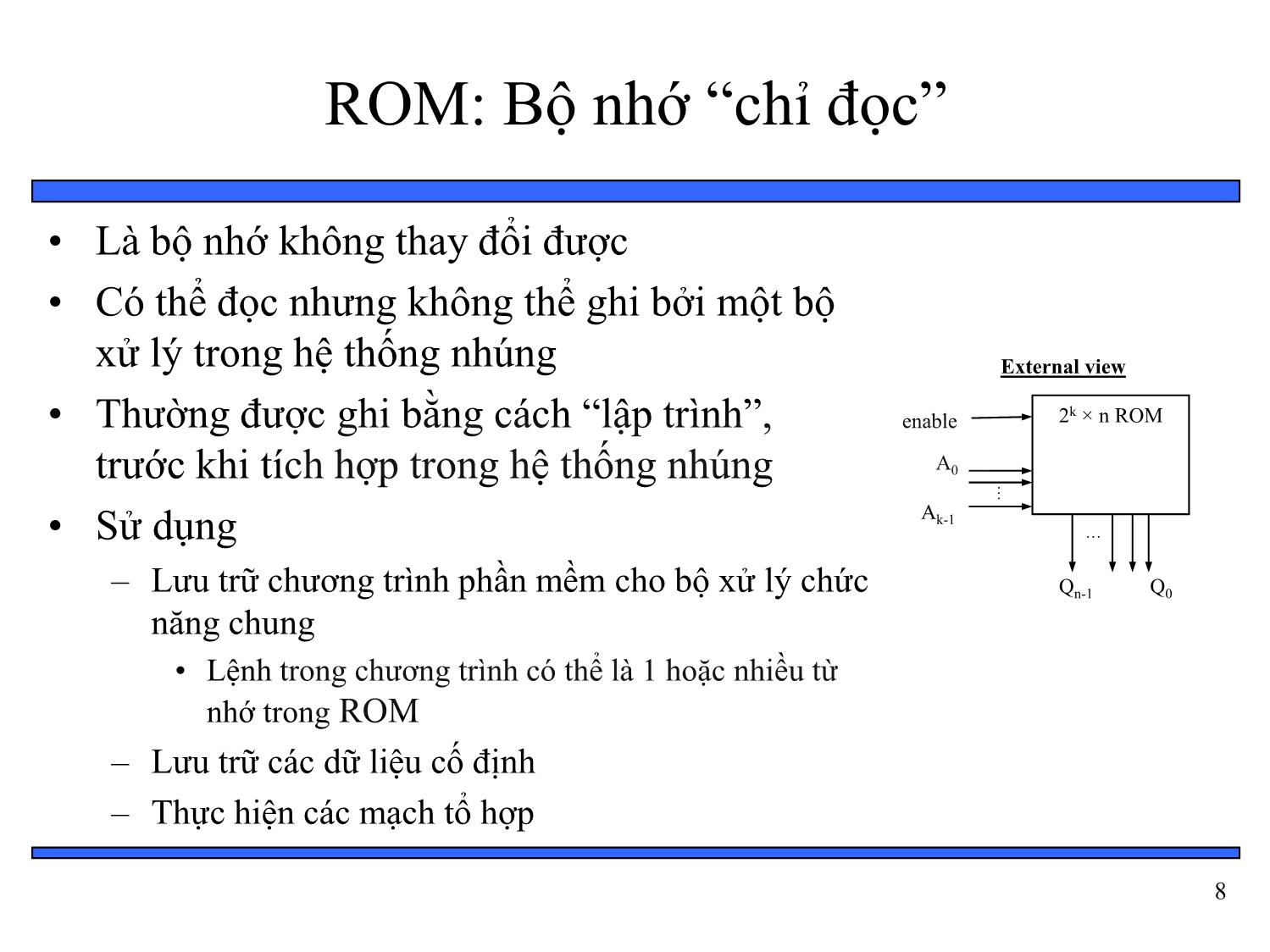

ROM: Bộ nhớ “chỉ đọc”

• Là bộ nhớ không thay đổi đƣợc

• Có thể đọc nhƣng không thể ghi bởi một bộ

xử lý trong hệ thống nhúng External view

• Thƣờng đƣợc ghi bằng cách “lập trình”, enable 2k × n ROM

A0

trƣớc khi tích hợp trong hệ thống nhúng

Ak-1

• Sử dụng

– Lƣu trữ chƣơng trình phần mềm cho bộ xử lý chức Qn-1 Q0

năng chung

• Lệnh trong chƣơng trình có thể là 1 hoặc nhiều từ

nhớ trong ROM

– Lƣu trữ các dữ liệu cố định

– Thực hiện các mạch tổ hợp

8

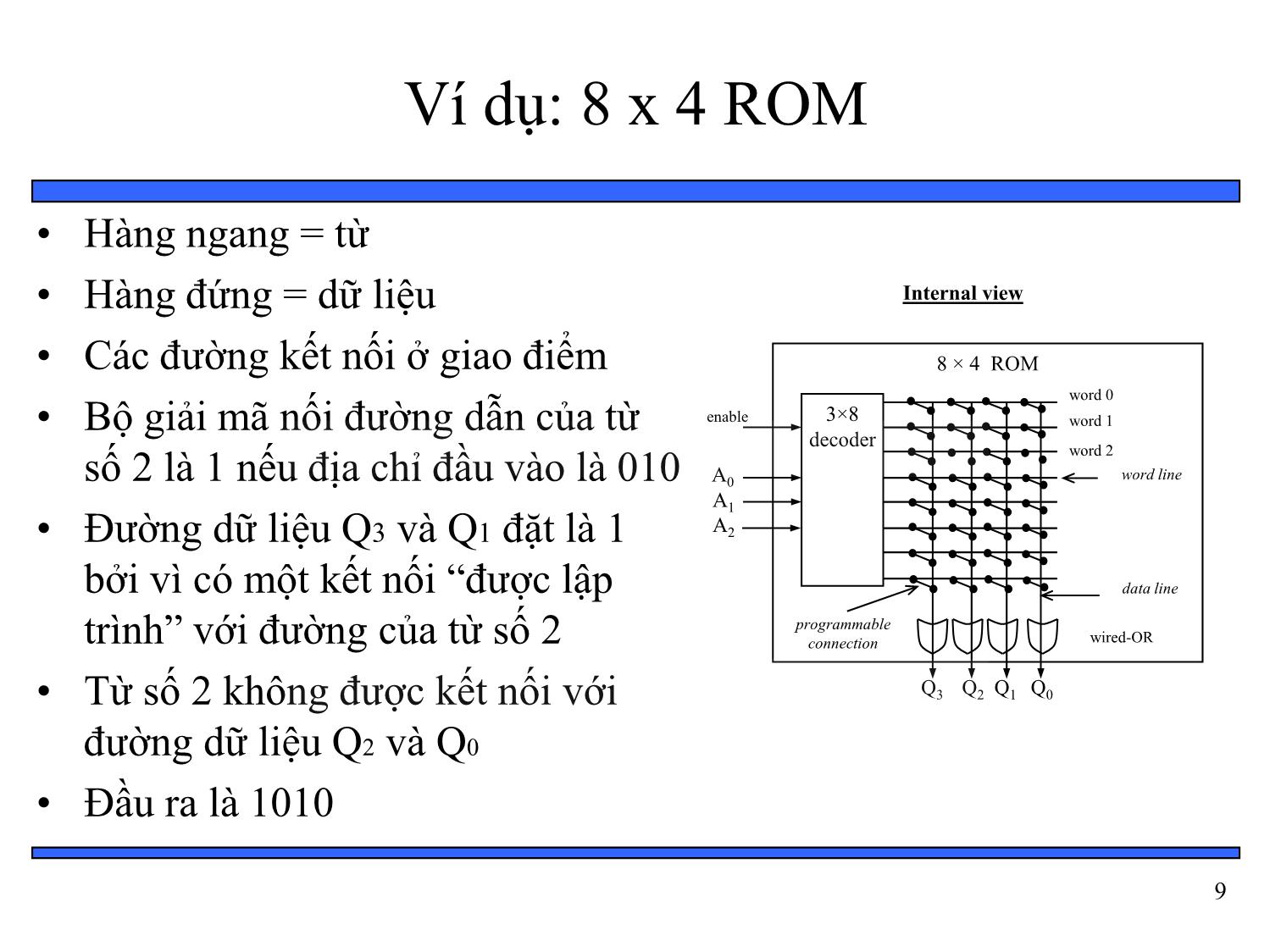

Ví dụ: 8 x 4 ROM

• Hàng ngang = từ

• Hàng đứng = dữ liệu Internal view

• Các đƣờng kết nối ở giao điểm 8 × 4 ROM

word 0

• Bộ giải mã nối đƣờng dẫn của từ enable 3×8 word 1

decoder

word 2

số 2 là 1 nếu địa chỉ đầu vào là 010 A0 word line

A1

• Đƣờng dữ liệu Q3 và Q1 đặt là 1 A2

bởi vì có một kết nối “đƣợc lập data line

programmable

trình” với đƣờng của từ số 2 connection wired-OR

• Từ số 2 không đƣợc kết nối với Q3 Q2 Q1 Q0

đƣờng dữ liệu Q2 và Q0

• Đầu ra là 1010

9

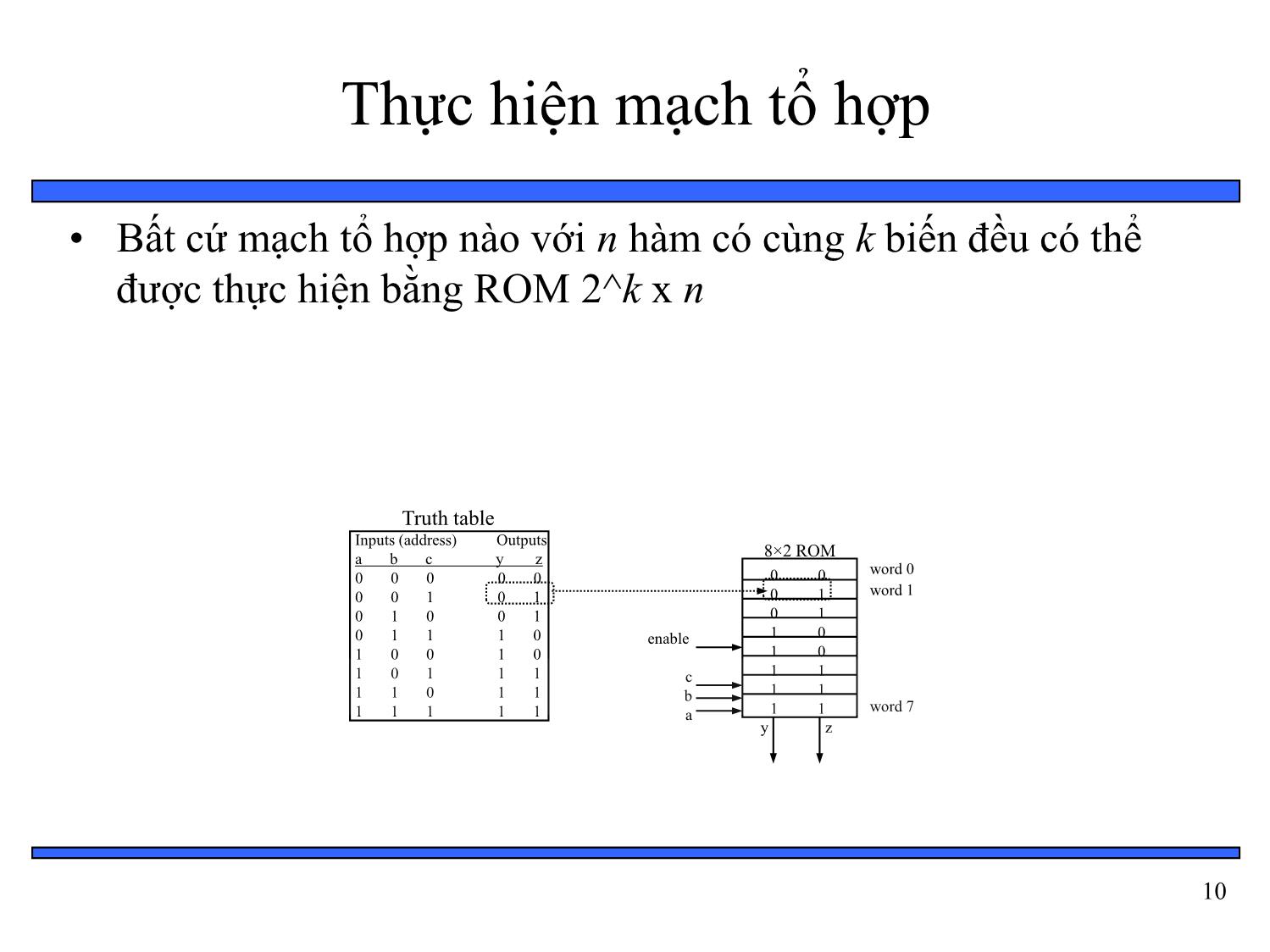

Thực hiện mạch tổ hợp

• Bất cứ mạch tổ hợp nào với n hàm có cùng k biến đều có thể

đƣợc thực hiện bằng ROM 2^k x n

Truth table

Inputs (address) Outputs

a b c y z 8×2 ROM

word 0

0 0 0 0 0 0 0

0 0 1 0 1 0 1 word 1

0 1 0 0 1 0 1

0 1 1 1 0 enable 1 0

1 0 0 1 0 1 0

1 0 1 1 1 c 1 1

1 1 0 1 1 b 1 1

word 7

1 1 1 1 1 a 1 1

y z

10

ROM lập trình bằng mặt nạ

• Các kết nối đƣợc “lập trình” khi sản xuất

– Thiết lập các mặt nạ

• Khả năng ghi thấp nhất

– Chỉ ghi một lần

• Chất lƣợng lƣu trữ cao nhất

– Bít không bao giờ thay đổi

• Đƣợc sử dụng điển hình cho các thiết kế cuối cùng của hệ

với dung lƣợng lớn

– Giá NRE cao nếu sản xuất với số lƣợng ít

11

OTP ROM: ROM lập trình một lần

• Các kết nối đƣợc “lập trình” sau khi sản xuất bởi ngƣời sử dụng

– Ngƣời sử dụng cung cấp nội dung yêu cầu lƣu trữ trong ROM

– Nội dung đƣợc đƣa vào thiết bị gọi là bộ lập trình ROM

– Mỗi kết nối có thể lập trình đƣợc là một cầu chì

– Bộ lập trình ROM phá vỡ các cầu chì khi không muốn duy trì kết nối

• Khả năng ghi rất thấp

– Điển hình ghi chỉ một lần và yêu cầu thiết bị lập trình ROM

• Chất lƣợng lƣu trữ rất cao

– Bit không thay đổi trừ khi kết nối với bộ lập trình

• Thƣờng sử dụng trong các sản phầm cuối cùng

– Rẻ, khó thay đổi nội dung

12

EPROM: ROM lập trình ghi xóa

• Phần tử có thể lập trình là một transistor MOS

– Transistor có cổng “floating” bao quanh bởi chất cách điện

0V

– (a) Điện tích âm hình thành một kênh giữa nguồn và máng lƣu floating gate

giữ mức logic “1” source drain

– (b) Điện áp dƣơng lớn ở “cổng” làm cho các điện tích âm di

chuyển ra khỏi kênh và duy trì trong cổng “floating” lƣu trữ mức (a)

logic 0

– (c) (Xóa) chiếu tia UV trên bề mặt cổng “floating” làm cho các

điện tích âm trở lại kênh từ cổng “floating” lƣu trữ mức logic 1 +15V

– (d) Một IC EPROM có một cửa sổ để tia UV có thể chiếu qua

(b) source drain

• Khả năng ghi tốt

– Có thể tẩy xóa và lập trình hàng nghìn lần

5-30 min

• Chất lượng lưu trữ giảm

– Chƣơng trình kéo dài khoảng 10 năm nhƣng sẽ bị suy source drain

giảm do nhiễu bức xạ và từ trƣờng (c)

• Điển hình được sử dụng trong quá trình phát triển

sản phẩm (d)

. 13

EEPROM: ROM có thể ghi xóa bằng điện

• Lập trình và xóa bằng điện

– Sử dụng mức điện áp cao hơn bình thƣờng

– Có thể lập trình và xóa từng từ riêng

• Khả năng ghi tốt

– Có thể lập trình trong hệ thống với mạch tích hợp để cung cấp điện áp cao

hơn mức thông thƣờng

• Bộ điều khiển tích hợp trong bộ nhớ thƣờng dùng để ẩn các chi tiết từ ngƣời

sử dụng bộ nhớ

– Ghi rất chậm do xóa và lập trình

• Chân “busy” biểu thị với bộ xử lý là EEPROM vẫn đang trong quá trình ghi

– Khả năng xóa và lập trình có thể lên tới 10 nghìn lần

• Chất lƣợng lƣu trữ tƣơng tự nhƣ EPROM (khoảng 10 năm)

• Thuận tiện hơn EPROMs, nhƣng đắt hơn

14

Bộ nhớ Flash

• Mở rộng của EEPROM

– Nguyên lý cổng “floating” tƣơng tự

– Chất lƣợng lƣu trữ và khả năng ghi tƣơng tự

• Xóa nhanh

– Nhiều ô nhớ đƣợc xóa đồng thời, chứ không chỉ một ô nhớ tại một thời

điểm

– Các khối nhớ có kích thƣớc khoảng vài nghìn byte

• Khả năng ghi từng từ có thể chậm hơn

– Toàn bộ khối phải đƣợc đọc, từ đƣợc cập nhật, sau đó toàn bộ khối đƣợc

ghi

• Sử dụng với các hệ thống nhúng lƣu trữ dữ liệu lớn trong bộ

nhớ

– VD: camera số, điện thoại di động

15

RAM: Bộ nhớ “Truy cập ngẫu nhiên”

• Thường là bộ nhớ “volatile” external view

r/w 2k × n read and write

– Dữ liệu bị mất khi không có nguồn cấp enable memory

• Khi và đọc dễ dàng trong hệ thống nhúng trong A0

quá trình làm việc

Ak-1

• Cấu trúc bên trong phức tạp hơn ROM

– Một từ nhớ có vài ô nhớ, mỗi ô nhớ chứa một Qn-1 Q0

bít nhớ internal view

I I I I

– Mỗi đƣờng dữ liệu vào và ra kết nối tới mỗi ô 3 2 1 0

nhớ trong cột của nó

4×4 RAM

– rd/wr Kết nối tới tất cả các ô nhớ

enable 2×4

– Khi hàng đƣợc “enable” bởi bộ giải mã, mỗi ô decoder

nhớ có mức logic lƣu trữ bít dữ liệu đầu vào A0

A1

khi chân rd/wr biểu thị ghi hoặc đầu ra lƣu trữ Memory

bit khi chân rd/wr biểu thị đọc cell

rd/wr To every cell

Q3 Q2 Q1 Q0

16

Các kiểu RAM cơ bản

• SRAM: RAM tĩnh memory cell internals

– Ô nhớ dùng flip-flop để lƣu trữ bít

– Yêu cầu 6 transistors SRAM

– Giữ dữ liệu khi có nguồn cấp

• DRAM: RAM động Data' Data

– Ô nhớ dùng transistor MOS và tụ để lƣu

trữ bít W

– Gọn nhẹ hơn SRAM

– Yêu cầu “Refresh” do tụ bị dò

DRAM

• Các ô nhớ của từ đƣợc “refresh” khi đọc

Data

– Tốc độ “refresh” thƣờng khoảng 15.625 W

microsec.

– Truy cập chậm hơn SRAM

17

Các biến thể của RAM

• PSRAM: RAM giả tĩnh

– DRAM với bộ điều khiển “refresh” tích hợp bên trong bộ nhớ

– Giá thấp và mật độ lƣu trữ cao hơn so với SRAM

• NVRAM: Nonvolatile RAM

– Lƣu trữ giữ liệu ngay cả khi không cấp nguồn

– RAM có nguồn dự phòng

• SRAM với battery đƣợc kết nối vĩnh cửu

• Ghi nhanh nhƣ đọc

• Không giới hạn số lần ghi

– SRAM với EEPROM hoặc flash

• Lƣu trữ toàn bộ nội dung của RAM trên EEPROM hoặc flash trƣớc khi ngắt

nguồn

18

Ví dụ:

Thiết bị HM6264 & 27C256 RAM/ROM

• Là thiết bị giá thấp, mật độ thấp

data

11-13, 15-19 11-13, 15-19 data

• Thƣờng dùng trong bộ hệ thống addr

2,23,21,24, 27,26,2,23,21, addr

25, 3-10 24,25, 3-10

nhúng dựa trên vi điều khiển 8- 22 /OE 22 /OE

bit 27 /WE 20 /CS

• Hai số đầu thể hiện kiểu thiết bị 20 /CS1

26 CS2 HM6264 27C256

– RAM: 62 block diagrams

Device Access Time (ns) Standby Pwr. (mW) Active Pwr. (mW) Vcc Voltage (V)

– ROM: 27 HM6264 85-100 .01 15 5

27C256 90 .5 100 5

• Các số tiếp theo biểu thị dung device characteristics

lƣợng tính theo kilobits Read operation Write operation

data data

addr addr

OE WE

/CS1 /CS1

CS2 CS2

timing diagrams

19

Ví dụ:

Thiết bị nhớ TC55V2325FF-100

data Device Access Time (ns) Standby Pwr. (mW) Active Pwr. (mW) Vcc Voltage (V)

• Thiệt bị nhớ SRAM 2- TC55V23 10 na 1200 3.3

megabit addr 25FF-100

addr device characteristics

• Thiết kế để giao tiếp /CS1

với bộ xử lý 32-bit /CS2 A single read operation

• Có khả năng đọc ghi CS3

CLK

/WE

tuần tự nhanh /ADSP

/OE

/ADSC

MODE

/ADV

/ADSP

addr

/ADSC /WE

/ADV /OE

CLK /CS1 and /CS2

TC55V2325F CS3

F-100

data

block diagram

timing diagram

20

Ghép bộ nhớ

• Kích thƣớc bộ nhớ yêu cầu thƣờng khác với kích thƣớc thiết Tăng số từ nhớ

kế của bộ nhớ 2m+1 × n ROM

• Khi bộ nhớ thiết kế sẵn lớn hơn yêu cầu, chúng ta chỉ cần bỏ 2m × n ROM

các địa chỉ nhớ ở vùng cao và đƣờng dữ liệu ở vùng cao A0

Am-1

• Khi bộ nhớ thiết kế sẵn nhỏ hơn yêu cầu, chúng ta cần ghép 1 × 2

A decoder

một vài bộ nhớ nhỏ hơn thành một bộ nhớ lớn m

m

– Kết nối kề nhau để tăng độ rộng từ nhớ 2 × n ROM

enable

– Kết nối tầng để tăng số từ

• Dùng các đƣờng địa chỉ vùng cao để lựa chọn bộ nhớ nhỏ

hơn sử dụng bộ giải mã

– Kết hợp cả hai khi cần tăng số từ cũng nhƣ độ rộng từ

Q Q

2m × 3n ROM n-1 0

enable 2m × n ROM 2m × n ROM 2m × n ROM A

Tăng độ rộng Tăng số từ cũng

A

từ nhớ 0 như độ rộng từ

Am nhớ

enable

Q3n-1 Q2n-1 Q0 outputs

21

Phân cấp bộ nhớ

• Chúng ta muốn bộ nhớ rẻ,

truy cập nhanh

• Bộ nhớ chính Processor

– Dùng bộ nhớ dung lƣợng Registers

lớn, rẻ, chậm để lƣu trữ toàn

Cache

bộ chƣơng trình và dữ liệu

• Cache Main memory

– Dùng bộ nhớ nhỏ, đắt tiền và Disk

nhanh để lƣu trữ phần

“copy” của phần dữ liệu truy Tape

cập thuộc bộ nhớ lớn

– Có thể có nhiều mức cache

22

Cache

• Thường được thiết kế dùng SRAM

– Nhanh hơn nhƣng đắt hơn DRAM

• Thường đặt trên cùng chip với bộ xử lý

– Không gian hạn chế, vì vậy có dung lƣợng nhỏ hơn nhiều so với bộ nhớ chính

bên ngoài chip

– Truy cập nhanh hơn (thƣờng là 1 chu kỳ đồng hồ so với vài chu kỳ đồng hồ so

với bộ nhớ ngoài)

• Một số thiết kế cache

– Bản đồ cache, cơ chế thay thế, và kỹ thuật ghi

23

RAM cải tiến

• DRAMs thƣờng đƣợc sử dụng nhƣ bộ nhớ chính trong bộ xử

lý của hệ thống nhúng

– Dung lƣợng lớn, giá thành thấp

• Các biến thể chính của DRAMs

– Cần tƣơng thích với tốc độ của bộ xử lý

– FPM DRAM: DRAM kiểu trang nhanh

– EDO DRAM: DRAM có đầu ra dữ liệu mở rộng

– SDRAM/ESDRAM: DRAM đồng bộ và đồng bộ mở rộng

24

DRAM cơ bản

• Bus địa chỉ ghép giữa

các phần tử hàng và cột

data Refresh

• Địa chỉ hàng và cột Circuit

. Buffer . Sense

đƣợc chốt, tuần tự, Buffer In Amplifiers

Addr Col Decoder

rd/wr Data cas

bằng các tín hiệu ras và Col

cas, tƣơng ứng clock ras,

Buffer

cas, cas,

Out Buffer Out

Addr. Addr.

ras Decoder Row

• Mạch “refresh” có thể Data

address Row

bên trong hoặc bên Bit storage array

ngoài DRAM

25

Vấn đề tích hợp DRAM

• SRAM dễ dàng tích hợp trên một chip nhƣ bộ xử lý

• DRAM khó hơn

– Sự khác biệt giữa thiết kế DRAM và mạch tổ hợp

– Mục tiêu của ngƣời thiết kế mạch tổ hợp:

• Giảm điện dung ký sinh để giảm trễ truyền lan và mức tiêu thụ công

suất

– Mục tiêu của ngƣời thiết kế DRAM:

• Tạo ra điện dung để lƣu trữ thông tin

– Quá trình tổ hợp gặp khó khăn

26

Đơn vị quản lý bộ nhớ (MMU)

• Chức năng của MMU

– Thực hiện “refresh” DRAM, giao tiếp bus và điều phối

– Thực hiện việc chia sẻ bộ nhớ

– Chuyển đổi địa chỉ nhớ từ bộ xử lý sang địa chỉ nhớ vật

lý của DRAM

• Các CPUs thƣờng có bộ MMU tích hợp sẵn

• Bộ xử lý chức năng đơn có thể sử dụng để xây

dựng MMU

27File đính kèm:

bai_giang_thiet_ke_he_thong_nhung_chuong_2_cau_truc_phan_cun.pdf

bai_giang_thiet_ke_he_thong_nhung_chuong_2_cau_truc_phan_cun.pdf