Bài giảng Kiến trúc máy tính - Chương 11: Bộ xử lý trung tâm - Nguyễn Thị Phương

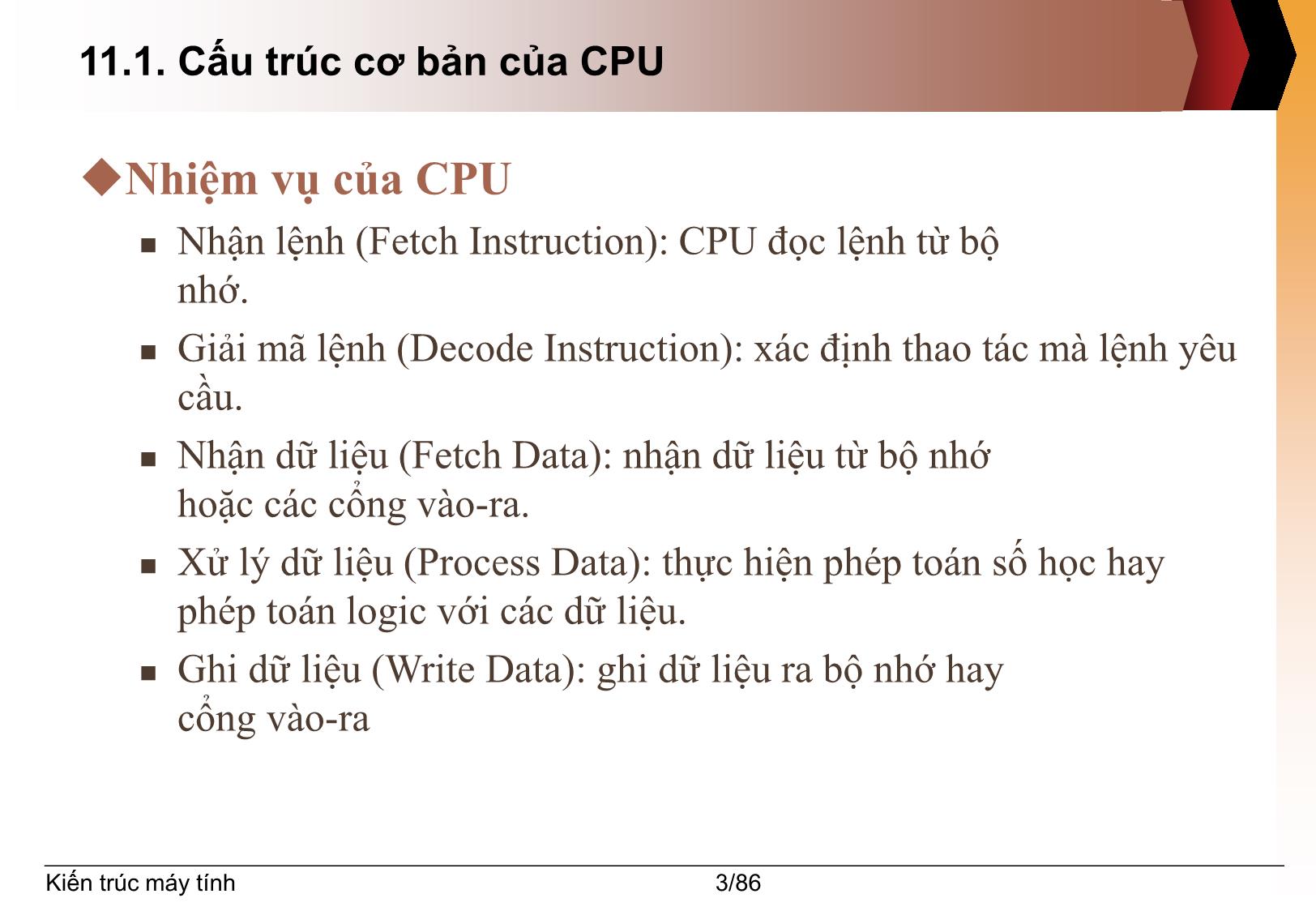

Nhiệm vụ của CPU

Nhận lệnh (Fetch Instruction): CPU đọc lệnh từ bộ

nhớ.

Giải mã lệnh (Decode Instruction): xác định thao tác mà lệnh yêu

cầu.

Nhận dữ liệu (Fetch Data): nhận dữ liệu từ bộ nhớ

hoặc các cổng vào-ra.

Xử lý dữ liệu (Process Data): thực hiện phép toán số học hay

phép toán logic với các dữ liệu.

Ghi dữ liệu (Write Data): ghi dữ liệu ra bộ nhớ hay

cổng vào-ra

Trang 1

Trang 2

Trang 3

Trang 4

Trang 5

Trang 6

Trang 7

Trang 8

Trang 9

Trang 10

Tải về để xem bản đầy đủ

Bạn đang xem 10 trang mẫu của tài liệu "Bài giảng Kiến trúc máy tính - Chương 11: Bộ xử lý trung tâm - Nguyễn Thị Phương", để tải tài liệu gốc về máy hãy click vào nút Download ở trên

Tóm tắt nội dung tài liệu: Bài giảng Kiến trúc máy tính - Chương 11: Bộ xử lý trung tâm - Nguyễn Thị Phương

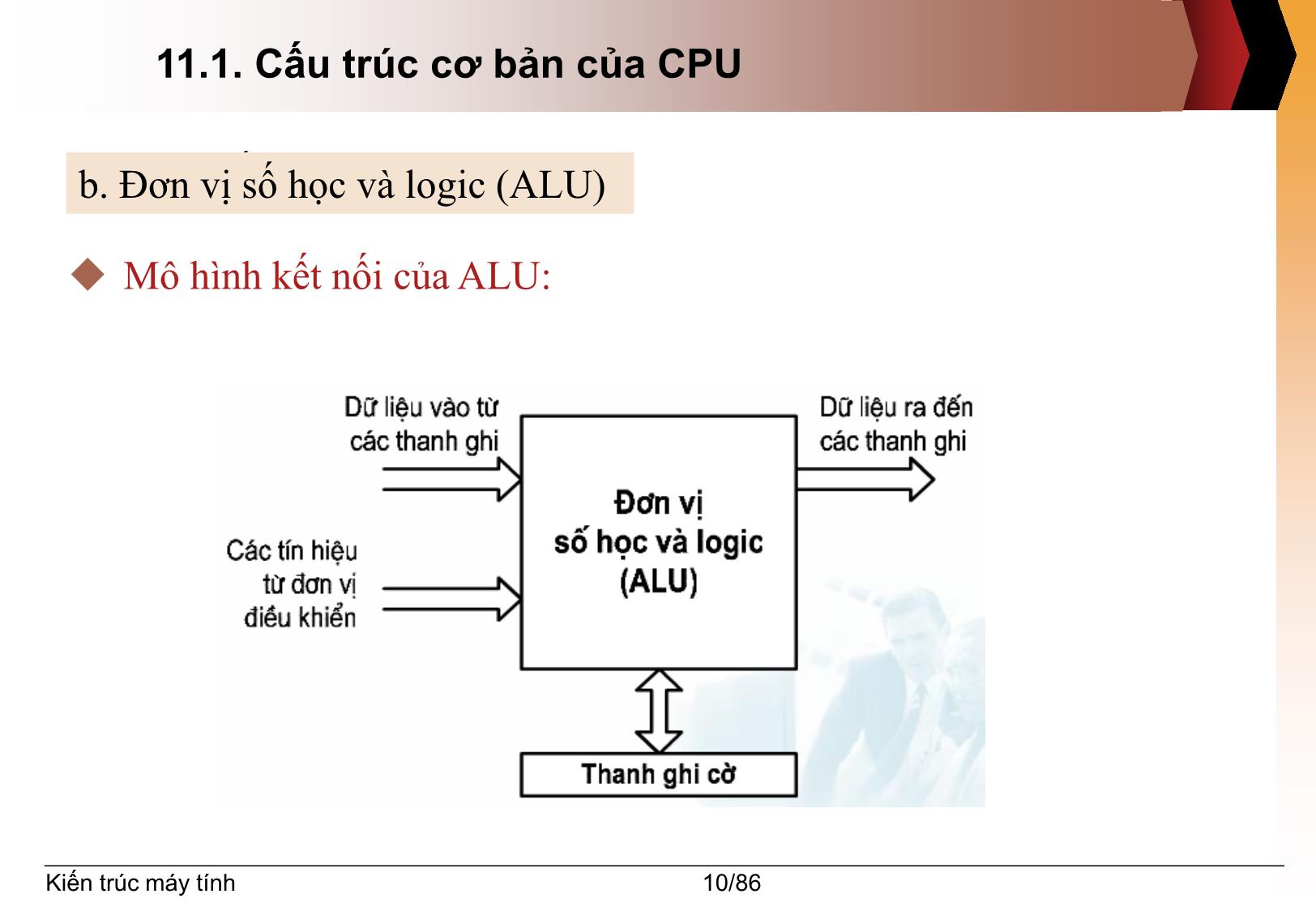

b.b. ĐơnĐơn vịvị số số học học và vàlogic logic (ALU) (ALU) Mô hình kết nối của ALU: Kiến trúc máy tính 10/86 11.1. Cấu trúc cơ bản của CPU c. Các thanh ghi Chức năng và đặc điểm: Tập hợp các thanh ghi nằm trong CPU Chứa các thông tin tạm thời phục vụ cho hoạt động ở thời điểm hiện tại của CPU Được coi là mức đầu tiên của hệ thống nhớ Tuỳ thuộc vào bộ xử lý cụ thể Số lượng thanh ghi nhiều tăng hiệu năng của CPU Có hai loại thanh ghi: Các thanh ghi lập trình được Các thanh ghi không lập trình được Kiến trúc máy tính 11/86 11.1. Cấu trúc cơ bản của CPU c. Các thanh ghi Các thanh ghi địa chỉ Bộ đếm chương trình (Program Counter – PC) Con trỏ dữ liệu (Data Pointer – DP) Con trỏ ngăn xếp (Stack Pointer – SP) Thanh ghi cơ sở và thanh ghi chỉ số (Base Register & Index Register) Các thanh ghi dữ liệu Thanh ghi trạng thái Kiến trúc máy tính 12/86 11.1. Cấu trúc cơ bản của CPU c. Các thanh ghi Thanh ghi PC Còn gọi là con trỏ lệnh (Instruction Pointer - IP) Là thanh ghi chứa địa chỉ của lệnh tiếp theo sẽ được nhận vào. Sau khi một lệnh được nhận vào thì nội dung của PC tự động tăng để trỏ sang lệnh kế tiếp nằm ngay sau lệnh vừa được nhận. Kiến trúc máy tính 13/86 11.1. Cấu trúc cơ bản của CPU c. Các thanh ghi Thanh ghi con trỏ dữ liệu (DP) Chứa địa chỉ của ngăn nhớ dữ liệu mà CPU muốn truy cập. Thường có một số thanh ghi con trỏ dữ liệu. Kiến trúc máy tính 14/86 11.1. Cấu trúc cơ bản của CPU c. Các thanh ghi Con trỏ ngăn xếp (SP) Ngăn xếp là vùng nhớ có cấu trúc SP chứa địa chỉ của ngăn nhớ đỉnh ngăn xếp LIFO (Last In - First Out) Khi cất một thông tin vào ngăn xếp: Ngăn xếp thường dùng để phục vụ Nội dung của SP tự động giảm cho chương trình con Thông tin được cất vào ngăn nhớ được trỏ bởi SP Đáy ngăn xếp là một ngăn nhớ xác Khi lấy một thông tin ra khỏi ngăn xếp: định Thông tin được đọc từ ngăn nhớ được trỏ bởi SP Đỉnh ngăn xếp là thông tin nằm ở Nội dung của SP tự động tăng vị trí trên cùng trong ngăn xếp Khi ngăn xếp rỗng, SP trỏ vào đáy Đỉnh ngăn xếp có thể bị thay đổi Kiến trúc máy tính 15/86 11.1. Cấu trúc cơ bản của CPU c. Các thanh ghi Minh họa hoạt động của SP Kiến trúc máy tính 16/86 11.1. Cấu trúc cơ bản của CPU c. Các thanh ghi Thanh ghi cơ sở và thanh ghi chỉ số Thanh ghi cơ sở: chứa địa chỉ của ngăn nhớ cơ sở (địa chỉ cơ sở). Thanh ghi chỉ số: chứa độ lệch địa chỉ giữa ngăn nhớ mà CPU cần truy cập so với ngăn nhớ cơ sở. Địa chỉ của ngăn nhớ cần truy cập = địa chỉ cơ sở + chỉ số Kiến trúc máy tính 17/86 11.1. Cấu trúc cơ bản của CPU c. Các thanh ghi Thanh ghi cơ sở và thanh ghi chỉ số Kiến trúc máy tính 18/86 11.1. Cấu trúc cơ bản của CPU c. Các thanh ghi Thanh ghi dữ liệu Chứa các dữ liệu tạm thời hoặc các kết quả trung gian phục vụ cho việc xử lý dữ liệu của CPU Cần có nhiều thanh ghi dữ liệu Các thanh ghi số nguyên: 8, 16, 32, 64 bit Các thanh ghi số dấu chấm động Kiến trúc máy tính 19/86 11.1. Cấu trúc cơ bản của CPU c. Các thanh ghi Thanh ghi trạng thái Còn gọi là thanh ghi cờ (Flag Register) Chứa các thông tin trạng thái của CPU Các cờ phép toán: biểu thị trạng thái của kết quả phép toán Các cờ điều khiển: điều khiển chế độ làm việc của CPU Kiến trúc máy tính 20/86 11.1. Cấu trúc cơ bản của CPU Ví dụ cờ phép toán Cờ Zero (ZF - cờ rỗng): được thiết lập lên 1 khi kết quả của phép toán vừa thực hiện xong bằng 0. Cờ Sign (SF - cờ dấu): được thiết lập lên 1 khi kết quả của phép toán vừa thực hiện nhỏ hơn 0, hay nói cách khác, cờ Sign nhận giá trị bằng bit dấu của kết quả. Cờ Carry (CF - cờ nhớ): được thiết lập lên 1 nếu phép toán xảy ra hiện tượng carry-out. Cờ Overflow (OF - cờ tràn): được thiết lập lên 1 nếu phép toán xảy ra hiện tượng overflow. Kiến trúc máy tính 21/86 11.2. Các chế độ địa chỉ a. Chế độ địa chỉ tức thì b. Chế độ địa chỉ trực tiếp c. Chế độ địa chỉ gián tiếp d. Chế độ địa chỉ thanh ghi e. Chế độ địa chỉ thanh ghi gián tiếp f. Chế độ địa chỉ dịch chuyển g. Chế độ địa chỉ ngăn xếp Các chế độ định địa chỉ cơ bản a. Định địa chỉ tức thì Dạng đơn giản nhất của định địa chỉ Toán hạng = A Chế độ này có thể được sử dụng để định nghĩa và sử dụng các hằng số và thiết lập các giá trị ban đầu của biến Các số thường được lưu trữ dưới dạng số bù Bit ngoài cùng bên trái của trường toán hạng được sử dụng như bit dấu Ưu điểm: Chỉ cần truy xuất bộ nhớ một lần (để lấy lệnh), do vậy tiết kiệm một chu kỳ cache hoặc bộ nhớ trong chu kỳ lệnh. Nhược điểm: Kích thước của số bị giới hạn bởi kích thước của trường địa chỉ vì thông thường kích thước của trường này nhỏ hơn kích thước từ b. Định địa chỉ trực tiếp Trường địa chỉ chứa địa chỉ hiệu dụng của toán hạng Địa chỉ hiệu dụng (Effective address (EA)) = trường địa chỉ (Address field (A)) Phổ biến trong các thế hệ máy tính trước đây Tham chiếu bộ nhớ một lần để lấy dữ liệu toán hạng Hạn chế: chỉ cung cấp một không gian địa chỉ hạn chế c. Định địa chỉ gián tiếp Tham chiếu đến địa chỉ của một từ trong bộ nhớ chứa địa chỉ đầy đủ của toán hạng EA = (A) Dấu ngoặc đơn được hiểu như là nội dung của Ưu điểm: Với một từ có kích thước N cho phép một không gian địa chỉ là 2N Nhược điểm: Thực thi câu lệnh đòi hỏi hai lần tham chiếu bộ nhớ để truy xuất hoạt động: một để lấy ra địa chỉ, hai là để lấy ra giá trị của nó Một biến thể hiếm gặp của địa chỉ gián tiếp là địa chỉ gián tiếp nhiều cấp hoặc nhiều tầng EA = ( . . . (A) . . . ) Nhược điểm là cần ba hoặc nhiều hơn tham chiếu bộ nhớ để truy xuất toán hạng d. Định địa chỉ thanh ghi Trường địa chỉ dùng để tham chiếu thanh ghi chứ không phải địa chỉ bộ nhớ chính EA = R Ưu điểm: Chỉ cần một trường địa chỉ nhỏ trong lệnh (do số lượng thanh ghi ít) Không cần tham chiếu bộ nhớ (tốn nhiều thời gian) Nhược điểm: Không gian địa chỉ giới hạn e. Định địa chỉ gián tiếp thanh ghi Tương tự như địa chỉ gián tiếp, sự khác biệt duy nhất là trường địa chỉ tham chiếu đến thanh ghi EA = (R) Không gian địa chỉ lớn hơn (trường địa chỉ tham chiếu đến vị trí chứa địa chỉ có độ dài bằng một từ ) Tham chiếu bộ nhớ ít hơn định địa chỉ gián tiếp f. Định địa chỉ dịch chuyển - Displacement Addressing Kết hợp chế độ định địa chỉ trực tiếp và định địa chỉ trực tiếp thanh ghi EA = A + (R) Yêu cầu lệnh phải có hai trường địa chỉ, ít nhất một trong hai phải có giá trị cụ thể Một giá trị trong một trường địa chỉ (giá trị = A) được sử dụng trực tiếp Một trường địa chỉ khác tham chiếu đến thanh ghi trong đó nội dung được cộng với A để tạo ra địa chỉ hiệu dụng Hầu hết sử dụng: Định địa chỉ tương đối Định địa chỉ thanh ghi cơ sở Định địa chỉ chỉ mục 11.3. Hoạt động của CPU a. Chu kỳ lệnh Bao gồm các công đoạn chính sau đây: Truy xuất lệnh Giải mã lệnh Nhận toán hạng Thực hiện lệnh Cất toán hạng Ngắt Kiến trúc máy tính 30/86 11.3. Hoạt động của CPU Giản đồ trạng thái chu kỳ lệnh Kiến trúc máy tính 31/86 11.3. Hoạt động của CPU Truy xuất lệnh CPU đưa địa chỉ của lệnh cần nhận từ thanh ghi bộ đếm chương trình PC ra bus địa chỉ CPU phát tín hiệu điều khiển đọc bộ nhớ Lệnh từ bộ nhớ được đặt lên bus dữ liệu và được CPU copy vào trong thanh ghi lệnh IR CPU tăng nội dung của PC để trỏ sang lệnh kế tiếp Kiến trúc máy tính 32/86 11.3. Hoạt động của CPU Minh họa quá trình truy xuất lệnh Kiến trúc máy tính 33/86 C4.CPU 11.3. Hoạt động của CPU Giải mã lệnh Lệnh từ thanh ghi lệnh IR được đưa đến đơn vị điều khiển Đơn vị điều khiển tiến hành giải mã lệnh để xác định thao tác cần phải thực hiện Nhận toán hạng CPU đưa địa chỉ của toán hạng ra bus địa chỉ CPU phát tín hiệu điều khiển đọc Toán hạng được chuyển vào trong CPU Kiến trúc máy tính 34/86 11.3. Hoạt động của CPU Nhận toán hạng gián tiếp CPU đưa địa chỉ ra bus địa chỉ CPU phát tín hiệu điều khiển đọc Nội dung ngăn nhớ được chuyển vào CPU, đó chính là địa chỉ của toán hạng CPU phát địa chỉ này ra bus địa chỉ CPU phát tín hiệu điều khiển đọc Nội dung của toán hạng được chuyển vào CPU Kiến trúc máy tính 35/86 11.3. Hoạt động của CPU Minh họa nhận toán hạng gián tiếp Kiến trúc máy tính 36/86 11.3. Hoạt động của CPU Thực thi lệnh Có nhiều dạng thao tác tùy thuộc vào lệnh Có thể là: Đọc/ghi bộ nhớ Vào-ra dữ liệu Chuyển dữ liệu giữa các thanh ghi Thực hiện phép toán số học hoặc logic Truyền điều khiển (rẽ nhánh) Kiến trúc máy tính 37/86 C4.CPU 11.3. Hoạt động của CPU GhiGhi toántoán hạng hạng CPU đưa địa chỉ ra bus địa chỉ CPU đưa dữ liệu cần ghi ra bus dữ liệu CPU phát tín hiệu điều khiển ghi Dữ liệu trên bus dữ liệu được copy đến vị trí xác định Kiến trúc máy tính 38/86 11.3. Hoạt động của CPU Minh họa quá trình ghi toán hạng Kiến trúc máy tính 39/86 11.3. Hoạt động của CPU Ngắt CPU lưu lại giá trị hiện tại của PC (là địa chỉ trở về sau khi hoàn thành ngắt) – thường lưu vào Stack: CPU đưa nội dung của PC ra bus dữ liệu CPU đưa địa chỉ (thường được xác định từ con trỏ ngăn xếp SP) ra bus địa chỉ CPU phát tín hiệu điều khiển ghi bộ nhớ Địa chỉ trở về (nội dung của PC) trên bus dữ liệu được lưu vào ngăn nhớ tương ứng ở ngăn xếp CPU nạp vào PC địa chỉ lệnh đầu tiên của chương trình con phục vụ ngắt tương ứng: CPU xác định địa chỉ của vector ngắt tương ứng CPU phát địa chỉ này ra bus địa chỉ CPU phát tín hiệu điều khiển đọc bộ nhớ Giá trị của vector ngắt (địa chỉ lệnh đầu tiên của CTC phục vụ ngắt) được chuyển ra bus dữ liệu Giá trị này được nạp vào trong PC Kiến trúc máy tính 40/86 11.3. Hoạt động của CPU b. Đường ống lệnh Nguyên tắc của Pipeline: chia chu trình lệnh thành các công đoạn và cho phép thực hiện gối lên nhau theo kiểu dây chuyền. Giả sử chu trình lệnh gồm 6 công đoạn với thời gian thực hiện như nhau (T): Truy xuất lệnh (Fetch Instruction – FI) Giải mã lệnh (Decode Instruction – DI) Tính địa chỉ toán hạng (Calculate Operand Address – CO) Nhận toán hạng (Fetch Operands – FO) Thực hiện lệnh (Execute Instruction – EI) Ghi toán hạng (Write Operands – WO) Kiến trúc máy tính 41/86 11.3. Hoạt động của CPU b. Đường ống lệnh Biểu đồ thời gian của đường ống lệnh Kiến trúc máy tính 42/86 11.3. Hoạt động của CPU b. Đường ống lệnh Các xung đột của đường ống lệnh Xung đột cấu trúc: do nhiều công đoạn dùng chung một tài nguyên (thêm các bộ phận chức năng cần thiết và hữu hiệu) Xung đột dữ liệu: lệnh sau sử dụng kết quả của lệnh trước (một bộ phận phần cứng được dùng để đưa kết quả từ ngõ ra ALU trực tiếp vào một trong các thanh ghi ngõ vào) Xung đột điều khiển: do rẽ nhánh gây ra (đóng băng kỹ thuật ống dẫn trong một chu kỳ) Kiến trúc máy tính 43/86 11.4. Các kỹ thuật tiên tiến của bộ xử lý a. Cấu trúc chung của các bộ xử lý tiên tiến b. Các kiến trúc song song mức lệnh c. Kiến trúc RISC Kiến trúc máy tính 44/86 11.4. Các kỹ thuật tiên tiến của bộ xử lý a. Cấu trúc chung của các BXL tiên tiến Kiến trúc máy tính 45/86 11.4. Các kỹ thuật tiên tiến của bộ xử lý Các đơn vị xử lý dữ liệu Các đơn vị số nguyên (Integer Unit – IU) Các đơn vị số dấu chấm động (Floating Point Unit – FPU) Các đơn vị chức năng đặc biệt: Đơn vị xử lý dữ liệu âm thanh Đơn vị xử lý dữ liệu hình ảnh Đơn vị xử lý dữ liệu vector Kiến trúc máy tính 46/86 11.4. Các kỹ thuật tiên tiến của bộ xử lý Bộ nhớ cache Được tích hợp trên chip vi xử lý Thường bao gồm 2 mức Cache: Cache L1 gồm 2 phần tách rời: Cache lệnh Cache dữ liệu → giải quyết xung đột khi nhận lệnh và dữ liệu Cache L2: dùng chung cho lệnh và dữ liệu Kiến trúc máy tính 47/86 11.4. Các kỹ thuật tiên tiến của bộ xử lý Đơn vị quản lý bộ nhớ Chuyển đổi địa chỉ ảo thành địa chỉ vật lý Cung cấp cơ chế phân trang hoặc phân đoạn Cung cấp chế độ bảo vệ bộ nhớ Kiến trúc máy tính 48/86 11.4. Các kỹ thuật tiên tiến của bộ xử lý b. Kiến trúc song song mức lệnh Siêu đường ống (Superpipeline và Hyperpipeline) Siêu vô hướng (Superscalar) Từ lệnh dài – VLIW (Very Long Instruction Word) Kiến trúc máy tính 49/86 11.4. Các kỹ thuật tiên tiến của bộ xử lý Kiến trúc máy tính 50/86 11.4. Các kỹ thuật tiên tiến của bộ xử lý VLIW (Very Long Instruction Word) Kiến trúc máy tính 51/86 11.4. Các kỹ thuật tiên tiến của bộ xử lý c. Kiến trúc RISC CISC và RISC: CISC – Complex Instruction Set Computer: Máy tính có tập lệnh phức tạp VD: các bộ xử lý 80x86 ... RISC – Reduced Instruction Set Computer: Máy tính có tập lệnh rút gọn VD: các bộ xử lý Sun SPARC, Power PC, ... Kiến trúc máy tính 52/86 11.4. Các kỹ thuật tiên tiến của bộ xử lý Các đặc trưng của RISC Số lượng lệnh ít Các lệnh có thời gian thực hiện là 1 chu kỳ máy Độ dài của các lệnh bằng nhau (32 bit) Có ít khuôn dạng lệnh (≤ 4) Có ít chế độ địa chỉ hóa toán hạng (≤ 4) Có nhiều thanh ghi Các lệnh chủ yếu là thao tác giữa thanh ghi với thanh ghi Truy cập bộ nhớ thông qua 2 lệnh LOAD và STORE Kiến trúc máy tính 53/86 11.5. Kiến trúc Intel Các bộ xử lý 4 bit: 4004, 4040 Các bộ xử lý 8 bit: 8008, 8080, 8085 Các bộ xử lý 16 bit: 8086, 8088, 80186, 80188, 80286 Các bộ xử lý 32 bit: họ 80386, 80486, các họ Pentium I, II, III, 4 Các bộ xử lý 64 bit: Itanium, Itanium 2, Pentium D, Xeon, Intel Core 2 Kiến trúc máy tính 54/86 11.5. Kiến trúc Intel a. Kiến trúc 16 bit (IA-16) Các thanh ghi bên trong: 16 bit Xử lý phép toán số nguyên với 16 bit Quản lý bộ nhớ theo đoạn 64KB Là kiến trúc mở đầu cho dòng máy tính IBM-PC Kiến trúc máy tính 55/86 11.4. Các kỹ thuật tiên tiến của bộ xử lý b. Kiến trúc 32 bit (IA-32) Các thanh ghi bên trong: 32 bit Xử lý phép toán số nguyên với 32 bit Có 3 chế độ làm việc: Chế độ 8086 thực (Real 8086 mode): làm việc như 1 bộ xử lý 8086 Chế độ 8086 ảo (Virtual mode): làm việc như nhiều bộ xử lý 8086 (đa nhiệm 16-bit) Chế độ bảo vệ (Protected mode): Đa nhiệm 32 bit Quản lý bộ nhớ ảo Xử lý các phép toán số dấu chấm động (từ 80486) Kiến trúc máy tính 56/86 11.4. Các kỹ thuật tiên tiến của bộ xử lý c. Kiến trúc 64 bit (IA-64) Các thanh ghi bên trong: 64 bit Xử lý phép toán số nguyên với 64 bit Xử lý các phép toán số dấu chấm động Không tương thích phần cứng với các bộ phận trước đó Tương thích phần mềm bằng cách giả lập môi trường Kiến trúc máy tính 57/86

File đính kèm:

bai_giang_kien_truc_may_tinh_chuong_11_bo_xu_ly_trung_tam_ng.pdf

bai_giang_kien_truc_may_tinh_chuong_11_bo_xu_ly_trung_tam_ng.pdf