Bài giảng Kiến trúc máy tính - Bài 7: Ghép nối máy tính với thiết bị ngoại vi - Phan Thanh Toàn

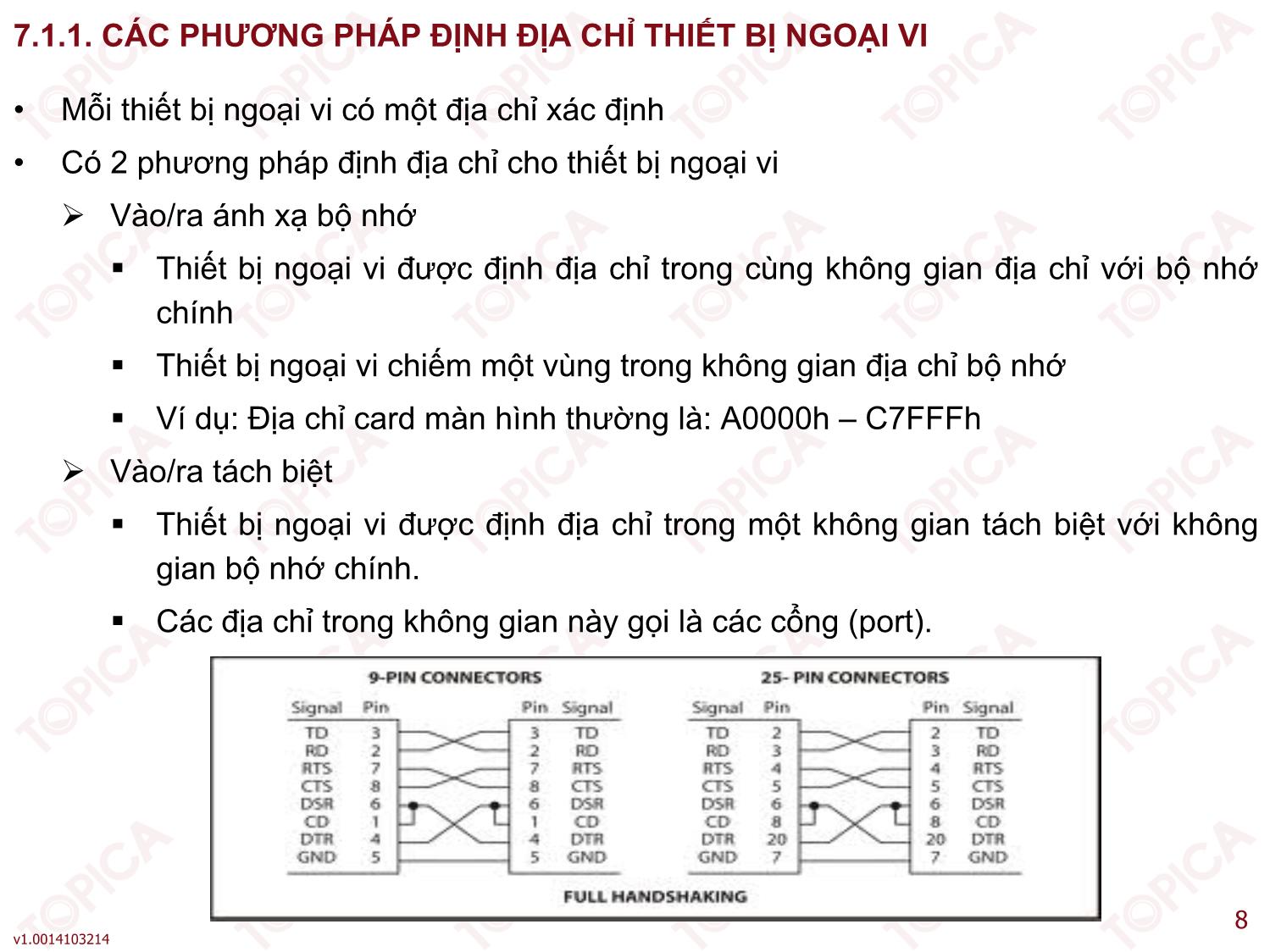

Mỗi thiết bị ngoại vi có một địa chỉ xác định

• Có 2 phương pháp định địa chỉ cho thiết bị ngoại vi

Vào/ra ánh xạ bộ nhớ

Thiết bị ngoại vi được định địa chỉ trong cùng không gian địa chỉ với bộ nhớ

chính

Thiết bị ngoại vi chiếm một vùng trong không gian địa chỉ bộ nhớ

Ví dụ: Địa chỉ card màn hình thường là: A0000h – C7FFFh

Vào/ra tách biệt

Thiết bị ngoại vi được định địa chỉ trong một không gian tách biệt với không

gian bộ nhớ chính.

Các địa chỉ trong không gian này gọi là các cổng (port)

Trang 1

Trang 2

Trang 3

Trang 4

Trang 5

Trang 6

Trang 7

Trang 8

Trang 9

Trang 10

Tải về để xem bản đầy đủ

Bạn đang xem 10 trang mẫu của tài liệu "Bài giảng Kiến trúc máy tính - Bài 7: Ghép nối máy tính với thiết bị ngoại vi - Phan Thanh Toàn", để tải tài liệu gốc về máy hãy click vào nút Download ở trên

Tóm tắt nội dung tài liệu: Bài giảng Kiến trúc máy tính - Bài 7: Ghép nối máy tính với thiết bị ngoại vi - Phan Thanh Toàn

ền dữ liệu dạng bit nối tiếp • Truyền nối tiếp thường có 2 dạng: Truyền đồng bộ: Ngoài đường truyền tín hiệu số liệu sử dụng thêm một đường tín hiệu đồng bộ để chỉ thị khi nào bit tiếp theo ổn định trên đường truyền. Truyền không đồng bộ: Không sử dụng đường tín hiệu đồng bộ, bit dữ liệu chứa thêm các thông tin đồng bộ; Sử dụng bit start và stop để chỉ thị sự bắt đầu và kết thúc của khối dữ liệu được truyền; Sử dụng các bit chẵn lẻ để phát hiện lỗi khi truyền. 7.2.2. CỔNG NỐI TIẾP COM 20 v1.0014103214 7.2.2. CỔNG NỐI TIẾP COM • Chuẩn ghép nối nối tiếp RS-232C: Thiết kế theo chuẩn của EIA (Electronic Industries Association); Chuẩn qui định về cách thức truyền số liệu giữa DTE (Data Terminal Equipment) và DCE (Data Communication Equipment); Mức logic cao (mức 1): Điện thế từ -3V đến -15V; Mức logic thấp (mức 0): Điện thế từ +3V đến + 15V; Có 3 phương thức truyền: Đơn công: Dữ liệu truyền theo 1 chiều; Bán song công: Số liệu gửi theo 2 chiều, tại một thời điểm chỉ truyền theo 1 chiều; Song công: Số liệu truyền đồng thời theo 2 chiều. 21 v1.0014103214 • Chuẩn ghép nối nối tiếp RS-232C: Khuôn dạng dữ liệu truyền theo chuẩn RS-232C: 1 bit start, mức logic thấp, điện thế dương; 1 hoặc 1.5 hoặc 2 bit stop, mức logic cao, điện thế âm; 1 bit kiểm tra chẵn lẻ; 5,6 hoặc 7 bit số liệu; Dữ liệu trên đường truyền chỉ ở 1 trong 2 trạng thái: đánh dấu (MARK) hoặc trống (SPACE) tương ứng với trạng thái điện thế âm hoặc dương. 7.2.2. CỔNG NỐI TIẾP COM (tiếp theo) 22 v1.0014103214 7.2.2. CỔNG NỐI TIẾP COM (tiếp theo) Chân số Tên Kí hiệu Chức năng D-25 D-9 1 Frame ground FG Nối với vỏ bọc kim của cáp dẫn hoặc đất 2 3 Transmit data TxD Số liệu được phát từ DTE tới DCE 3 2 Receive Data RxD Số liệu được thu từ DCE vào DTE 4 7 Request To Send RTS DTE đặt đường này ở mức tích cực khi nó sẵn sàng phát số liệu 5 8 Clear To Send CTS DCE đặt đường này ở mức tích cực để thông tin cho DTE rằng nó sẵn sàng nhận số liệu 6 6 Data Set Ready DSR Chức năng tương tự CTS nhưng được kích hoạt bởi DTE khi nó sẵn sàng nhận số liệu Tốc độ truyền: 20.000 baud, hoặc: 115.200 baud Chiều dài: 17 – 20 m 23 v1.0014103214 Chân số Tên Kí hiệu Chức năng D-25 D-9 20 4 Data Terminal Ready DTR Chức năng tương tự như RTS nhưng được kích hoạt bởi DCE khi nó muốn phát số liệu. 8 1 Data Carrier Detect DCD DCE đặt đường này ở mức tích cực để báo DTE biết là đã thiết lập được liên kết với DCE. 22 9 Ring Indicator RI DCE báo với DTE có một cuộc gọi từ xa gọi đến. 7 5 Signal Ground SG GND 7.2.2. CỔNG NỐI TIẾP COM (tiếp theo) 24 v1.0014103214 7.2.2. CỔNG NỐI TIẾP COM (tiếp theo) • Thâm nhập cổng nối tiếp COM qua DOS và BIOS Sử dụng lệnh mode của dos để thiết lập các thông số cho cổng COM; MODE COM2:2400, E, 8, 1; Thiết lập thông số COM2: tốc độ 2400 baund, bit chẵn lẻ chẵn, 8 bit dữ liệu, 1 bit stop; Sử dụng ngắt 21 của DOS để phát và thu dữ liệu; Hàm 03h: Đọc kí tự từ COM; Hàm 04h: Phát kí tự ra cổng COM; Hàm 3Fh: Đọc một file qua cổng COM; Hàm 40h: Viết một file qua cổng COM. 25 v1.0014103214 • Chip UART 8250 điều khiển cổng nối tiếp UART điều khiển quá trình phát, thu tín hiệu qua cổng COM. Biến đổi dữ liệu song song trên máy tính thành dòng bit nối tiếp và ngược lại. Đặc tính UART: Làm việc ở chế độ đồng bộ, dị bộ và lai; Chế độ đồng bộ: làm việc với kí tự 6, 7, 8 bit. Có sử dụng bit chẵn lẻ; Chế độ không đồng bộ: làm việc với kí tự 6,7,8 bit. Thêm 1 bit start, 1,5/2 bit stop; Tốc độ truyền: 9600bps. 7.2.2. CỔNG NỐI TIẾP COM (tiếp theo) 26 v1.0014103214 7.2.2. CỔNG NỐI TIẾP COM (tiếp theo) 27 v1.0014103214 • D0-D7: Bus số liệu; • RCLK: Lối vào xung đồng hồ; • SIN: Lối vào số liệu nối tiếp; • SOUT: Lối ra số liệu nối tiếp; • CS0, CS1, CS2: Chọn chíp; • : Lối ra xung nhịp; • , DOUTS: Cho phép CPU viết số liệu hoặc từ điều khiển vào các thanh ghi trong UART; • XTAL1, XTAL2: Lối vào từ bộ tạo dao động thạch anh; • , DINS: Cho phép CPU đọc số liệu hoặc từ điều khiển từ các thanh ghi trong UART; • DDIS: CPU đang đọc số liệu từ UART; • CSOUT: CPU đã chọn UART; • : Tín hiệu địa chỉ và các tín hiệu chọn chíp đã ổn định. BAUDOUT DOUTS DINS AS 7.2.2. CỔNG NỐI TIẾP COM (tiếp theo) 28 v1.0014103214 7.2.2. CỔNG NỐI TIẾP COM (tiếp theo) • A0-A2: Tín hiệu chọn địa chỉ hoặc thanh ghi, xác định thanh ghi nào CPU đang thâm nhập; • INTR: CPU nâng mức cao nếu phát hiện có một điều kiện ngắt; • : Cho phép ngắt; • : Cho người sử dụng; • MR: Reset các thanh ghi của UART; • : Báo đang có ngoại vi tìm cách truy cập cổng qua đường điện thoại; • Vcc: Nguồn; • GND: Đất. 2OUT 1OUT 1R 29 v1.0014103214 • Các thanh ghi và chương trình với 8250 8250 có 10 thanh ghi trạng thái và điều khiển; Địa chỉ cơ sở và ngắt IRQ như sau: Hai thanh ghi số liệu thu và phát (offset: 00h): Số liệu truyền vào chân SIN, chuyển thành byte và byte này được chuyển vào thanh ghi đệm thu. Cổng Địa chỉ cơ sở Ngắt COM1 3F8h IRQ4 COM2 2F8h IRQ3 COM3 3E8h IRQ4 COM4 2E8h IRQ3 7.2.2. CỔNG NỐI TIẾP COM (tiếp theo) 30 v1.0014103214 7.2.2. CỔNG NỐI TIẾP COM (tiếp theo) Thanh ghi cho phép ngắt (offset: 01h) SINP = 1: UART phát ra một yêu cầu ngắt khi một trong các lối vào CTS, DSR, DCD hoặc RI của cổng COM thay đổi trạng thái; ERBK = 1: Phát ngắt nếu bộ thu phát hiện có lỗi chẵn lẻ, lỗi điểm dừng, lỗi khung truyền; TBE = 1: Phát yêu cầu ngắt nếu byte số liệu cần truyền đã được chuyển từ thanh ghi đệm phát tới thanh ghi dịch phát (bộ đệm phát đã rỗng, có thể truyền byte tiếp); RxRD = 1: Phát một ngắt ngay sau khi một byte số liệu có sẵn trong thanh ghi đệm thu. 07 TBE000 RxRDERBKSINP0 31 v1.0014103214 Thanh ghi nhận diện ngắt (offset: 02h) ID1, ID0: Các bit nhận diện; 00: Có sự thay đổi tín hiệu vào cổng COM; 01: Bộ đệm phát rỗng; 10: Số liệu đã được thu; 11: Lỗi truyền nối tiếp hoặc xảy ra điểm ngắt dữ liệu; PNP = 1 - không có ngắt, PNP = 0 - đang có ngắt. 07 ID0000 PNPID100 7.2.2. CỔNG NỐI TIẾP COM (tiếp theo) 32 v1.0014103214 7.2.2. CỔNG NỐI TIẾP COM (tiếp theo) Thanh ghi định dạng dữ liệu (offset: 03h) DAB = 1: Cho phép thâm nhập thanh ghi chốt số, =0 thâm nhập thanh ghi thu, phát và thanh ghi cho phép ngắt; BRK = 1: Tín hiệu ở lối ra SOUT luôn ở trạng thái ngắt, BRK = 0: Số liệu được cấp ra SOUT; PAR2, PAR1, PAR0: Loại bit chẵn lẻ; 000: Không có, 001: Chẵn lẻ lẻ, 011: Chẵn lẻ chẵn, 101: Luôn bằng 1(mark), 111: Luôn bằng 0 (space); STOP: Số bit stop, 0: 1 bit stop, 1: 2 bit stop; DAB1, DAB0: Số bit số liệu, 00: 5 bit, 01: 6 bit, 10: 7 bit, 11: 8 bit. DAB1PAR1PAR2BRK DAB0STOPPAR0DLAB 07 33 v1.0014103214 7.2.2. CỔNG NỐI TIẾP COM (tiếp theo) Thanh ghi trạng thái modem (offset: 04h) LOOP: Kiểm tra vòng lặp phản hổi của UART; LOOP = 0: Hoạt động ở chế độ; LOOP = 1: Lối ra 4 của RS-232X sẽ được nối với các lối vào như sau: RTS nối với CTS, DTR nối với DSR, OUT1 với R1, OUT2 với DC; OUT1, OUT2, RTS, DTR cho phép điều khiển mức logic các lối ra tương ứng của UART. Nếu các bit được đặt bằng 1 sẽ cho tín hiệu lối ra tương ứng ở mức thấp và ngược lại nếu được xóa sẽ cho tín hiệu lối ra tương ứng ở mức cao. 07 RSTLOOP00 DTROUT1OUT20 34 v1.0014103214 7.2.2. CỔNG NỐI TIẾP COM (tiếp theo) Thanh ghi trạng thái đường truyền (offset: 05h) TXE: Các thanh ghi phát; TXE = 1: Không có byte nào trong các thanh ghi đệm và dịch phát, TXE = 0: Có byte trong thanh ghi đệm và dịch phát; TBE: Thanh ghi đệm giữ số liệu, TBE = 1: Không có byte nào trong thanh ghi đệm phát, TBE = 0: Có 1 byte; BREK: Điểm ngắt dữ liệu, BREK = 1: Phát hiện có điểm ngắt trong dòng dữ liệu, BREK = 0: Không có; FRME: Lỗi khung truyền, =1: Có lỗi, =0: Không có lỗi; PARE: Lỗi chẵn lẻ, =1: Có lỗi, =0: Không có lỗi; OVRE: Lỗi tràn dữ liệu, =1: Có lỗi, =0: Không có lỗi; RxRD: Số liệu sẵn sàng, =1: Số liệu thu có sẵn trong bộ đệm, =0: Không có. 07 OVRREBREKTBETXE RxRDPAREFRME0 35 v1.0014103214 7.3.1. Điều chế tín hiệu trong modem 7.3.2. Các chuẩn modem 7.3. MODEM 36 v1.0014103214 • Dải thông đường điện thoại: 2400Hz. • Tốc độ điều chế cho truyền bán song công tối đa: 1200bps. • Có 3 dạng điều chế: Điều chế biên độ ASK, điều chế tần số FSK, điều chế pha FSK. • Chuẩn Bell 103A, điều chế tốc độ 300 baund FSK: Tần số 2.025Hz cho mức 0, 2.225Hz cho mức 1 cho một hướng và 1.070Hz cho mức 0, 1.270Hz cho mức 1 cho một hướng còn lại. • Điều chế pha vi sai sử dụng sóng mang hình sin có tần số không đổi cỡ: 1700Hz được dịch đi 1800 để biểu diễn cho một sự thay đổi số liệu từ 1 tới 0 hoặc từ 0 tới 1. 7.3.1. ĐIỀU CHẾ TÍN HIỆU TRONG MODEM 37 v1.0014103214 • Chuẩn modem CCITT CCITT Mô tả V.21 Song công, tốc độ phát 300pbs V.22 Bán song công, tốc độ phát 600pbs và 1200pbs V.22bits Song công, tốc độ phát 1200pbs và 2400pbs V.23 Song công, tốc độ phát 1200pbs, thu 75pbs V.24 Chuẩn CCITT cho ghép nối RS-232 V.32 Song công, tốc độ phát 4800pbs và 9600pbs V.25bits Ngôn ngữ lệnh modem V.32bits Song công, phát ở 7200pbs, 12000pbs và 14400pbs V.42 Giao thức điều khiển lỗi 7.3.2. CÁC CHUẨN MODEM 38 v1.0014103214 7.4.1. Cấu tạo vào nguyên tắc hoạt động 7.4.2. Thâm nhập bàn phím trực tiếp qua cổng vào/ra 7.4. BÀN PHÍM 39 v1.0014103214 • Bàn phím là một ma trận quét (bao gồm các đường dây dẫn ngang và dọc). • Các điểm giao cắt đặt các công tắc (phím bấm). • Khi nhấn hay nhả phím một mã 8 bit được gửi về bộ VXL (mã quét). • Khi nhấn phím tạo ra mã từ 01h – E0h (mã make-code). • Khi nhả phím mã được cộng thêm 80h (mã break-code). • Ví dụ: Nhấn phím Z phát ra mã quét: 2Ch, khi nhả phím phát ra mã Ach. 7.4.1. CẤU TẠO VÀ NGUYÊN TẮC HOẠT ĐỘNG 40 v1.0014103214 7.4.1. CẤU TẠO VÀ NGUYÊN TẮC HOẠT ĐỘNG • Cấu trúc khung truyền số liệu bàn phím STRT: Bit start (luôn bằng 0); DB0-DB7: 8 bit số liệu; PAR: Bit chẵn lẻ; STOP: Bit stop (luôn bằng 1). STRT DB0 DB1 DB2 DB3 DB4 DB5 DB6 DB7 PAR STOP 0 10 41 v1.0014103214 • Bàn phím là thiết bị ngoại vi có thể truy nhập qua cổng vào/ra. • Địa chỉ cổng bàn phím: 60h, 64h. • Thanh ghi trạng thái xác định trạng thái hiện tại của bộ điều khiển bàn phím. PARE: Lỗi chẵn lẻ của byte cuối cùng được đưa vào từ bàn phím, 1: Có lối, 0: Không có; TIM: Lỗi quá thời gian, 1: Có lỗi, 0: Không có; AUXB: đệm ra cho thiết bị phụ, 1: Giữ số liệu cho thiết bị, 0: Giữ cho bàn phím; KEYL: Trạng thái khóa bàn phím, 1: Không khóa, 0: Khóa; C/D: Lệnh/số liệu, 1: Viết qua cổng 64h, 0: Viết qua cổng 60h; INPB: Trạng thái đệm vào, 1: Số liệu CPU trong đệm vào, 0: Đệm rỗng; OUTB: Trạng thái đệm ra, 1: Số liệu bộ điều khiển bàn phím trong bộ đệm ra, 0: Đệm ra rỗng. 7 0 INPBKEYLAUXBTIM OUTBXC/DPARE 7.4.2. THÂM NHẬP TRỰC TIẾP BÀN PHÍM QUA CÁC CỔNG VÀO/RA 42 v1.0014103214 7.4.2. THÂM NHẬP TRỰC TIẾP BÀN PHÍM QUA CÁC CỔNG VÀO/RA • Thanh ghi điều khiển ở địa chỉ 64h là thanh ghi chỉ viết, mã các từ lệnh: Mã Lệnh A7h Cấm thiết bị phụ A8h Cho phép thiết bị phụ A9h Kiểm tra ghép nối tới TB phụ AAh Tự kiểm tra Abh Kiểm tra ghép nối bàn phím Adh Cấm bàn phím Aeh Cho phép bàn phím C0h Đọc cổng vào C1h Đọc cổng vào ra byte thấp C2h Đọc cổng vào ra byte cao Mã Lệnh D0h Đọc cổng ra D1h Viết cổng ra D2h Viết đệm ra bàn phím D3h Viết đệm ra TB phụ D4h Viết thiết bị phụ E0h Kiểm tra đọc cổng vào F0h Gửi 1 xung tới lối ra FFh Cổng 43 v1.0014103214 • Lệnh điều khiển bàn phím Mã Lệnh Edh ON/OFF leds Bật/tắt đèn led bàn phím Eeh Echo Trả về byte eeh F0h Đăt/nhận diện Đặt 1 trong 3 mã quét và nhận diện các mã quét F2h Nhận diện bàn phím Nhận diện ACK=AT, ACK+abh+41h=MFII F3h Đặt tốc độ lặp lại/trễ Đặt tốc độ lặp lại và thời gian trễ bàn phím F4h Enable Cho phép bàn phím hoạt động F5h Chuẩn/không cho phép Đặt giá trị chuẩn và cấm bàn phím F6h Chuẩn/cho phép Đặt giá trị chuẩn và cho phép bàn phím Feh Resend Bàn phím truyền kí tự cuối cùng một lần cuối nữa tới PC FFh Reset Khởi động bên trong bàn phím 7.4.2. THÂM NHẬP TRỰC TIẾP BÀN PHÍM QUA CÁC CỔNG VÀO/RA (tiếp theo) 44 v1.0014103214 7.4.2. THÂM NHẬP TRỰC TIẾP BÀN PHÍM QUA CÁC CỔNG VÀO/RA (tiếp theo) • Cấu trúc byte chỉ thị CPL: 1 bật đèn Caps Lock, 0 tắt; NUM: 1 bật đèn Num Lock, 0 tắt; SCR: 1 bật đèn Scr Lock, 0 tắt. 7 0 NUM000 SCRCPL00 45 v1.0014103214 7.5.1. Cấu tạo vào nguyên tắc hoạt động 7.5.2. Ghép nối chuột 7.5. CHUỘT 46 v1.0014103214 • Bi dễ dàng chuyển động; • 2 thanh sắt (nhựa) chuyển động đặt vuông góc với nhau; • Đèn cảm biến; • Vi mạch điều khiển. 7.5.1. CẤU TẠO VÀ NGUYÊN TẮC HOẠT ĐỘNG 47 v1.0014103214 • Chuột kết nối tới PC qua cổng COM. • Chuột không dây (USB). • Ngắt 33h của BIOS. • Chương trình ghép nối chuột thực hiện việc nối chuột với các trình ứng dụng, chúng thường được cài đặt như các trình quản lí thiết bị, hoạt động như một chương trình thường trú trong hệ thống. • Có thể định nghĩa dạng con trỏ chuột qua hàm 09h và 0Ah của ngắt 33h. 7.5.2. GHÉP NỐI CHUỘT 48 v1.0014103214 7.6.1. Màn hình quét CRT 7.6.3. Các chuẩn màn hình thông dụng 7.6.2. Bản mạch ghép nối màn hình 7.6.4. Thâm nhập màn hình qua DOS và BIOS 7.6.5. Màn hình LCD 7.6. MÀN HÌNH 49 v1.0014103214 • Cấu tạo màn hình CRT CRT: Ống chân không; Súng bắn tia điện tử; Mặt trong thành ống phủ lớp huỳnh quang; Bộ phận lái tia điện tử. 7.6.1. MÀN HÌNH QUÉT CRT 50 v1.0014103214 7.6.1. MÀN HÌNH QUÉT CRT • Vi mạch ghép nối màn hình (card màn hình): Chuyển tải các thông tin từ bộ VXL ra màn hình. • Card màn hình cắm và các khe mở rộng của PC. • Trung tâm là chip điều khiển ống hình CRTC. • VXL thâm nhập RAM video qua mạch ghép nối BUS để viết thông tin xác định kí tự hoặc hình vẽ cần hiển thị, CRTC liên tục phát ra các địa chỉ để RAM video đọc các kí tự trong đó và truyền tới máy phát kí tự. 51 v1.0014103214 • Card CGA Độ phân giải: 640x350 pixel; RAM video: 64-256KB; 16 màu; Tần số quét ngang: 15.7-21.8KHz, tần số quét dọc: 60Hz. • Card VGA Độ phân giải: 640x480 pixel; RAM video: 256KB; 256 màu; Tần số quét ngang: 31.5 KHz, tần số quét dọc: 50-70Hz. 7.6.3. CÁC CHUẨN MÀN HÌNH THÔNG DỤNG 52 v1.0014103214 • Thâm nhập qua DOS: Sử dụng các hàm của ngắt 21 để truy cập màn hình Hàm 02h: Ra màn hình; Hàm 06h: Ra một kí tự; Hàm 09h: Ra một chuỗi; Hàm 40h: Viết file/thiết bị; • Thâm nhập qua BIOS: Sử dụng ngắt 10h. 7.6.4. THÂM NHẬP MÀN HÌNH QUA DOS VÀ BIOS 53 v1.0014103214 • Kết hợp tinh thể rắn và tinh thể lỏng. • Các tinh thể lỏng phía trên dọc theo chiều a, phần tử dưới dọc theo chiều b. • Các phần tử tinh thể lỏng được sắp xếp thành ma trận các điểm ảnh (dots). 7.6.5. MÀN HÌNH LCD 54 v1.0014103214 Trong bài này chúng ta đã nghiên cứu các nội dung chính sau: • Các phương pháp định địa chỉ bộ nhớ cho các thiết bị ngoại vi; • Các thiết bị ngoại vi thông dụng, cấu tạo và nguyên tắc hoạt động của các thiết bị đó; • Phương pháp trao đổi thông tin hỏi vòng và phương pháp ngắt. TÓM LƯỢC CUỐI BÀI

File đính kèm:

bai_giang_kien_truc_may_tinh_bai_7_ghep_noi_may_tinh_voi_thi.pdf

bai_giang_kien_truc_may_tinh_bai_7_ghep_noi_may_tinh_voi_thi.pdf