Bài giảng Kiến trúc máy tính 1 - Chương 5: Mạch tuần tự - Vũ Đức Lung

5.1. Xung đồng hồ

5.2. Mạch lật (chốt – latch)

5.2.1. Mạch lật SR (SR-latch)

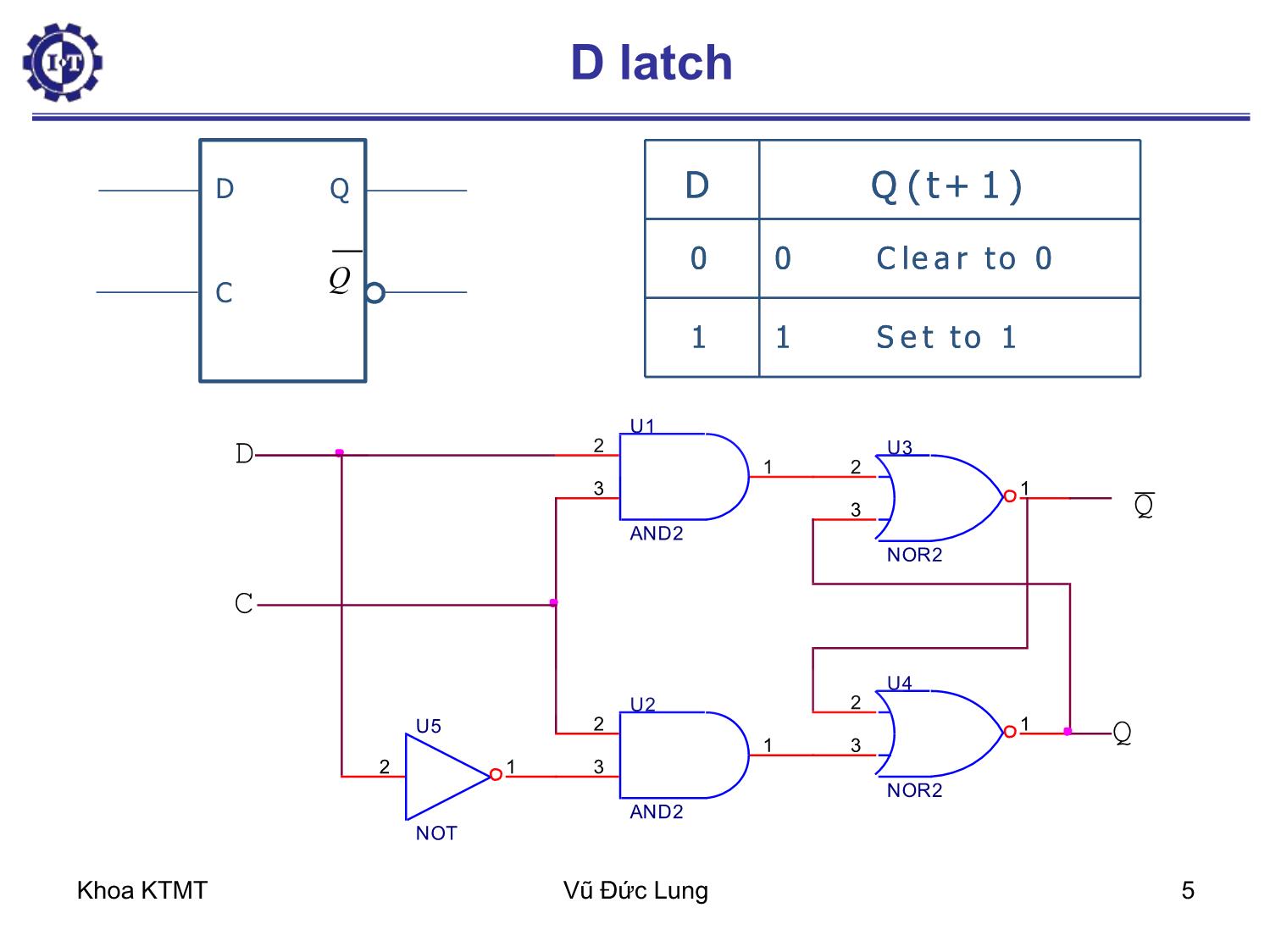

5.2.2. Mạch lật D

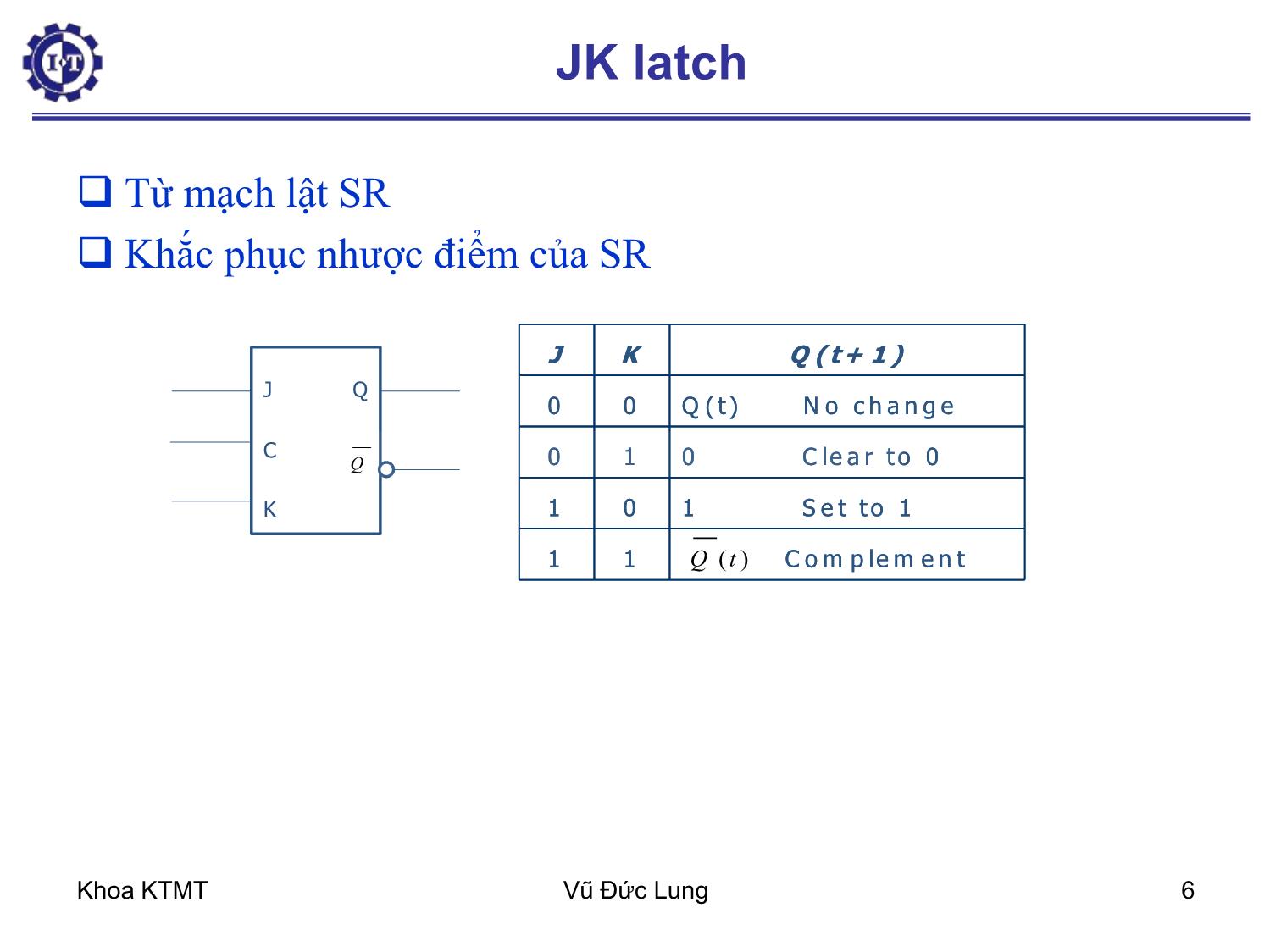

5.2.3. Mạch lật IK

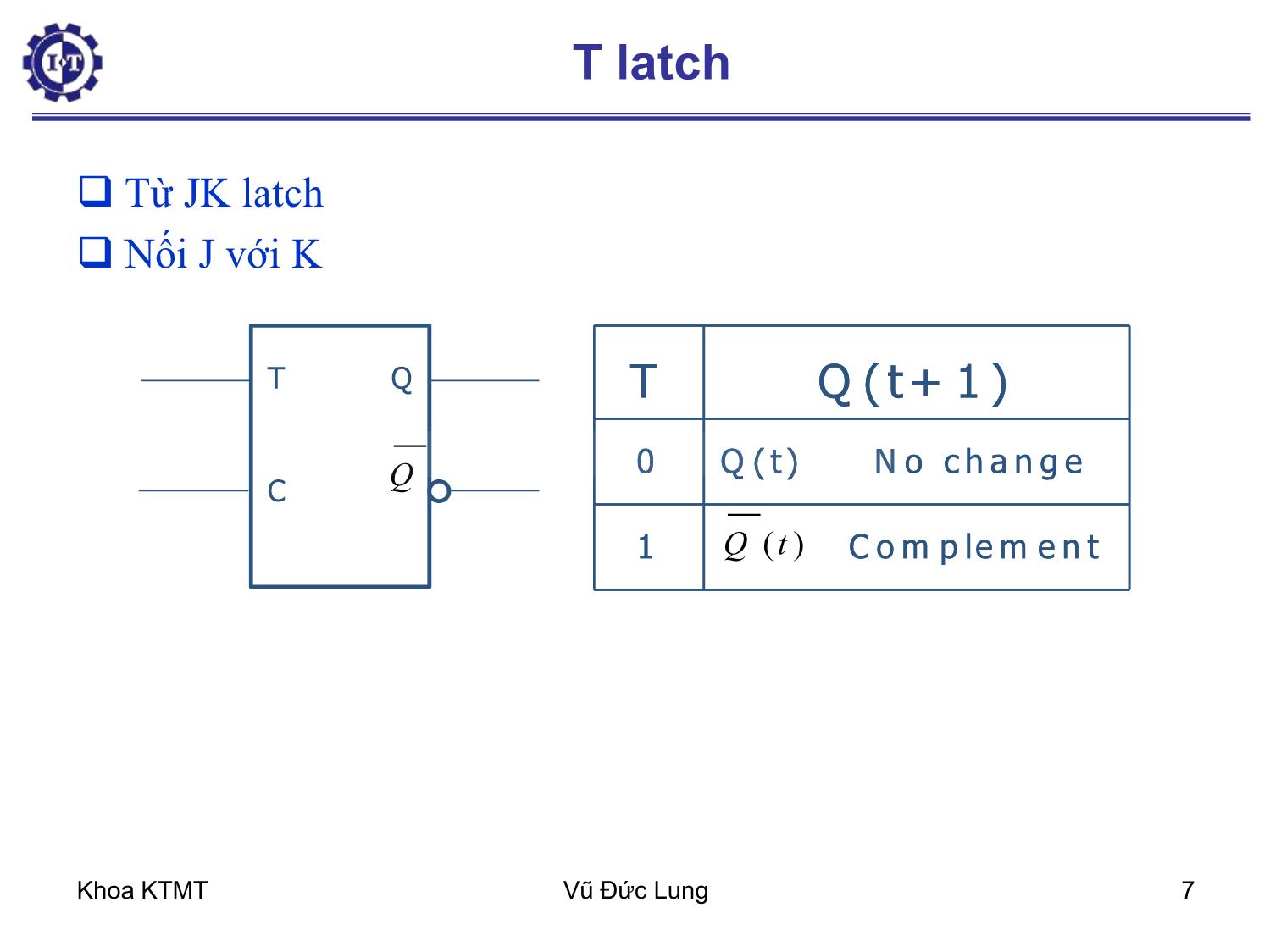

5.3.4. Mạch lật T

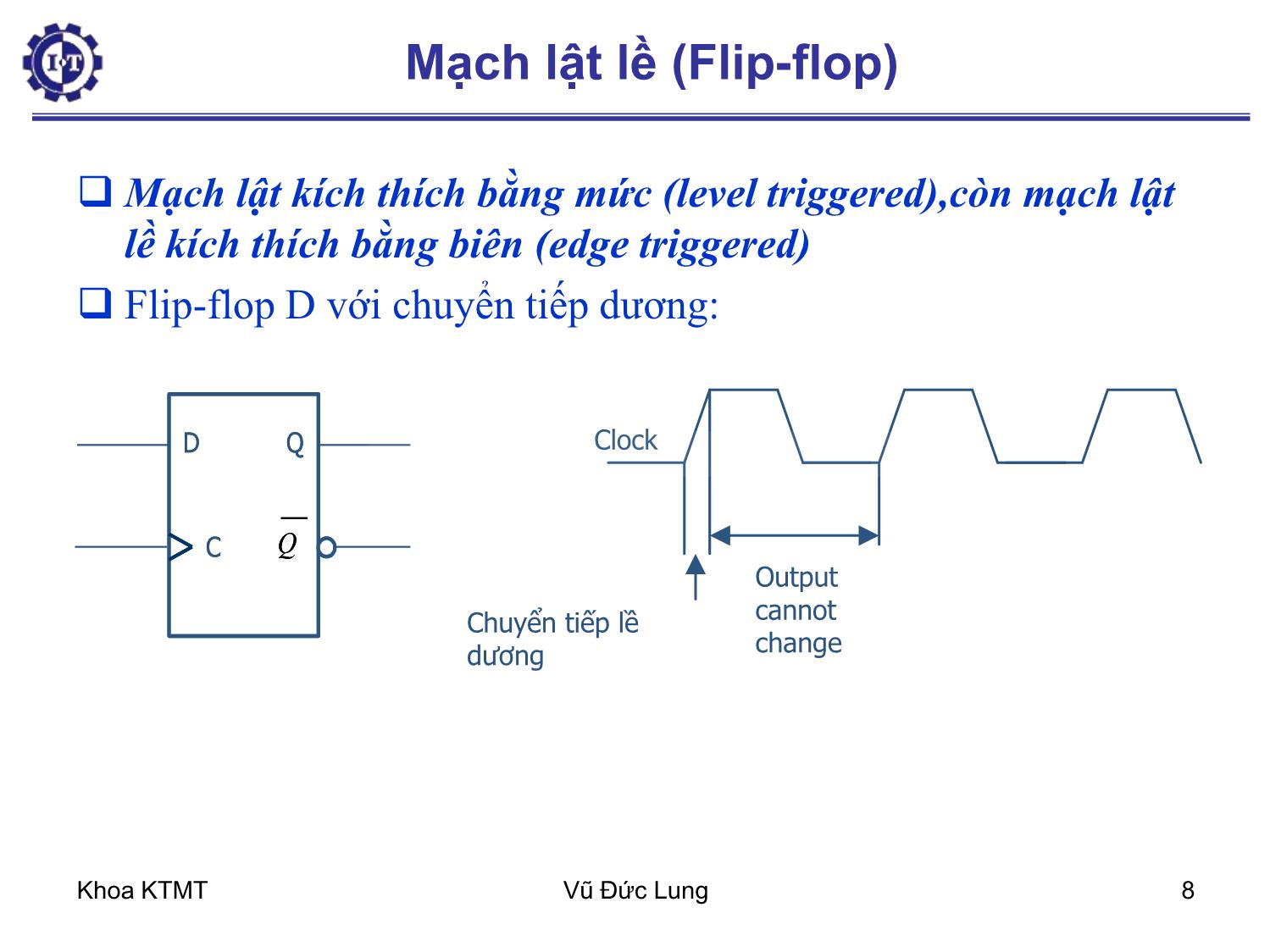

5.3. Mạch lật lề (Flip-flop)

5.4. Mạch tuần tự

Trang 1

Trang 2

Trang 3

Trang 4

Trang 5

Trang 6

Trang 7

Trang 8

Trang 9

Trang 10

Tải về để xem bản đầy đủ

Bạn đang xem 10 trang mẫu của tài liệu "Bài giảng Kiến trúc máy tính 1 - Chương 5: Mạch tuần tự - Vũ Đức Lung", để tải tài liệu gốc về máy hãy click vào nút Download ở trên

Tóm tắt nội dung tài liệu: Bài giảng Kiến trúc máy tính 1 - Chương 5: Mạch tuần tự - Vũ Đức Lung

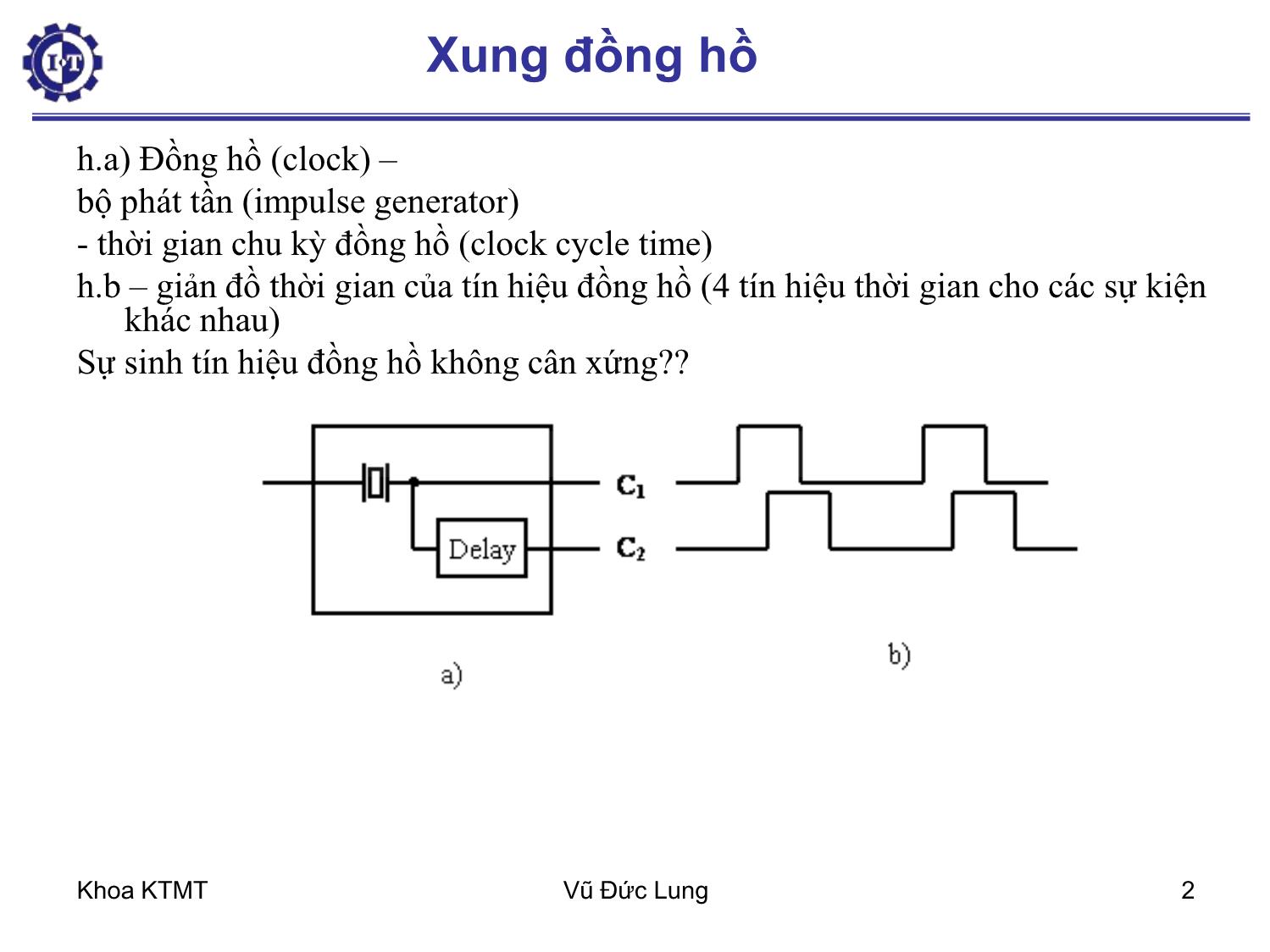

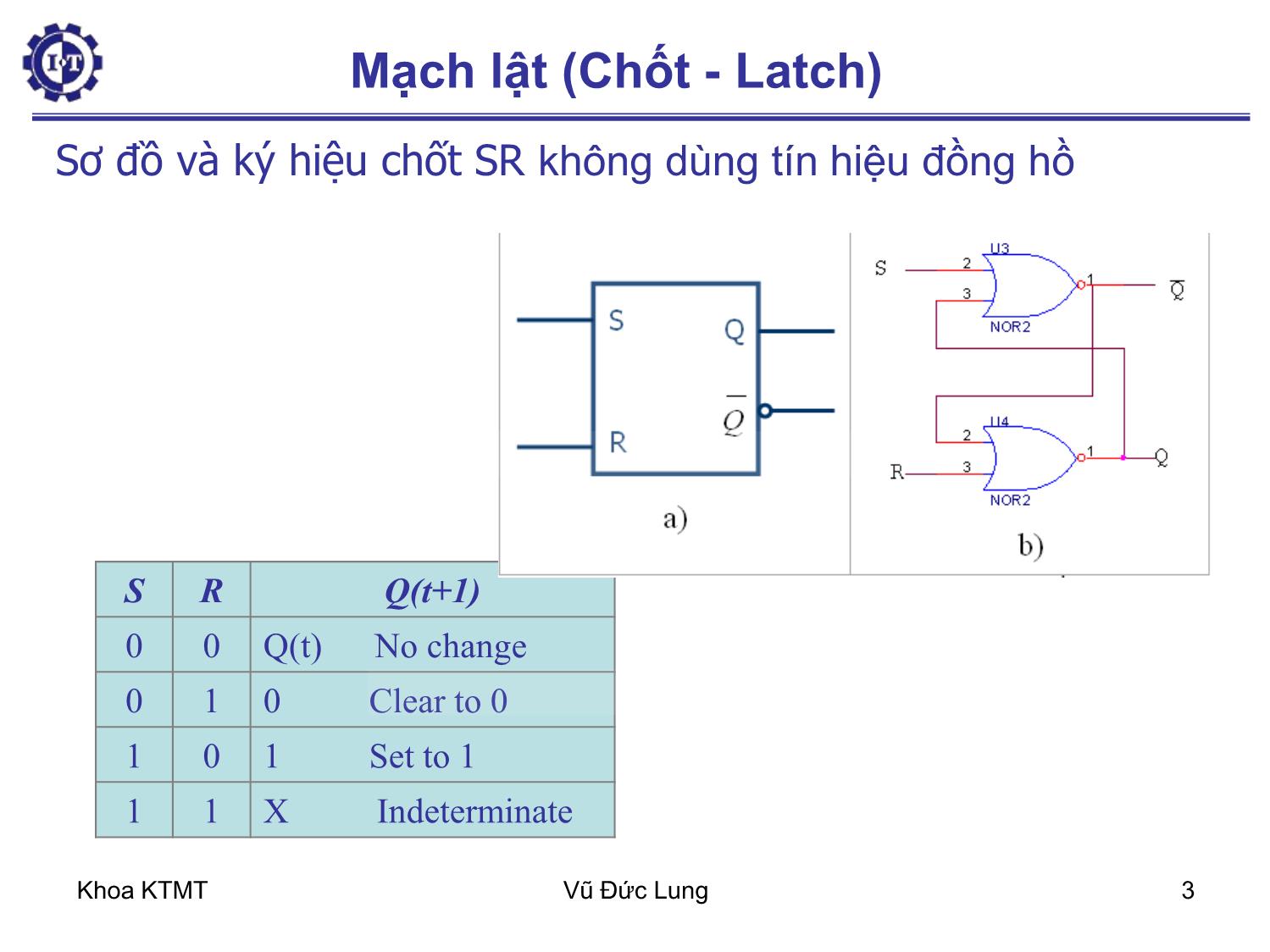

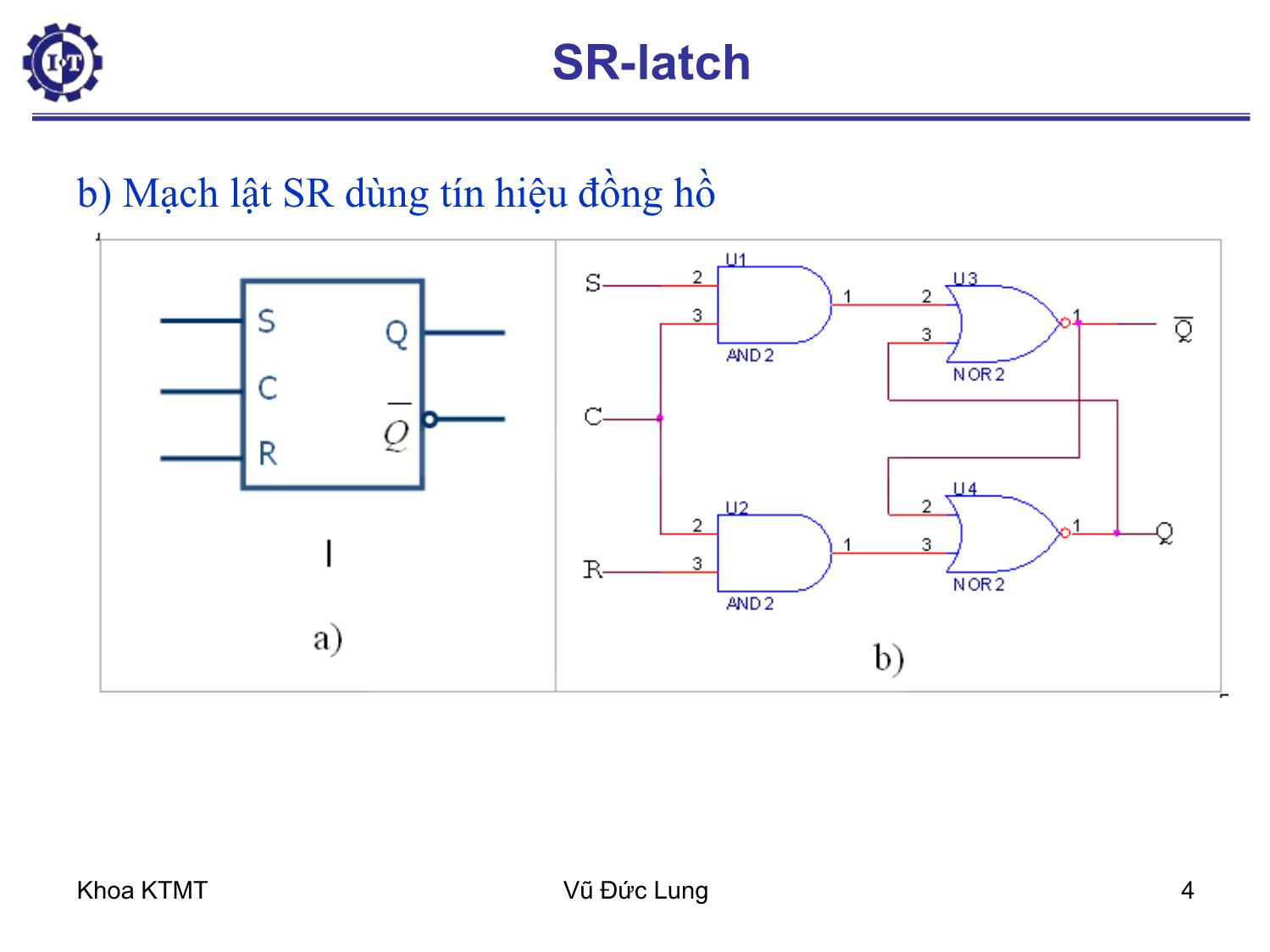

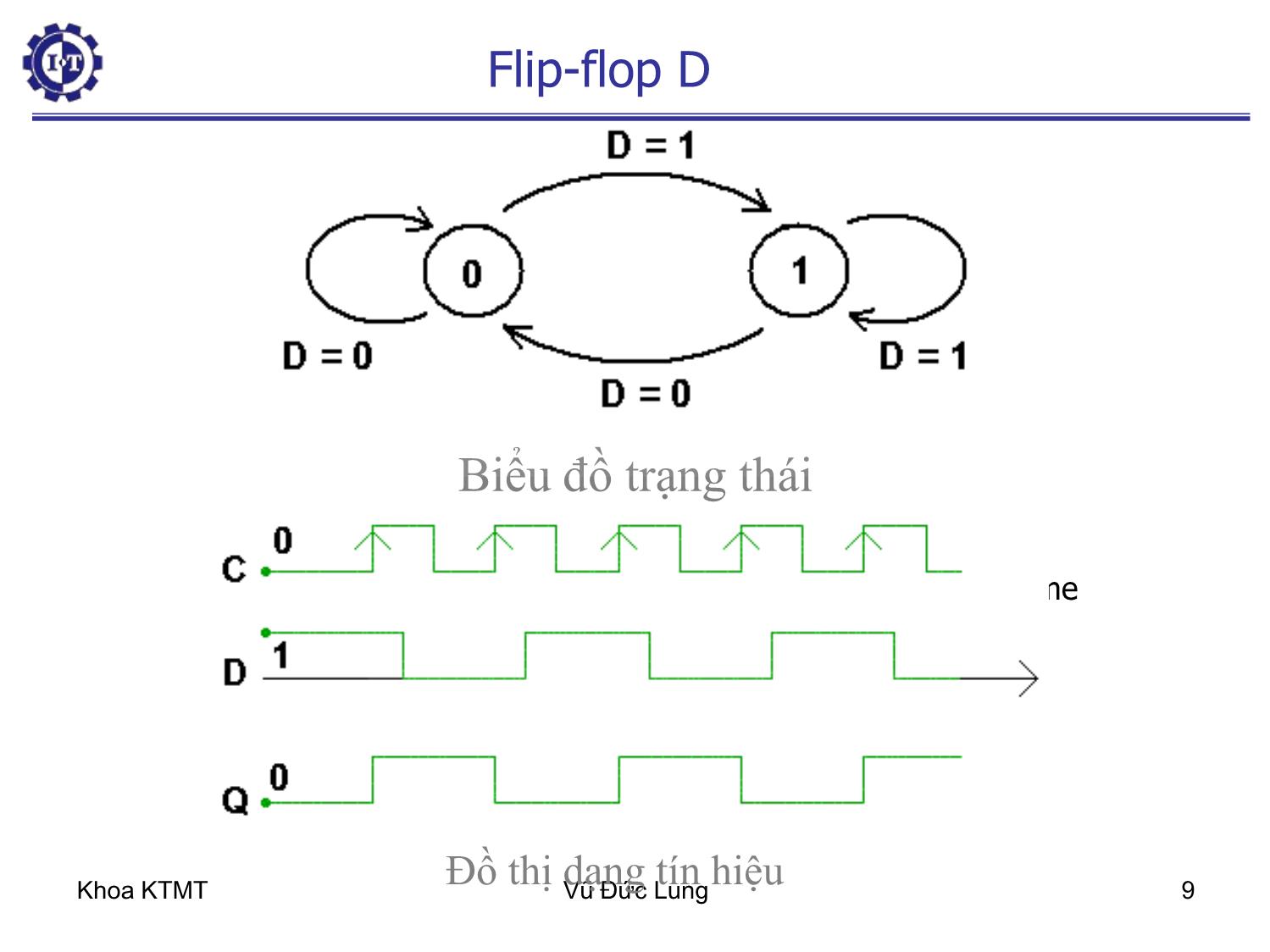

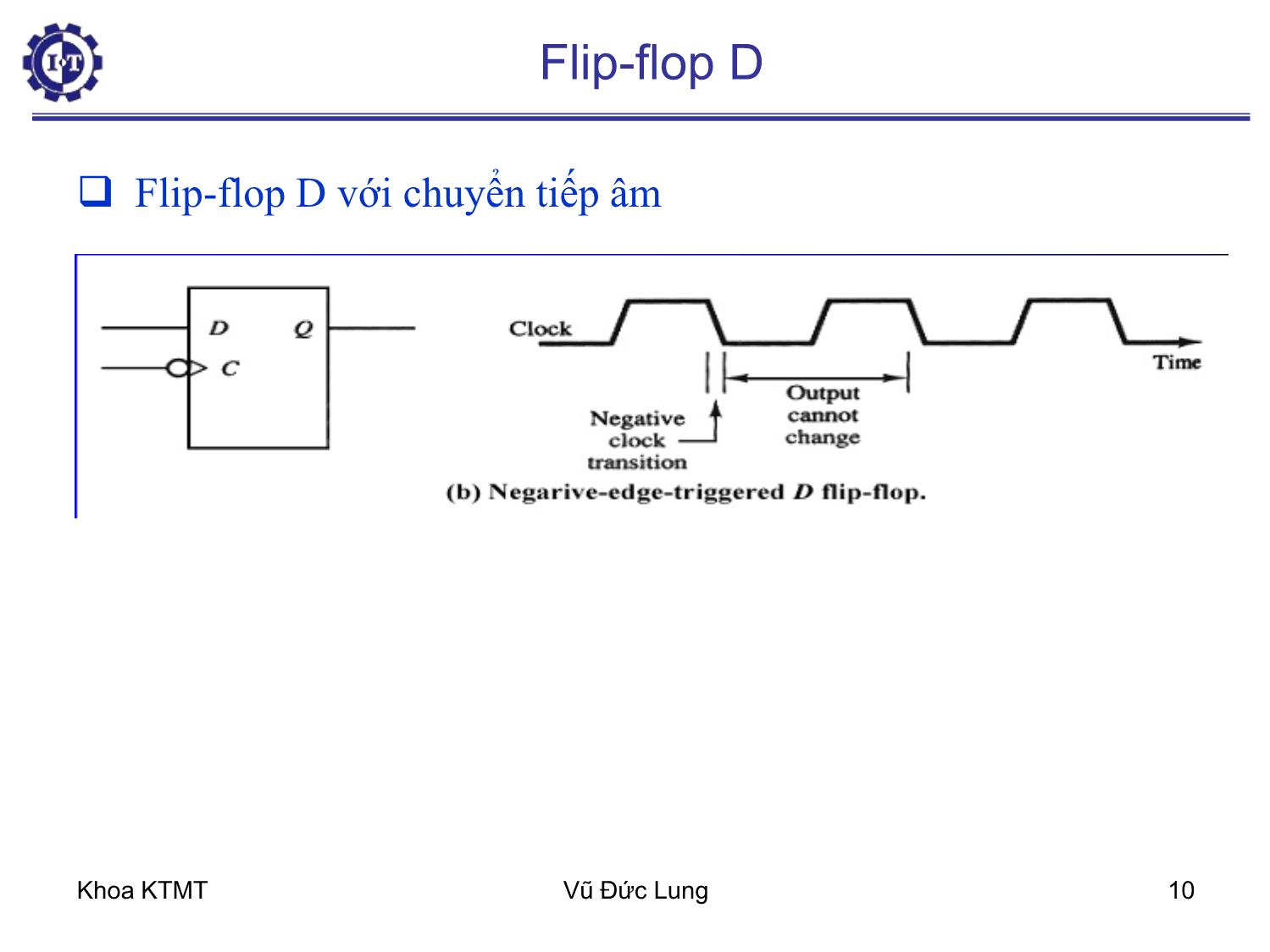

Khoa KTMT Vũ Đức Lung 1 Chương 5 – Mạch Tuần tự 5.1. Xung đồng hồ 5.2. Mạch lật (chốt – latch) 5.2.1. Mạch lật SR (SR-latch) 5.2.2. Mạch lật D 5.2.3. Mạch lật IK 5.3.4. Mạch lật T 5.3. Mạch lật lề (Flip-flop) 5.4. Mạch tuần tự Khoa KTMT Vũ Đức Lung 2 Xung đồng hồ h.a) Đồng hồ (clock) – bộ phát tần (impulse generator) - thời gian chu kỳ đồng hồ (clock cycle time) h.b – giản đồ thời gian của tín hiệu đồng hồ (4 tín hiệu thời gian cho các sự kiện khác nhau) Sự sinh tín hiệu đồng hồ không cân xứng?? Khoa KTMT Vũ Đức Lung 3 Mạch lật (Chốt - Latch) Sơ đồ và ký hiệu chốt SR không dùng tín hiệu đồng hồ S R Q(t+1) 0 0 Q(t) No change 0 1 0 Clear to 0 1 0 1 Set to 1 1 1 X Indeterminate Khoa KTMT Vũ Đức Lung 4 SR-latch b) Mạch lật SR dùng tín hiệu đồng hồ Khoa KTMT Vũ Đức Lung 5 D latch D C Q Q 1 S e t to 11 0 C le a r to 00 Q ( t+ 1 )D U3 NOR2 1 2 3 U4 NOR2 1 2 3 U2 AND2 1 2 3 U1 AND2 1 2 3 U5 NOT 12 D Q _ Q C Khoa KTMT Vũ Đức Lung 6 JK latch Từ mạch lật SR Khắc phục nhược điểm của SR J C Q Q K C o m p le m e n t11 1 S e t to 101 0 C le a r to 010 Q ( t ) N o c h a n g e00 Q ( t+ 1 )KJ )( tQ Khoa KTMT Vũ Đức Lung 7 T latch Từ JK latch Nối J với K T C Q Q C o m p le m e n t1 Q ( t ) N o c h a n g e0 Q ( t+ 1 )T )( tQ Khoa KTMT Vũ Đức Lung 8 Mạch lật lề (Flip-flop) Mạch lật kích thích bằng mức (level triggered),còn mạch lật lề kích thích bằng biên (edge triggered) Flip-flop D với chuyển tiếp dương: D C Q Q Clock Chuyển tiếp lề dương Output cannot change Khoa KTMT Vũ Đức Lung 9 Flip-flop D Time Biểu đồ trạng thái Đồ thị dạng tín hiệu Khoa KTMT Vũ Đức Lung 10 Flip-flop D Flip-flop D với chuyển tiếp âm Khoa KTMT Vũ Đức Lung 11 4. Bảng kích thích Q(t) Q(t+1) S R 0 0 0 X 0 1 1 0 1 0 0 1 1 1 X 0 SR Q(t) Q(t+1) J K 0 0 0 X 0 1 1 x 1 0 x 1 1 1 X 0 JK Q(t) Q(t+1) D 0 0 0 0 1 1 1 0 0 1 1 1 D Q(t) Q(t+1) T 0 0 0 0 1 1 1 0 1 1 1 0 T Bảng kích thích của bốn mạch lật lề Khoa KTMT Vũ Đức Lung 12 Mạch tuần tự C o m b in a t io n a l c ir c u it F l ip - f lo p s C lo c k In p u t O u tp u t Khoa KTMT Vũ Đức Lung 13 Mạch tuần tự Khoa KTMT Vũ Đức Lung 14 Mạch tuần tự Khoa KTMT Vũ Đức Lung 15 Mạch tuần tự Khoa KTMT Vũ Đức Lung 16 Mạch tuần tự Trạng thái hiện tại Nhập Trạng thái kế Ngõ nhập vào các flip-flop Đầu ra A B x A B SA RA SB RB y 0 0 0 0 0 0 x 0 x 0 0 0 1 1 1 1 0 1 0 0 0 1 0 0 1 0 x x 0 0 0 1 1 0 0 0 x 0 1 1 1 0 0 1 0 x 0 0 x 0 1 0 1 0 1 0 1 1 0 1 1 1 0 1 1 x 0 x 0 0 1 1 1 1 0 x 0 0 1 0 Khoa KTMT Vũ Đức Lung 17 Mạch tuần tự Khoa KTMT Vũ Đức Lung 18 Mạch tuần tự Khoa KTMT Vũ Đức Lung 19 Mạch tuần tự Qui trình thiết kế mạch tuần tự – Bước 1: Chuyển đặc tả mạch sang lược đồ trạng thái – Bước 2: lược đồ trạng thái => bảng trạng thái – Bước 3: Từ bảng trạng thái viết hàm cho các ngõ nhập của Flip-flops – Bước 4: vẽ sơ đồ mạch Khoa KTMT Vũ Đức Lung 20 Mạch tuần tự Khoa KTMT Vũ Đức Lung 21 Mạch tuần tự Khoa KTMT Vũ Đức Lung 22 Mạch tuần tự Khoa KTMT Vũ Đức Lung 23 Mạch tuần tự Khoa KTMT Vũ Đức Lung 24 Ví dụ thiết kế mạch tuần tự Thiết kế mạch tuần tự dùng mạch lật SR. Khi ngõ nhập x=0, trạng thái mạch lật lề không thay đổi, ngõ xuất y=0. Khi x=1, dãy trạng thái là 11,10,01,00 và lặp lại còn ngõ xuất y sẽ có giá trị là 1 khi số bit trạng thái mạch lật lề bằng 1 là lẻ, các trường hợp còn lại thì bằng 0.

File đính kèm:

bai_giang_kien_truc_may_tinh_1_chuong_5_mach_tuan_tu_vu_duc.pdf

bai_giang_kien_truc_may_tinh_1_chuong_5_mach_tuan_tu_vu_duc.pdf