Về một giải pháp cứng hóa phép tính lũy thừa modulo

Abstract— Modular exponentiation is the

basic operation in cryptography algorithm RSA.

This’s o p i te gorith , onsu ing

resource and time to implement (especially with

large number). Hardware implementation of

modular exponentiation on the FPGA would

increase speed, reduce computation time that is

required by the practice. The heart of modular

operand is modular multiplication of large

number. In this paper we presented introduction,

the analysis, choosing modular exponentiation

algorithm and modular multiplication

Montgomery based on several public researchs

on the world. Modular exponentiation operation

is implemented with hardware language HDL

Verilog with the modulus is chosen as 2048 bit,

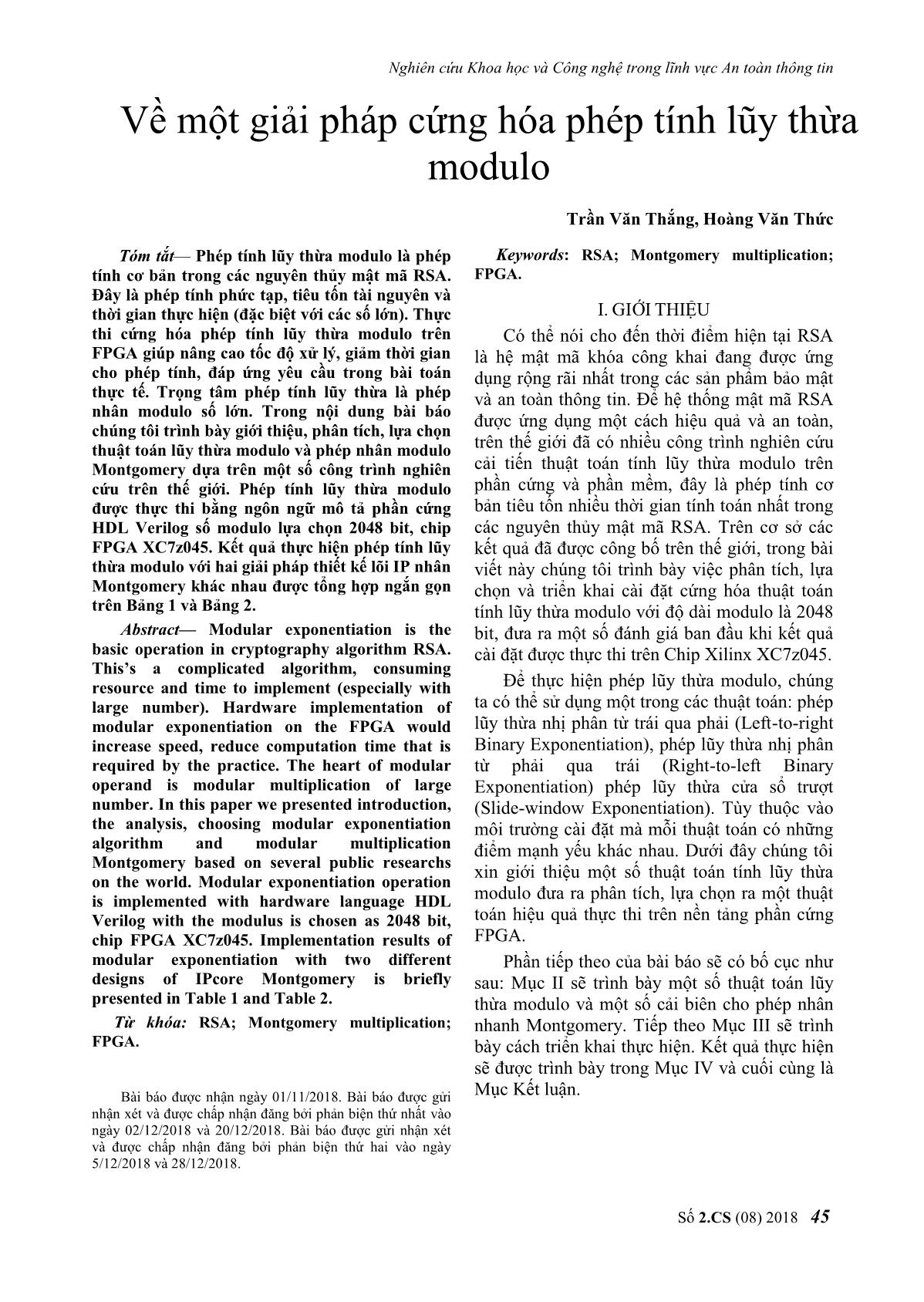

chip FPGA XC7z045. Implementation results of

modular exponentiation with two different

designs of IPcore Montgomery is briefly

presented in Table 1 and Table 2.

Trang 1

Trang 2

Trang 3

Trang 4

Trang 5

Trang 6

Trang 7

File đính kèm:

ve_mot_giai_phap_cung_hoa_phep_tinh_luy_thua_modulo.pdf

ve_mot_giai_phap_cung_hoa_phep_tinh_luy_thua_modulo.pdf