Thiết kế và chế tạo máy phân tích đa kênh ghép máy tính qua cổng USB

TÓM TẮT

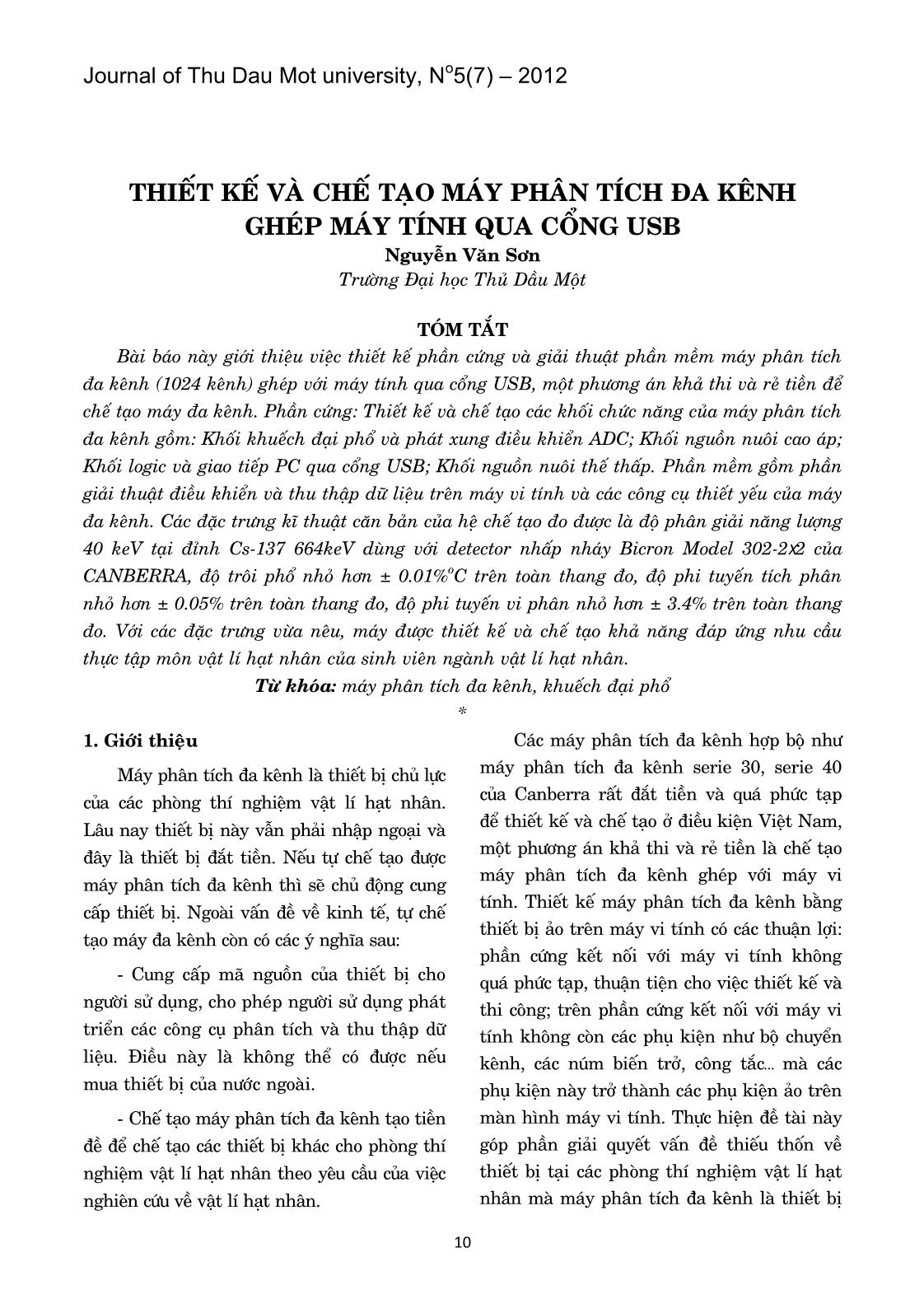

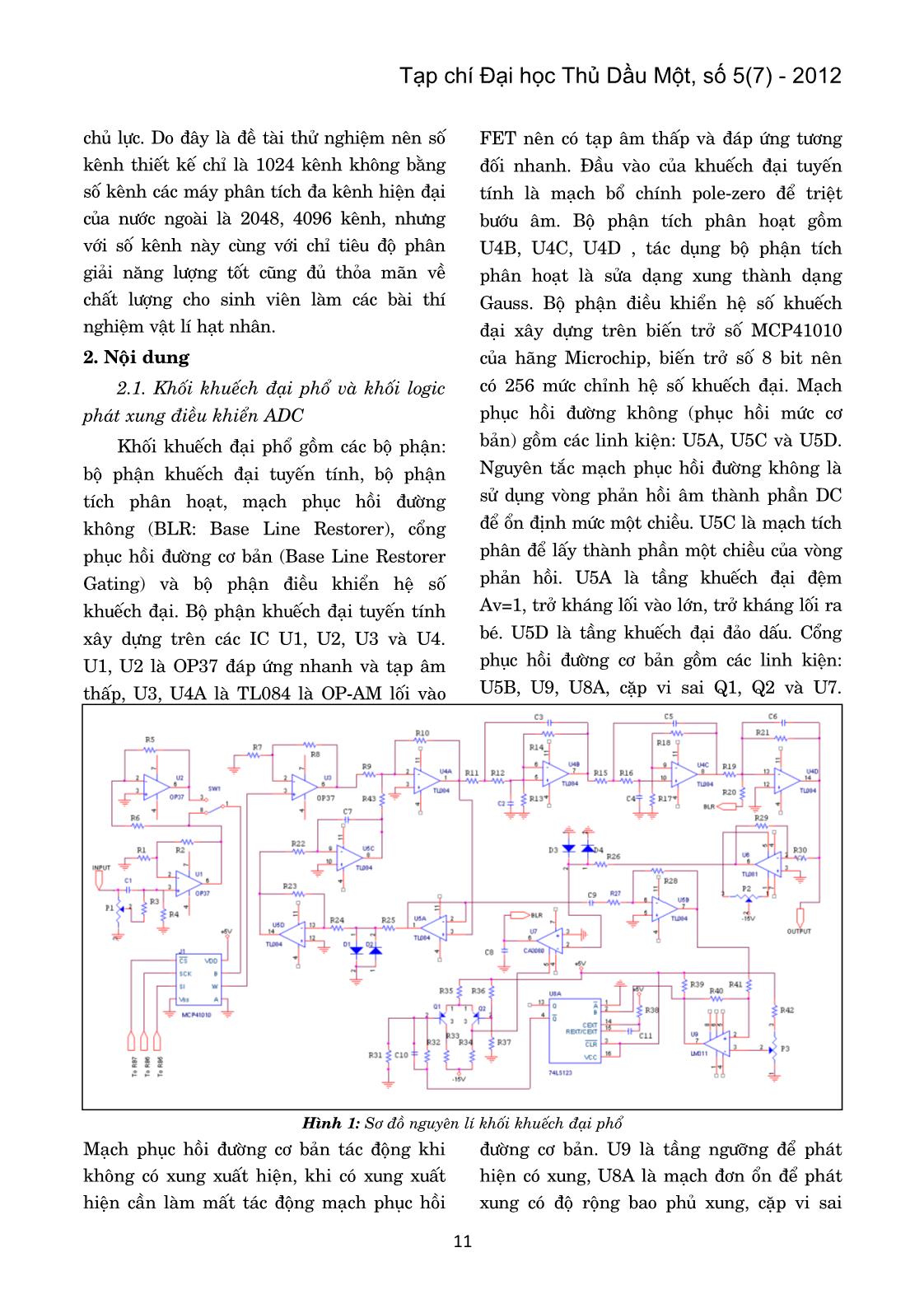

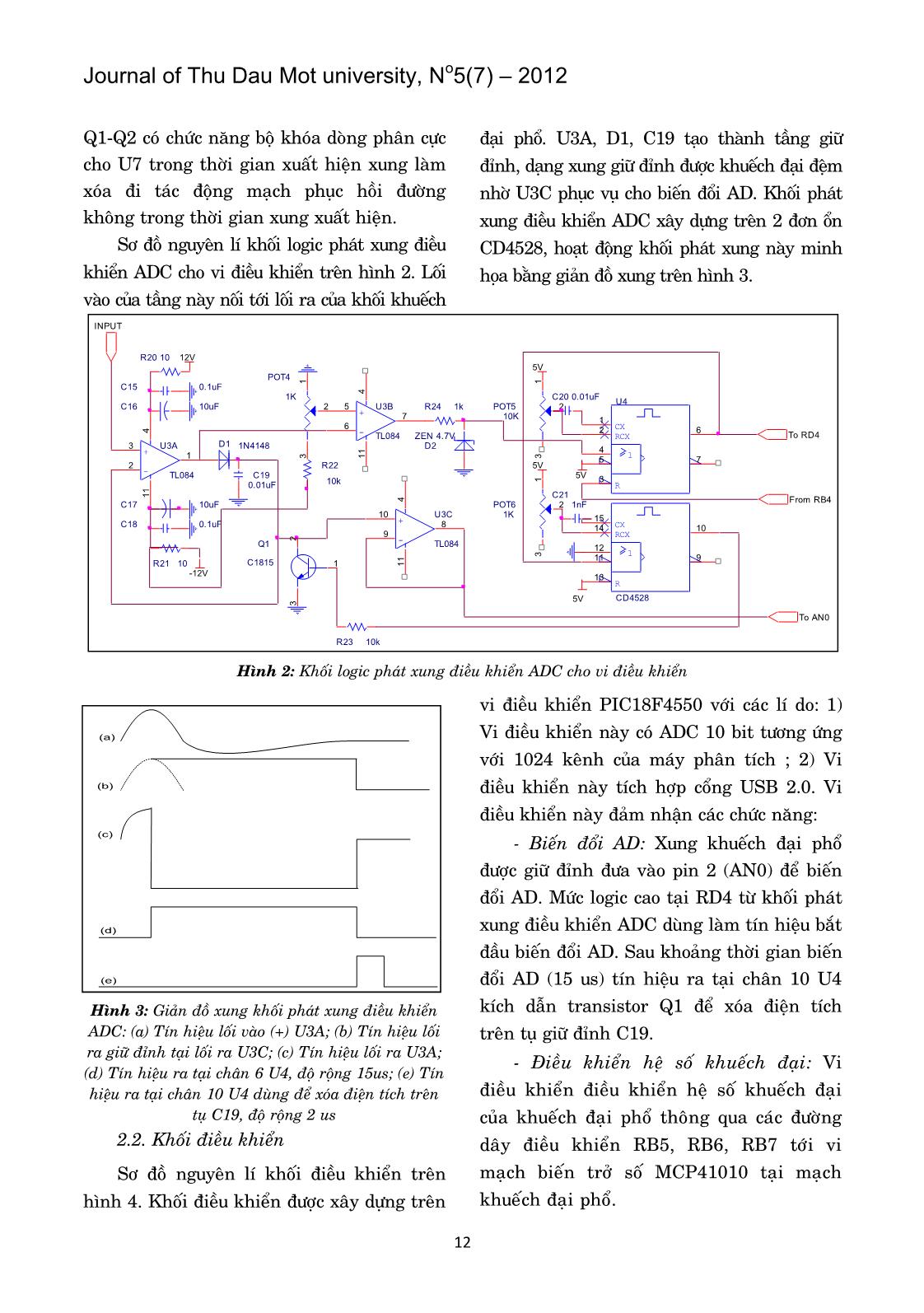

Bài báo này giới thiệu việc thiết kế phần cứng và giải thuật phần mềm máy phân tích

đa kênh (1024 kênh) ghép với máy tính qua cổng USB, một phương án khả thi và rẻ tiền để

chế tạo máy đa kênh. Phần cứng: Thiết kế và chế tạo các khối chức năng của máy phân tích

đa kênh gồm: Khối khuếch đại phổ và phát xung điều khiển ADC; Khối nguồn nuôi cao áp;

Khối logic và giao tiếp PC qua cổng USB; Khối nguồn nuôi thế thấp. Phần mềm gồm phần

giải thuật điều khiển và thu thập dữ liệu trên máy vi tính và các công cụ thiết yếu của máy

đa kênh. Các đặc trưng kĩ thuật căn bản của hệ chế tạo đo được là độ phân giải năng lượng

40 keV tại đỉnh Cs-137 664keV dùng với detector nhấp nháy Bicron Model 302-2x2 của

CANBERRA, độ trôi phổ nhỏ hơn ± 0.01%oC trên toàn thang đo, độ phi tuyến tích phân

nhỏ hơn ± 0.05% trên toàn thang đo, độ phi tuyến vi phân nhỏ hơn ± 3.4% trên toàn thang

đo. Với các đặc trưng vừa nêu, máy được thiết kế và chế tạo khả năng đáp ứng nhu cầu

thực tập môn vật lí hạt nhân của sinh viên ngành vật lí hạt nhân.

Trang 1

Trang 2

Trang 3

Trang 4

Trang 5

Trang 6

Trang 7

Trang 8

Trang 9

Trang 10

Tải về để xem bản đầy đủ

Tóm tắt nội dung tài liệu: Thiết kế và chế tạo máy phân tích đa kênh ghép máy tính qua cổng USB

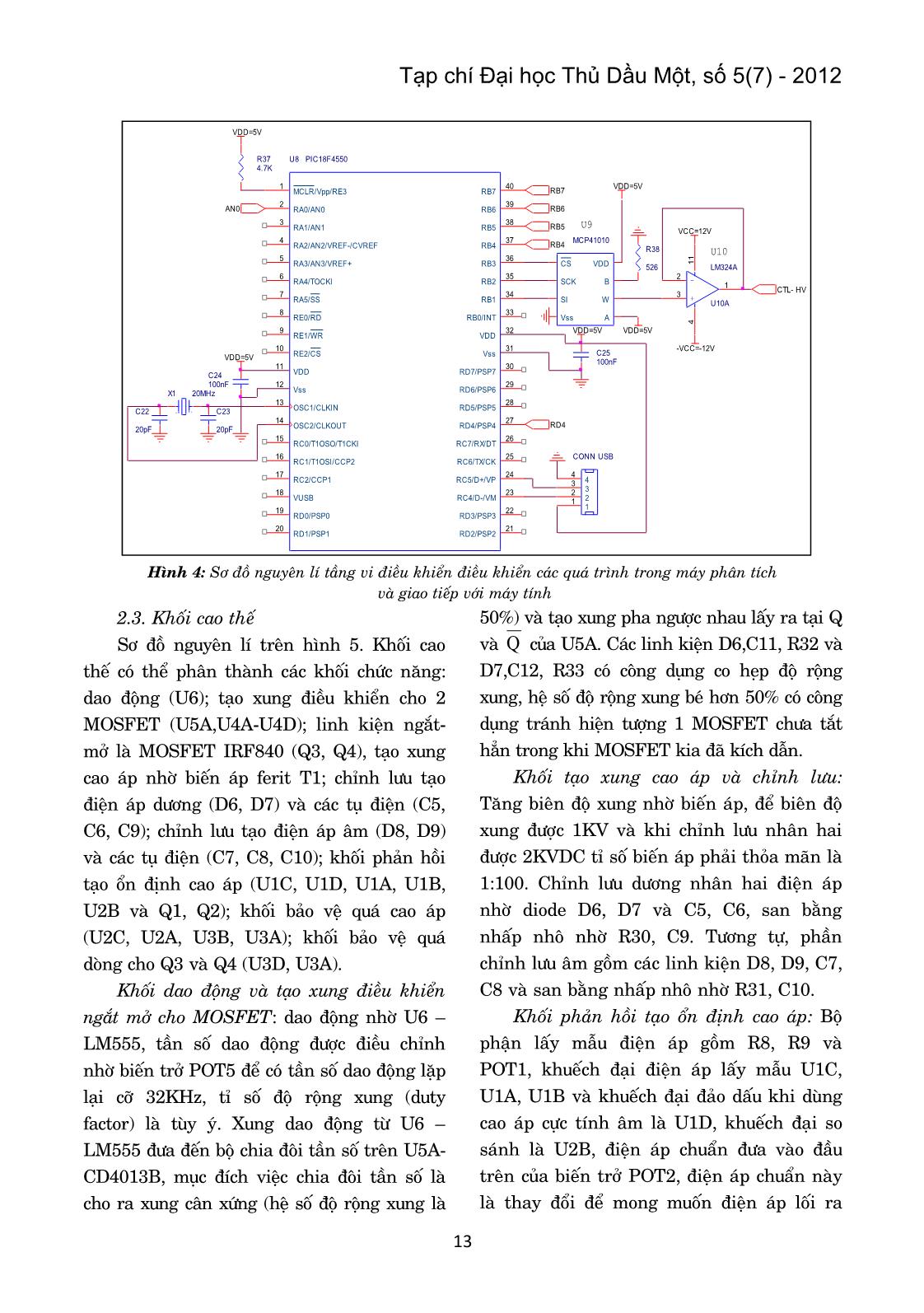

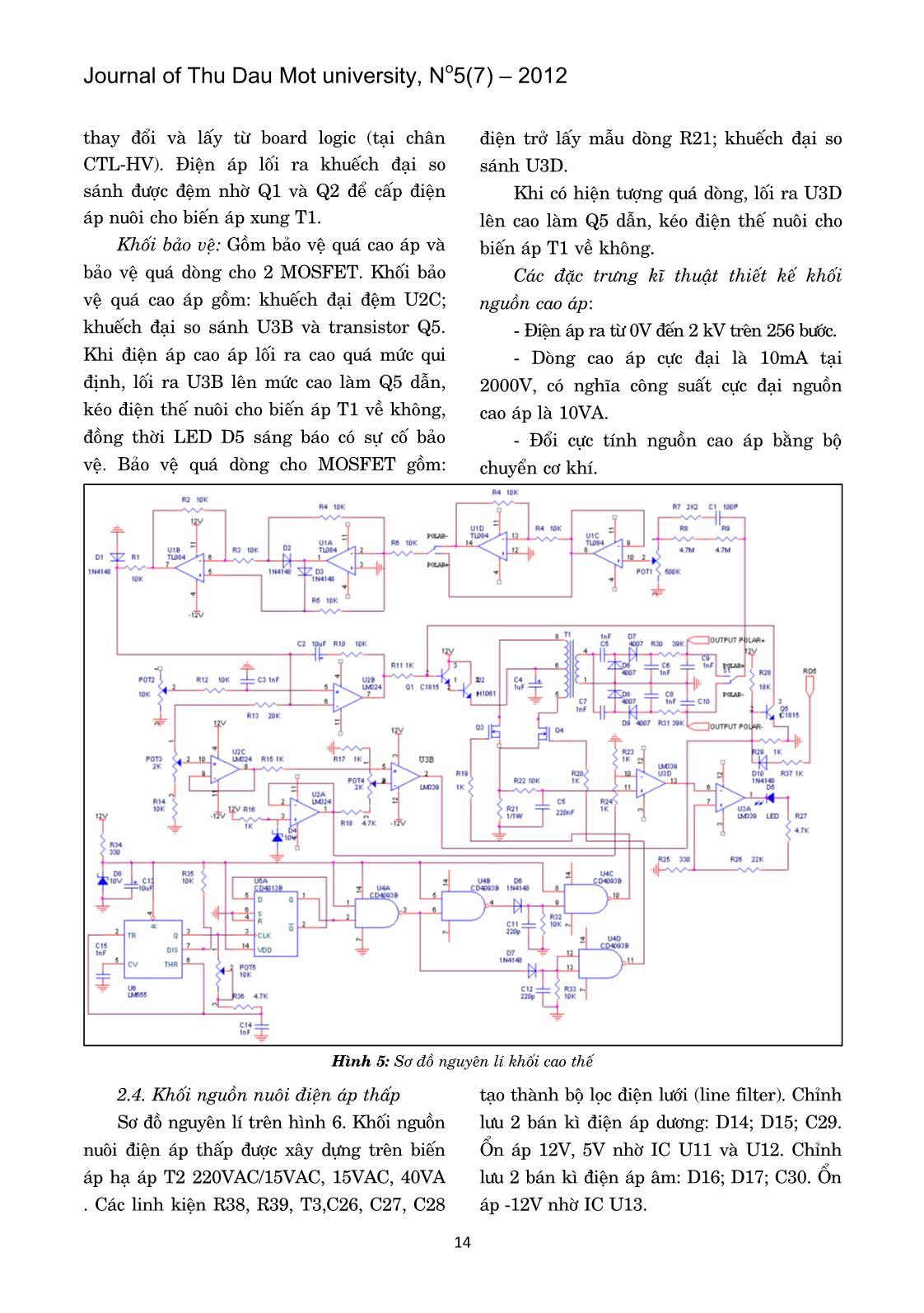

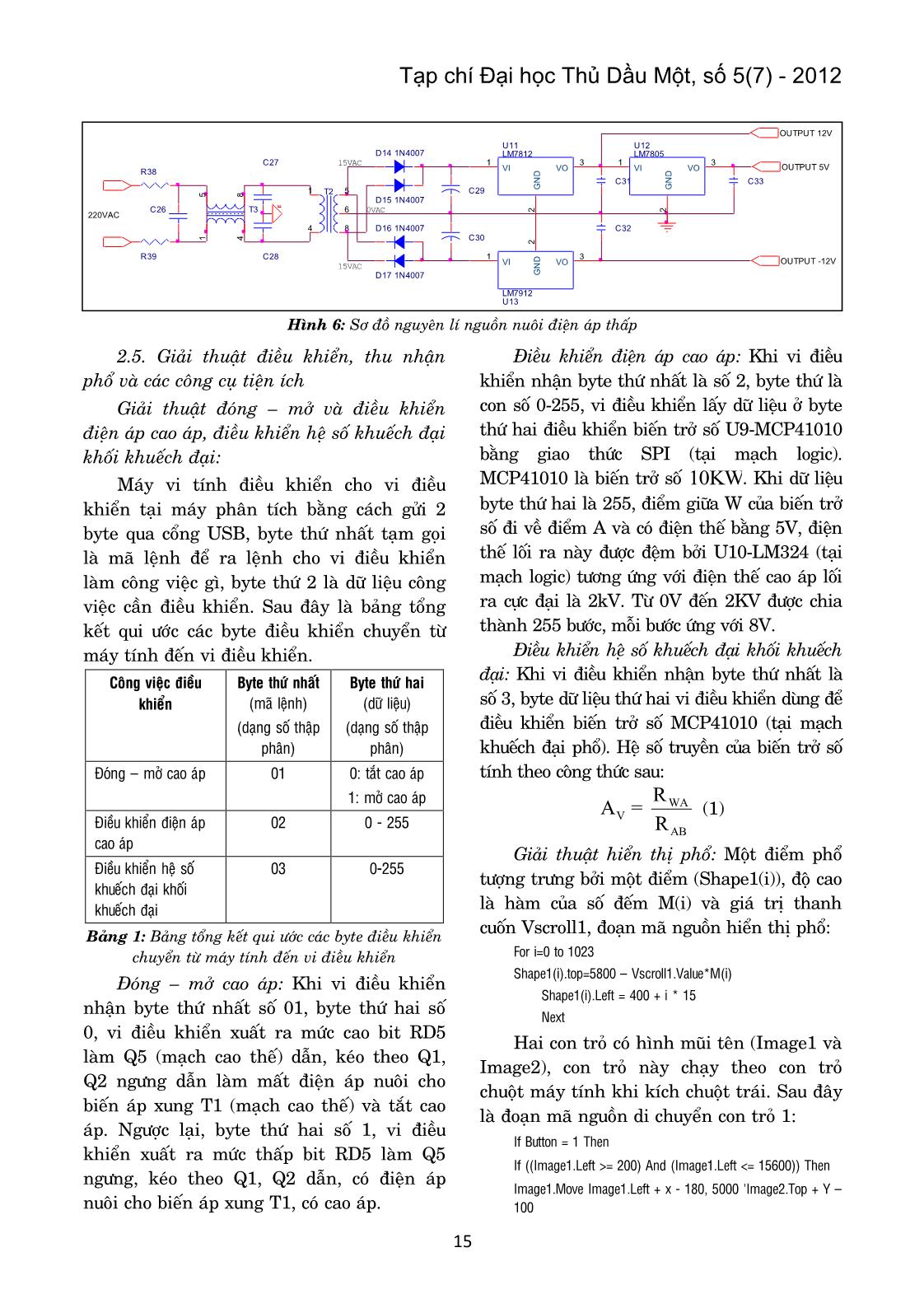

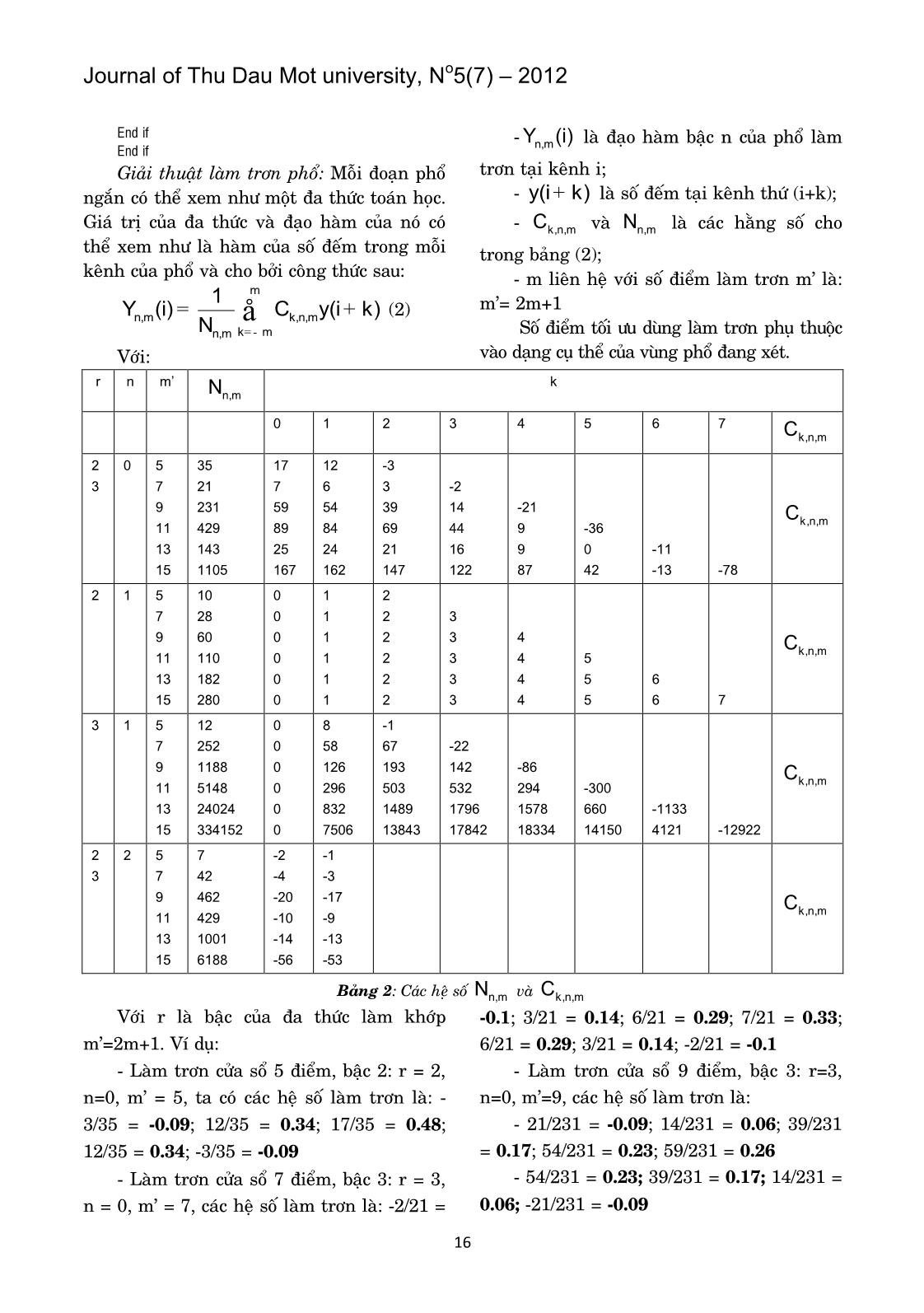

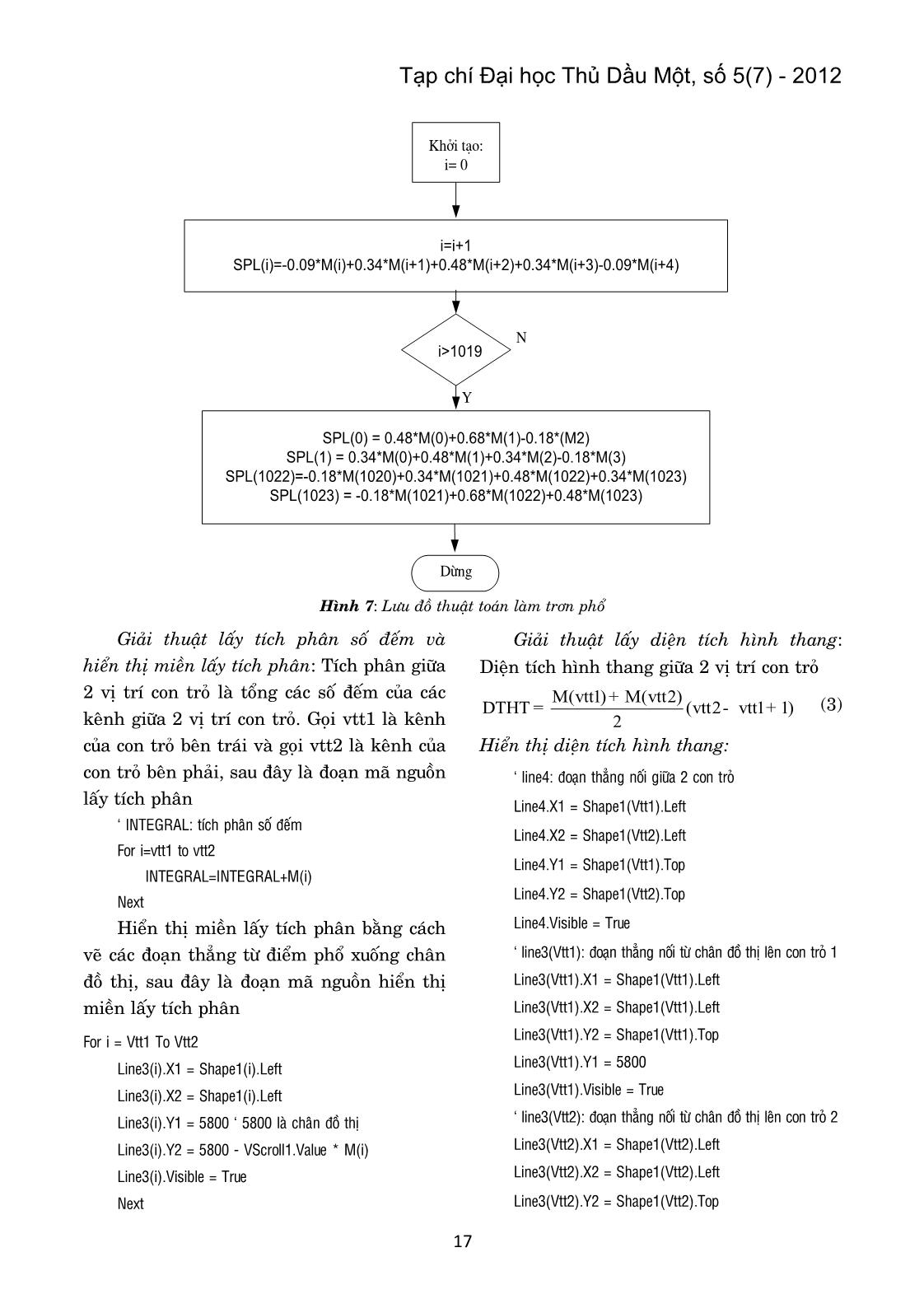

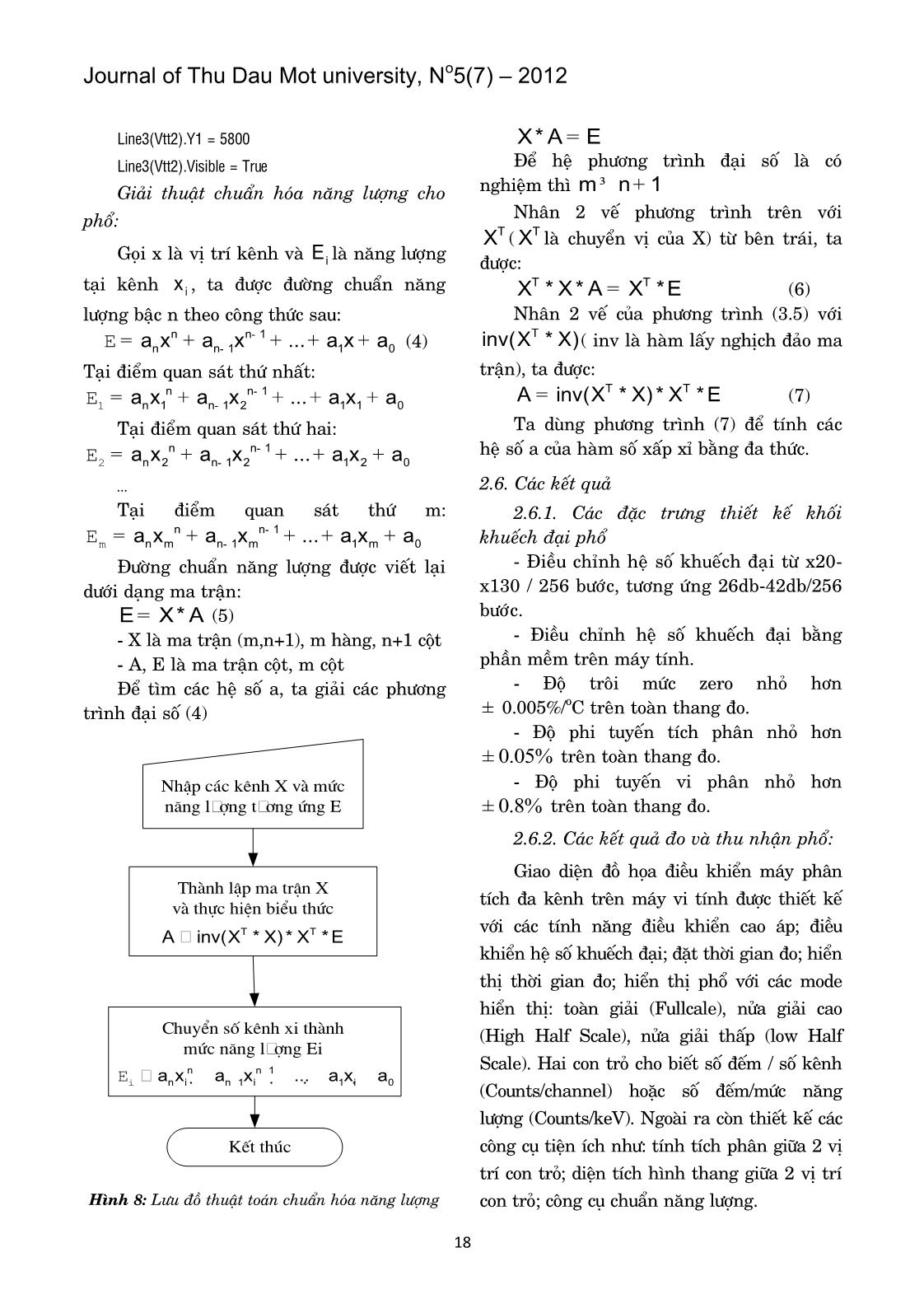

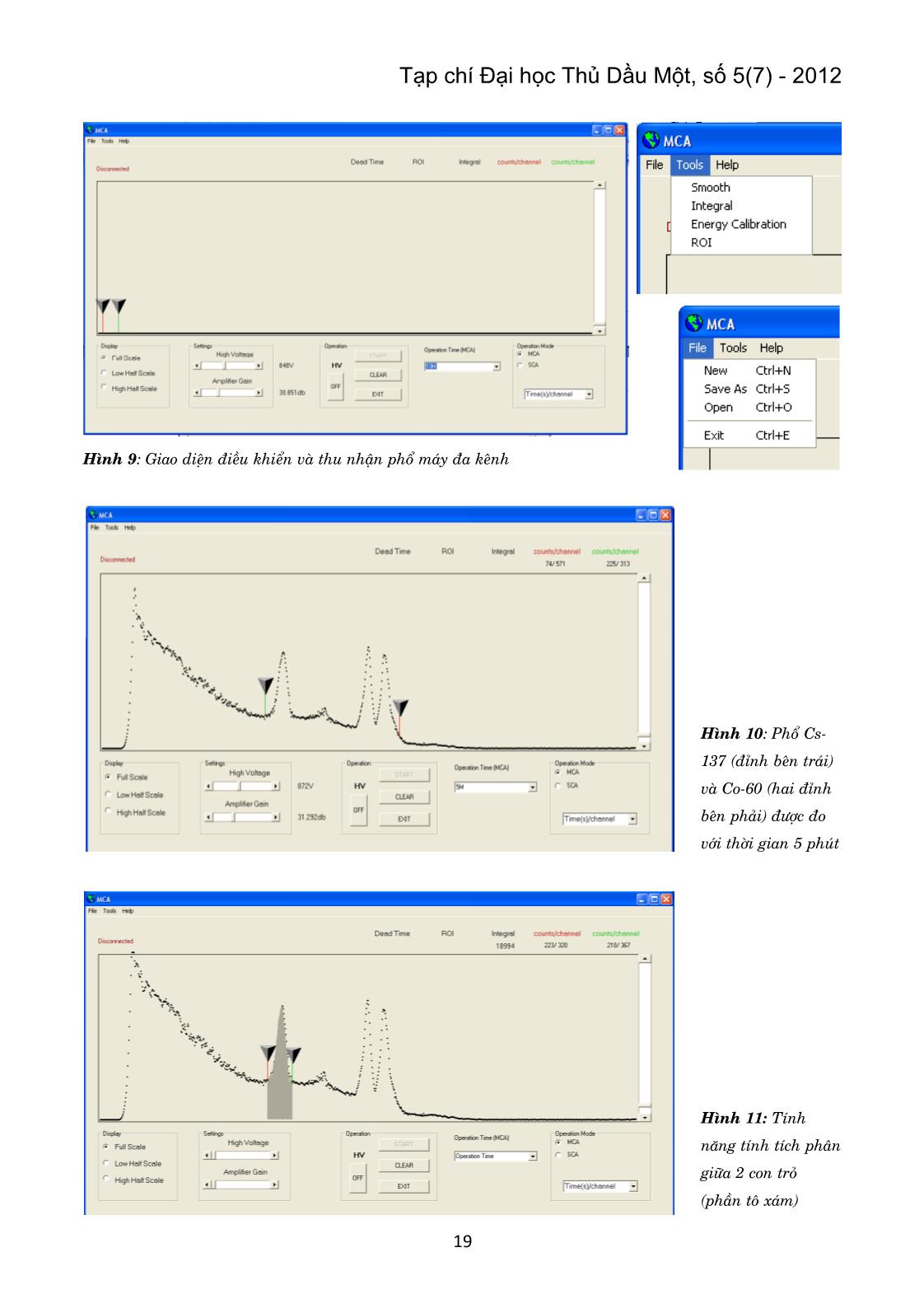

ot university, No5(7) – 2012 thay đổi và lấy từ board logic (tại chân điện trở lấy mẫu dòng R21; khuếch đại so CTL-HV). Điện áp lối ra khuếch đại so sánh U3D. sánh được đệm nhờ Q1 và Q2 để cấp điện Khi có hiện tượng quá dòng, lối ra U3D áp nuôi cho biến áp xung T1. lên cao làm Q5 dẫn, kéo điện thế nuôi cho Khối bảo vệ: Gồm bảo vệ quá cao áp và biến áp T1 về không. bảo vệ quá dòng cho 2 MOSFET. Khối bảo Các đặc trưng kĩ thuật thiết kế khối vệ quá cao áp gồm: khuếch đại đệm U2C; nguồn cao áp: khuếch đại so sánh U3B và transistor Q5. - Điện áp ra từ 0V đến 2 kV trên 256 bước. Khi điện áp cao áp lối ra cao quá mức qui - Dòng cao áp cực đại là 10mA tại định, lối ra U3B lên mức cao làm Q5 dẫn, 2000V, có nghĩa công suất cực đại nguồn kéo điện thế nuôi cho biến áp T1 về không, cao áp là 10VA. đồng thời LED D5 sáng báo có sự cố bảo - Đổi cực tính nguồn cao áp bằng bộ vệ. Bảo vệ quá dòng cho MOSFET gồm: chuyển cơ khí. Hình 5: Sơ đồ nguyên lí khối cao thế 2.4. Khối nguồn nuôi điện áp thấp tạo thành bộ lọc điện lưới (line filter). Chỉnh Sơ đồ nguyên lí trên hình 6. Khối nguồn lưu 2 bán kì điện áp dương: D14; D15; C29. nuôi điện áp thấp được xây dựng trên biến Ổn áp 12V, 5V nhờ IC U11 và U12. Chỉnh áp hạ áp T2 220VAC/15VAC, 15VAC, 40VA lưu 2 bán kì điện áp âm: D16; D17; C30. Ổn . Các linh kiện R38, R39, T3,C26, C27, C28 áp -12V nhờ IC U13. 14 Tạp chí Đại học Thủ Dầu Một, số 5(7) - 2012 OUTPUT 12V U11 U12 D14 1N4007 LM7812 LM7805 C27 15VAC 1 3 1 3 OUTPUT 5V R38 VI VO VI VO C31 C33 GND 1 T2 5 C29 GND 8 5 D15 1N4007 2 C26 T3 6 0VAC 2 220VAC 4 8 D16 1N4007 C32 4 1 C30 2 R39 C28 1 3 OUTPUT -12V 15VAC VI VO D17 1N4007 GND LM7912 U13 Hình 6: Sơ đồ nguyên lí nguồn nuôi điện áp thấp 2.5. Giải thuật điều khiển, thu nhận Điều khiển điện áp cao áp: Khi vi điều phổ và các công cụ tiện ích khiển nhận byte thứ nhất là số 2, byte thứ là Giải thuật đóng – mở và điều khiển con số 0-255, vi điều khiển lấy dữ liệu ở byte điện áp cao áp, điều khiển hệ số khuếch đại thứ hai điều khiển biến trở số U9-MCP41010 khối khuếch đại: bằng giao thức SPI (tại mạch logic). Máy vi tính điều khiển cho vi điều MCP41010 là biến trở số 10KW. Khi dữ liệu khiển tại máy phân tích bằng cách gửi 2 byte thứ hai là 255, điểm giữa W của biến trở byte qua cổng USB, byte thứ nhất tạm gọi số đi về điểm A và có điện thế bằng 5V, điện là mã lệnh để ra lệnh cho vi điều khiển thế lối ra này được đệm bởi U10-LM324 (tại làm công việc gì, byte thứ 2 là dữ liệu công mạch logic) tương ứng với điện thế cao áp lối việc cần điều khiển. Sau đây là bảng tổng ra cực đại là 2kV. Từ 0V đến 2KV được chia kết qui ước các byte điều khiển chuyển từ thành 255 bước, mỗi bước ứng với 8V. máy tính đến vi điều khiển. Điều khiển hệ số khuếch đại khối khuếch Công việc điều Byte thứ nhất Byte thứ hai đại: Khi vi điều khiển nhận byte thứ nhất là khiển (mã lệnh) (dữ liệu) số 3, byte dữ liệu thứ hai vi điều khiển dùng để (dạng số thập (dạng số thập điều khiển biến trở số MCP41010 (tại mạch phân) phân) khuếch đại phổ). Hệ số truyền của biến trở số Đóng – mở cao áp 01 0: tắt cao áp tính theo công thức sau: 1: mở cao áp R A = WA (1) Điều khiển điện áp 02 0 - 255 V R AB cao áp Giải thuật hiển thị phổ: Một điểm phổ Điều khiển hệ số 03 0-255 tượng trưng bởi một điểm (Shape1(i)), độ cao khuếch đại khối khuếch đại là hàm của số đếm M(i) và giá trị thanh Bảng 1: Bảng tổng kết qui ước các byte điều khiển cuốn Vscroll1, đoạn mã nguồn hiển thị phổ: chuyển từ máy tính đến vi điều khiển For i=0 to 1023 Shape1(i).top=5800 – Vscroll1.Value*M(i) Đóng – mở cao áp: Khi vi điều khiển Shape1(i).Left = 400 + i * 15 nhận byte thứ nhất số 01, byte thứ hai số Next 0, vi điều khiển xuất ra mức cao bit RD5 Hai con trỏ có hình mũi tên (Image1 và làm Q5 (mạch cao thế) dẫn, kéo theo Q1, Image2), con trỏ này chạy theo con trỏ Q2 ngưng dẫn làm mất điện áp nuôi cho chuột máy tính khi kích chuột trái. Sau đây biến áp xung T1 (mạch cao thế) và tắt cao là đoạn mã nguồn di chuyển con trỏ 1: áp. Ngược lại, byte thứ hai số 1, vi điều If Button = 1 Then khiển xuất ra mức thấp bit RD5 làm Q5 If ((Image1.Left >= 200) And (Image1.Left <= 15600)) Then ngưng, kéo theo Q1, Q2 dẫn, có điện áp Image1.Move Image1.Left + x - 180, 5000 'Image2.Top + Y – nuôi cho biến áp xung T1, có cao áp. 100 15 Journal of Thu Dau Mot university, No5(7) – 2012 End if - Yn,m (i) là đạo hàm bậc n của phổ làm End if Giải thuật làm trơn phổ: Mỗi đoạn phổ trơn tại kênh i; ngắn có thể xem như một đa thức toán học. - y(i+ k) là số đếm tại kênh thứ (i+k); Giá trị của đa thức và đạo hàm của nó có - Ck,n,m và Nn,m là các hằng số cho thể xem như là hàm của số đếm trong mỗi trong bảng (2); kênh của phổ và cho bởi công thức sau: - m liên hệ với số điểm làm trơn m’ là: 1 m m’= 2m+1 Yn,m (i)=+å C k,n,m y(i k) (2) Nn,m km=- Số điểm tối ưu dùng làm trơn phụ thuộc Với: vào dạng cụ thể của vùng phổ đang xét. r n m’ k Nn,m 0 1 2 3 4 5 6 7 Ck,n,m 2 0 5 35 17 12 -3 3 7 21 7 6 3 -2 9 231 59 54 39 14 -21 Ck,n,m 11 429 89 84 69 44 9 -36 13 143 25 24 21 16 9 0 -11 15 1105 167 162 147 122 87 42 -13 -78 2 1 5 10 0 1 2 7 28 0 1 2 3 9 60 0 1 2 3 4 Ck,n,m 11 110 0 1 2 3 4 5 13 182 0 1 2 3 4 5 6 15 280 0 1 2 3 4 5 6 7 3 1 5 12 0 8 -1 7 252 0 58 67 -22 9 1188 0 126 193 142 -86 11 5148 0 296 503 532 294 -300 13 24024 0 832 1489 1796 1578 660 -1133 15 334152 0 7506 13843 17842 18334 14150 4121 -12922 2 2 5 7 -2 -1 3 7 42 -4 -3 9 462 -20 -17 11 429 -10 -9 13 1001 -14 -13 15 6188 -56 -53 Bảng 2: Các hệ số Nn,m và Ck,n,m Với r là bậc của đa thức làm khớp -0.1; 3/21 = 0.14; 6/21 = 0.29; 7/21 = 0.33; m’=2m+1. Ví dụ: 6/21 = 0.29; 3/21 = 0.14; -2/21 = -0.1 - Làm trơn cửa sổ 5 điểm, bậc 2: r = 2, - Làm trơn cửa sổ 9 điểm, bậc 3: r=3, n=0, m’ = 5, ta có các hệ số làm trơn là: - n=0, m’=9, các hệ số làm trơn là: 3/35 = -0.09; 12/35 = 0.34; 17/35 = 0.48; - 21/231 = -0.09; 14/231 = 0.06; 39/231 12/35 = 0.34; -3/35 = -0.09 = 0.17; 54/231 = 0.23; 59/231 = 0.26 - Làm trơn cửa sổ 7 điểm, bậc 3: r = 3, - 54/231 = 0.23; 39/231 = 0.17; 14/231 = n = 0, m’ = 7, các hệ số làm trơn là: -2/21 = 0.06; -21/231 = -0.09 16 Tạp chí Đại học Thủ Dầu Một, số 5(7) - 2012 Khëi t¹o: i= 0 i=i+1 SPL(i)=-0.09*M(i)+0.34*M(i+1)+0.48*M(i+2)+0.34*M(i+3)-0.09*M(i+4) N i>1019 Y SPL(0) = 0.48*M(0)+0.68*M(1)-0.18*(M2) SPL(1) = 0.34*M(0)+0.48*M(1)+0.34*M(2)-0.18*M(3) SPL(1022)=-0.18*M(1020)+0.34*M(1021)+0.48*M(1022)+0.34*M(1023) SPL(1023) = -0.18*M(1021)+0.68*M(1022)+0.48*M(1023) Dõng Hình 7: Lưu đồ thuật toán làm trơn phổ Giải thuật lấy tích phân số đếm và Giải thuật lấy diện tích hình thang: hiển thị miền lấy tích phân: Tích phân giữa Diện tích hình thang giữa 2 vị trí con trỏ 2 vị trí con trỏ là tổng các số đếm của các M(vtt1)+ M(vtt2) DTHT= (vtt2 - vtt1 + 1) (3) kênh giữa 2 vị trí con trỏ. Gọi vtt1 là kênh 2 của con trỏ bên trái và gọi vtt2 là kênh của Hiển thị diện tích hình thang: con trỏ bên phải, sau đây là đoạn mã nguồn ‘ line4: đoạn thẳng nối giữa 2 con trỏ lấy tích phân Line4.X1 = Shape1(Vtt1).Left ‘ INTEGRAL: tích phân số đếm Line4.X2 = Shape1(Vtt2).Left For i=vtt1 to vtt2 Line4.Y1 = Shape1(Vtt1).Top INTEGRAL=INTEGRAL+M(i) Line4.Y2 = Shape1(Vtt2).Top Next Hiển thị miền lấy tích phân bằng cách Line4.Visible = True vẽ các đoạn thẳng từ điểm phổ xuống chân ‘ line3(Vtt1): đoạn thẳng nối từ chân đồ thị lên con trỏ 1 đồ thị, sau đây là đoạn mã nguồn hiển thị Line3(Vtt1).X1 = Shape1(Vtt1).Left miền lấy tích phân Line3(Vtt1).X2 = Shape1(Vtt1).Left For i = Vtt1 To Vtt2 Line3(Vtt1).Y2 = Shape1(Vtt1).Top Line3(i).X1 = Shape1(i).Left Line3(Vtt1).Y1 = 5800 Line3(i).X2 = Shape1(i).Left Line3(Vtt1).Visible = True Line3(i).Y1 = 5800 ‘ 5800 là chân đồ thị ‘ line3(Vtt2): đoạn thẳng nối từ chân đồ thị lên con trỏ 2 Line3(i).Y2 = 5800 - VScroll1.Value * M(i) Line3(Vtt2).X1 = Shape1(Vtt2).Left Line3(i).Visible = True Line3(Vtt2).X2 = Shape1(Vtt2).Left Next Line3(Vtt2).Y2 = Shape1(Vtt2).Top 17 Journal of Thu Dau Mot university, No5(7) – 2012 Line3(Vtt2).Y1 = 5800 X*AE= Line3(Vtt2).Visible = True Để hệ phương trình đại số là có Giải thuật chuẩn hóa năng lượng cho nghiệm thì m³+ n 1 phổ: Nhân 2 vế phương trình trên với XT ( XT là chuyển vị của X) từ bên trái, ta Gọi x là vị trí kênh và E là năng lượng i được: TT tại kênh x i , ta được đường chuẩn năng X*X*AX*E= (6) lượng bậc n theo công thức sau: Nhân 2 vế của phương trình (3.5) với n n- 1 T E =an x + a n- 1 x + ... + a 1 x + a 0 (4) inv(X * X)( inv là hàm lấy nghịch đảo ma Tại điểm quan sát thứ nhất: trận), ta được: n n- 1 A= inv(XTT * X) * X * E (7) E1 =an x 1 + a n- 1 x 2 + ... + a 1 x 1 + a 0 Tại điểm quan sát thứ hai: Ta dùng phương trình (7) để tính các n n- 1 hệ số a của hàm số xấp xỉ bằng đa thức. E2 =an x 2 + a n- 1 x 2 + ... + a 1 x 2 + a 0 2.6. Các kết quả Tại điểm quan sát thứ m: 2.6.1. Các đặc trưng thiết kế khối n n- 1 Em =an x m + a n- 1 x m + ... + a 1 x m + a 0 khuếch đại phổ Đường chuẩn năng lượng được viết lại - Điều chỉnh hệ số khuếch đại từ x20- dưới dạng ma trận: x130 / 256 bước, tương ứng 26db-42db/256 EX*A= (5) bước. - X là ma trận (m,n+1), m hàng, n+1 cột - Điều chỉnh hệ số khuếch đại bằng - A, E là ma trận cột, m cột phần mềm trên máy tính. Để tìm các hệ số a, ta giải các phương - Độ trôi mức zero nhỏ hơn o trình đại số (4) ± 0.005%/ C trên toàn thang đo. - Độ phi tuyến tích phân nhỏ hơn ± 0.05% trên toàn thang đo. NhËp c¸c kªnh X vµ møc - Độ phi tuyến vi phân nhỏ hơn n¨ng l•ỵng t• ¬ng øng E ± 0.8% trên toàn thang đo. 2.6.2. Các kết quả đo và thu nhận phổ: Giao diện đồ họa điều khiển máy phân Thµnh lËp ma trËn X tích đa kênh trên máy vi tính được thiết kế vµ thùc hiƯn biĨu thøc với các tính năng điều khiển cao áp; điều A inv(XTT *X)*X *E khiển hệ số khuếch đại; đặt thời gian đo; hiển thị thời gian đo; hiển thị phổ với các mode hiển thị: toàn giải (Fullcale), nửa giải cao ChuyĨn sè kªnh xi thµnh (High Half Scale), nửa giải thấp (low Half møc n¨ng l •ỵng Ei n n 1 Scale). Hai con trỏ cho biết số đếm / số kênh Ei an x i a n 1 x i ... a 1 x i a 0 (Counts/channel) hoặc số đếm/mức năng lượng (Counts/keV). Ngoài ra còn thiết kế các KÕt t hĩc công cụ tiện ích như: tính tích phân giữa 2 vị trí con trỏ; diện tích hình thang giữa 2 vị trí Hình 8: Lưu đồ thuật toán chuẩn hóa năng lượng con trỏ; công cụ chuẩn năng lượng. 18 Tạp chí Đại học Thủ Dầu Một, số 5(7) - 2012 Hình 9: Giao diện điều khiển và thu nhận phổ máy đa kênh Hình 10: Phổ Cs- 137 (đỉnh bên trái) và Co-60 (hai đỉnh bên phải) được đo với thời gian 5 phút Hình 11: Tính năng tính tích phân giữa 2 con trỏ (phần tô xám) 19 Journal of Thu Dau Mot university, No5(7) – 2012 Hình 12: Tính năng tính diện tích hình thang giữa 2 con trỏ Hình 13: Phổ CS-137 đã làm trơn 1 lần với cửa sổ 3 điểm Hình 14: Công cụ chuẩn hóa năng lượng cho phổ Hình 15: Hình ảnh bên trong và bên ngoài máy phân tích đa kênh đã thiết kế và chế tạo 20 Tạp chí Đại học Thủ Dầu Một, số 5(7) - 2012 3. Kết luận phân tích đa kênh Series 30 của - Máy phân tích đa kênh (1024 kênh) CANBERRA. được thiết kế với các đặc trưng căn bản cho - Máy có thể sử dụng cho sinh viên tại thấy tương đương với các đặc trưng của máy các phòng thí nghiệm vật lí hạt nhân. * DESIGNING AND PRODUCING THE MULTI-CHANNEL ANALYSING MACHINE COMBING COMPUTERS THROUGH USB GATE Nguyen Van Son Thu Dau Mot University ABSTRACT This paper introduces the design of hardware and software algorithms multichannel analyzer connected with computer via USB port that is a feasible and inexpensive to manufacture multi-channel analyzer. Hardware: Design and fabrication of functional blocks of multi-channel analyzer includes: spectral amplifier; ADC control; high-voltage power supply; USB interface; low voltage power supply. The software consists of a control algorithm and data acquisition computer and the essential tools of multi-channel analyzer. The basic specifications of manufactured multi-channel analyzer were measured: The energy resolution is less than 39keV at peak Cs-137 664 KeV using CANBERRA Bicron model 302-2x2 scintillation detector; The peak drift is less than ±0.01%/oC of full scale; The integral nonlinearity is less than ±0.05% over total output range; The differential nonlinearity is less than ±3.4 over total output range. For technical characteristics mentioned above, the machine was designed and built can be used by students to practice nuclear physics. TÀI LIỆU THAM KHẢO [1]. Datasheet PIC18F4550 tại [2]. Jan Axelson (2005), USB Complete (3th Edition), Lakeview Reasearch LLC, Madison. [3]. Genie-2000 Spectrocopy System, Canberra Industries. [4]. Các tài liệu tại [5]. Kenneth L. Short, Microprocessors and Programmed Logic, Prentice-Hall, INC, Englewood Cliffs, New Jersey 07632. [6]. Analog to digital converter 7070-CANBERRA. [7]. Analog to digital converter 8075-CANBERRA. [8]. SPECTROSCOPE AMPLIFIER 2021-CANBERRA. [9]. Bùi Quang Khánh (2009), Xử lí phổ gamma bằng thuật toán di truyền, luận văn thạc sĩ vật lí Trường Đại học Khoa học Tự nhiên – Đại học Quốc gia TPHCM. [10]. Đỗ Công Khanh, Nguyễn Minh Hằng, Ngô Thu Lương (2004), Toán cao cấp – Đại số tuyến tính, NXB Đại học Quốc gia TPHCM. [11]. Millman-Halkias (1972), Integrated Electronics: Analog and Digital Circuits and Systems, McGRAW-HILL. 21

File đính kèm:

thiet_ke_va_che_tao_may_phan_tich_da_kenh_ghep_may_tinh_qua.pdf

thiet_ke_va_che_tao_may_phan_tich_da_kenh_ghep_may_tinh_qua.pdf