Giáo trình Kiến trúc máy tính & Quản lý hệ thống máy tính (Phần 1)

1. Một số phần tử Logic cơ bản

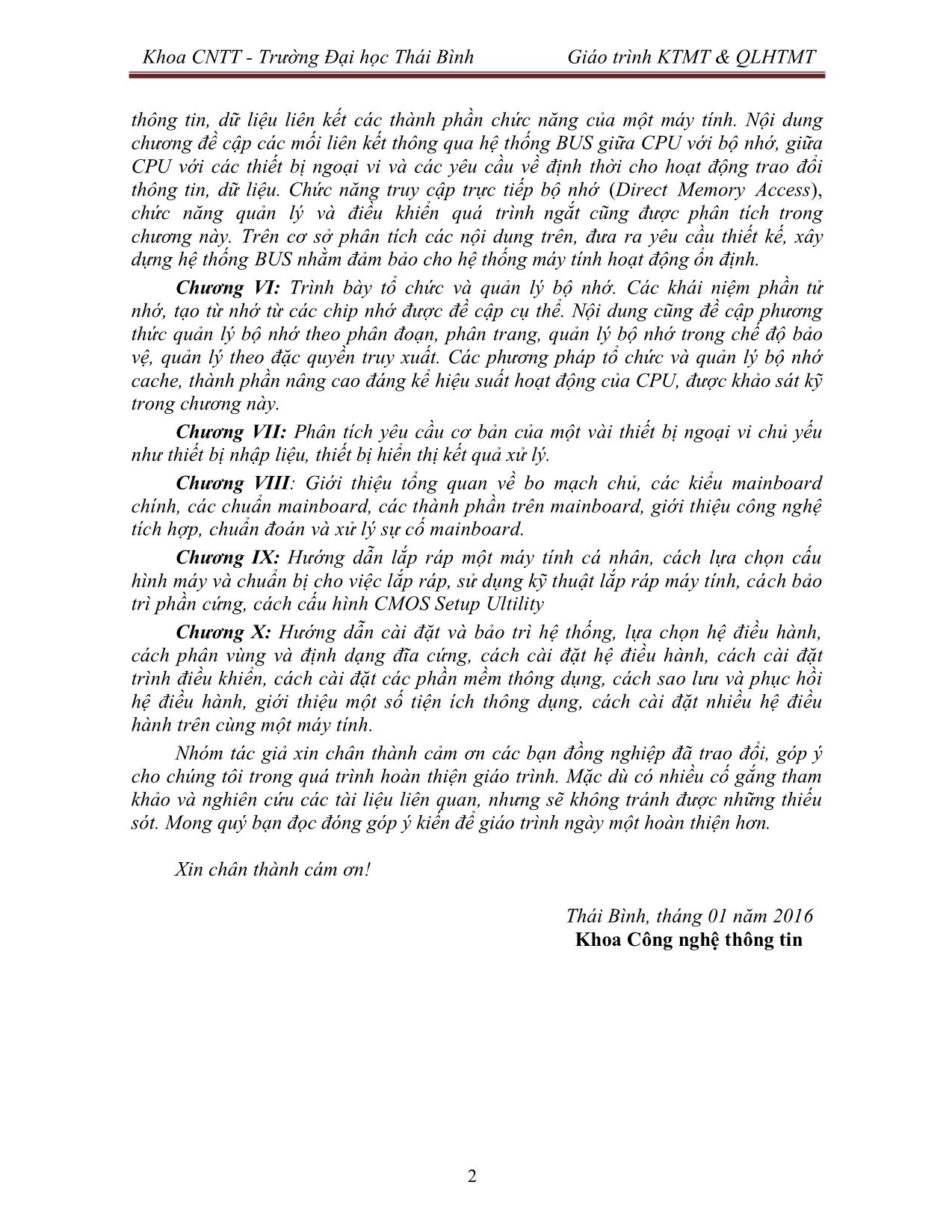

Các mạch logic cơ bản được tạo ra từ liên kết các phần tử điện tử thông

dụng là transistor, diode, điện trở, tụ điện, Tuỳ theo công nghệ chế tạo các phần

tử đó mà chúng có những tên gọi khác nhau như logic TTL, logic CMOS, logic

HMOS, logic MOSFET v.v Hình I.1 cho ta thấy cấu trúc mạch nguyên lý của

một phần tử TTL thực hiện chức năng đảo tích logic của hai giá trị đầu vào

(NAND).

Hình I.1. Sơ đồ nguyên lý mạch tạo phần tử NAND

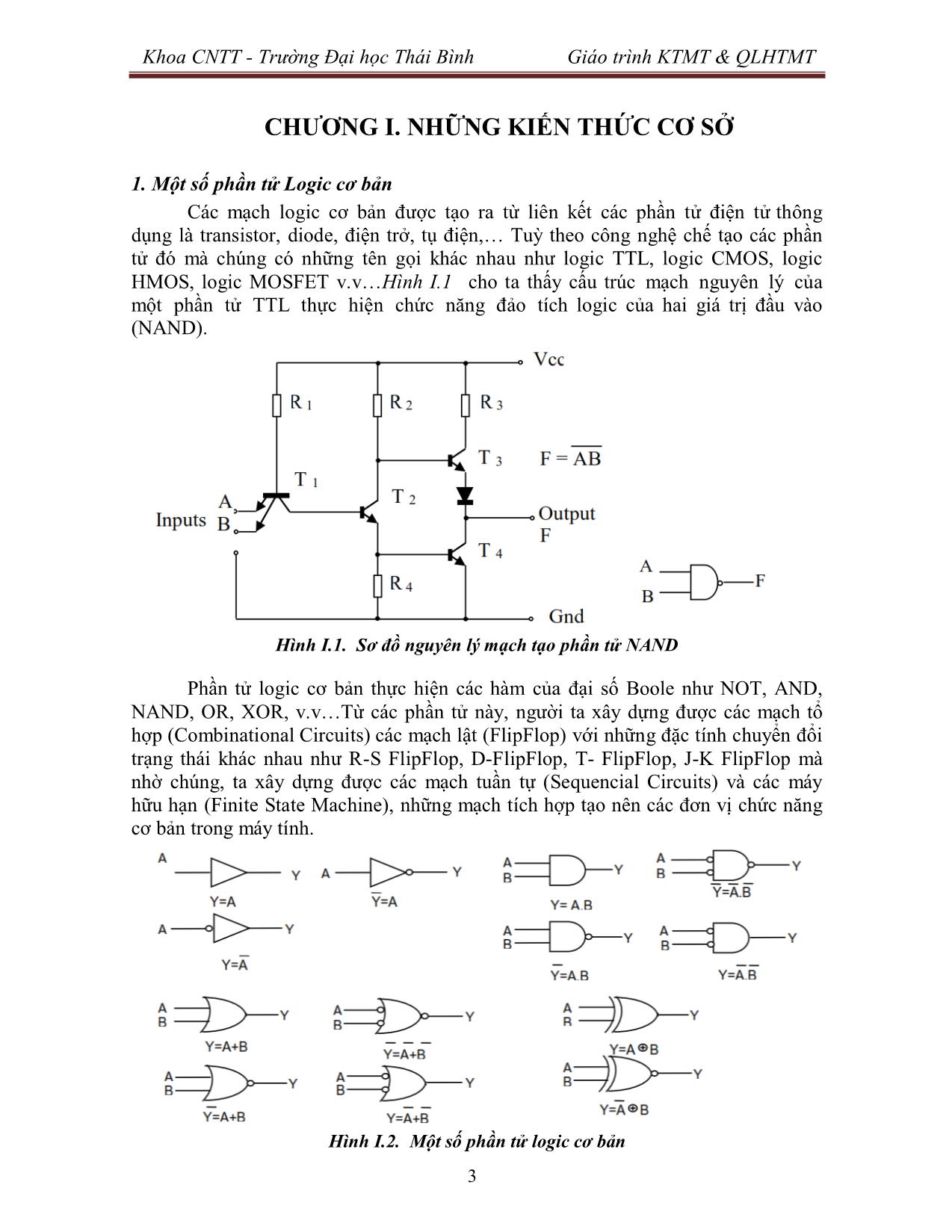

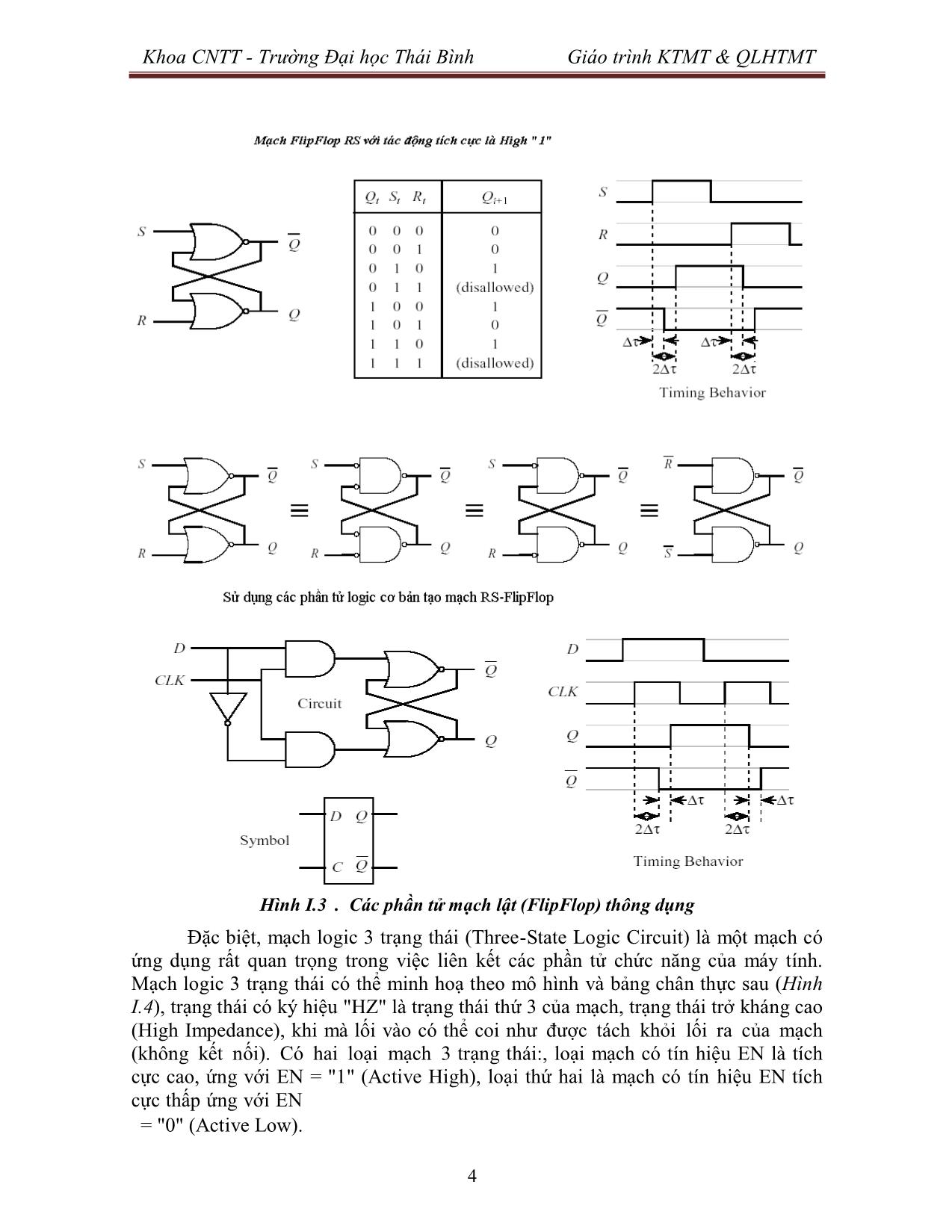

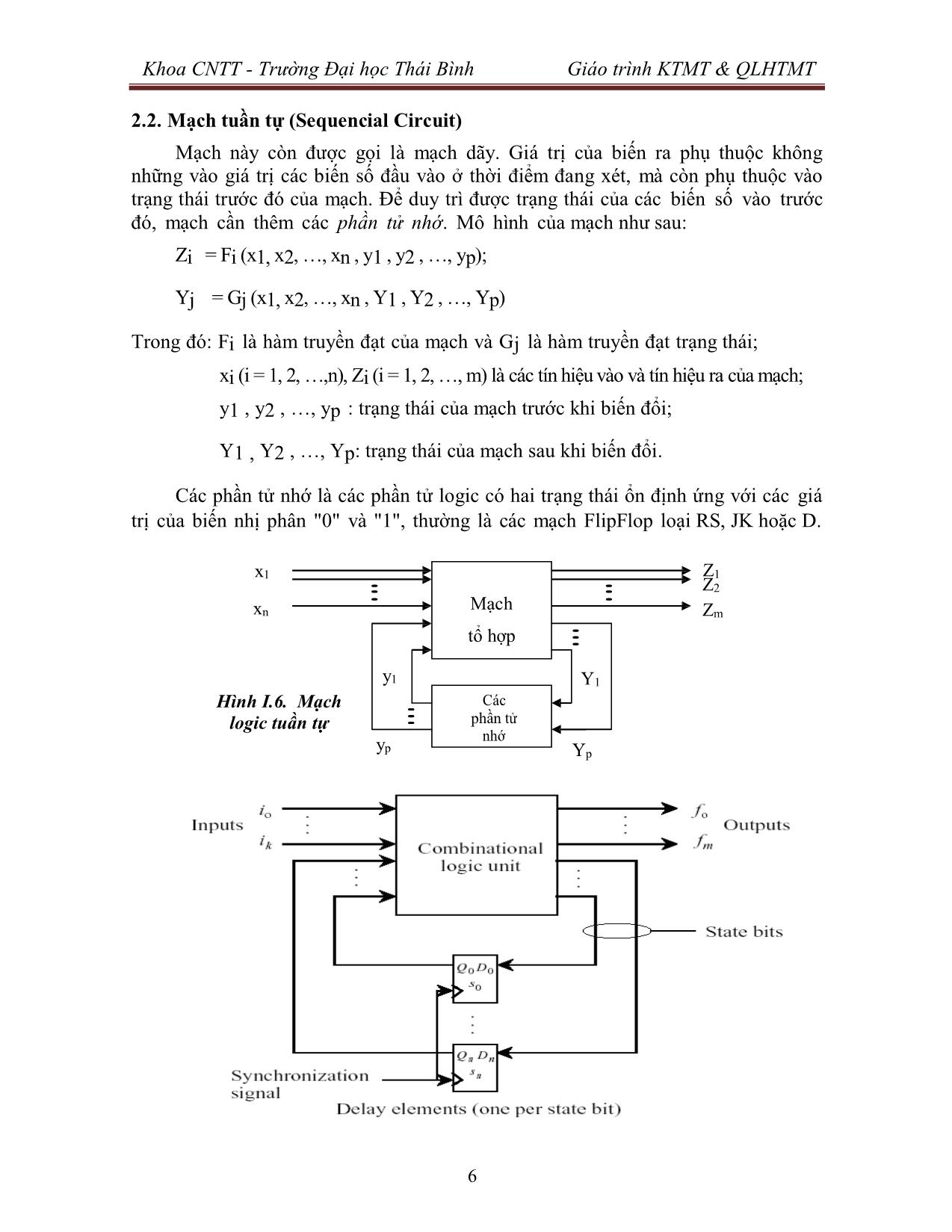

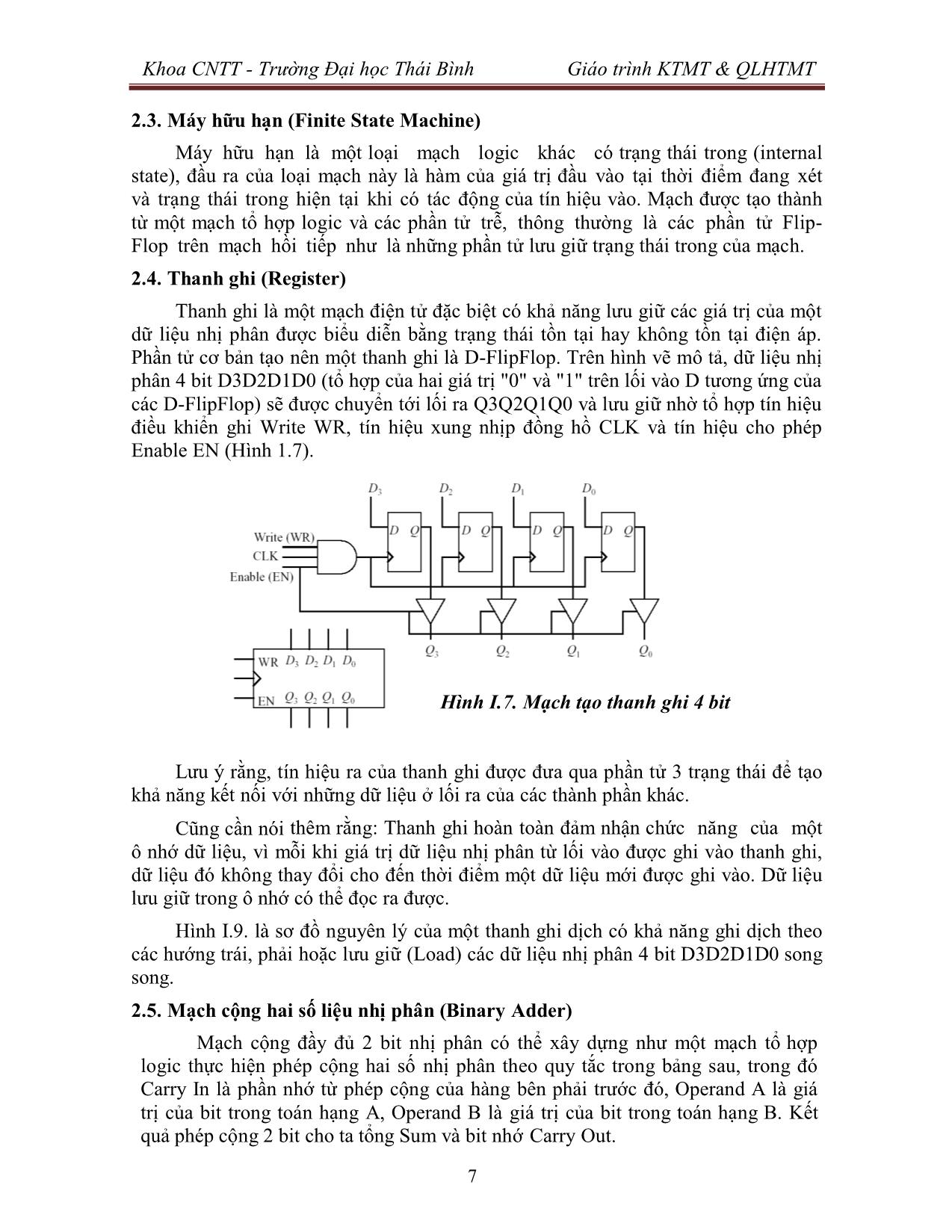

Phần tử logic cơ bản thực hiện các hàm của đại số Boole như NOT, AND,

NAND, OR, XOR, v.v Từ các phần tử này, người ta xây dựng được các mạch tổ

hợp (Combinational Circuits) các mạch lật (FlipFlop) với những đặc tính chuyển đổi

trạng thái khác nhau như R-S FlipFlop, D-FlipFlop, T- FlipFlop, J-K FlipFlop mà

nhờ chúng, ta xây dựng được các mạch tuần tự (Sequencial Circuits) và các máy

hữu hạn (Finite State Machine), những mạch tích hợp tạo nên các đơn vị chức năng

cơ bản trong máy tính.

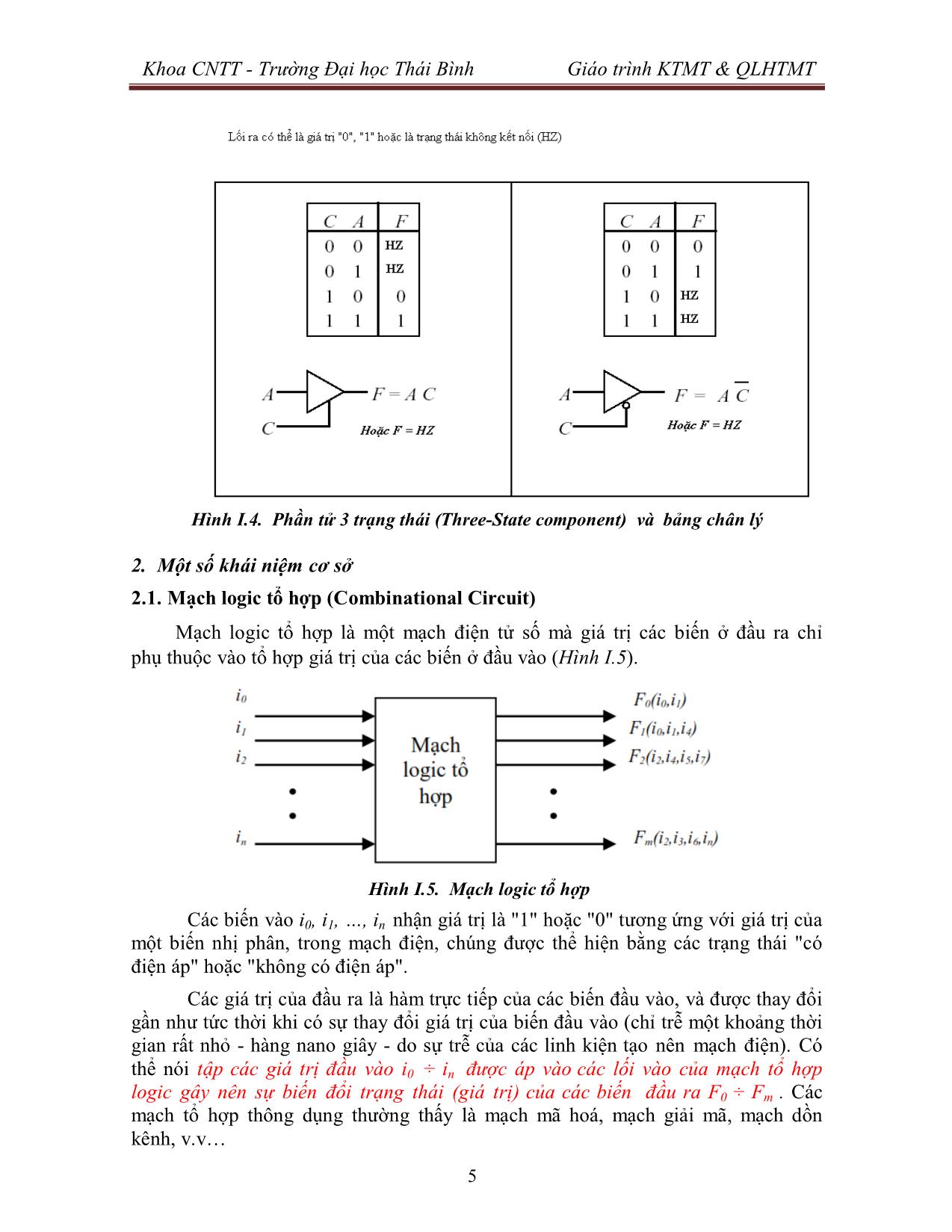

Đặc biệt, mạch logic 3 trạng thái (Three-State Logic Circuit) là một mạch có

ứng dụng rất quan trọng trong việc liên kết các phần tử chức năng của máy tính.

Mạch logic 3 trạng thái có thể minh hoạ theo mô hình và bảng chân thực sau (Hình

I.4), trạng thái có ký hiệu "HZ" là trạng thái thứ 3 của mạch, trạng thái trở kháng cao

(High Impedance), khi mà lối vào có thể coi như được tách khỏi lối ra của mạch

(không kết nối). Có hai loại mạch 3 trạng thái:, loại mạch có tín hiệu EN là tích

cực cao, ứng với EN = "1" (Active High), loại thứ hai là mạch có tín hiệu EN tích

cực thấp ứng với EN

= "0" (Active Low).

Trang 1

Trang 2

Trang 3

Trang 4

Trang 5

Trang 6

Trang 7

Trang 8

Trang 9

Trang 10

Tải về để xem bản đầy đủ

Tóm tắt nội dung tài liệu: Giáo trình Kiến trúc máy tính & Quản lý hệ thống máy tính (Phần 1)

để tính được địa chỉ vật lý của ô nhớ được xác định bởi nội dung thanh ghi đoạn và nội dung thanh ghi offset, ta thực hiện phép dịch trái nội dung thanh ghi đoạn 4 bit rồi tiến hành cộng với nội dung thanh ghi offset như được biểu diễn trong hình vẽ dưới đây, và phép tính được biểu diễn theo biểu thức sau: Địa chỉ vật lý = (Nội dung thanh ghi đoạn) x 10H + (Nội dung thanh ghi offset) Mỗi thanh ghi con trỏ và chỉ số đều được gán một chức năng cụ thể, và cùng với một thanh ghi đoạn tương ứng, tạo thành địa chỉ logic của những đoạn nhớ theo chức năng trong bộ nhớ. Thanh ghi chỉ số nguồn SI và thanh ghi chỉ số đích DI là những thanh ghi được sử dụng trong các thao tác xử lý xâu, chuỗi . 7.2. Quản lý bộ nhớ, các mode địa chỉ trong CPU 8086 a. Phương thức quản lý bộ nhớ trong CPU8086: BUS địa chỉ của µP8086 có độ dài 20 bits, do vậy có thể quản lý được 220 = 1M ô nhớ (Mỗi tổ hợp “0” hoặc “1” của các bit trong 20 bits địa chỉ xác định vị trí của một ô nhớ). Vì một ô nhớ trong hệ Vi xử lý là 1 Byte, nên nói cách khác, không gian nhớ mà µP8086 quản lý được là 1Mbyte. Hình IV.13. Cách chia đoạn nhớ trong µP8086 95 Khoa CNTT - Trường Đại học Thái Bình Giáo trình KTMT & QLHTMT Các thanh ghi của µP8086 chỉ có độ dài 16 bits, nên nếu dùng một thanh ghi để đánh địa chỉ thì chỉ quản lý được 216 ô nhớ, tức là 64KB. Để giải quyết vấn đề quản lý 1MByte, tức là 1.048.576 Bytes, µP8086 sử dụng BUS địa chỉ có độ rộng 20 bits thông qua nội dung của hai thanh ghi 16 bits để đánh địa chỉ của bộ nhớ theo phương thức sau: Bằng cách lập chương trình, không gian địa chỉ được chia thành các đoạn (segment) nhớ với kích thước cố định là 64Kbytes gọi là một đơn vị logic của bộ nhớ. Mỗi đoạn gồm các ô nhớ liên tiếp, độc lập và được định vị tách rời nhau. Mỗi đoạn được người lập trình gán cho một địa chỉ đoạn, là địa chỉ ô nhớ đầu tiên của đoạn đó, còn được gọi là địa chỉ nền.Giá trị của các địa chỉ đoạn liền kề cách nhau tối thiểu là 16 Bytes. Các đoạn có thể kế cận, tách rời, phủ lấp nhau. Bên trong đoạn sẽ sử dụng các giá trị lệch (offset), tức là khoảng cách từ địa chỉ đoạn đến ô nhớ nằm trong đoạn. Một cặp giá trị địa chỉ đoạn và giá trị lệch, [segment]:[offset], được gọi là địa chỉ logic. Địa chỉ logic cho phép định vị chính xác một Byte nhớ trong không gian địa chỉ. Địa chỉ đoạn được chứa trong các thanh ghi đoạn, giá trị dịch chuyển được chứa trong các thanh ghi đa năng, con trỏ hoặc chỉ số. Về bản chất, thanh ghi đoạn chứa 16 bits cao của 20 bits dịa chỉ, giá trị dịch chuyển là 16 bit thấp, và sự lệch nhau 4 bits đã được đơn vị địa chỉ của BIU giải quyết như trình bày trong hình IV.14: Dịch trái thanh ghi đoạn 4 bits (tương đương phép nhân với 16, cộng với giá trị dịch chuyển offset trong thanh ghi đa năng để tính địa chỉ vật lý của ô nhớ. Như đã trình bày ở trên, công thức tương ứng phép “dịch trái và cộng” có thể trình bày như trên hình vẽ sau, việc tính toán này do đơn vị giao diện BUS đảm nhận (BIU – BUS Interface Unit) Địa chỉ vật lý = 10H x (segment) + (offset) Hình IV.14. 96 Khoa CNTT - Trường Đại học Thái Bình Giáo trình KTMT & QLHTMT Thanh ghi đoạn là một thanh ghi 16 bits, có nhiệm vụ xác định đoạn của ô nhớ, còn thanh ghi đa năng cũng là một thanh ghi 16 bits. Vậy thanh ghi đoạn có thể địnhđược 216 = 65.536 đơn vị (64K) đoạn nhớ và mỗi đoạn có 64Kbytes. Vậy Vi xử lý µP8086 có thể định địa chỉ tới 64K x 64Kbytes = 4Gbytes nhớ. Thanh ghi đoạn mã CS xác định đoạn nhớ chương trình mà lệnh kế tiếp sẽ được lấy để thực hiện, thanh ghi con trỏ IP chứa địa chỉ offset của lệnh kế tiếp. Cặp CS:IP tạo nên địa chỉ logic của lệnh kế tiếp trong tuần tự thực hiện chương trình. Các từ lệnh của họ 80x86 có thể có độ dài từ 1 byte đến tối đa là 15 bytes. Khi lệnh được thực hiện, giá trị của con trỏ IP do vậy sẽ tăng lên đúng bằng số Bytes của từ lệnh. Cần nhớ rằng nội dung của thanh ghi con trỏ lệnh IP cùng với nội dung thanh ghi đoạn CS xác định địa chỉ của ô nhớ lệnh tiếp theo trong tuần tự thực hiện chương trình. b. Mode địa chỉ trực tiếp 1. Mode định vị thanh ghi (register addressing): Toán hạng được truy xuất là nội dung thanh ghi của CPU. Thí dụ: MOV AX, BX ; chuyển nội dung của toán hạng nguồn (nội dung của thanh ghi) BX vào toán hạng đích AX. Nội dung thanh ghi BX vẫn được giữ nguyên. 2. Mode định vị tức thời (immediate addressing): Toán hạng tức thời là dữ liệu 8 hay 16 bits nằm ngay trong lệnh, có thể dùng làm toán hạng nguồn hay hằng số. Toán hạng tức thời được lưu giữ ngay trong đoạn mã của bộ nhớ, ngay sau mã lệnh, nó được lấy ra cùng với lệnh và ghi vào hàng đợi lệnh PQ, do vậy được truy xuất nhanh hơn so với truy xuất toán hạng từ bộ nhớ. Thí dụ: MOV AL, 12H ; nạp số 12H vào thanh ghi AL c. Các mode định vị gián tiếp Khác với hai kiểu định vị trên, toán hạng trong đoạn nhớ dữ liệu được CPU truy xuất qua BUS dữ liệu. Biết rằng, địa chỉ vật lý của ô nhớ được tính từ nội dung thanh ghi đoạn và offset theo cách trình bày trong Hình II. 18. Giá trị offset mà đơn vị thực hiện lệnh EU tính cho một toán hạng trong đoạn nhớ được gọi là địa chỉ hiệu dụng EA (effective address) của toán hạng. Đơn vị thực hiện lệnh có thể tính EA dựa vào cách mô tả địa chỉ trong phần toán hạng nguồn của lệnh. Ngoài giá trị trực tiếp, hoặc nội dung thanh ghi cơ sở hay thanh ghi chỉ số, khi cần còn có thể có một giá trị số có độ dài 8 bits hay 16 bits được cộng thêm vào gọi là giá trị dịch chuyển dp (displacement). 97 Khoa CNTT - Trường Đại học Thái Bình Giáo trình KTMT & QLHTMT Hình IV. 15. Mô tả cách xác định địa chỉ vật lý của ô nhớ càn truy xuất Cụ thể như sau: Định vị trực tiếp (direct addressing): Toán hạngchứa địa chỉ là một số nằm ngay trong lệnh. Địa chỉ đoạn hiện tại nằm trong thanh ghi đoạn DS Thí dụ: MOV CX,[1435H] ; chuyển nội dung ô nhớ có địa chỉ offset bằng 1435H trong đoạn số liệu hiện tại vào thanh ghi CX Định vị gián tiếp thanh ghi (register indirect): địa chỉ hiệu dụng EA là nội dung của một trong các thanh ghi BX, BP, SI hoặc DI Thí dụ: MOV AX, [SI] ; chuyển nội dung của ô nhớ trong đoạn số liệu hiện tại có địa chỉ offset là nội dung thanh ghi SI Định vị cơ sở (based addressing): EA là tổng của nội dung thanh ghi BX hoặc BP và giá trị dịch chuyển dp nếu có Thí dụ: MOV [BX] + dp, AL ; chuyển nội dung thanh ghi AL và ô nhớ có địa chỉ offset bằng tổng của nội dung thanh ghi BX và giá trị dịch chuyển dp 98 Khoa CNTT - Trường Đại học Thái Bình Giáo trình KTMT & QLHTMT Hình IV. 16. Hình vẽ mô tả phương thức quản lý bộ nhớ theo phân đoạn, cách xác định địa chỉ vật lý của ô nhớ từ địa chỉ logic. 99 Khoa CNTT - Trường Đại học Thái Bình Giáo trình KTMT & QLHTMT Định vị chỉ số (indexed addressing): EA là tổng của nội dung thanh ghi SI hoặc DI và giá trị dịch chuyển dp nếu có Thí dụ MOV AL,[SI] + dp ; chuyển nội dung ô nhớ có địa chỉ offset bằng tổng của nội dung thanh ghi SI và giá trị dịch chuyển dp vào thanh ghi AL Định vị chỉ số và cơ sở (indexed addressing): EA là tổng của nội dung các thanh ghi cơ sở, thanh ghi chỉ số và giá trị dịch chuyển dp nếu có Thí dụ MOV AH,[BX][SI] + dp ; chuyển nội dung ô nhớ có địa chỉ offset bằng tổng của nội dung thanh ghi BX, thanh ghi SI và giá trị dịch chuyển dp vào thanh ghi AH Định vị chuỗi (string addressing): dùng riêng cho xử lý chuỗi. CPU sẽ tự động sử dụng các thanh ghi chỉ số nguồn SI và thanh ghi chỉ số đích DI để chỉ đến các byte kế tiếp Thí dụ MOVS ; di chuyển chuỗi, nguồn tại vùng nhớ có địa chỉ đầu là DS : SI, đích là vùng nhớ có địa chỉ đầu DS : DI. Phương pháp đánh địa chỉ là cách thức kiến trúc máy tính chỉ ra phương thức xác định địa chỉ của một đối tượng mà các thành phần khác muốn truy cập. 7.3. Biểu diễn lệnh và dữ liệu Máy tính hiện nay thường có: Bộ nhớ được chia thành các từ 8 bit, mỗi từ ứng với một địa chỉ trong bộ nhớ. Các lệnh có độ dài (số bit) thay đổi nhưng là bội số của 8. Các từ chứa dữ liệu cũng có độ dài (số bit) thay đổi và cũng là bội số của 8. Trong kiến trúc của nhiều máy tính các từ chứa dữ liệu có độ dài 16, 32, thậm chí tới 64 bit. 100 Khoa CNTT - Trường Đại học Thái Bình Giáo trình KTMT & QLHTMT 7.4. Yêu cầu đối với các phƣơng pháp đánh địa chỉ trong lệnh Để mô tả địa chỉ trong một lệnh, phương pháp hiển nhiên và đơn giản nhất là cho địa chỉ trực tiếp dạng một số liệu nhị phân. Phương pháp này được gọi là phương pháp đánh địa chỉ trực tiếp. Ngoài ra người ta còn sử dụng nhiều phương pháp đánh địa chỉ khác nhau. Các phương pháp đánh địa chỉ phải thỏa mãn các yêu cầu sau đây: Rút ngắn phần địa chỉ trong lệnh. Thuận tiện cho người lập trình. Hỗ trợ hệ thống. Ví dụ như nếu máy tính nạp đồng thời nhiều chương trình vào bộ nhớ và thường xuyên chuyển đổi việc thực thi các chương trình đó thì để nạp và giải phóng bộ nhớ một cách hiệu quả từ nhiều vị trí khác nhau, phương pháp đánh địa chỉ có thể cho phép chương trình nạp và thực thi trên nhiều vùng khác nhau của bộ nhớ. Các phương pháp đánh địa chỉ Chúng ta xét một số phương pháp đánh địa chỉ thông dụng sau đây: Phương pháp đánh địa chỉ trực tiếp Phương pháp đánh địa chỉ tức thời Phương pháp đánh địa chỉ tương đối Phương pháp đánh địa chỉ gián tiếp 7.5. Phƣơng pháp đánh địa chỉ trực tiếp Phương pháp đánh địa chỉ trực tiếp nạp địa chỉ trong lệnh tại ô nhớ ngay sau ô nhớ lưu mã lệnh (Tức là ô nhớ có địa chỉ lớn hơn 1). Ta xét ví dụ sau đây: Giả sử bộ nhớ được tổ chức thành từng ô 8 bit. Mã lệnh chiếm 8 bit, tức trọn vẹn một ô nhớ. Các bit địa chỉ của lệnh chiếm các ô nhớ tiếp theo. Nếu CPU có thể sử dụng 216 từ trong bộ nhớ thì sẽ cần 2 byte để đánh địa chỉ các ô nhớ. Như vậy để nạp một lệnh cần sử dụng 3 byte, tức 3 ô nhớ. Nếu mã lệnh 3AH (lệnh LOAD), được nạp trong 8 bit ở ô nhớ 0245H, địa chỉ trong lệnh sẽ được nạp trong 16 bit ở hai ô nhớ tiếp theo ngay sau đó với các địa chỉ tương ứng là 0246H và 0247H. Khi thực hiện lệnh CPU đọc mã lệnh trong ô nhớ có địa chỉ 0245H. Sau đó nó sẽ đọc các byte tiếp theo từ ô nhớ 0246H và 0247H, ráp các nội dung đọc được thành một lệnh nguyên vẹn (các bit có thứ tự thấp chứa ở byte đầu tiên) và thực thi lệnh này, tức là nạp nôi dung của ô nhớ có địa chỉ là nội dung hai ô nhớ 0246H và 0247H vào thanh ghi gộp. 101 Khoa CNTT - Trường Đại học Thái Bình Giáo trình KTMT & QLHTMT 7.6. Phƣơng pháp đánh địa chỉ tức thời Phương pháp đánh địa chỉ tức thời thực chất là nạp nội dung của toán hạng (chứ không phải địa chỉ ô nhớ chứa toán hạng) vào ngay sau các ô nhớ chứa mã lệnh. Trở lại ví dụ trên, nếu mã lệnh 3AH (LOAD), được nạp trong 8 bit ở ô nhớ 0245H, toán hạng của lệnh LOAD sẽ được nạp trong các bit ở ô nhớ tiếp theo ngay sau đó với địa chỉ tương ứng là 0246H hoặc có thể ở cả các ô nhớ tiếp theo. Khi thực hiện lệnh CPU đọc mã lệnh trong ô nhớ có địa chỉ 0245H và biết lệnh cần thực hiện là nạp nội dung vào thanh ghi gộp. Sau đó nó sẽ đọc các byte tiếp theo từ ô nhớ 0246H hoặc có thể ở cả các ô nhớ tiếp theo và cuối cùng nạp nội dung đó vào thanh ghi. Để làm ví dụ minh họa, ta xét lệnh như trên (ADD0000010100010000). Giả sử mã lệnh ADD (00000011) được lưu trong ô nhớ có địa chỉ 300H. Với cách đánh địa chỉ trực tiếp, hai ô nhớ tiếp theo 301H và 302H sẽ lưu các bit 00000101 và 00010000. Các dãy bit này được ghép lại thành địa chỉ 0510H và đây là địa chỉ của ô nhớ chứa toán hạng. Còn với cách đánh địa chỉ tức thời thì 0000010100010000 và đây chính là toán hạng. 7.7. Phƣơng pháp đánh địa chỉ tƣơng đối Phương pháp đánh địa chỉ tương đối không cho địa chỉ của toán hạng trong lệnh mà cho gia số của địa chỉ ô nhớ chứa toán hạng và địa chỉ của ô nhớ chứa mã lệnh. Với phương pháp này ta có thể giảm bớt số bít cần sử dụng để cho địa chỉ trong lệnh. Ví dụ nếu bộ nhớ quản lý được 216 ô nhớ (từ), chúng ta phải cần 2 byte để đánh địa chỉ các ô nhớ. Khi đó với cách đánh địa chỉ trực tiếp, ngoài 1 byte để cho mã lệnh, ta cần thêm 2 byte trong lệnh để cho địa chỉ của toán hạng. Còn nếu sử dụng phương pháp đánh địa chỉ tương đối, gia số của địa chỉ chỉ cần 8 bit để biểu diễn. Để hiểu rõ nhất cách đánh địa chỉ này ta so sánh với cách đánh địa chỉ trực tiếp. Với cách đánh địa chỉ trực tiếp, các bit tiếp theo trong lệnh là địa chỉ của toán hạng. Còn với cách đánh địa chỉ tương đối, chúng là hiệu số của địa chỉ của toán hạng và địa chỉ của mã lệnh. Ví dụ như với các máy tính 6800, sử dụng cách đánh địa chỉ tương đối lệnh sẽ gồm mã lệnh và gia số của địa chỉ gồm 8 bit (mã lệnh sẽ cho biết sử dụng cách đánh địa chỉ nào). Như vậy để nạp hết một lệnh chỉ cần 2 byte. Địa chỉ trong byte thứ hai của lệnh sẽ được cộng với địa chỉ của ô nhớ chứa mã lệnh và kết quả sẽ là địa chỉ của toán hạng. Địa chỉ trong byte thứ hai của lệnh được hiểu như là số bù 2 có dấu, do đó nó có thể trỏ tới một địa chỉ cao hơn hoặc thấp hơn so với địa chỉ chứa mã lệnh. Một vấn đề quan trọng cần phải xác định đối với phương pháp đánh địa chỉ tương đối là độ lớn tối đa của gia số. Việc lựa chọn độ lớn này có tác động trực tiếp tới độ dài của lệnh cũng như vùng nhớ có thể truy cập được. 102 Khoa CNTT - Trường Đại học Thái Bình Giáo trình KTMT & QLHTMT 7.8. Phƣơng pháp đánh địa chỉ gián tiếp Một cách đánh địa chỉ khác cũng rất thông dụng là đánh địa chỉ gián tiếp. Với cách đánh địa chỉ này, phần địa chỉ trong lệnh không phải là địa chỉ của toán hạng mà là địa chỉ trỏ tới địa chỉ của toán hạng. Ví dụ trong ô nhớ địa chỉ 245 (hexa) ta có lệnh ADD 302H. Phần thứ hai của lệnh, địa chỉ 302H trỏ tới ô nhớ có địa chỉ 495 (hexa). Đây mới là cho địa chỉ của toán hạng. Giả sử ô nhớ này chứa dữ liệu 194H. Kết quả là CPU sẽ cộng 194H với nội dung của thanh ghi gộp và lưu kết quả nhận được ở thanh ghi gộp. Ngoài các phương pháp đánh địa chỉ nói trên nhiều kiến trúc máy tính còn sử dụng các cách đánh địa chỉ khác. Các phương pháp đánh địa chỉ tức thời và đánh địa chỉ tương đối thường được sử dụng phổ biến nhất. 7.9. Mã hóa các phƣơng pháp đánh địa chỉ Một kiến trúc máy tính có thể sử dụng đồng thời nhiều phương pháp đánh địa chỉ khác nhau. Vì vậy lệnh phải chưa thông tin cho biết nó sử dụng phương pháp đánh địa chỉ gì. Việc mã hóa cách đánh địa chỉ trong lệnh phụ thuộc vào hai yếu tố: Số phương pháp đánh địa chỉ được sử dụng và mức độ độc lập giữa các mã lệnh và phương pháp đánh địa chỉ. Nếu sử dụng ít phương pháp đánh địa chỉ hoặc số tổ hợp mã lệnh/phương pháp đánh địa chỉ ít, cách đánh địa chỉ thường được mã hóa vào trong mã lệnh. Nếu số lượng các tổ hợp nhiều, người ta thường sử dụng các bit chỉ định cách đánh địa chỉ cho mỗi toán hạng. Sau đây là cấu trúc của lệnh với từng kiểu địa chỉ khác nhau : Trong số 16 bit của lệnh có các bit chứa Opcode là phần mã lệnh, và các bit chứa Address là phần địa chỉ. Hình IV. 17. 103

File đính kèm:

giao_trinh_kien_truc_may_tinh_quan_ly_he_thong_may_tinh.pdf

giao_trinh_kien_truc_may_tinh_quan_ly_he_thong_may_tinh.pdf