Bài giảng thiết kế luận lý 1 - Chương 5, Phần 2: Flip-Flop và mạch tuần tự

NAND Gate Latch

• FF cơ bản nhất có thể được xây dựng từ 2 cổng

NAND hoặc 2 cổng NOR

• FF tạo thành từ 2 cổng NAND được gọi là NAND

gate latch hay latch

• Ngõ ra cổng NAND-1 nối vào ngõ nhập của cổng

NAND-2 và ngược lại

• Output được đặt tên là Q và Q’ (Q và Q’ luôn ngược

nhau trong điều kiện bình thường – X/X’, A/A’.).

• Có 2 input:

– SET input: set Q = 1.

– CLEAR input : set Q = 0

NAND Gate Latch

• Khi SET = 1 và CLEAR = 1 thì mạch NAND latch có

2 trường hợp có thể xảy ra

– Ngõ xuất phụ thuộc vào trạng thái các ngõ nhập trước đo

Trang 1

Trang 2

Trang 3

Trang 4

Trang 5

Trang 6

Trang 7

Trang 8

Trang 9

Trang 10

Tải về để xem bản đầy đủ

Bạn đang xem 10 trang mẫu của tài liệu "Bài giảng thiết kế luận lý 1 - Chương 5, Phần 2: Flip-Flop và mạch tuần tự", để tải tài liệu gốc về máy hãy click vào nút Download ở trên

Tóm tắt nội dung tài liệu: Bài giảng thiết kế luận lý 1 - Chương 5, Phần 2: Flip-Flop và mạch tuần tự

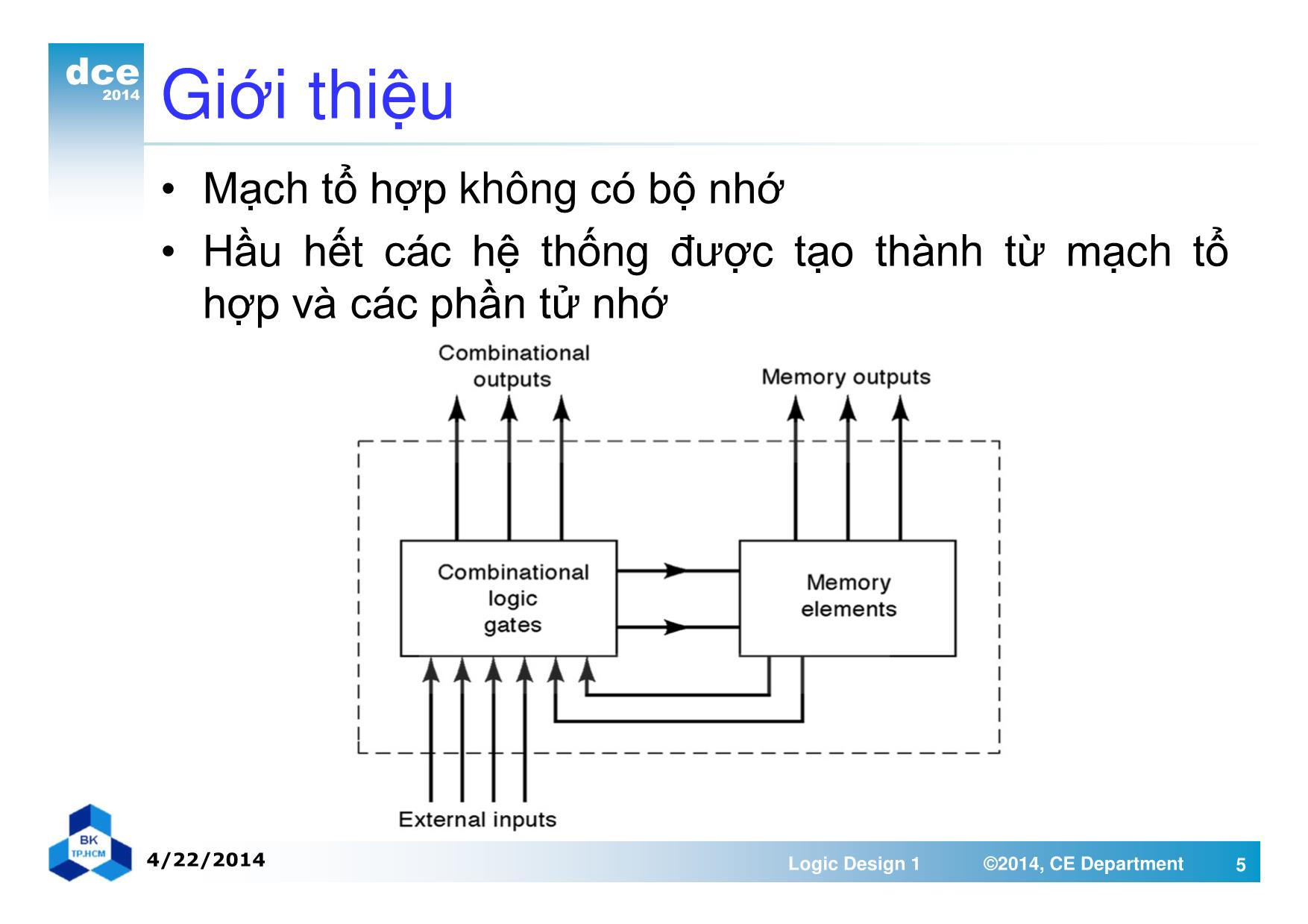

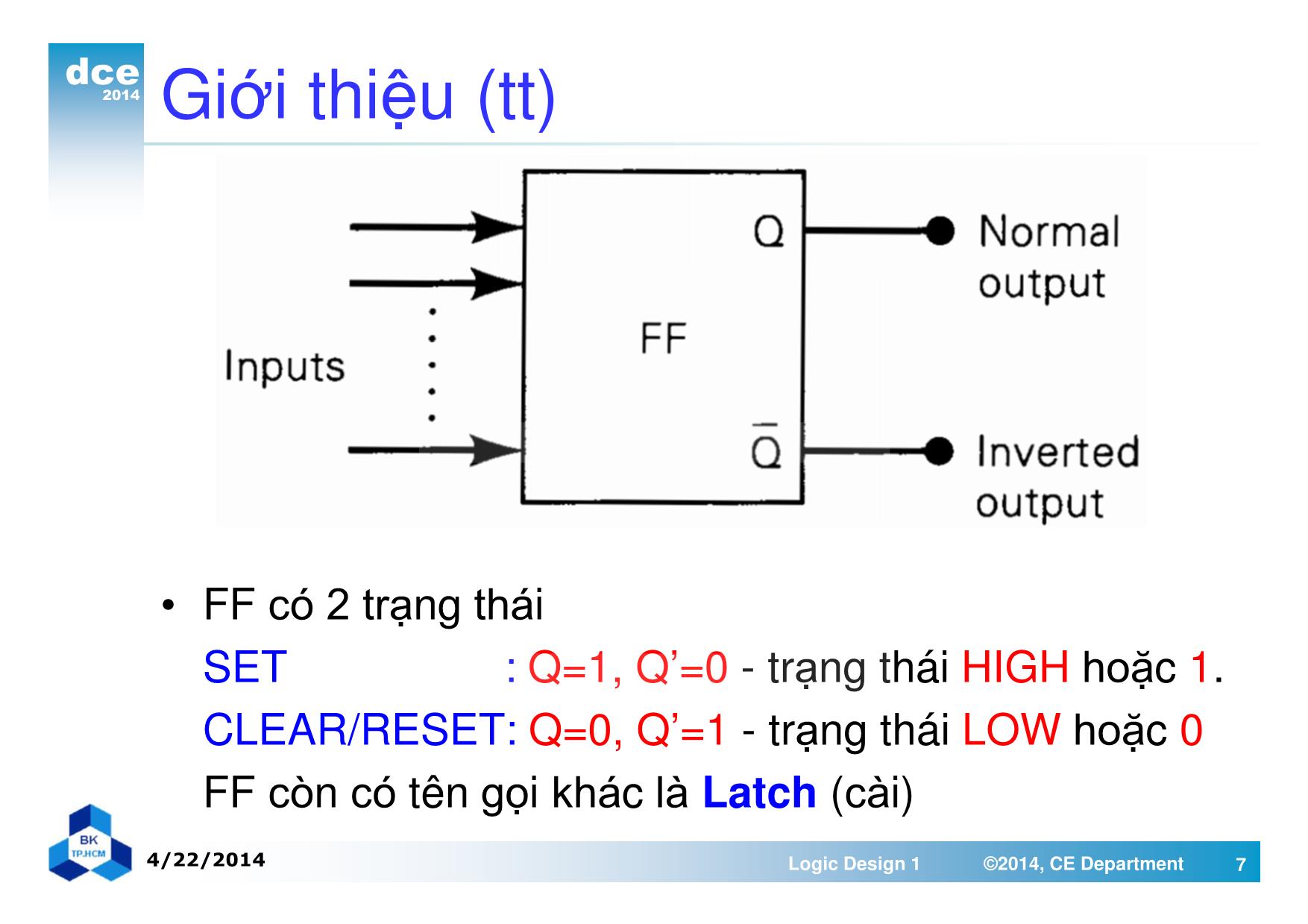

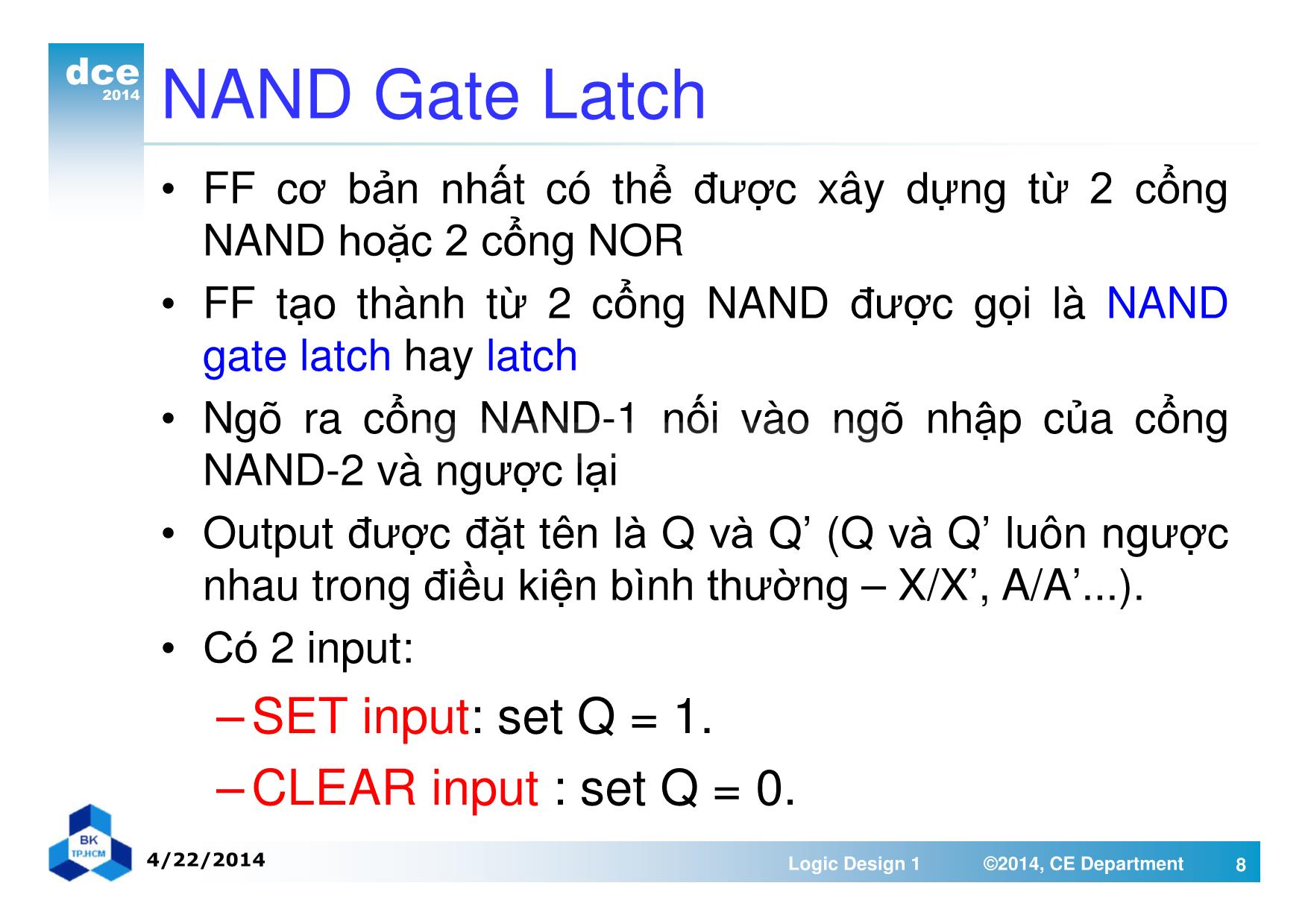

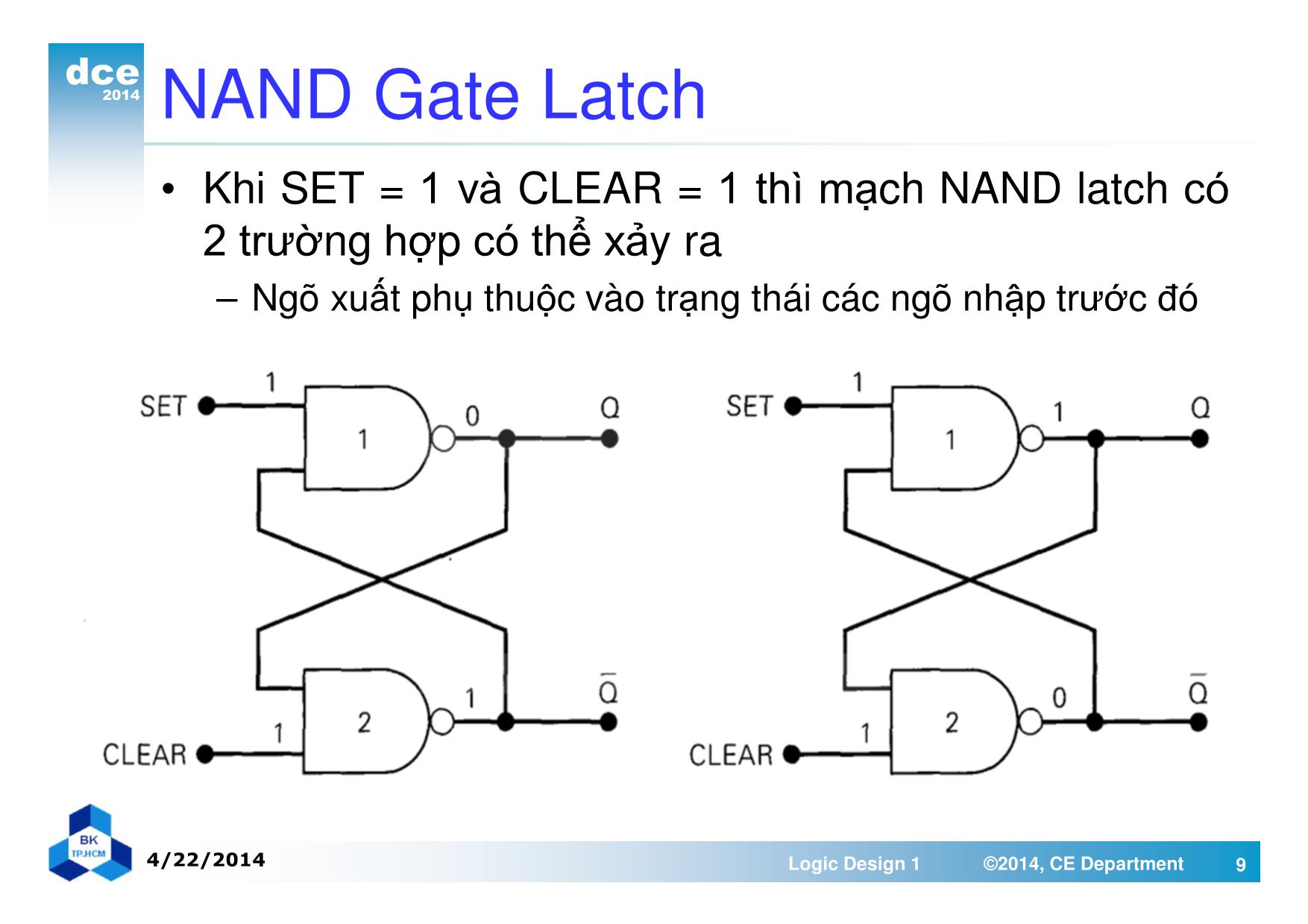

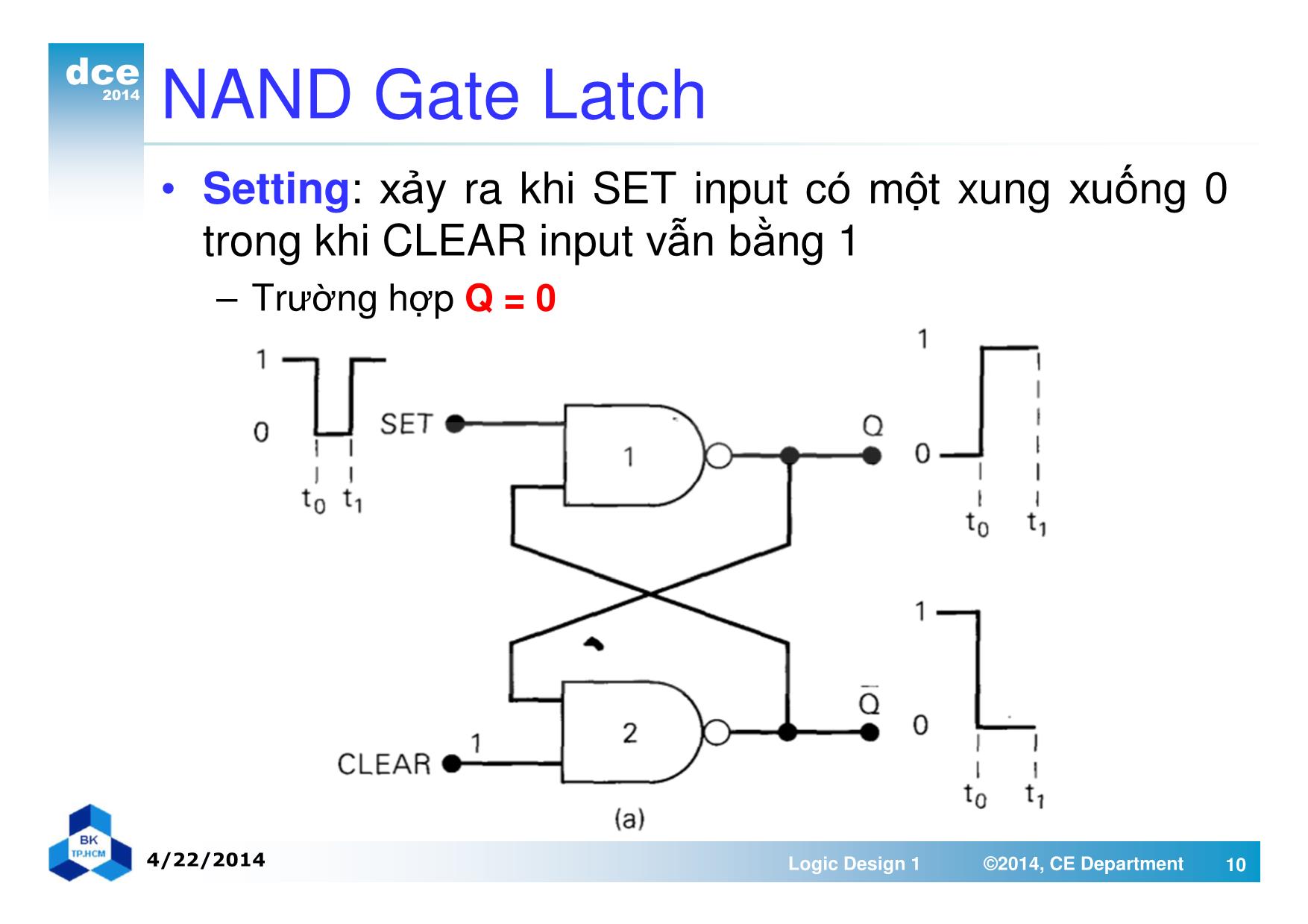

dce 2014 Khoa KH & KTMT Bộ môn Kỹ Thu ật Máy Tính dce 2014 Tài li ệu tham khảo •“Digital Systems, Principles and Applications ”, 11th Edition, Ronald J. Tocci, Neal S. Widmer, Gregory L. Moss 4/22/2014 Logic Design 1 ©2014, CE Department 2 dce 2014 Flip-Flop và mạch tuần tự dce 2014 Nội dung • Gi ới thi ệu mạch tu ần tự • Flip-Flop NAND, NOR • Clocked Flip-Flop • Flip-Flop với ngõ nh ập bất đồ ng bộ • Các vấn đề về th ời gian 4/22/2014 Logic Design 1 ©2014, CE Department 4 dce 2014 Gi ới thi ệu • Mạ ch tổ hợp không có bộ nhớ • Hầ u hế t cá c hệ thố ng được tạ o thà nh từ mạ ch tổ hợp và cá c phầ n tử nhớ 4/22/2014 Logic Design 1 ©2014, CE Department 5 dce 2014 Gi ới thi ệu (tt) • Phầ n mạ ch tổ hợp nhậ n tí n hiệ u từ input ngoà i và từ output củ a cá c phầ n tử nhớ (memory elements). • Output củ a hệ thố ng là mộ t hà m chức năng lấ y tí n hiệ u input ngoà i và thông tin từ cá c phầ n tử nhớ. • Phầ n tử nhớ quan trọ ng nhấ t là flip-flop (FF) (được tạ o ra từ cá c cổ ng logic). –Bản thân cổng logic không có kh ả năng nh ớ – FF: kết nối các cổng logic theo cách mà thông tin có th ể đượ c lưu tr ữ 4/22/2014 Logic Design 1 ©2014, CE Department 6 dce 2014 Gi ới thi ệu (tt) • FF có 2 trạ ng thá i SET : Q=1, Q’=0 - tr ạng thái HIGH hoặ c 1. CLEAR/RESET: Q=0, Q’=1 - tr ạng thái LOW hoặ c 0 FF cò n có tên gọ i khá c là Latch (cà i) 4/22/2014 Logic Design 1 ©2014, CE Department 7 dce 2014 NAND Gate Latch • FF cơ bả n nhấ t có th ể được xây dựng từ 2 cổ ng NAND hoặ c 2 cổ ng NOR • FF tạo thành từ 2 cổng NAND được gọi là NAND gate latch hay latch • Ngõ ra cổng NAND-1 nối vào ngõ nh ập của cổng NAND-2 và ng ược lại • Output được đặ t tên là Q và Q’ (Q và Q’ luôn ngược nhau trong điề u kiệ n bì nh thường – X/X’, A/A’...). • Có 2 input: – SET input : set Q = 1. – CLEAR input : set Q = 0. 4/22/2014 Logic Design 1 ©2014, CE Department 8 dce 2014 NAND Gate Latch • Khi SET = 1 và CLEAR = 1 thì mạ ch NAND latch có 2 trường hợp có thể xả y ra – Ngõ xu ất ph ụ thu ộc vào tr ạng thái các ngõ nh ập tr ướ c đó 4/22/2014 Logic Design 1 ©2014, CE Department 9 dce 2014 NAND Gate Latch • Setting: xả y ra khi SET input có mộ t xung xuố ng 0 trong khi CLEAR input vẫ n bằ ng 1 – Tr ườ ng hợp Q = 0 4/22/2014 Logic Design 1 ©2014, CE Department 10 dce 2014 NAND Gate Latch • Setting: xả y ra khi SET input có mộ t xung xuố ng 0 trong khi CLEAR input vẫ n bằ ng 1 – Tr ườ ng hợp Q = 1 4/22/2014 Logic Design 1 ©2014, CE Department 11 dce 2014 NAND Gate Latch • Clearing: xả y ra khi CLEAR input có mộ t xung xuố ng 0 trong khi SET input vẫ n bằ ng 1 – Tr ạng thái Q = 0 4/22/2014 Logic Design 1 ©2014, CE Department 12 dce 2014 NAND Gate Latch • Clearing: xả y ra khi CLEAR input có mộ t xung xuố ng 0 trong khi SET input vẫ n bằ ng 1 – Tr ạng thái Q = 1 4/22/2014 Logic Design 1 ©2014, CE Department 13 dce 2014 NAND Gate Latch • Khi SET = CLEAR = 0 cù ng lú c thì giá trị output sẽ không thể đoá n trước được. Tuỳ thuộ c và o tí n hiệ u nà o lên 1 trước. • Vì vậ y, trong NAND latch điề u kiệ n SET = CLEAR = 0 không được sử dụ ng. 4/22/2014 Logic Design 1 ©2014, CE Department 14 dce 2014 NAND Gate Latch 4/22/2014 Logic Design 1 ©2014, CE Department 15 dce 2014 Các ký hi ệu t ương đương 4/22/2014 Logic Design 1 ©2014, CE Department 16 dce 2014 NOR Gate Latch 4/22/2014 Logic Design 1 ©2014, CE Department 17 dce 2014 Clock Signals và Clocked FFs • Mộ t hệ thố ng số có thể hoạ t độ ng trong chế độ bấ t đồ ng bộ (Asynchronous) hoặ c đồ ng bộ (Synchronous). – Hệ thố ng bấ t đồ ng bộ : output có thể thay đổ i trạ ng thá i bấ t kì lú c nà o khi input thay đổ i. – Hệ thố ng đồ ng bộ : output thay đổ i trạ ng thá i tạ i mộ t thờ i điể m xá c đị nh bở i tí n hiệ u clock (Clock signal) 4/22/2014 Logic Design 1 ©2014, CE Department 18 dce 2014 Clock Signals và Clocked FFs • Tí n hiệ u Clock được phân bổ đế n tấ t cả cá c phầ n củ a hệ thố ng. Output có thể thay đổ i chỉ khi tí n hiệ u clock chuyể n trạ ng thá i. • Tí n hiệ u clock chuyể n trạ ng thá i từ – 0 lên 1: cạ nh lên (Positive going transition – PGT). – 1 xuố ng 0: cạ nh xuố ng (Negative going transition – NGT). 4/22/2014 Logic Design 1 ©2014, CE Department 19 dce 2014 Clock Signals và Clocked FFs • Hầ u hế t cá c hệ thố ng số đề u hoạ t độ ng ở chế độ đồ ng bộ (Synchronous). –Dễ thi ết kế –Dễ sửa ch ữa • Clocked FF được thiế t kế để khi có sự thay đổ i trạ ng thá i củ a clock thì trạ ng thá i củ a output cũ ng thay đổ i theo. 4/22/2014 Logic Design 1 ©2014, CE Department 20 dce 2014 Clocked Flip-Flops • Clocked FFs có mộ t tí n hiệ u clock được đặ t tên là CLK, CP, hoặ c CK. Hầ u hế t cá c tí n hiệ u CLK là tí n hiệ u kí ch cạ nh (egde triggered). • Clocked FFs có 1 ho ặc nhi ều tí n hiệ u điề u khiể n – Cá c tí n hiệ u điề u khiể n không ảnh hưở ng đế n trạ ng thá i củ a output cho đế n khi có sự thay đổ i trạ ng thá i củ a clock xả y ra. • Tín hi ệu Clock: quy ết đị nh th ời điểm (WHEN) • Tín hi ệu điều khi ển: quy ết đị nh tr ạng thái (WHAT) 4/22/2014 Logic Design 1 ©2014, CE Department 21 dce 2014 Clocked Flip-Flops 4/22/2014 Logic Design 1 ©2014, CE Department 22 dce 2014 Clocked SC Flip-Flops 4/22/2014 Logic Design 1 ©2014, CE Department 23 dce 2014 Clocked SC Flip-Flops 4/22/2014 Logic Design 1 ©2014, CE Department 24 dce 2014 Clocked SC Flip-Flops 4/22/2014 Logic Design 1 ©2014, CE Department 25 dce 2014 Cấu t ạo mạch - edge triggered SC FF 4/22/2014 Logic Design 1 ©2014, CE Department 26 dce 2014 Cấu t ạo mạch - edge triggered SC FF 4/22/2014 Logic Design 1 ©2014, CE Department 27 dce 2014 JK Flip-Flops • Ở mạch cài SC / SR –Cả 2 ngõ vào không đượ c đồ ng th ời mang giá tr ị 1 – Không phù hợp với th ực tế, cần ph ải có sự cải ti ến 4/22/2014 Logic Design 1 ©2014, CE Department 28 dce 2014 JK Flip-Flops 4/22/2014 Logic Design 1 ©2014, CE Department 29 dce 2014 JK Flip-Flops 4/22/2014 Logic Design 1 ©2014, CE Department 30 dce 2014 D Flip-Flops 4/22/2014 Logic Design 1 ©2014, CE Department 31 dce 2014 D Flip-Flops • Hiệ n thực D FF từ JK FF 4/22/2014 Logic Design 1 ©2014, CE Department 32 dce 2014 D Latch 4/22/2014 Logic Design 1 ©2014, CE Department 33 dce 2014 Asynchronous Inputs (bất đồng bộ) • Ngõ nh ập đồ ng bộ (synchronous): S, C, J, K, D – Tí n hiệ u điề u khiể n (control inputs ). – Nhữ ng thay đổ i củ a chú ng chỉ ảnh hưở ng đế n ngõ output khi có tí n hiệ u độ ng bộ củ a CLK. • Ngõ nh ập bấ t đồ ng bộ (asynchronous inputs ) – Hoạ t độ ng độ c lậ p vớ i cá c tí n hiệ u input đồ ng bộ và tí n hiệ u CLK (Bấ t kì lú c nà o và không quan tâm đế n nhữ ng input khá c). – Set FF lên trạ ng thá i 1 – Clear FF về trạ ng thá i 0 4/22/2014 Logic Design 1 ©2014, CE Department 34 dce 2014 Asynchronous Inputs (bất đồng bộ) 4/22/2014 Logic Design 1 ©2014, CE Department 35 dce 2014 Asynchronous Inputs (bất đồng bộ) 4/22/2014 Logic Design 1 ©2014, CE Department 36 dce 2014 FF – Vấn đề thời gian • Setup and Hold time 4/22/2014 Logic Design 1 ©2014, CE Department 37 dce 2014 FF – Vấn đề thời gian (tt) • Tr ễ lan truy ền (Propagation delay) – Giá tr ị tối đa (Maximum): vài ns đế n 100ns 4/22/2014 Logic Design 1 ©2014, CE Department 38 dce 2014 FF – Vấn đề thời gian (tt) • Maximum clock frequency • Clock pulse high or low times • Clock transition times 4/22/2014 Logic Design 1 ©2014, CE Department 39 dce 2014 FF – Vấn đề thời gian (tt) 4/22/2014 Logic Design 1 ©2014, CE Department 40 dce 2014 FF – Vấn đề thời gian (tt) 4/22/2014 Logic Design 1 ©2014, CE Department 41 dce 2014 Ứng dụng FF • 74LS74 (D-FF positive-edge) • 74LS73 (JK-FF, negative-edge) •Lưu trữ dữ liệ u và truyề n dữ liệ u – Thườ ng sử dụ ng FF để lưu trữ dữ liệ u hay thông tin. Dữ liệ u đượ c lưu trữ theo 1 nhó m cá c FF gọ i là register (thanh ghi). – Cá c hoạ t độ ng thườ ng đượ c thự c hiệ n vớ i cá c dữ liệ u đượ c lưu trong register là truyề n dữ liệ u (data transfer). 4/22/2014 Logic Design 1 ©2014, CE Department 42 dce 2014 Ứng dụng FF (1) • Truyề n dữ liệ u song song (Parallel transfer) 4/22/2014 Logic Design 1 ©2014, CE Department 43 dce 2014 Ứng dụng FF (2) • Thanh ghi dị ch (shift register) 4/22/2014 Logic Design 1 ©2014, CE Department 44 dce 2014 Ứng dụng FF (3) • Chia tầ n số và đế m (Frequency division and counting) 4/22/2014 Logic Design 1 ©2014, CE Department 45 dce 2014 Ứng dụng FF (3) • Ho ạt độ ng đế m và sơ đồ chuy ển tr ạng thái (state transition diagram) 4/22/2014 Logic Design 1 ©2014, CE Department 46 dce 2014 Ứng dụng FF (3) • Mod number – MOD number: chỉ số trạ ng thá i trong chuỗ i đế m . – Bộ đế m ở ví dụ trướ c có 23=8 trạ ng thá i khá c nhau(000 tớ i 111 ). Bộ đế m nà y đượ c gọ i là bộ đế m MOD-8. – Nế u có 4 FF thì chuỗ i trạ ng thá i sẽ đế m từ 0000 đế n 1111 (có 16 trạ ng thá i). Và đượ c gọ i là bộ đế m MOD-16. – Bộ đế m MOD-2N có khả năng đế m tớ i 2N -1 sau đó quay về trạ ng thá i 0. 4/22/2014 Logic Design 1 ©2014, CE Department 47 dce 2014 Thi ết bị Schmitt-trigger 4/22/2014 Logic Design 1 ©2014, CE Department 48 dce 2014 Mạch t ạo xung clock •Bộ dao độ ng Schmitt-trigger 4/22/2014 Logic Design 1 ©2014, CE Department 49 dce 2014 Mạch t ạo xung clock • IC đị nh th ời (timer ) 555 4/22/2014 Logic Design 1 ©2014, CE Department 50

File đính kèm:

bai_giang_thiet_ke_luan_ly_1_chuong_5_phan_2_flip_flop_va_ma.pdf

bai_giang_thiet_ke_luan_ly_1_chuong_5_phan_2_flip_flop_va_ma.pdf