Bài giảng Kiến trúc máy tính - Tuần 10: Bộ xử lý Processor

Hiệu suất của một máy tính được xác định bởi ba yếu tố:

Tổng số câu lệnh Được xác định bởi trình biên dịch

và kiến trúc tập lệnh

Chu kỳ xung clock

Số chu kỳ xung clock trên một lệnh

(Clock cycles per instruction − CPI)

Mục đích chính của chương này:

Giải thích quy tắc hoạt động và hướng dẫn xây dựng datapath cho một bộ xử lý chứa một số lệnh đơn giản (giống kiến trúc tập lệnh dạng MIPS), gồm hai ý chính:

Thiết kế datapath

Hiện thực datapath đã thiết kế

MIPS (bắt nguồn từ chữ viết tắt của ‘Microprocessor without Interlocked Pipeline Stages’) là một kiến trúc tập tập lệnh dạng RISC, được phát triển bởi MIPS Technologies (trước đây là MIPS Computer Systems, Inc.)

Trang 1

Trang 2

Trang 3

Trang 4

Trang 5

Trang 6

Trang 7

Trang 8

Trang 9

Trang 10

Tải về để xem bản đầy đủ

Tóm tắt nội dung tài liệu: Bài giảng Kiến trúc máy tính - Tuần 10: Bộ xử lý Processor

1 Read register 2 Write register Write data Read data 1 Read data 2 RegWrite Register File 5 5 5 Nội dung của thanh ghi $22 Immediate 15:0 opcode 31:26 rs 25:21 rt 20:16 Inst [25:21] Inst [20:16] Inst [15:11] Vấn đề: Thanh ghi đích $21 “ đặt không đúng vị trí” lw $21, -50($22) 03/2017 Copyrights 2017 CE-UIT. All Rights Reserved. 27 001000 10110 10101 1111 1111 1100 1110 Read register 1 Read register 2 Write register Write data Read data 1 Read data 2 Register File 5 5 5 Immediate 15:0 opcode 31:26 rs 25:21 rt 20:16 Inst [25:21] Inst [20:16] Inst [15:11] MUX RegDst RegDst : Tín hiệu điều khiển chọn Inst[20:16] hay [15:11] để đưa vào ngõ write register Giải pháp (cho chỉ số thanh ghi sẽ được ghi): Sử dụng một multiplexer để lựa chọn chỉ số thanh ghi cho ngõ write register chính xác dựa trên từng loại lệnh lw $21, -50($22) Giải mã: Giải pháp cho ngõ “Write register” 03/2017 Multiplexer (MUX) Chức năng: Chọn một input từ tập input đầu vào Inputs: n đường vào có cùng chiều rộng Control: Cần m bit trong đó n = 2 m Output: Chọn đường input thứ i nếu giá trị tín hiệu điều khiển control = i 28 Control=0 select in 0 Control=3 select in 3 in 0 in n-1 out Control m . . . MUX 03/2017 Copyrights 2017 CE-UIT. All Rights Reserved. Giải mã: giải pháp cho ngõ “Data 2” 29 001000 10110 10101 1111 1111 1100 1110 Read register 1 Read register 2 Write register Write data Read data 1 Read data 2 5 5 5 Immediate 15:0 opcode 31:26 rs 25:21 rt 20:16 Inst [25:21] Inst [20:16] Inst [15:11] MUX RegDst Inst [ 15:0] MUX ALUSrc RegWrite Sign Extend 16 32 Register File ALUSrc : Tín hiệu điều khiển để chọn “Read data 2” hay giá trị của Inst[15:0] (đã được mở rộng có dấu) cho toán hạng thứ hai Giải pháp (cho đường dữ liệu data 2) Sử dụng một multiplexer để chọn chính xác toán hạn g thứ 2. Sign extend : khối mở rộng số tức thời 16 bit thành 32 bit lw $21, -50($22) 03/2017 Copyrights 2017 CE-UIT. All Rights Reserved. 30 100011 10110 10101 1111 1111 1100 1110 Read register 1 Read register 2 Write register Write data Read data 1 Read data 2 5 5 5 Immediate 15:0 opcode 31:26 rs 25:21 rt 20:16 Inst [25:21] Inst [20:16] Inst [15:11] MUX RegDst Inst [ 15:0] MUX ALUSrc RegWrite Sign Extend 16 32 Register File V í dụ với lệnh : “ s w $21 , -50( $22 ) " Có cần phải thay đổi thành phần nào? Giải mã: Lệnh Load Word 03/2017 Copyrights 2017 CE-UIT. All Rights Reserved. Ví dụ: " beq $9 , $0 , 3 " Cần tính kết quả rẽ nhánh và đích đến cùng một lúc ! Giải quyết vấn đề này trong giai đoạn của ALU 31 000100 01001 00000 0000 0000 0000 0011 Immediate 15:0 opcode 31:26 rs 25:21 rt 20:16 Read register 1 Read register 2 Write register Write data Read data 1 Read data 2 5 5 5 Inst [25:21] Inst [20:16] Inst [15:11] MUX RegDst Inst [ 15:0] MUX ALUSrc RegWrite Sign Extend 16 32 Register File Giải mã: Lệnh nhánh/nhảy 03/2017 Copyrights 2017 CE-UIT. All Rights Reserved. Giải mã: tổng kết 32 Read register 1 Read register 2 Write register Write data Read data 1 Read data 2 Registers 5 5 5 Inst [25:21] Inst [20:16] Inst [15:11] MUX RegDst Inst [ 15:0] MUX ALUSrc RegWrite Sign Extend 16 32 Operand 1 Operand 2 Inst[31:0] 03/2017 Copyrights 2017 CE-UIT. All Rights Reserved. Instruction Fetch (Nạp lệnh) Instruction Decode & Operand Fetch (Giải mã và lấy các toán hạng cần thiết, Gọi tắt là “Instruction Decode”) ALU (Giai đoạn sử dụng ALU hay giai đoạn thực thi) Memory Access (Giai đoạn truy xuất vùng nhớ) Result Write (Giai đoạn ghi lại kết quả/lưu trữ) 33 Fetch Instruction Decode ALU Memory Access Result Write Next Instruction Quy trình thực thi lệnh của MIPS (5 công đoạn) 03/2017 Copyrights 2017 CE-UIT. All Rights Reserved. Công đoạn ALU Công đoạn ALU: ALU = Arithmetic-Logic Unit Công việc thật sự của hầu hết các lệnh được hiện chủ yếu trong giai đoạn này Số học (Arithmetic) (ví dụ: add , sub ), Logic (ví dụ: and , or ): ALU tính ra kết quả cuối cùng Lệnh làm việc với bộ nhớ (ví dụ: lw , sw ): ALU dùng tính toán địa chỉ của bộ nhớ Lệnh nhảy/nhánh (ví dụ: bne , beq ): ALU thực hiện so sánh các giá trị trên thanh ghi và tính toán địa chỉ đích sẽ nhảy tới Đầu vào từ công đoạn trước ( Decode ): Các thao tác (operation) và toán hạng (operand(s)) Đầu ra cho công đoạn tiếp theo ( Memory ): Tính toán kết quả (Đối với lệnh lw và sw: Kết quả của công đoạn này sẽ là địa chỉ cung cấp cho memory để lấy dữ liệu) 34 03/2017 Copyrights 2017 CE-UIT. All Rights Reserved. Công đoạn ALU 35 ALU result ALU Decode Stage Operands Memory Stage Khối mạch thực hiện các phép toán logic và số học 03/2017 Copyrights 2017 CE-UIT. All Rights Reserved. ALU (Arithmetic-logical unit ) Khối dùng để thực hiện các phép tính logic và số học Inputs: 2 số 32-bit Điều khiển khối ALU: Do ALU có thể thực hiện nhiều chức năng dùng 4-bit để quyết định chức năng/phép toán cụ thể nào cho ALU Outputs: Kết quả của phép toán số học hoặc logic Một bit tín hiệu để chỉ ra rằng kết quả có bằng 0 hay không ALUcontrol Function 0000 AND 0001 OR 0010 add 0110 subtract 0111 slt 1100 NOR 36 ALU result ALU ALUcontrol 4 isZero? A B A op B (A op B) == 0? Khối ALU ( Arithmetic Logical Unit) 03/2017 Copyrights 2017 CE-UIT. All Rights Reserved. Các lệnh không nhánh/nhảy (non-branch) kết nối ALU như hình: 37 Read register 1 Read register 2 Write register Write data Read data 1 Read data 2 Register File 5 5 5 Inst [25:21] Inst [20:16] Inst [15:11] MUX RegDst Inst [ 15:0] MUX ALUSrc RegWrite Sign Extend 16 32 ALU result ALU ALUcontrol 4 isZero? opcode 31:26 rs 25:21 rt 20:16 rd 15:11 shamt 10:6 funct 5:0 000000 01001 01010 01000 00000 100000 ALUcontrol: Thiết lập giá trị cho ALUcontrol cần sử dụng trường opcode và funct add $8 , $9 , $10 Công đoạn ALU: các lệnh non-branch 03/2017 Copyrights 2017 CE-UIT. All Rights Reserved. Công đoạn ALU: Các lệnh Branch Lệnh rẽ nhánh thì khó hơn vì phải tính toán hai phép toán: Ví dụ: " beq $9 , $0 , 3 " Kết quả rẽ nhánh: Sử dụng ALU để so sánh thanh ghi Tín hiệu 1-bit " isZero? “ để kiểm tra tính chất bằng/không bằng Địa chỉ đích của nhánh: Sử dụng một bộ cộng để tính địa chỉ Cần nội dung của thanh ghi PC (từ Fetch Stage) Cần Offset (từ Decode Stage) 38 03/2017 Copyrights 2017 CE-UIT. All Rights Reserved. 000100 01001 00000 0000 0000 0000 0011 Immediate 15:0 opcode 31:26 rs 25:21 rt 20:16 Read register 1 Read register 2 Write register Write data Read data 1 Read data 2 Register File 5 5 5 Inst [25:21] Inst [20:16] Inst [15:11] MUX RegDst Inst [ 15:0] MUX ALUSrc RegWrite Sign Extend 16 32 ALU result ALU ALUcontrol 4 isZero? Left Shift 2-bit PC Add 4 Add MUX PCSrc Ví dụ: " beq $9 , $0 , 3 " Datapath với công đoạn ALU hoàn chỉnh 39 PCSrc: Tín hiệu điều khiển để lựa chọn giữa (PC+4) hoặc địa chỉ đích mà lệnh nhánh/nhảy sẽ nhảy tới 03/2017 Instruction Fetch (Nạp lệnh) Instruction Decode & Operand Fetch (Giải mã và lấy các toán hạng cần thiết, Gọi tắt là “Instruction Decode”) ALU (Giai đoạn sử dụng ALU hay giai đoạn thực thi) Memory Access (Giai đoạn truy xuất vùng nhớ) Result Write (Giai đoạn ghi lại kết quả/lưu trữ) 40 Fetch Instruction Decode ALU Memory Access Result Write Next Instruction Quy trình thực thi lệnh của MIPS (5 công đoạn) 03/2017 Copyrights 2017 CE-UIT. All Rights Reserved. Giai đoạn truy xuất vùng nhớ: Chỉ có lệnh Load và Store cần thực hiện các thao tác trong giai đoạn này: Sử dụng địa chỉ vùng nhớ được tính toán ở giai đoạn ALU Đọc dữ liệu ra hoặc ghi dữ liệu vào vùng nhớ dữ liệu Tất cả các lệnh khác sẽ rảnh trong giai đoạn này Đầu vào từ giai đoạn trước ( ALU ): Kết quả tính toán được dùng làm địa chỉ vùng nhớ (nếu có thể ứng dụng) Đầu ra cho giai đoạn tiếp theo ( Result Write ): Kết quả được lưu trữ lại (nếu cần) 41 Giai đoạn truy xuất vùng nhớ (Memory stage) 03/2017 Copyrights 2017 CE-UIT. All Rights Reserved. ALU Stage Result Result Store Stage Bộ nhớ lưu trữ dữ liệu Data Memory Address Read Data Write Data MemRead MemWrite 42 Giai đoạn truy xuất vùng nhớ (Memory stage) 03/2017 Copyrights 2017 CE-UIT. All Rights Reserved. Vùng nhớ này lưu trữ dữ liệu cần thiết của chương trình Inputs: Address: Địa chỉ vùng nhớ Write Data: Dữ liệu sẽ được ghi vào vùng nhớ đối với lệnh Store Tín hiệu điều khiển: Tín hiệu đọc (MemRead ) và ghi (MemWrite); chỉ một tín hiệu được bật lên tại bất kì một thời điểm nào Output: Dữ liệu được đọc từ vùng nhớ đối với lệnh Load 43 Data Memory Address Read Data Write Data MemRead MemWrite Khối Data Memory 03/2017 Copyrights 2017 CE-UIT. All Rights Reserved. Chỉ những phần liên quan đến Decode & ALU Stage được trình bày 44 000100 01001 00000 0000 0000 0000 0011 Immediate 15:0 opcode 31:26 rs 25:21 rt 20:16 Inst [25:21] Inst [20:16] Inst [15:11] MUX RegDst Inst [ 15:0] MUX ALUSrc RR1 RR2 WR WD RD1 RD2 Registers 5 5 5 RegWrite Sign Extend 16 32 ALU result ALU ALUcontrol 4 100011 10110 10101 1111 1111 1100 1110 Address Write Data MemRead MemWrite Data Memory Read Data lw $21 , -50( $22 ) Giai đoạn Memory: lệnh Load 03/2017 Copyrights 2017 CE-UIT. All Rights Reserved. Cần Read Data 2 (Decode) để đưa vào Write Data 45 000100 01001 00000 0000 0000 0000 0011 Immediate 15:0 opcode 31:26 rs 25:21 rt 20:16 Inst [25:21] Inst [20:16] Inst [15:11] MUX RegDst Inst [ 15:0] MUX RR1 RR2 WR WD RD1 RD2 Registers 5 5 5 RegWrite Sign Extend 16 32 ALU result ALU ALUcontrol 4 101011 10110 10101 1111 1111 1100 1110 Address Write Data MemRead MemWrite Data Memory Read Data sw $21 , -50( $22 ) Giai đoạn Memory: lệnh Store 03/2017 Copyrights 2017 CE-UIT. All Rights Reserved. MemToReg : Tín hiệu điều khiển giúp lựa chọn giá trị lưu vào thanh ghi là từ Read Data hay từ ALU result Sử dụng thêm một multiplexer để lựa chọn kết quả lưu trữ vào thanh ghi 46 Inst [25:21] Inst [20:16] Inst [15:11] MUX RegDst Inst [ 15:0] MUX RR1 RR2 WR WD RD1 RD2 Registers 5 5 5 RegWrite Sign Extend 16 32 ALU result ALU ALUcontrol 4 Data Memory Address Read Data Write Data MemWrite opcode 31:26 rs 25:21 rt 20:16 rd 15:11 shamt 10:6 funct 5:0 000000 01001 01010 01000 00000 100000 MUX MemToReg add $8 , $9 , $10 MemRead Giai đoạn Memory: lệnh không truy xuất vùng nhớ 03/2017 Copyrights 2017 CE-UIT. All Rights Reserved. Instruction Fetch (Nạp lệnh) Instruction Decode & Operand Fetch (Giải mã và lấy các toán hạng cần thiết, Gọi tắt là “Instruction Decode”) ALU (Giai đoạn sử dụng ALU hay giai đoạn thực thi) Memory Access (Giai đoạn truy xuất vùng nhớ) Result Write (Giai đoạn ghi lại kết quả/lưu trữ) 47 Fetch Instruction Decode ALU Memory Access Result Write Next Instruction Quy trình thực thi lệnh của MIPS (5 công đoạn) 03/2017 Copyrights 2017 CE-UIT. All Rights Reserved. Công đoạn Result Write: Những lệnh ghi kết quả của các phép toán vào thanh ghi: Ví dụ: số học, logic, shifts, load, set-less-than Cần chỉ số thanh ghi đích và kết quả tính toán Những lệnh không ghi kết quả như: store, branch, jump: Không có ghi kết quả Những lệnh này sẽ rảnh trong giai đoạn này Đầu vào từ giai đoạn trước ( Memory ): Kết quả tính toán hoặc là từ Memory hoặc là từ ALU 48 Giai đoạn lưu trữ kết quả (Result Write) 03/2017 Copyrights 2017 CE-UIT. All Rights Reserved. Công đoạn Result Write không có thêm bất kỳ thành phần nào khác: Chỉ đơn giản đưa kết quả vào thanh ghi (ngõ Write data của khối Registers/Register file) Chỉ số của thanh ghi được ghi vào (ngõ vào Write Register) được sinh ra trong giai đoạn Decode Stage 49 Memory Stage Result Read register 1 Read register 2 Write register Read data 1 Read data 2 Registers 5 5 5 Write data Giai đoạn lưu trữ kết quả (Result Write) 03/2017 Copyrights 2017 CE-UIT. All Rights Reserved. 50 Inst [25:21] Inst [20:16] Inst [15:11] MUX Inst [ 15:0] MUX RR1 RR2 WR WD RD1 RD2 Registers 5 5 5 RegWrite Sign Extend ALU result ALU ALUcontrol 4 Data Memory Address Read Data Write Data MemWrite opcode 31:26 rs 25:21 rt 20:16 rd 15:11 shamt 10:6 funct 5:0 000000 01001 01010 01000 00000 100000 MUX MemToReg add $8 , $9 , $10 MemRead Giai đoạn lưu trữ kết quả (Result Write) 03/2017 Copyrights 2017 CE-UIT. All Rights Reserved. Inst [25:21] Inst [20:16] Inst [15:11] MUX Inst [ 15:0] MUX RR1 RR2 WR WD RD1 RD2 Registers 5 5 5 RegWrite Sign Extend ALU result ALU ALUcontrol 4 Data Memory Address Read Data Write Data MemWrite opcode 31:26 rs 25:21 rt 20:16 rd 15:11 shamt 10:6 funct 5:0 000000 01001 01010 01000 00000 100000 Left Shift 2-bit PC Add 4 Add MUX PCSrc Instruction Memory is0? Address Instruction RegDst MemRead ALUSrc Datapath hoàn chỉnh MemToReg MUX 51 (Chưa có khối Control để điều khiển các tín hiệu điều khiển) 03/2017 Copyrights 2017 CE-UIT. All Rights Reserved. BỘ XỬ LÝ 52 Tổng kết: Phần này trình bày một cách thiết kế datapath đơn giản cho bộ xử lý 32 bits, với 8 lệnh cơ bản của MIPS: add, sub, and, or, slt l w, sw beq Với khối chức năng cơ bản trong một bộ xử lý (tập thanh ghi, khối ALU, khối Control , thanh ghi PC, thanh ghi IR) và bộ nhớ chính, các khối này sẽ được kết nối với nhau để đảm bảo thực thi đúng 8 lệnh như trên. 03/2017 Copyrights 2017 CE-UIT. All Rights Reserved. BỘ XỬ LÝ Lý thuyết: Đọc sách tham khảo Mục: 4.1, 4.2, 4.3 Sách: Computer Organization and Design: The Hardware/Software Interface , Patterson, D. A., and J. L. Hennessy, Morgan Kaufman, Revised Fourth Edition, 2011. Bài tập: file đính kèm 53 03/2017 Copyrights 2017 CE-UIT. All Rights Reserved.

File đính kèm:

bai_giang_kien_truc_may_tinh_tuan_10_bo_xu_ly_processor.pptx

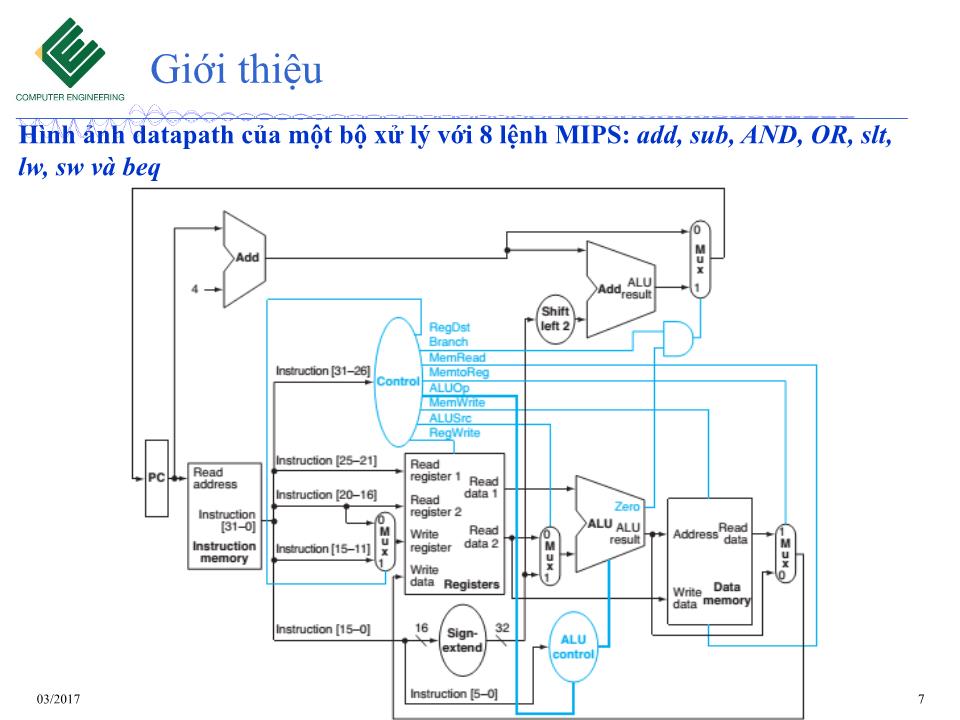

bai_giang_kien_truc_may_tinh_tuan_10_bo_xu_ly_processor.pptx