Bài giảng Kiến trúc máy tính - Chương: Tổ chức máy tính

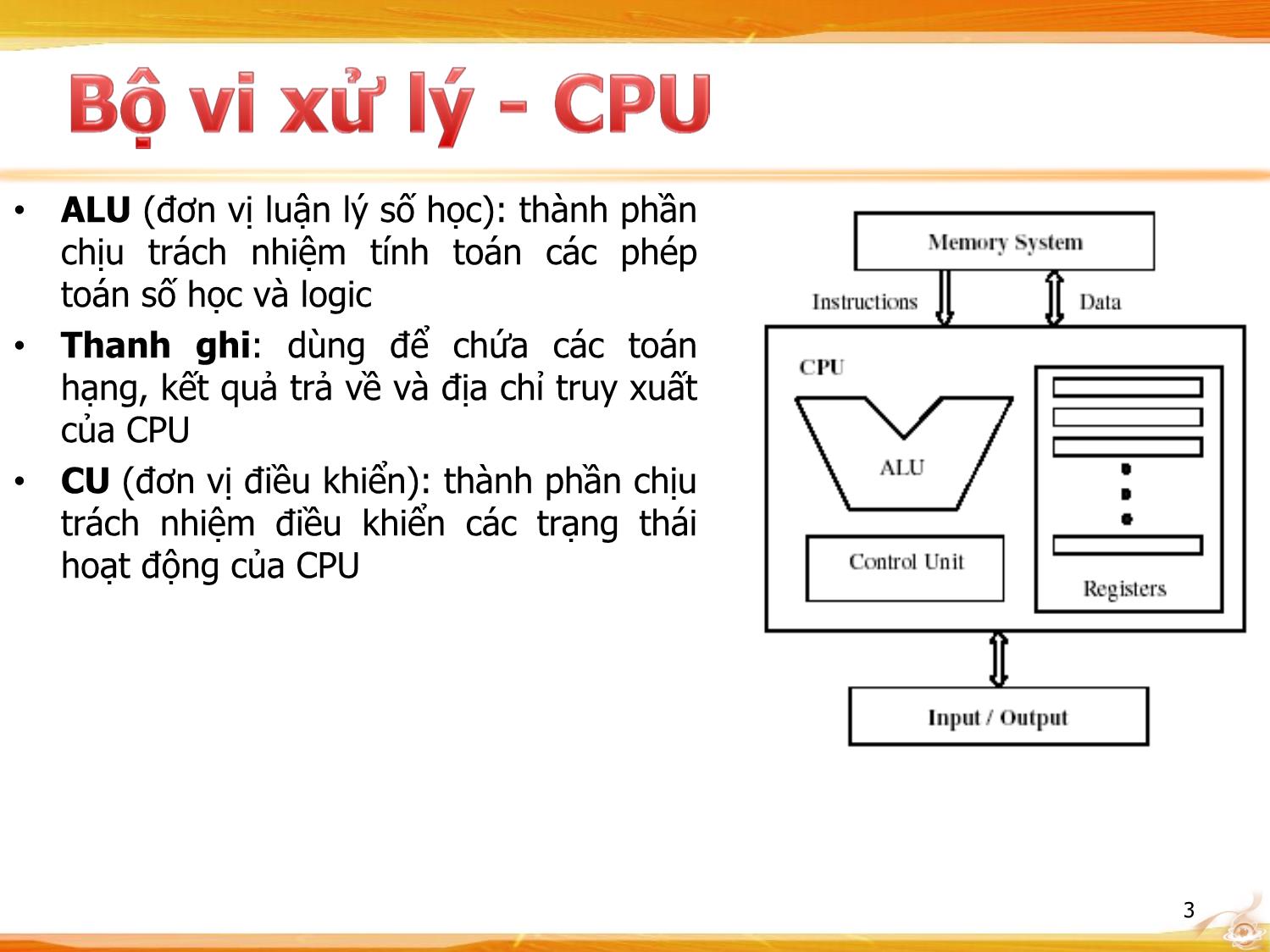

ALU (đơn vị luận lý số học): thành phần

chịu trách nhiệm tính toán các phép

toán số học và logic

• Thanh ghi: dùng để chứa các toán

hạng, kết quả trả về và địa chỉ truy xuất

của CPU

• CU (đơn vị điều khiển): thành phần chịu

trách nhiệm điều khiển các trạng thái

hoạt động của CPU

Trang 1

Trang 2

Trang 3

Trang 4

Trang 5

Trang 6

Trang 7

Trang 8

Trang 9

Trang 10

Tải về để xem bản đầy đủ

Bạn đang xem 10 trang mẫu của tài liệu "Bài giảng Kiến trúc máy tính - Chương: Tổ chức máy tính", để tải tài liệu gốc về máy hãy click vào nút Download ở trên

Tóm tắt nội dung tài liệu: Bài giảng Kiến trúc máy tính - Chương: Tổ chức máy tính

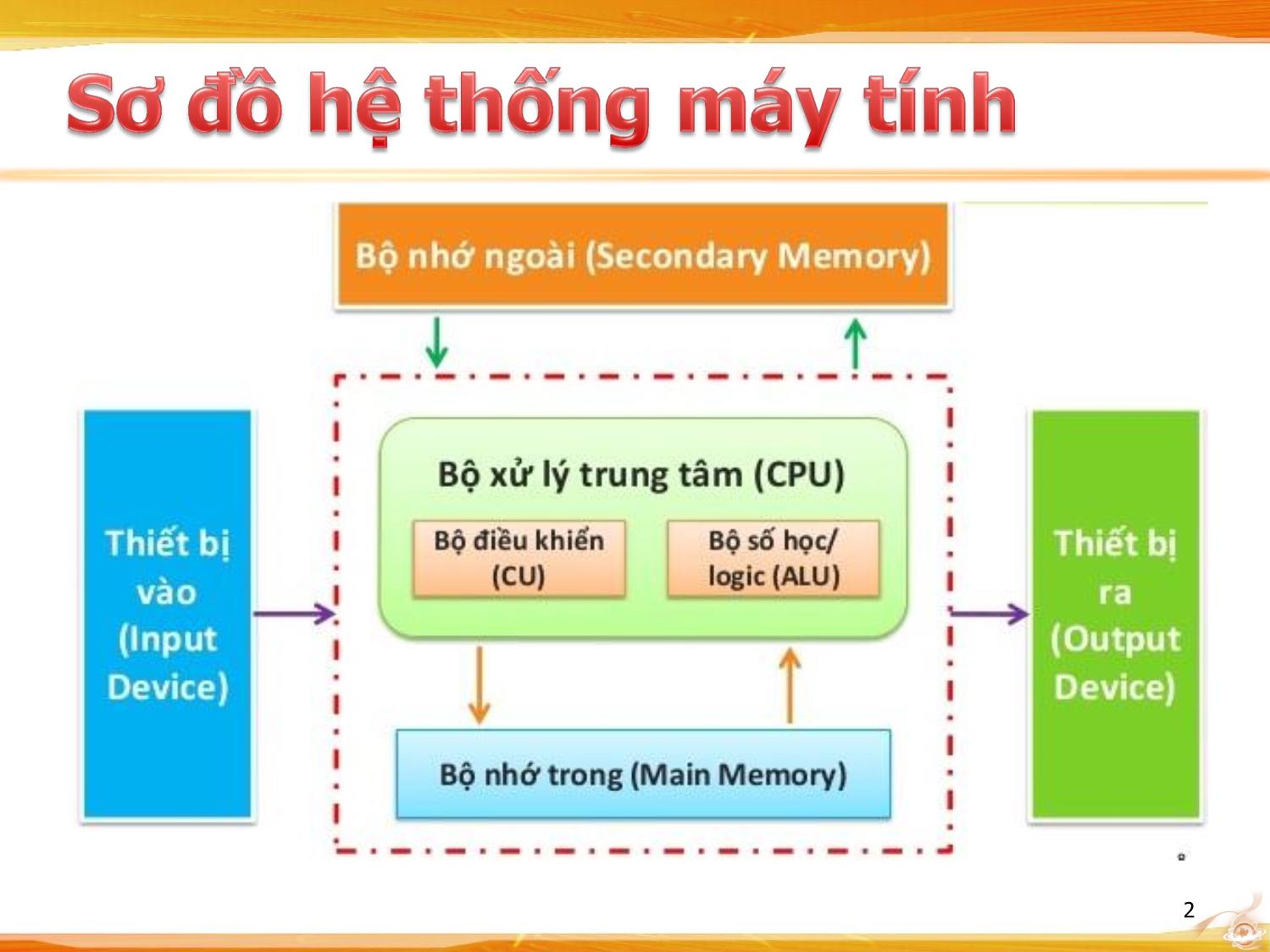

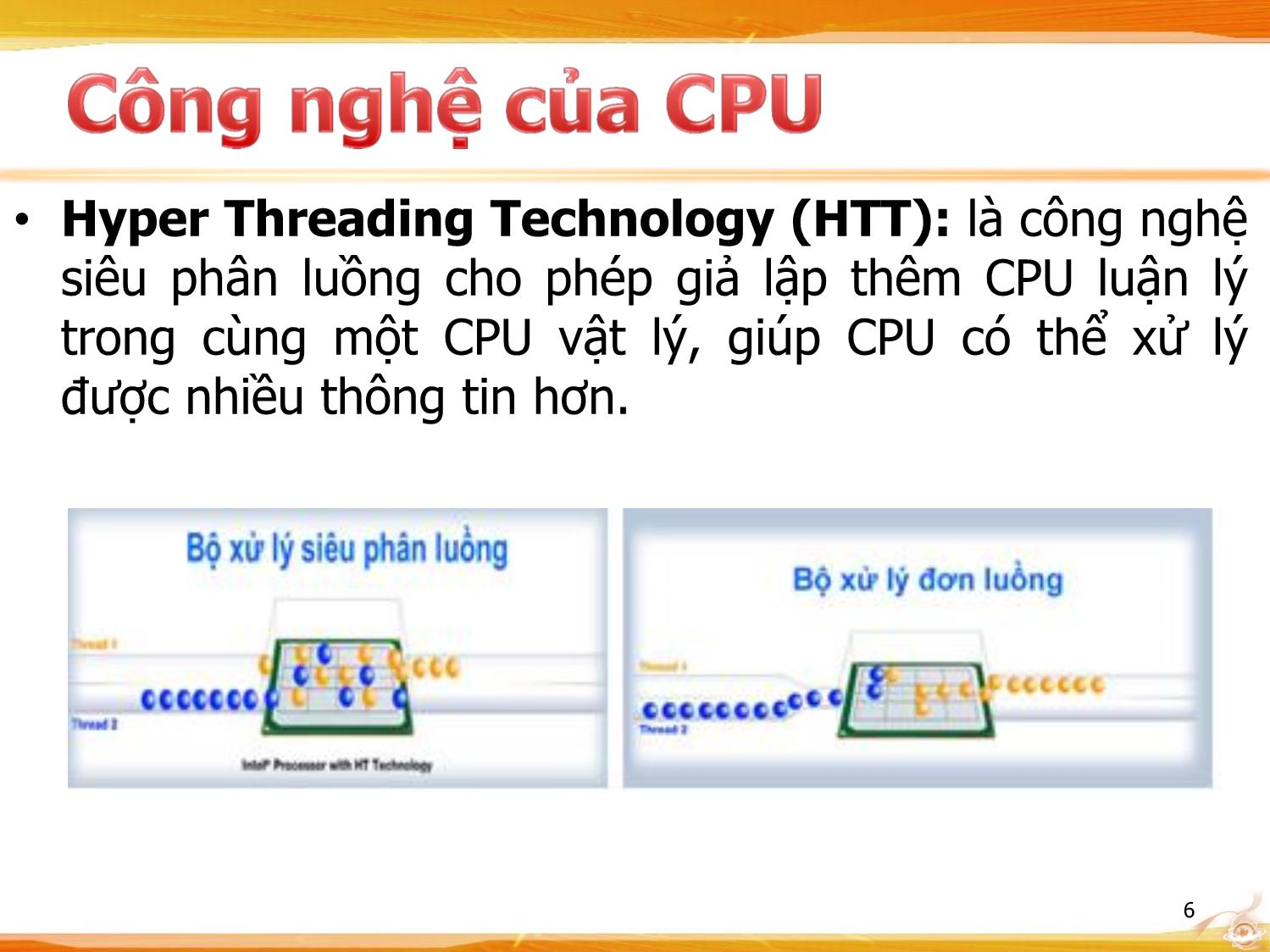

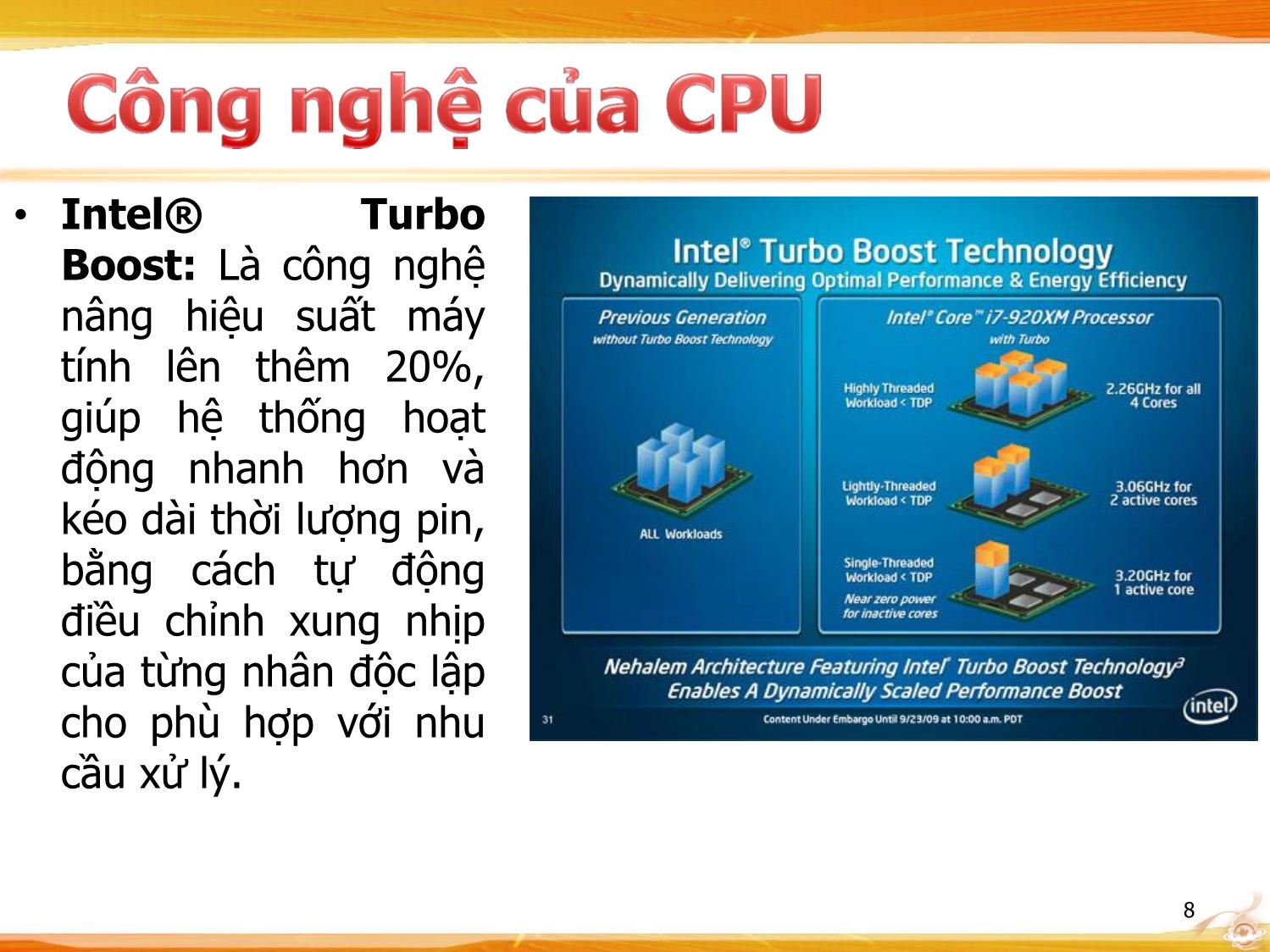

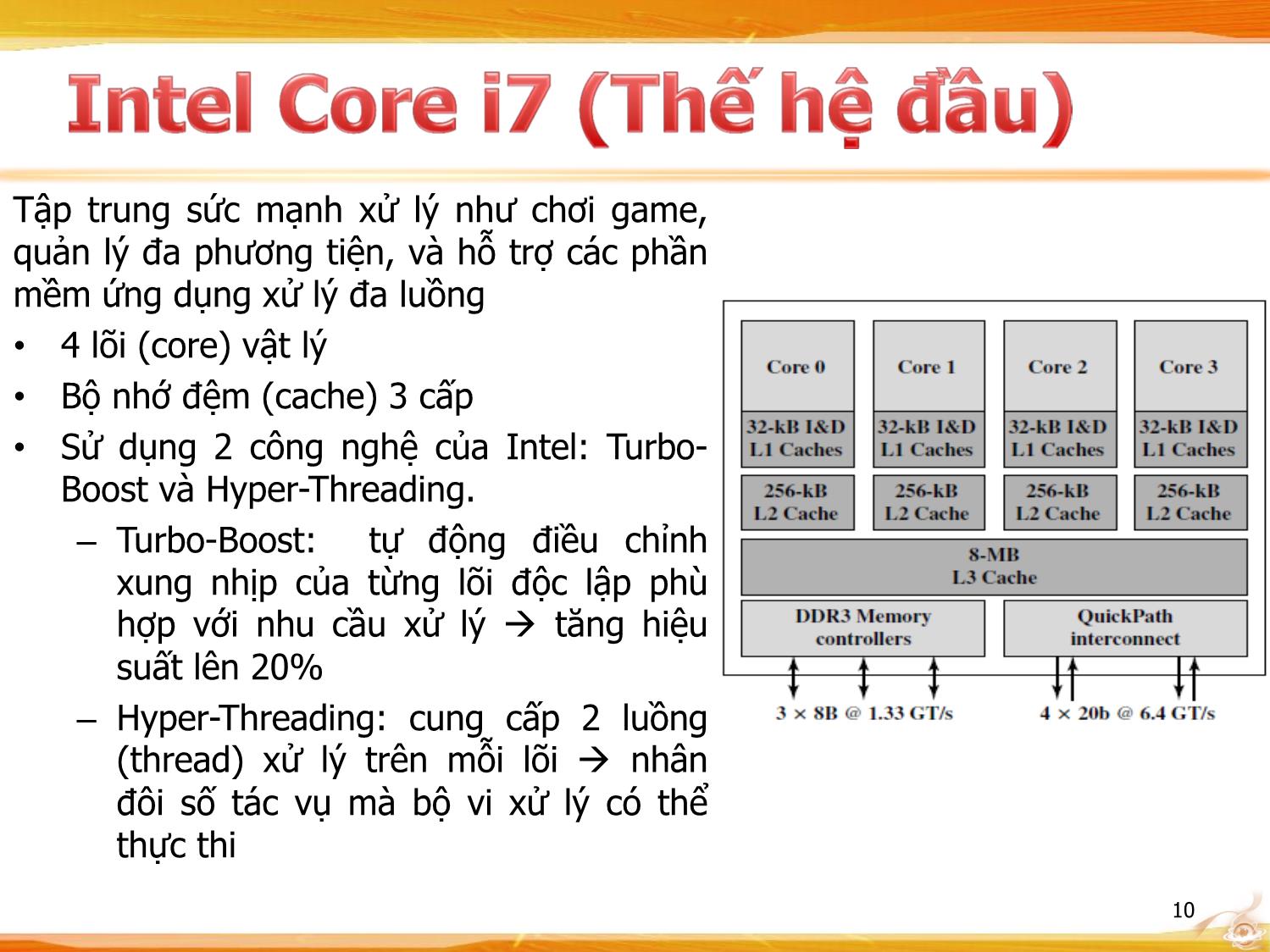

1 Môn học: Kiến trúc máy tính 2 • ALU (đơn vị luận lý số học): thành phần chịu trách nhiệm tính toán các phép toán số học và logic • Thanh ghi: dùng để chứa các toán hạng, kết quả trả về và địa chỉ truy xuất của CPU • CU (đơn vị điều khiển): thành phần chịu trách nhiệm điều khiển các trạng thái hoạt động của CPU 3 • 1970 bộ CPU 4004 (4 bit) của Intel trên 1 chip đầu tiên ra đời • 1972 CPU Intel 8008 (8 bit) • 1974 CPU 8080, 1978 CPU 8086 (16 bit) • 1979 CPU 8088 (8 bit) • 1981 máy tính IBM PC đầu tiên ra đời trên cơ sở CPU Intel 8088 và hệ điều hành MS DOS • 1982 CPU 80286 (16 bit) • 1985 CPU 80386 (32 bit), 1989 CPU 80486 . . . (xuất hiện khái niệm đa nhiệm) • 1993 Pentium • 1997 CPU Pentium II 4 • 1999 CPU Pentium III • 2000 CPU Pentium IV • 2002 Công nghệ siêu phân luồng cho Pentium IV tăng hiệu suất hoạt động máy tính lên 25% • 2003 Pentium IV Extreme Edition • 2005 Dual Core • 2006 Core 2 Duo tăng thêm 40% hiệu suất hoạt động • Đầu năm 2007, Core 2 Quad với số lõi thực sự là 4 • Cuối năm 2008, Core i7 ra đời với công nghệ Turbo Boost • Cuối năm 2009, Core i5 • Đầu năm 2010, Core i3 5 • Hyper Threading Technology (HTT): là công nghệ siêu phân luồng cho phép giả lập thêm CPU luận lý trong cùng một CPU vật lý, giúp CPU có thể xử lý được nhiều thông tin hơn. 6 • Multi Core (đa nhân): Công nghệ chế tạo CPU có hai hay nhiều nhân, xử lý vật lý hoạt động song song với nhau, mỗi nhân đảm nhận những công việc riêng biệt nhau. 7 • Intel® Turbo Boost: Là công nghệ nâng hiệu suất máy tính lên thêm 20%, giúp hệ thống hoạt động nhanh hơn và kéo dài thời lượng pin, bằng cách tự động điều chỉnh xung nhịp của từng nhân độc lập cho phù hợp với nhu cầu xử lý. 8 9 Tập trung sức mạnh xử lý như chơi game, quản lý đa phương tiện, và hỗ trợ các phần mềm ứng dụng xử lý đa luồng • 4 lõi (core) vật lý • Bộ nhớ đệm (cache) 3 cấp • Sử dụng 2 công nghệ của Intel: Turbo- Boost và Hyper-Threading. – Turbo-Boost: tự động điều chỉnh xung nhịp của từng lõi độc lập phù hợp với nhu cầu xử lý tăng hiệu suất lên 20% – Hyper-Threading: cung cấp 2 luồng (thread) xử lý trên mỗi lõi nhân đôi số tác vụ mà bộ vi xử lý có thể thực thi 10 11 • Bus dữ liệu (data bus): truyền dữ liệu giữa các thành phần trong hệ thống (2 chiều) • Bus địa chỉ (address bus): để CPU xác định các thành phần trong hệ thống (1 chiều) • Bus điều khiển (control bus): để CPU ra lệnh điều khiển cho các thành phần trong hệ thống (2 chiều) 12 13 14 • Bus địa chỉ bao gồm các tín hiệu dùng để chuyển tải địa chỉ (thường được ký hiệu là A, ví dụ CPU có 20 tín hiệu từ A0 đến A19). Khi đọc/ghi bộ nhớ (hoặc I/O), CPU đưa ra trên Bus này địa chỉ của bộ nhớ (hoặc I/O) cần đọc/ ghi. • Như vậy, số lượng tín hiệu địa chỉ sẽ quyết định không gian bộ nhớ (tức là số lượng ô nhớ) mà CPU có thể định vị được. Ví dụ: • CPU 8088/8086 có 20 bít tín hiệu địa chỉ thì không gian bộ nhớ của CPU này là 220 = 1Mbytes • CPU Pentium II có 36 tín hiệu địa chỉ thì không gian bộ nhớ của nó là 236 = 64Gbytes. 15 • Bus dữ liệu gồm các tín hiệu dùng để chuyển tải dữ liệu (thường được ký hiệu là D). Số tín hiệu dữ liệu quyết định số bit dữ liệu mà CPU có thể xử lý cùng một lúc. Lưu ý rằng các tín hiệu dữ liệu là hai chiều vì CPU có thể đọc/ghi dữ liệu từ bộ nhớ hoặc I/O. • Bus điều khiển dùng để điều khiển hoạt động của hệ thống như các tín hiệu /WR (Write) để báo hiệu CPU đọc dữ liệu, /RD (Read) để báo hiệu CPU ghi dữ liệu, Ready dùng để báo cho CPU biết bộ nhớ (hoặc I/O) sẵn sàng quá trình trao đổi dữ liệuDo đó, Bus điều khiển cũng phải là hai chiều. 16 • Bộ ghép nối vào ra cho phép ghép nối hệ thống với các thiết bị vào/ ra (I/O) như màn hình, bàn phím, chuột, ỗ đĩathông qua các địa chỉ cổng vào/ ra (Port) 17 • Bus địa chỉ có 20 bit không gian bộ nhớ của CPU là 220 ô nhớ. Trong các CPU của Intel, mỗi ô nhớ có độ dài là 8 bit, nên không gian bộ nhớ tương ứng của CPU 8088/ 8086 là 1 Mega bytes. • CPU 8088/8086 có 14 thanh ghi 16 bit. Trong sơ đồ bên dưới các thanh ghi đa năng AX, BX, CX, DX được trình bày ở dạng hai thanh ghi 8 bit tương ứng. 18 • Một chương trình hoạt động sẽ có 3 vùng nhớ: o Mã lệnh o Dữ liệu o Ngăn xếp (Stack) • CPU 8088/8086 có 4 thanh ghi đoạn: o CS (Code Segment) là thanh ghi đoạn mã lệnh, trỏ đến vùng nhớ chứa mã lệnh của chương trình. o DS (Data Segment) là thanh ghi đoạn dữ liệu, trỏ đến vùng nhớ chứa dữ liệu của chương trình. o ES (Extra Segment) là thanh ghi đoạn dữ liệu phụ, trỏ đến vùng nhớ chứa dữ liệu của chương trình. o SS (Stack Segment) là thanh ghi đoạn ngăn xếp. 19 AX (16 bit) BX (16 bit) AH (8 bit) AL (8 bit) BH (8 bit) BL (8 bit) CX (16 bit) DX (16 bit) CH (8 bit) CL (8 bit) DH (8 bit) DL (8 bit) • AX (Accumulator Register - thanh ghi tích lũy): Dùng trong các phép nhân chia, chứa dữ liệu cho các lệnh in, out. • BX (Base Register - thanh ghi cơ sở): Dùng trong chế độ địa chỉ cơ sở. • CX (Count register - thanh ghi đếm): Dùng để đếm số lần lặp trong các lệnh lặp. • DX (Data Register - thanh ghi dữ liệu): Dùng để chứa địa chỉ cho các lệnh in/ out và làm toán hạng trong các lệnh nhân, chia 16 bit. (DX chứa 16 bit cao). 20 • SI (Source Index) và DI (Destination Index): Các thanh ghi này có thể được dùng như là các con trỏ để truy xuất gián tiếp đến bộ nhớ. • IP (Instruction Pointer): Trỏ đến lệnh tiếp theo mà CPU sẽ thực hiện. • SP (Stack Pointer): Trỏ đến ô nhớ nằm trong vùng ngăn xếp. • BP (Base Pointer): Được dùng để truy xuất gián tiếp đến bộ nhớ. 21 • Thanh ghi cờ có nhiều chức năng: phản ánh kết quả sau khi tính toán, thể hiện trạng thái họat động của CPU • Cờ tràn (Overflow Flag - OF) • Cờ hướng (DirectionFlag – DF • Cờ ngắt (Interrupt flag - IF) • Cờ dấu (Sign Flag - SF) • Cờ Zero (Zero Flag - ZF) • Cờ phụ (Auxililary Flag - AF): Cờ nhớ phụ chứa bit nhớ • Cờ parity (Parity Flag PF) • Cờ nhớ (Carry Flag – CF): Cờ nhớ dùng cho phép toán nhị phân không dấu 22

File đính kèm:

bai_giang_kien_truc_may_tinh_chuong_to_chuc_may_tinh.pdf

bai_giang_kien_truc_may_tinh_chuong_to_chuc_may_tinh.pdf