Bài giảng Kiến trúc máy tính - Chương: CPU - Nguyễn Ngọc Hóa

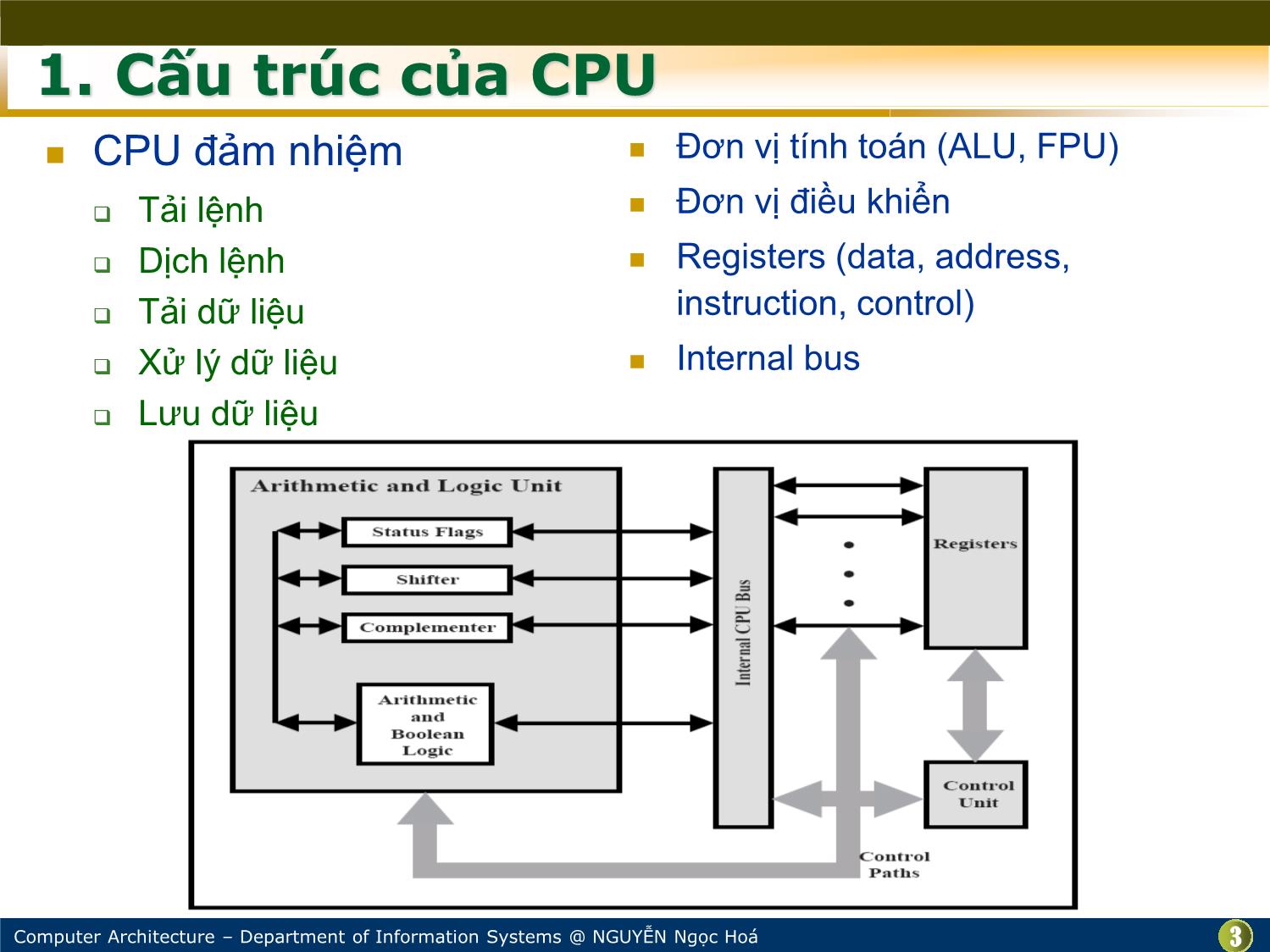

1. Cấu trúc của CPU

CPU đảm nhiệm

Tải lệnh

Dịch lệnh

Tải dữ liệu

Xử lý dữ liệu

Lưu dữ liệu

Đơn vị tính toán (ALU, FPU)

Đơn vị điều khiển

Registers (data, address,

instruction, control)

Internal bus

Trang 1

Trang 2

Trang 3

Trang 4

Trang 5

Trang 6

Trang 7

Trang 8

Trang 9

Trang 10

Tải về để xem bản đầy đủ

Bạn đang xem 10 trang mẫu của tài liệu "Bài giảng Kiến trúc máy tính - Chương: CPU - Nguyễn Ngọc Hóa", để tải tài liệu gốc về máy hãy click vào nút Download ở trên

Tóm tắt nội dung tài liệu: Bài giảng Kiến trúc máy tính - Chương: CPU - Nguyễn Ngọc Hóa

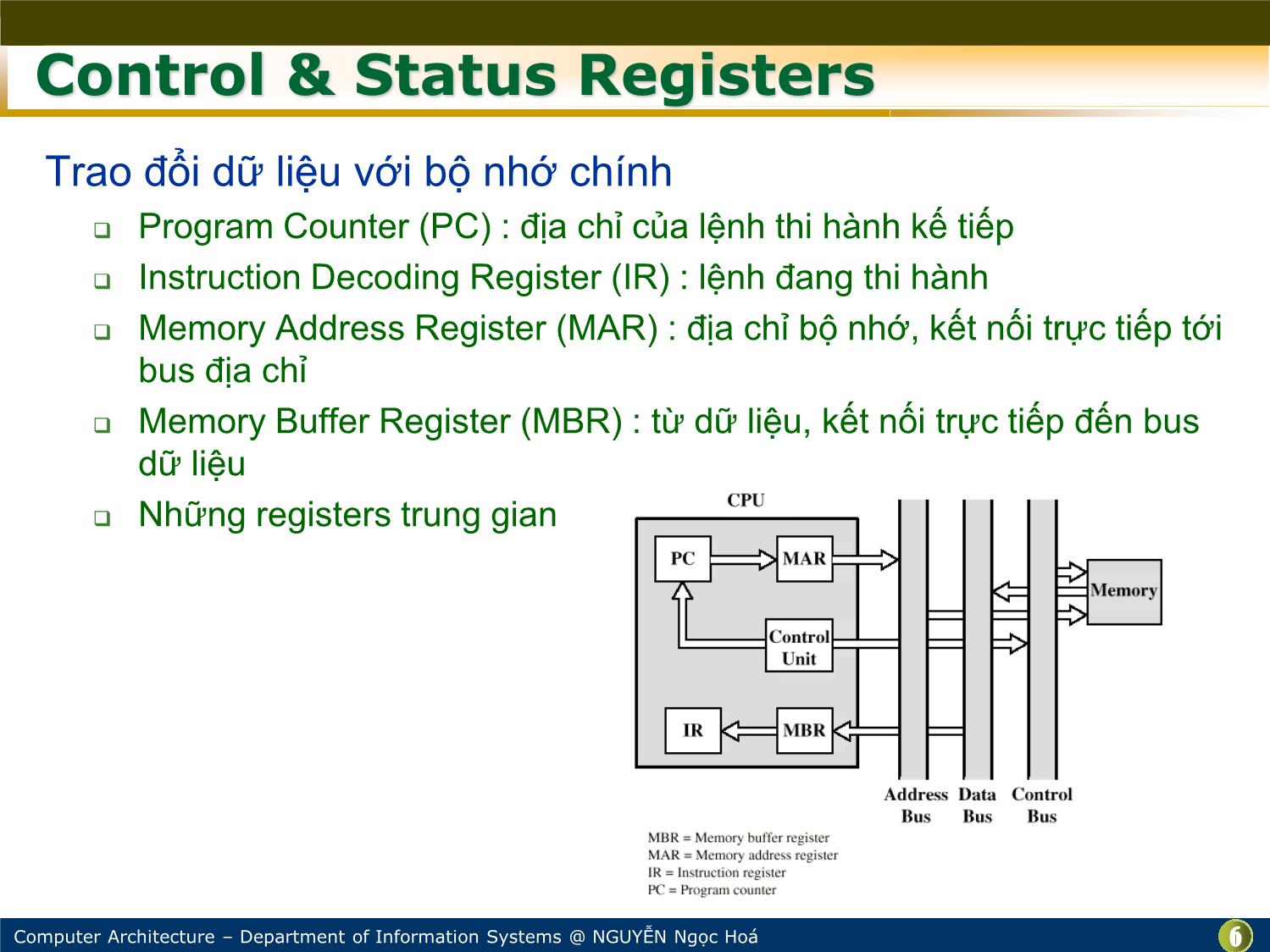

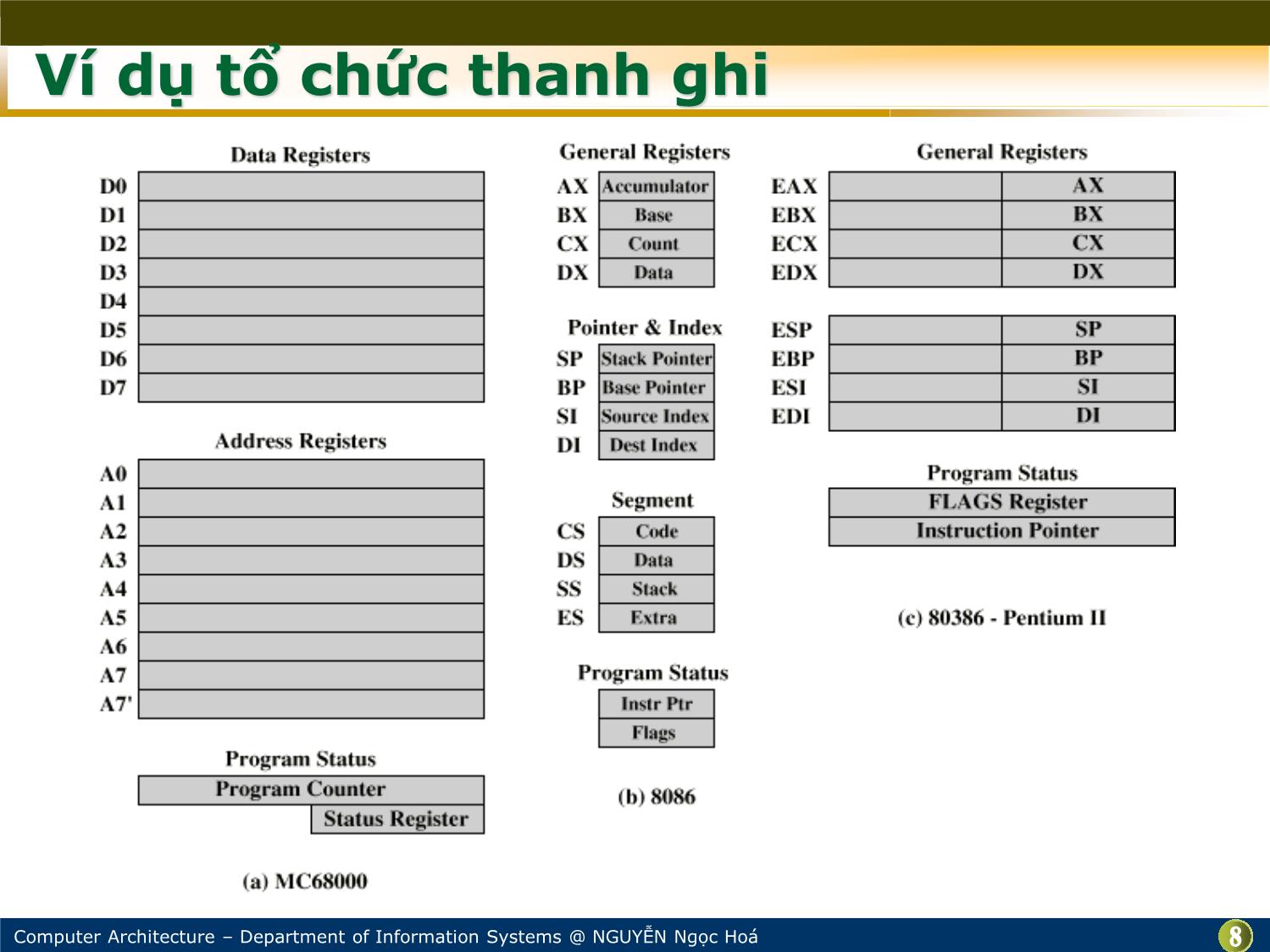

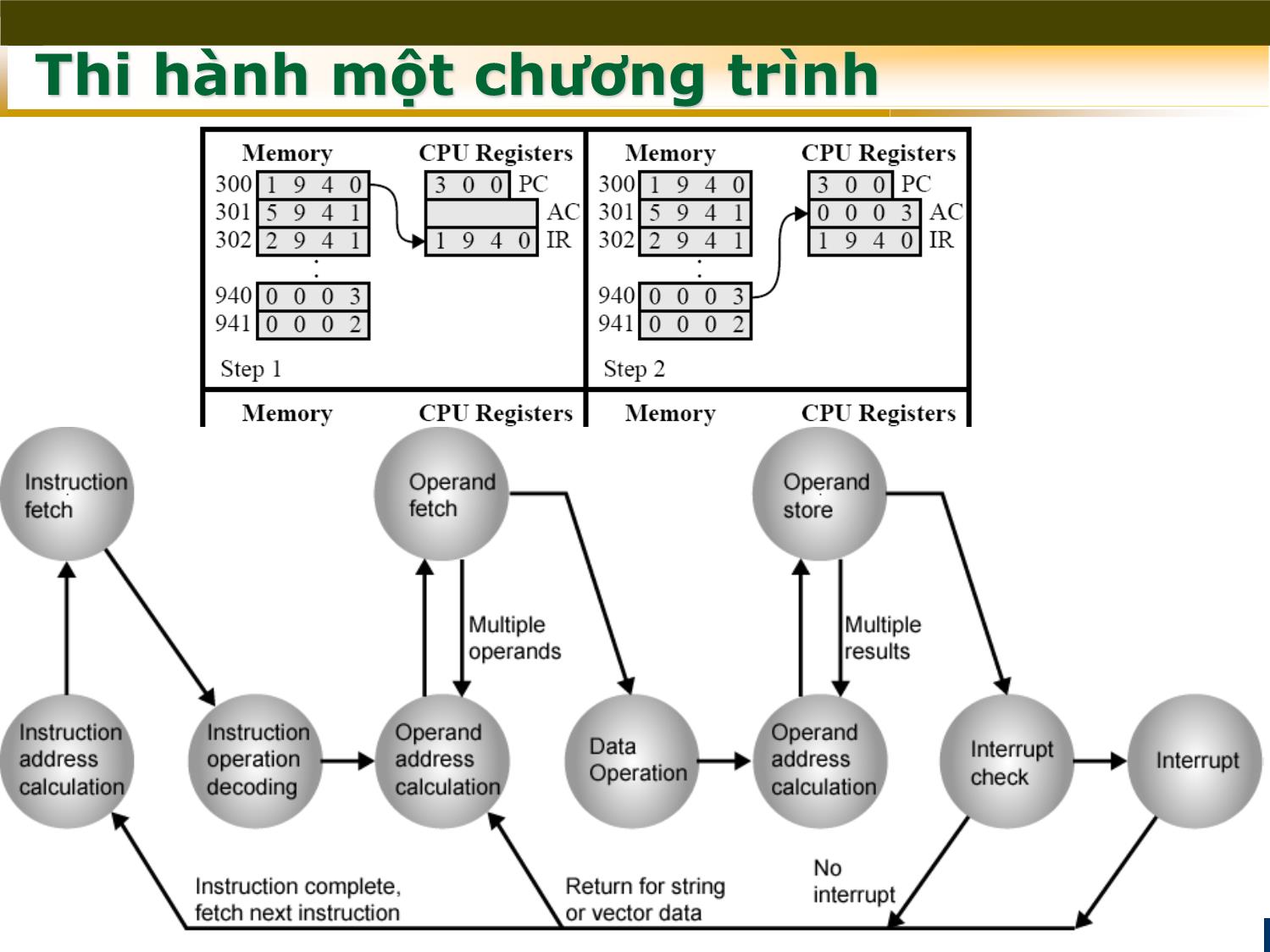

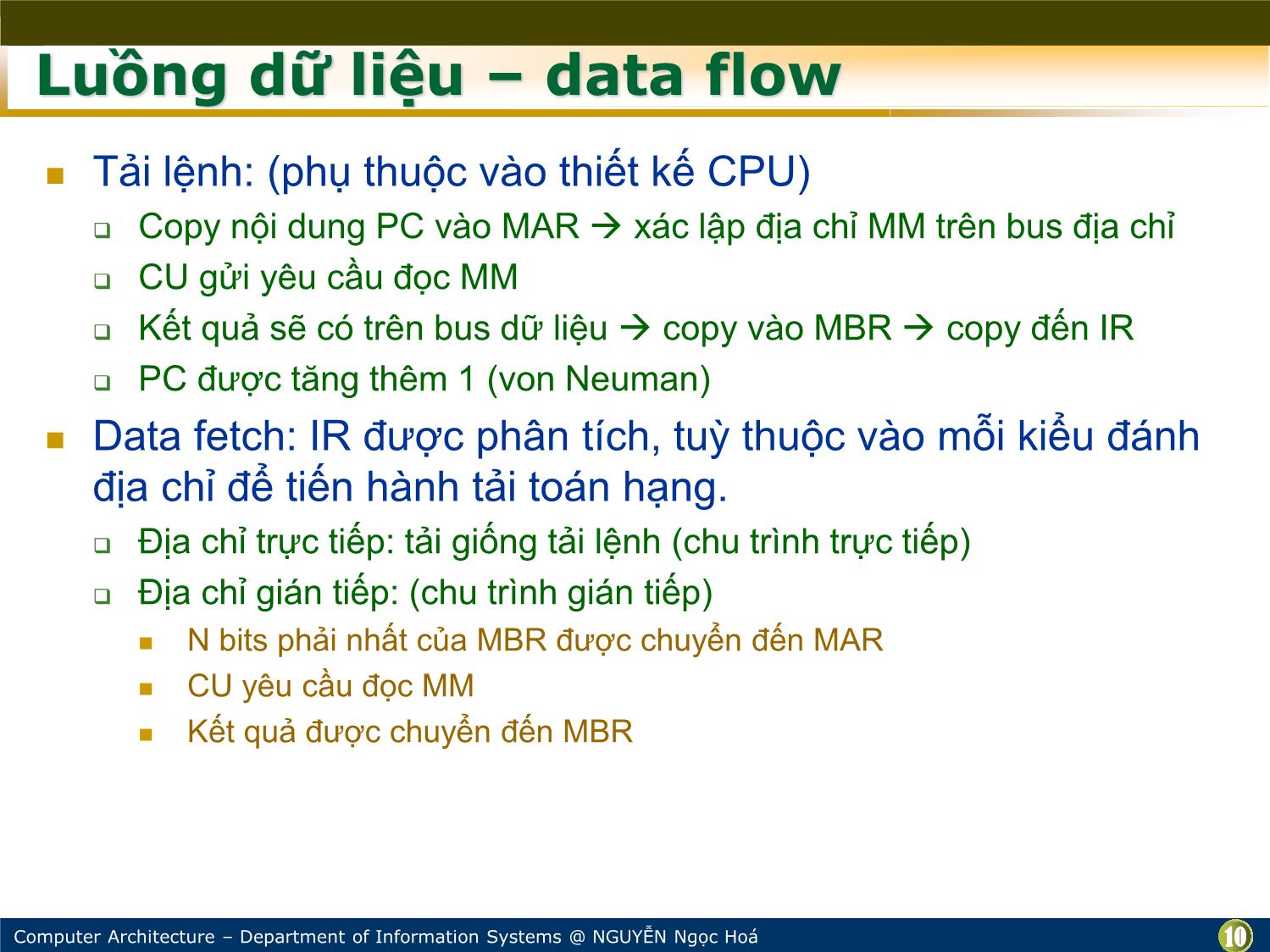

Kiến trúc máy tính CPU NGUYỄN Ngọc Hoá Bộ môn Hệ thống thông tin, Khoa CNTT Trường Đại học Công nghệ, Đại học Quốc gia Hà Nội 2 December 2015 Hoa.Nguyen@vnu.edu.vn Tổ chức và chức năng của CPU Cấu trúc CPU Pipeline CISC & RISC Superscalar, VLIW Tham khảo chương 12, 13 của [1] Computer Architecture –DepartmentDepartment ofof InformationInformation SystemsSystems @@ HoáNGUYỄN NGUYEN Ngọc Hoá 2 1. Cấu trúc của CPU CPU đảm nhiệm Đơn vị tính toán (ALU, FPU) Tải lệnh Đơn vị điều khiển Dịch lệnh Registers (data, address, Tải dữ liệu instruction, control) Xử lý dữ liệu Internal bus Lưu dữ liệu Computer Architecture –DepartmentDepartment ofof InformationInformation SystemsSystems @@ HoáNGUYỄN NGUYEN Ngọc Hoá 3 Registers Bộ nhớ trong của CPU registers được sử dụng trong các chương trình (user visible regs) registers điều khiển và thể hiện trạng thái được sử dụng bởi CPU được sử dụng bởi OS Chú ý Ít thanh ghi tham chiếu MM nhiều hơn Quá nhiều registers cũng không làm giảm nhiều tham chiếu MM, giảm hiệu năng CPU Đủ rộng để chứa được trường địa chỉ Đủ rộng để chứa từ nhớ Có thể ghép nhiều registers tạo word lớn hơn Computer Architecture –DepartmentDepartment ofof InformationInformation SystemsSystems @@ HoáNGUYỄN NGUYEN Ngọc Hoá 4 User Visible Registers Đa dụng - General Purpose Dữ liệu - Data Địa chỉ - Address: thường được sử dụng trong các mode đánh địa chỉ Segment based address (e.g., pentium) index pointer to memory stack Cờ nhớ - Condition codes (flags) : dãy các bits độc lập với nhau chương trình không thể thay đổi giá trị, chỉ có thể được đọc Computer Architecture –DepartmentDepartment ofof InformationInformation SystemsSystems @@ HoáNGUYỄN NGUYEN Ngọc Hoá 5 Control & Status Registers Trao đổi dữ liệu với bộ nhớ chính Program Counter (PC) : địa chỉ của lệnh thi hành kế tiếp Instruction Decoding Register (IR) : lệnh đang thi hành Memory Address Register (MAR) : địa chỉ bộ nhớ, kết nối trực tiếp tới bus địa chỉ Memory Buffer Register (MBR) : từ dữ liệu, kết nối trực tiếp đến bus dữ liệu Những registers trung gian Computer Architecture –DepartmentDepartment ofof InformationInformation SystemsSystems @@ HoáNGUYỄN NGUYEN Ngọc Hoá 6 Program Status Word Tập các bits thể hiện trạng thái phép tính vừa thực hiện trong CPU - Condition Codes Sign of last result Zero Carry Equal Overflow Interrupt enable/disable Supervisor Supervisor/Kernel mode Cho phép thi hành những lệnh đặc quyền (system calls) Được sử dụng bởi hệ điều hành và người sử dụng/programers không được cấp phép sử dụng chế độ này Computer Architecture –DepartmentDepartment ofof InformationInformation SystemsSystems @@ HoáNGUYỄN NGUYEN Ngọc Hoá 7 Ví dụ tổ chức thanh ghi Computer Architecture –DepartmentDepartment ofof InformationInformation SystemsSystems @@ HoáNGUYỄN NGUYEN Ngọc Hoá 8 Thi hành một chương trình Computer Architecture –DepartmentDepartment ofof InformationInformation SystemsSystems @@ HoáNGUYỄN NGUYEN Ngọc Hoá 9 Luồng dữ liệu – data flow Tải lệnh: (phụ thuộc vào thiết kế CPU) Copy nội dung PC vào MAR xác lập địa chỉ MM trên bus địa chỉ CU gửi yêu cầu đọc MM Kết quả sẽ có trên bus dữ liệu copy vào MBR copy đến IR PC được tăng thêm 1 (von Neuman) Data fetch: IR được phân tích, tuỳ thuộc vào mỗi kiểu đánh địa chỉ để tiến hành tải toán hạng. Địa chỉ trực tiếp: tải giống tải lệnh (chu trình trực tiếp) Địa chỉ gián tiếp: (chu trình gián tiếp) N bits phải nhất của MBR được chuyển đến MAR CU yêu cầu đọc MM Kết quả được chuyển đến MBR Computer Architecture –DepartmentDepartment ofof InformationInformation SystemsSystems @@ HoáNGUYỄN NGUYEN Ngọc Hoá 10 Data Flow : Fetch Diagram Computer Architecture –DepartmentDepartment ofof InformationInformation SystemsSystems @@ HoáNGUYỄN NGUYEN Ngọc Hoá 11 Data Flow : Indirect Diagram Computer Architecture –DepartmentDepartment ofof InformationInformation SystemsSystems @@ HoáNGUYỄN NGUYEN Ngọc Hoá 12 Data Flow : Execute Có thể thể hiện dưới nhiều hình thức khác nhau Phụ thuộc vào lệnh thi hành Có thể kèm theo Memory-I/O read/write ALU operations Computer Architecture –DepartmentDepartment ofof InformationInformation SystemsSystems @@ HoáNGUYỄN NGUYEN Ngọc Hoá 13 Data Flow : Interrupt Lưu PC hiện thời để có thể tiếp tục sau khi interrupt Contents of PC copied to MBR Special memory location (e.g. stack pointer) loaded to MAR MBR written to memory PC địa chỉ của hàm xử lý ngắt Next instruction (first of interrupt handler) can be fetched Computer Architecture –DepartmentDepartment ofof InformationInformation SystemsSystems @@ HoáNGUYỄN NGUYEN Ngọc Hoá 14 2. Pipeline Idea: Fetching: thường truy cập bộ nhớ chính Execution: thường không truy cập bộ nhớ chính Liệu có thể tải lệnh kế tiếp trong quá trình thi hành lệnh hiện thời ? Tải trước lệnh - instruction prefetch: thêm các tầng để cải thiện hiệu năng Fetch thường có thời gian thực thi ngắn hơn so với Execute Prefetch more than one instruction? Tuy nhiên, với các lệnh rẽ nhánh/nhảy: tải trước có thể không cải thiện được hiệu năng! Computer Architecture –DepartmentDepartment ofof InformationInformation SystemsSystems @@ HoáNGUYỄN NGUYEN Ngọc Hoá 15 Pipeline lệnh hai tầng Computer Architecture –DepartmentDepartment ofof InformationInformation SystemsSystems @@ HoáNGUYỄN NGUYEN Ngọc Hoá 16 Pipelining Chia việc thi hành một lệnh thành nhiều bước con: Fetch instruction Decode instruction Calculate operands (i.e. EAs) Fetch operands Execute instruction Write operands Thi hành gối đầu nhau (overlap) các thao tác con trên Computer Architecture –DepartmentDepartment ofof InformationInformation SystemsSystems @@ HoáNGUYỄN NGUYEN Ngọc Hoá 17 Biểu đồ thời gian thao tác trong pipeline lệnh Computer Architecture –DepartmentDepartment ofof InformationInformation SystemsSystems @@ HoáNGUYỄN NGUYEN Ngọc Hoá 18 Ảnh hưởng của rẽ nhánh có điều kiện trong các bộ pipeline Computer Architecture –DepartmentDepartment ofof InformationInformation SystemsSystems @@ HoáNGUYỄN NGUYEN Ngọc Hoá 19 Pipeline lệnh sáu tầng Computer Architecture –DepartmentDepartment ofof InformationInformation SystemsSystems @@ HoáNGUYỄN NGUYEN Ngọc Hoá 20

File đính kèm:

bai_giang_kien_truc_may_tinh_chuong_cpu_nguyen_ngoc_hoa.pdf

bai_giang_kien_truc_may_tinh_chuong_cpu_nguyen_ngoc_hoa.pdf