Bài giảng Kiến trúc máy tính - Chương 8: Hệ thống vào-ra - Nguyễn Kim Khánh

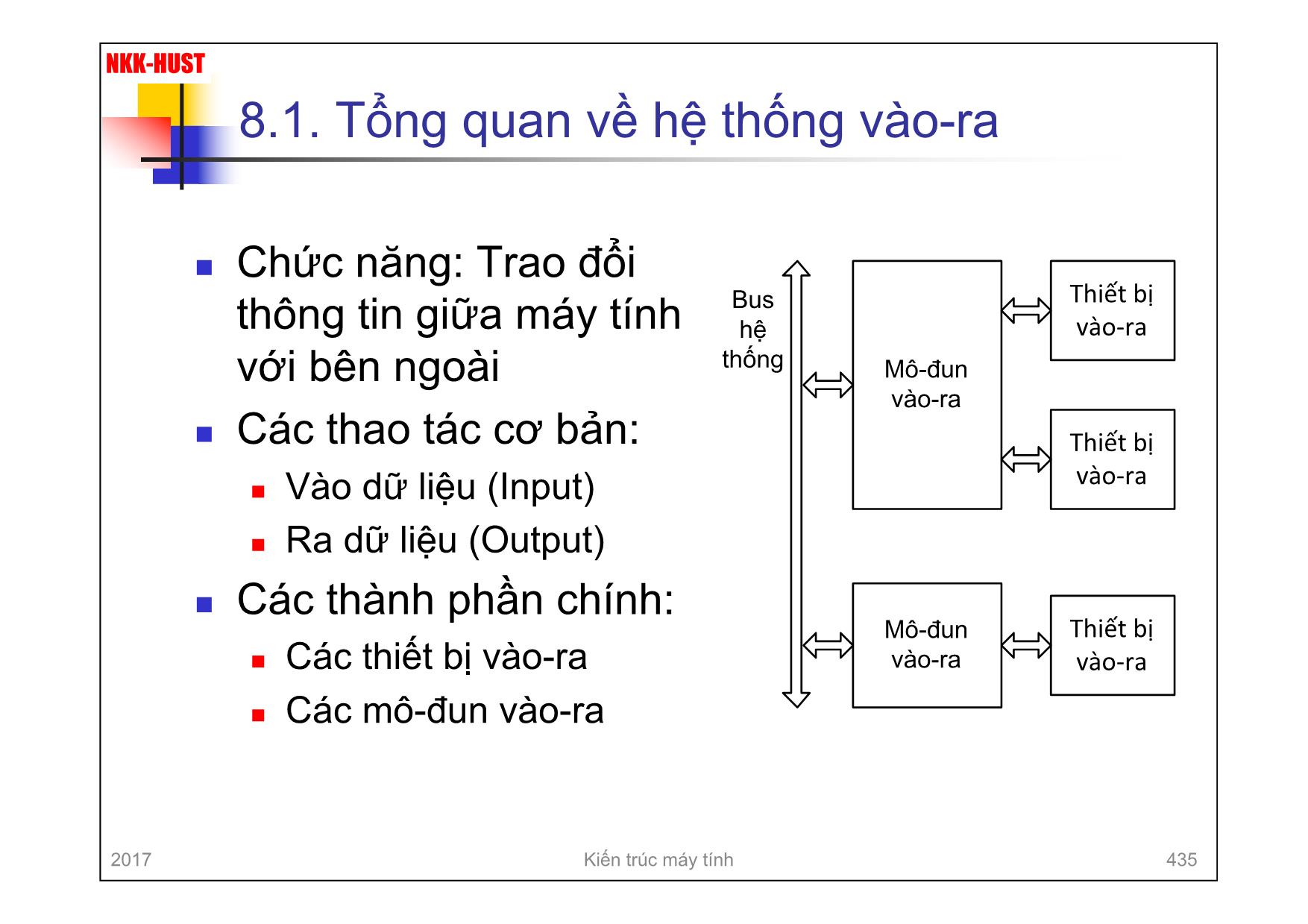

8.1. Tổng quan về hệ thống vào-ra

n Chức năng: Trao đổi

thông tin giữa máy tính

với bên ngoài

n Các thao tác cơ bản:

n Vào dữ liệu (Input)

n Ra dữ liệu (Output)

n Các thành phần chính:

n Các thiết bị vào-ra

n Các mô-đun vào-ra

Trang 1

Trang 2

Trang 3

Trang 4

Trang 5

Trang 6

Trang 7

Trang 8

Trang 9

Trang 10

Tải về để xem bản đầy đủ

Bạn đang xem 10 trang mẫu của tài liệu "Bài giảng Kiến trúc máy tính - Chương 8: Hệ thống vào-ra - Nguyễn Kim Khánh", để tải tài liệu gốc về máy hãy click vào nút Download ở trên

Tóm tắt nội dung tài liệu: Bài giảng Kiến trúc máy tính - Chương 8: Hệ thống vào-ra - Nguyễn Kim Khánh

3 NKK-HUST Vào-ra theo bản đồ bộ nhớ n Cổng vào-ra được đánh địa chỉ theo không gian địa chỉ bộ nhớ n CPU coi cổng vào-ra như ngăn nhớ n Lập trình trao đổi dữ liệu với cổng vào-ra bằng các lệnh truy nhập dữ liệu bộ nhớ n Có thể thực hiện trên mọi hệ thống n Ví dụ: Bộ xử lý MIPS n 32-bit địa chỉ cho một không gian địa chỉ chung cho cả các ngăn nhớ và các cổng vào-ra n Các cổng vào-ra được gắn các địa chỉ thuộc vùng địa chỉ dự trữ n Vào/ra dữ liệu: sử dụng lệnh load/store 2017 Kiến trúc máy tính 444 NKK-HUST Ví dụ lập trình vào-ra cho MIPS n Ví dụ: Có hai cổng vào-ra được gán địa chỉ: n Cổng 1: 0xFFFFFFF4 n Cổng 2: 0xFFFFFFF8 n Ghi giá trị 0x41 ra cổng 1 addi $t0, $0, 0x41 # đưa giá trị 0x41 sw $t0, 0xFFF4($0) # ra cổng 1 Chú ý: giá trị 16-bit 0xFFF4 được sign-extended thành 32-bit 0xFFFFFFF4 n Đọc dữ liệu từ cổng 2 đưa vào $t3 lw $t3, 0xFFF8($0) # đọc dữ liệu cổng 2 đưa vào $t3 2017 Kiến trúc máy tính 445 NKK-HUST Vào-ra riêng biệt (Isolated IO) n Cổng vào-ra được đánh địa chỉ theo không gian địa chỉ vào-ra riêng n Lập trình trao đổi dữ liệu với cổng vào-ra bằng các lệnh vào-ra chuyên dụng n Ví dụ: Intel x86 n Dùng 8-bit hoặc 16-bit địa chỉ cho không gian địa chỉ vào-ra riêng n Có hai lệnh vào-ra chuyên dụng n Lệnh IN: nhận dữ liệu từ cổng vào n Lệnh OUT: đưa dữ liệu đến cổng ra 2017 Kiến trúc máy tính 446 NKK-HUST 8.2. Các phương pháp điều khiển vào-ra n Vào-ra bằng chương trình (Programmed IO) n Vào-ra điều khiển bằng ngắt (Interrupt Driven IO) n Truy nhập bộ nhớ trực tiếp - DMA (Direct Memory Access) 2017 Kiến trúc máy tính 447 NKK-HUST Ba kỹ thuật thực hiện vào một khối dữ liệu230 CHAPTER 7 / INPUT/OUTPUT Figure 7.4a gives an example of the use of programmed I/O to read in a block of data from a peripheral device (e.g., a record from tape) into memory. Data are read in one word (e.g., 16 bits) at a time. For each word that is read in, the processor must remain in a status-checking cycle until it determines that the word is available in the I/O module’s data register. This flowchart highlights the main disadvantage of this technique: it is a time-consuming process that keeps the processor busy needlessly. I/O Instructions With programmed I/O, there is a close correspondence between the I/O-related instructions that the processor fetches from memory and the I/O commands that the processor issues to an I/O module to execute the instructions. That is, the instruc- tions are easily mapped into I/O commands, and there is often a simple one-to-one relationship. The form of the instruction depends on the way in which external devices are addressed. Typically, there will be many I/O devices connected through I/O modules to the system. Each device is given a unique identifier or address. When the processor issues an I/O command, the command contains the address of the desired device. Thus, each I/O module must interpret the address lines to determine if the com- mand is for itself. Issue read command to I/O module Read status of I/O module Check Status Read word from I/O module Write word into memory Done? Next instruction (a) Programmed I/O Error condition Ready Ready Yes Yes No Not ready Issue read command to I/O module Do something else InterruptRead status of I/O module Check status Read word from I/O module Write word into memory Done? Next instruction (b) Interrupt-Driven I/O Do something else Interrupt Error condition No Issue read block command to I/O module Read status of DMA module Next instruction (c) Direct Memory Access CPU DMA DMA CPU CPU I/O CPU I/O I/O CPU I/O CPU I/O CPU CPU Memory I/O CPU CPU Memory Figure 7.4 Three Techniques for Input of a Block of Data 2017 Kiến trúc máy tính 448 NKK-HUST 1. Vào-ra bằng chương trình n Nguyên tắc chung: n CPU điều khiển trực tiếp vào-ra bằng chương trình à cần phải lập trình vào-ra để trao đổi dữ liệu giữa CPU với mô-đun vào-ra n CPU nhanh hơn thiết bị vào-ra rất nhiều lần, vì vậy trước khi thực hiện lệnh vào-ra, chương trình cần đọc và kiểm tra trạng thái sẵn sàng của mô-đun vào-ra 2017 Kiến trúc máy tính 449 Đọc trạng thái mô-đun vào-ra Trao đổi dữ liệu Sẵn sàng ? Y N NKK-HUST Các tín hiệu điều khiển vào-ra n Tín hiệu điều khiển (Control): kích hoạt thiết bị vào-ra n Tín hiệu kiểm tra (Test): kiểm tra trạng thái của mô-đun vào-ra và thiết bị vào-ra n Tín hiệu điều khiển đọc (Read): yêu cầu mô- đun vào-ra nhận dữ liệu từ thiết bị vào-ra và đưa vào bộ đệm dữ liệu, rồi CPU nhận dữ liệu đó n Tín hiệu điều khiển ghi (Write): yêu cầu mô- đun vào-ra lấy dữ liệu trên bus dữ liệu đưa đến bộ đệm dữ liệu rồi chuyển ra thiết bị vào-ra 2017 Kiến trúc máy tính 450 NKK-HUST Các lệnh vào-ra n Với vào-ra theo bản đồ bộ nhớ: sử dụng các lệnh trao đổi dữ liệu với bộ nhớ để trao đổi dữ liệu với cổng vào-ra n Với vào-ra riêng biệt: sử dụng các lệnh vào-ra chuyên dụng (IN, OUT) 2017 Kiến trúc máy tính 451 NKK-HUST Đặc điểm n Vào-ra do ý muốn của người lập trình n CPU trực tiếp điều khiển trao đổi dữ liệu giữa CPU với mô-đun vào-ra n CPU đợi mô-đun vào-ra à tiêu tốn nhiều thời gian của CPU 2017 Kiến trúc máy tính 452 NKK-HUST 2. Vào-ra điều khiển bằng ngắt n Nguyên tắc chung: n CPU không phải đợi trạng thái sẵn sàng của mô-đun vào-ra, CPU thực hiện một chương trình nào đó n Khi mô-đun vào-ra sẵn sàng thì nó phát tín hiệu ngắt CPU n CPU thực hiện chương trình con xử lý ngắt vào-ra tương ứng để trao đổi dữ liệu n CPU trở lại tiếp tục thực hiện chương trình đang bị ngắt 2017 Kiến trúc máy tính 453 NKK-HUST Chuyển điều khiển đến chương trình con ngắt 2017 Kiến trúc máy tính 454 lệnh i+1 lệnh i lệnh lệnh lệnh Ngắt ở đây . . . lệnh lệnh lệnh RETURN . . . lệnh lệnh Chương trình đang thực hiện Chương trình con xử lý ngắt lệnh NKK-HUST Hoạt động vào dữ liệu: nhìn từ mô-đun vào-ra n Mô-đun vào-ra nhận tín hiệu điều khiển đọc từ CPU n Mô-đun vào-ra nhận dữ liệu từ thiết bị vào-ra, trong khi đó CPU làm việc khác n Khi đã có dữ liệu à mô-đun vào-ra phát tín hiệu ngắt CPU n CPU yêu cầu dữ liệu n Mô-đun vào-ra chuyển dữ liệu đến CPU 2017 Kiến trúc máy tính 455 NKK-HUST Hoạt động vào dữ liệu: nhìn từ CPU n Phát tín hiệu điều khiển đọc n Làm việc khác n Cuối mỗi chu trình lệnh, kiểm tra tín hiệu yêu cầu ngắt n Nếu bị ngắt: n Cất ngữ cảnh (nội dung các thanh ghi liên quan) n Thực hiện chương trình con xử lý ngắt để vào dữ liệu n Khôi phục ngữ cảnh của chương trình đang thực hiện 2017 Kiến trúc máy tính 456 NKK-HUST Các vấn đề nảy sinh khi thiết kế n Làm thế nào để xác định được mô-đun vào-ra nào phát tín hiệu ngắt ? n CPU làm như thế nào khi có nhiều yêu cầu ngắt cùng xẩy ra ? 2017 Kiến trúc máy tính 457 NKK-HUST Các phương pháp nối ghép ngắt n Sử dụng nhiều đường yêu cầu ngắt n Hỏi vòng bằng phần mềm (Software Poll) n Hỏi vòng bằng phần cứng (Daisy Chain or Hardware Poll) n Sử dụng bộ điều khiển ngắt (PIC) 2017 Kiến trúc máy tính 458 NKK-HUST Nhiều đường yêu cầu ngắt n Mỗi mô-đun vào-ra được nối với một đường yêu cầu ngắt n CPU phải có nhiều đường tín hiệu yêu cầu ngắt n Hạn chế số lượng mô-đun vào-ra n Các đường ngắt được qui định mức ưu tiên CPU Mô-đun vào-ra INTR3 INTR2 INTR1 INTR0 Thanh ghi yêu cầu ngắt Mô-đun vào-ra Mô-đun vào-ra Mô-đun vào-ra 2017 Kiến trúc máy tính 459 NKK-HUST Hỏi vòng bằng phần mềm n CPU thực hiện phần mềm hỏi lần lượt từng mô-đun vào-ra n Chậm n Thứ tự các mô-đun được hỏi vòng chính là thứ tự ưu tiên CPU Mô-đun vào-ra INTRCờ ngắt Mô-đun vào-ra Mô-đun vào-ra Mô-đun vào-ra 2017 Kiến trúc máy tính 460 NKK-HUST Hỏi vòng bằng phần cứng CPU Mô-đun vào-ra INTRCờ ngắt Bus dữ liệu Mô-đun vào-ra Mô-đun vào-ra Mô-đun vào-ra INTA 2017 Kiến trúc máy tính 461 NKK-HUST Hỏi vòng bằng phần cứng (tiếp) n CPU phát tín hiệu chấp nhận ngắt (INTA) đến mô-đun vào-ra đầu tiên n Nếu mô-đun vào-ra đó không gây ra ngắt thì nó gửi tín hiệu đến mô-đun kế tiếp cho đến khi xác định được mô-đun gây ngắt n Thứ tự các mô-đun vào-ra kết nối trong chuỗi xác định thứ tự ưu tiên 2017 Kiến trúc máy tính 462 NKK-HUST Bộ điều khiển ngắt lập trình được n PIC – Programmable Interrupt Controller n PIC có nhiều đường vào yêu cầu ngắt có qui định mức ưu tiên n PIC chọn một yêu cầu ngắt không bị cấm có mức ưu tiên cao nhất gửi tới CPU CPU Mô-đun vào-ra INTR n INTRn-1 INTR1 INTR0 Mô-đun vào-ra Mô-đun vào-ra Mô-đun vào-ra PIC . . .INTR INTA Bus dữ liệu 2017 Kiến trúc máy tính 463 NKK-HUST Đặc điểm của vào-ra điều khiển bằng ngắt n Có sự kết hợp giữa phần cứng và phần mềm n Phần cứng: gây ngắt CPU n Phần mềm: trao đổi dữ liệu giữa CPU với mô-đun vào-ra n CPU trực tiếp điều khiển vào-ra n CPU không phải đợi mô-đun vào-ra, do đó hiệu quả sử dụng CPU tốt hơn 2017 Kiến trúc máy tính 464 NKK-HUST 3. DMA (Direct Memory Access) n Vào-ra bằng chương trình và bằng ngắt do CPU trực tiếp điều khiển: n Chiếm thời gian của CPU n Để khắc phục dùng kỹ thuật DMA n Sử dụng mô-đun điều khiển vào-ra chuyên dụng, gọi là DMAC (Controller), điều khiển trao đổi dữ liệu giữa mô-đun vào-ra với bộ nhớ chính 2017 Kiến trúc máy tính 465 NKK-HUST Sơ đồ cấu trúc của DMAC Bộ đếm dữ liệu Logic điều khiển Thanh ghi địa chỉ Thanh ghi dữ liệu Các đường dữ liệu Các đường địa chỉ Yêu cầu bus Chuyển nhượng bus Ngắt Đọc Ghi Điều khiển đọc Điều khiển ghi Yêu cầu DMA Chấp nhận DMA 2017 Kiến trúc máy tính 466 NKK-HUST Các thành phần của DMAC n Thanh ghi dữ liệu: chứa dữ liệu trao đổi n Thanh ghi địa chỉ: chứa địa chỉ ngăn nhớ dữ liệu n Bộ đếm dữ liệu: chứa số từ dữ liệu cần trao đổi n Logic điều khiển: điều khiển hoạt động của DMAC 2017 Kiến trúc máy tính 467 NKK-HUST Hoạt động DMA n CPU “nói” cho DMAC n Vào hay Ra dữ liệu n Địa chỉ thiết bị vào-ra (cổng vào-ra tương ứng) n Địa chỉ đầu của mảng nhớ chứa dữ liệu à nạp vào thanh ghi địa chỉ n Số từ dữ liệu cần truyền à nạp vào bộ đếm dữ liệu n CPU làm việc khác n DMAC điều khiển trao đổi dữ liệu n Sau khi truyền được một từ dữ liệu thì: n nội dung thanh ghi địa chỉ tăng n nội dung bộ đếm dữ liệu giảm n Khi bộ đếm dữ liệu = 0, DMAC gửi tín hiệu ngắt CPU để báo kết thúc DMA 2017 Kiến trúc máy tính 468 NKK-HUST Các kiểu thực hiện DMA n DMA truyền theo khối (Block-transfer DMA): DMAC sử dụng bus để truyền xong cả khối dữ liệu n DMA lấy chu kỳ (Cycle Stealing DMA): DMAC cưỡng bức CPU treo tạm thời từng chu kỳ bus, DMAC chiếm bus thực hiện truyền một từ dữ liệu. n DMA trong suốt (Transparent DMA): DMAC nhận biết những chu kỳ nào CPU không sử dụng bus thì chiếm bus để trao đổi một từ dữ liệu. 2017 Kiến trúc máy tính 469 NKK-HUST Cấu hình DMA (1) n Mỗi lần trao đổi một dữ liệu, DMAC sử dụng bus hai lần n Giữa mô-đun vào-ra với DMAC n Giữa DMAC với bộ nhớ CPU . . . DMAC MemoryI/OModule I/O Module System Bus 2017 Kiến trúc máy tính 470 NKK-HUST Cấu hình DMA (2) n DMAC điều khiển một hoặc vài mô-đun vào-ra n Mỗi lần trao đổi một dữ liệu, DMAC sử dụng bus một lần n Giữa DMAC với bộ nhớ CPU . . . DMAC Memory I/O Module I/O Module I/O Module DMAC System Bus 2017 Kiến trúc máy tính 471 NKK-HUST Cấu hình DMA (3) n Bus vào-ra tách rời hỗ trợ tất cả các thiết bị cho phép DMA n Mỗi lần trao đổi một dữ liệu, DMAC sử dụng bus một lần n Giữa DMAC với bộ nhớ CPU . . . Memory I/O Module I/O Module I/O Module DMAC System Bus IO Bus 2017 Kiến trúc máy tính 472 NKK-HUST Đặc điểm của DMA n CPU không tham gia trong quá trình trao đổi dữ liệu n DMAC điều khiển trao đổi dữ liệu giữa bộ nhớ chính với mô-đun vào-ra (hoàn toàn bằng phần cứng)à tốc độ nhanh n Phù hợp với các yêu cầu trao đổi mảng dữ liệu có kích thước lớn 2017 Kiến trúc máy tính 473 NKK-HUST 4. Bộ xử lý vào-ra n Việc điều khiển vào-ra được thực hiện bởi một bộ xử lý vào-ra chuyên dụng n Bộ xử lý vào-ra hoạt động theo chương trình của riêng nó n Chương trình của bộ xử lý vào-ra có thể nằm trong bộ nhớ chính hoặc nằm trong một bộ nhớ riêng 2017 Kiến trúc máy tính 474 NKK-HUST 8.3. Nối ghép thiết bị vào-ra 1. Các kiểu nối ghép vào-ra n Nối ghép song song n Nối ghép nối tiếp 2017 Kiến trúc máy tính 475 NKK-HUST Nối ghép song song n Truyền nhiều bit song song n Tốc độ nhanh n Cần nhiều đường truyền dữ liệu Mô-đun vào-ra song song Đến thiết bị vào-ra Đến bus hệ thống 2017 Kiến trúc máy tính 476 NKK-HUST Nối ghép nối tiếp n Truyền lần lượt từng bit n Cần có bộ chuyển đổi từ dữ liệu song song sang nối tiếp hoặc/và ngược lại n Tốc độ chậm hơn n Cần ít đường truyền dữ liệu Mô-đun vào-ra nối tiếp Đến thiết bị vào-ra Đến bus hệ thống 2017 Kiến trúc máy tính 477 NKK-HUST 2. Các cấu hình nối ghép n Điểm tới điểm (Point to Point) n Thông qua một cổng vào-ra nối ghép với một thiết bị n Điểm tới đa điểm (Point to Multipoint) n Thông qua một cổng vào-ra cho phép nối ghép được với nhiều thiết bị n Ví dụ: n USB (Universal Serial Bus): 127 thiết bị n IEEE 1394 (FireWire): 63 thiết bị n Thunderbolt 2017 Kiến trúc máy tính 478 NKK-HUST Thunderbolt 7.7 / THE EXTERNAL INTERFACE: THUNDERBOLT AND INFINIBAND 251 THUNDERBOLT PROTOCOL ARCHITECTURE Figure 7.18 illustrates the Thunderbolt protocol architecture. The cable and connector layer provides transmission medium access. This layer specifies the physical and electrical attributes of the connector port. The Thunderbolt protocol physical layer is responsible for link maintenance including hot-plug3 detection and data encoding to provide highly efficient data transfer. The physical layer has been designed to introduce very minimal overhead and provides full-duplex 10 Gbps of usable capacity to the upper layers. The common transport layer is the key to the operation of Thunderbolt and what makes it attractive as a high-speed peripheral I/O technology. Some of the features include: • A high-performance, low-power, switching architecture. • A highly efficient, low-overhead packet format with flexible quality of service (QoS) support that allows multiplexing of bursty PCI Express transactions Processor COMPUTER Platform controller hub (PCH) Thunderbolt controller Memory TC TC TC Daisy chain Thunderbolt connector Thunderbolt 20 Gbps (max) PCIe x4 DisplayPort Graphics Sub- system DisplayPort Figure 7.17 Example Computer Configuration with Thunderbolt 3The term hot plug is defined as pulling out a component from a system and plugging in a new one while the main power is still on. It allows an external drive, network adapter, or other peripheral to be plugged in without having to power down the computer. 2017 Kiến trúc máy tính 479 NKK-HUST Hết chương 8 2017 Kiến trúc máy tính 480

File đính kèm:

bai_giang_kien_truc_may_tinh_chuong_8_he_thong_vao_ra_nguyen.pdf

bai_giang_kien_truc_may_tinh_chuong_8_he_thong_vao_ra_nguyen.pdf