Bài giảng Kiến trúc máy tính - Chương 7: Đầu vào/Đầu ra - Nguyễn Hằng Phương

Tổng quan về hệ thống Vào/ra

Chức năng của hệ thống vào-ra: Trao đổi thông tin giữa máy tính với

thế giới bên ngoài

Thành phần chính:

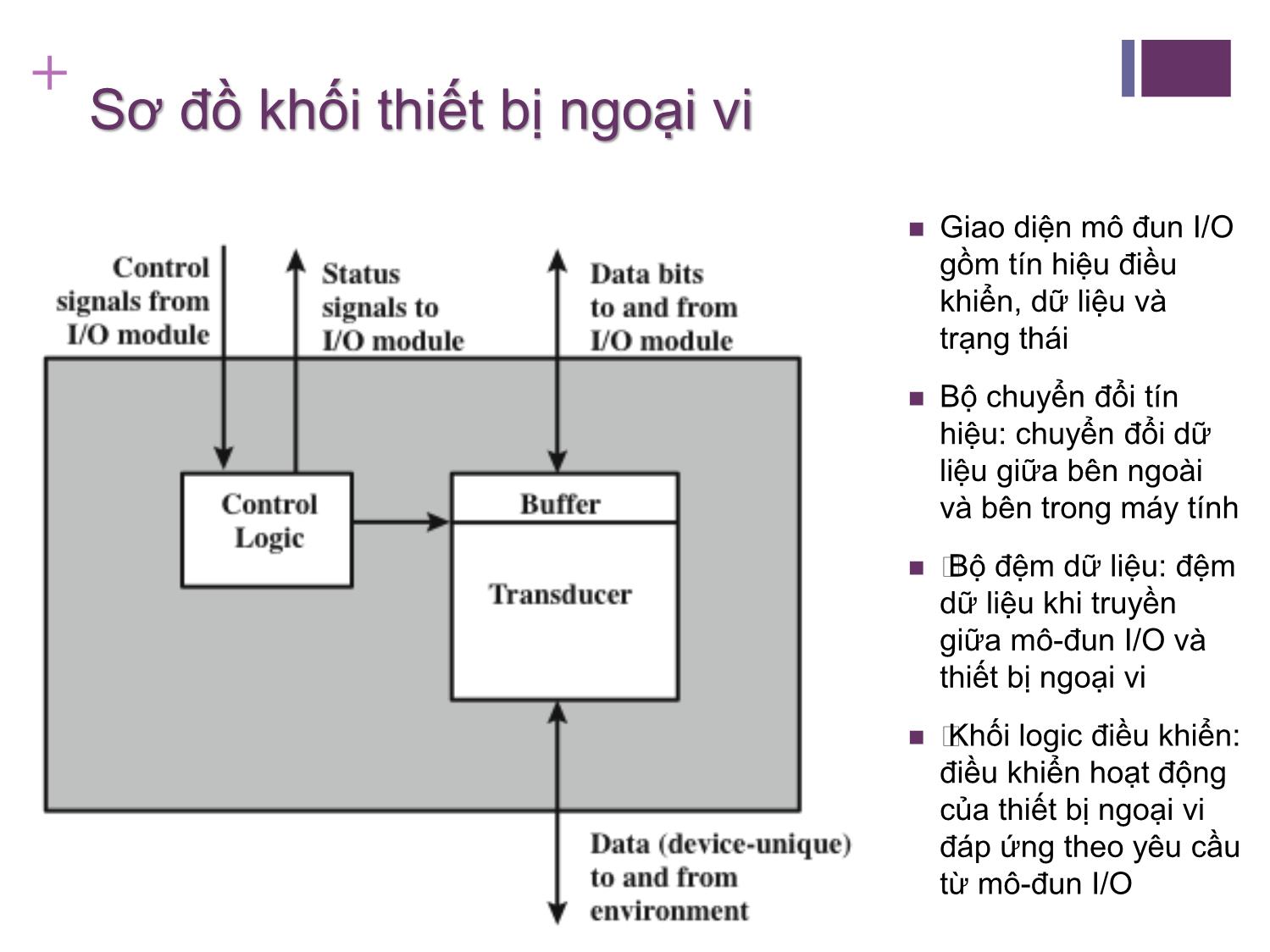

Các thiết bị ngoại vi

Các mô-đun I/O

Tại sao không kết nối thiết bị ngoại vi trực tiếp với hệ thống bus?

Có rất nhiều thiết bị ngoại vi khác nhau

Truyền lượng dữ liệu khác nhau

Tốc độ truyền dữ liệu khác nhau

Ở định dạng khác nhau

Tốc độ truyền của thiết bị ngoại vi chậm hơn tốc độ của CPU và RAM

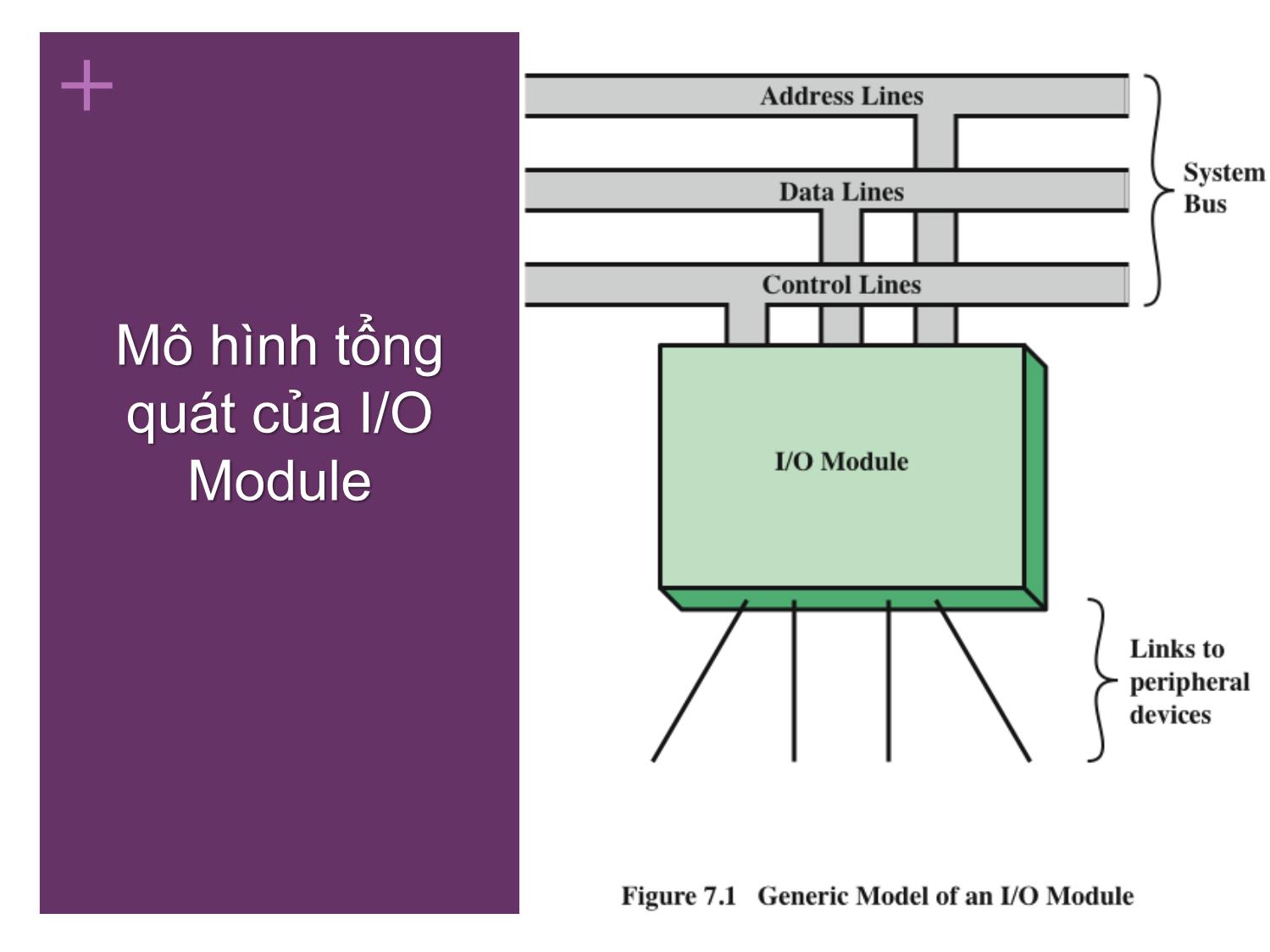

Cần các mô-đun I/O

Không chỉ là dây kết nối để nối một thiết bị vào bus hệ thống.

Còn chứa logic để thực hiện truyền thông giữa thiết bị ngoại vi và bus

Trang 1

Trang 2

Trang 3

Trang 4

Trang 5

Trang 6

Trang 7

Trang 8

Trang 9

Trang 10

Tải về để xem bản đầy đủ

Bạn đang xem 10 trang mẫu của tài liệu "Bài giảng Kiến trúc máy tính - Chương 7: Đầu vào/Đầu ra - Nguyễn Hằng Phương", để tải tài liệu gốc về máy hãy click vào nút Download ở trên

Tóm tắt nội dung tài liệu: Bài giảng Kiến trúc máy tính - Chương 7: Đầu vào/Đầu ra - Nguyễn Hằng Phương

hiển thị trên màn hình truyền đến một thiết bị ngoại vi từ Điều khiển mô-đun I/O Điều khiển việc in/hiển thị các ký Bộ biến đổi giải mã và gửi các tín tự hiệu điện cần thiết đến thiết bị đầu Các ký tự điều khiển khác liên ra để hiển thị ký tự được chỉ định quan đến các thủ tục truyền tin hoặc thực hiện chức năng điều khiển yêu cầu 9 2. Module I/O Chức năng của Module I/O: . Điều khiển và định thời . Phối hợp luồng lưu lượng truy cập giữa tài nguyên bên trong và thiết bị ngoại vi . Trao đổi thông tin với bộ xử lý . Gồm giải mã lệnh, dữ liệu, báo cáo trạng thái, nhận dạng địa chỉ . Trao đổi thông tin với thiết bị . Gồm các lệnh, thông tin trạng thái và dữ liệu . Đệm dữ liệu . Thực hiện các hoạt động đệm cần thiết để cân bằng tốc độ thiết bị và bộ nhớ . Phát hiện lỗi . Phát hiện và báo cáo lỗi truyền 10 Các bước I/O . CPU hỏi module I/O để kiểm tra trạng thái thiết bị I/O được gắn vào . Môđun I/O trả về trạng thái thiết bị . Nếu thiết bị đã sẵn sàng, CPU yêu cầu truyền dữ liệu bằng cách gửi một lệnh tới mô đun I / O . Môđun I/O nhận dữ liệu từ thiết bị . I/O module truyền dữ liệu đến CPU Cấu trúc Module I/O 11 + 12 Các thành phần của mô-đun vào-ra Thanh ghi đệm dữ liệu: đệm dữ liệu trong quá trình trao đổi Các cổng vào-ra (I/O Port): kết nối với thiết bị ngoại vi, mỗi cổng cómột địa chỉ xác định Thanh ghi trạng thái/điều khiển: lưu giữ thông tin trạng thái/điều khiển cho các cổng vào-ra Khối logic điều khiển: điều khiển mô-đun vào-ra + 13 Địa chỉ hoá cổng vào-ra Không gian địa chỉ của bộ xử lý + 14 Không gian địa chỉ của bộ xử lý Một số bộ xử lý chỉ quản lý duy nhất một không gian địa chỉ: không gian địa chỉ bộ nhớ: 2N địa chỉ Ví dụ: Các bộ xử lý 680x0 (Motorola) Một số bộ xử lý quản lý hai không gian địa chỉ tách biệt: „ Không gian địa chỉ bộ nhớ: 2N địa chỉ Không gian địa chỉ vào-ra: 2N1 địa chỉ „ Có tín hiệu điều khiển phân biệt truy cập không gian địa chỉ „ Tập lệnh có các lệnh vào-ra chuyên dụng \ „ Vídụ: Pentium (Intel) + 15 Các phương pháp ánh xạ địa chỉ vào-ra I/O ánh xạ bộ nhớ Thiết bị và bộ nhớ chia sẻ một không gian địa chỉ Cổng vào-ra đánh địa chỉ theo không gian địa chỉ bộ nhớ Không có mệnh lệnh đặc biệt cho I/O CPU dùng chung lệnh máy để truy cập cả bộ nhớ và thiết bị I/O bus cần có một dòng đọc riêng và một dòng ghi riêng I/O - bộ nhớ tách biệt Không gian địa chỉ riêng biệt Cổng vào-ra được đánh địa chỉ theo không gian địa chỉ vào-ra Cần có dòng chọn I/O hoặc bộ nhớ Mệnh lệnh đặc biệt cho I/O 16 I/O ánh xạ bộ nhớ và I/O - bộ nhớ tách biệt + 17 3. Các kỹ thuật vào/ra I/O bằng chương trình (Programmed IO) I/O điều khiển bằng gián đoạn (Interrupt Driven IO) Truy cập bộ nhớ trực tiếp (DMA) + 18 a. I/O bằng chương trình Nguyên tắc chung: CPU điều khiển trực tiếp vào-ra bằng chương trình cần phải lập trình vào-ra. Vào-ra do ý muốn của người lập trình „ Dữ liệu được trao đổi giữa CPU và mô đun I/O CPU thi hành một chương trình cho phép nó trực tiếp điều hành các hoạt động I/O Khi CPU ra lệnh, nó phải đợi cho đến khi hoạt động I/O hoàn tất CPU chạy nhanh hơn mô-đun I/O sẽ gây lãng phí thời gian xử lý + 19 Mệnh lệnh I/O (Command) Để thực hiện 1 lệnh liên quan đến vào/ra, CPU đưa ra địa chỉ: xác định module I/O và thiết bị CPU đưa ra mệnh lệnh: 4 loại mệnh lệnh I/O 1) Control - Dùng để kích hoạt một thiết bị ngoại vi và chỉ định nó phải làm gì. (VD: quay đĩa) 2) Test - kiểm tra các điều kiện trạng thái liên quan đến mô-đun I/O và các thiết bị ngoại vi (VD: nguồn? Lỗi?) 3) Read - Cho phép mô-đun I/O lấy dữ liệu từ thiết bị ngoại vi và đặt nó vào bộ đệm bên trong 4) Write - Cho phép mô-đun I/O lấy dữ liệu từ bus dữ liệu rồi chuyển dữ liệu đó đến thiết bị ngoại vi + 20 Hoạt động I/O bằng chương trình CPU yêu cầu hoạt động vào/ra: ra mệnh lệnh cho module I/O mong muốn Môđun I/O thực hiện yêu cầu Môđun I/O đặt bit trạng thái Môđun I/O không thông báo trực tiếp cho CPU / không gián đoạn CPU CPU kiểm tra định kỳ bit trạng thái Nếu chưa sẵn sàng thì CPU có thể đợi hoặc quay lại sau Nếu sẵn sàng thì chuyển sang trao đổi dữ liệu với mô-đun vào-ra 21 Đọc vào một khối dữ liệu + 23 b. I/O điều khiển bằng gián đoạn Với I/O chương trình, CPU phải đợi một thời gian dài để mô đun I/O sẵn sàng cho việc nhận hoặc truyền dữ liệu Giải pháp: I/O điều khiển bằng gián đoạn CPU ra lệnh I/O cho một mô-đun, sau đó thực hiện các công việc hữu ích khác Mô-đun I/O sẽ gián đoạn bộ xử lý để yêu cầu dịch vụ khi nó đã sẵn sàng trao đổi dữ liệu với bộ vi xử lý Bộ xử lý thực hiện việc truyền dữ liệu và tiếp tục quá trình xử lý trước đó 24 Chuyển điều khiển đến chương trình con gián đoạn Chương trình con gián đoạn phục vụ vào-ra Gián đoạn ở đây Hoạt động vào dữ liệu: 25 Nhìn từ môđun I/O Nhìn từ CPU • Mô-đun I/O nhận mệnh • Phát mệnh lệnh READ lệnh READ từ CPU • Làm việc khác • „Mô-đun I/O nhận dữ liệu • Cuối mỗi chu kỳ lệnh, kiểm từ thiết bị ngoại vi, trong tra tín hiệu gián đoạn khi đó CPU làm việc khác • Nếu bị gián đoạn : • Khi đã có dữ liệu mô- • Lưu ngữ cảnh (nội dung đun I/O phát tín hiệu gián các thanh ghi) đoạn CPU • Thực hiện chương trình • CPU yêu cầu dữ liệu con gián đoạn • „ Mô-đun I/O chuyển dữ • Khôi phục ngữ cảnh của liệu đến CPU chương trình đang thực hiện Thay đổi trong bộ nhớ và thanh ghi khi có một gián đoạn 27 Vấn đề nảy sinh khi thiết kế Hai vấn đề thiết kế phát sinh khi gián đoạn I/O: Do có nhiều mô-đun I/O, làm thế nào để xác định được mô-đun I/O nào Nếu cùng lúc xảy ra nhiều phát tín hiệu ngắt ? gián đoạn, bộ vi xử lý lựa chọn 1 gián đoạn để xử lý như thế nào ? + 28 Nhận diện thiết bị Bốn loại kỹ thuật chung được sử dụng phổ biến: Dùng nhiều đường gián đoạn Thăm dò bằng phần mềm Chuỗi Daisy (thăm dò bằng phần cứng) Phân xử bus + 29 Nhiều đường gián đoạn Nhiều đường gián đoạn giữa bộ xử lý và môđun I/O Cách tiếp cận đơn giản nhất Hạn chế số lượng mô-đun I/O Các đường gián đoạn được qui định mức ưu tiên + 30 Thăm dò bằng phần mềm Khi bộ xử lý phát hiện ra một gián đoạn, nó rẽ nhánh tới một trình dịch vụ ngắt (phần mềm) chuyên thăm dò từng module I/O để xác định mô-đun nào gây ra gián đoạn Tốn thời gian Thứ tự thăm dò mô-đun phụ thuộc thứ tự ưu tiên + Thăm dò bằng phần cứng (chuỗi Daisy) 31 Dòng thông báo gián đoạn (INTA) được nối chuỗi qua các mô đun CPU phát tín hiệu INTA đến mô-đun vào-ra đầu tiên Nếu mô-đun vào-ra đó không gây ra gián đoạn thì nó gửi tín hiệu đến mô-đun tiếp cho đến khi xác định được mô-đun gây gián đoạn Thứ tự các mô-đun vào-ra kết nối trong chuỗi xác định thứ tự ưu tiên + 32 Phân xử bus (vector) Vector - địa chỉ của mô-đun I/O hoặc mã nhận dạng khác của mô-đun I/O Gián đoạn vector - bộ xử lý sử dụng vector như một con trỏ tới trinh phục vụ gián đoạn thích hợp, tránh phải thực hiện trình phục vụ gián đoạn chung Mô-đun I/O phải kiểm soát được của bus trước khi nó bật dòng yêu cầu gián đoạn Khi bộ xử lý phát hiện ra gián đoạn, nó phản ứng trên dòng thông báo gián đoạn Mô đun yêu cầu sẽ đặt các vector của nó trên các đường dữ liệu 33 Bộ điều khiển gián đoạn lập trình được PIC –Programmable Interrupt Controller „Có nhiều đường vào yêu cầu gián đoạn có qui định mức ưu tiên PIC chọn một yêu cầu gián đoạn không bị cấm có mức ưu tiên cao nhất gửi tới CPU 34 Ví dụ - Bộ điều khiển gián đoạn Intel 82C59A 80x86 có một đường gián đoạn hệ thống 8086 sử dụng bộ điều khiển gián đoạn 8259A 8259A có 8 đường gián đoạn +Bộ điều khiển gián đoạn Intel 82C59A Chuỗi sự kiện: • 8259A nhận gián đoạn • 8259A xác định ưu tiên • 8259A báo hiệu 8086 (nâng INTR) • CPU phản hồi • 8259A đặt véc tơ trên bus dữ liệu • CPU xử lý gián đoạn + Đặc điểm của I/O điều khiển bằng 36 gián đoạn . Có sự kết hợp giữa phần cứng và phần mềm . Phần cứng: gây ngắt CPU . Phần mềm: trao đổi dữ liệu . CPU trực tiếp điều khiển vào-ra . CPU không phải đợi mô-đun vào-ra hiệu quả sử dụng CPU tốt hơn 37 c. Truy cập bộ nhớ trực tiếp (DMA) Nhược điểm của I/O chương trình và điều khiển gián đoạn 1) Tốc độ truyền I/O bị giới hạn bởi tốc độ kiểm tra và phục vụ thiết bị của bộ xử lý 2) Bộ xử lý gắn với việc quản lý truyền I/O; Một số lệnh phải được thực hiện cho mỗi lần truyền I/O Khi cần di chuyển khối lượng dữ liệu lớn, sẽ hiệu quả hơn nếu sử dụng truy cập bộ nhớ trực tiếp (DMA) DMA: Mô đun I/O và bộ nhớ chính trực tiếp trao đổi dữ liệu mà không có sự tham gia của CPU Chức năng DMA: Mô đun bổ sung trên bus Bộ điều khiển DMA chiếm quyền điều khiển I/O của CPU + Sơ đồ cấu trúc mô-đun DMA • Thanh ghi dữ liệu: chứa dữ liệu trao đổi • Thanh ghi địa chỉ: chứa địa chỉ ngăn nhớ dữ liệu • Bộ đếm dữ liệu: chứa số từ dữ liệu cần trao đổi • Logic điều khiển: điều khiển hoạt động 39 + Hoạt động DMA CPU “nói” cho bộ điều khiển DMA: Đọc/ghi dữ liệu Địa chỉ thiết bị I/O Địa chỉ bắt đầu của khối bộ nhớ chứa dữ liệu Số lượng dữ liệu cần truyền CPU tiếp tục thực hiện công việc khác Bộ điều khiển DMA truyền Bộ điều khiển DMA gửi gián đoạn tới CPU khi hoàn thành để báo kết thúc DMA + 40 Các kiểu thực hiện DMA DMA truyền theo khối (Block-transfer DMA): Bộ điều khiển DMA sử dụng bus để truyền xong cả khối dữ liệu „ DMA chiếm chu kỳ (Cycle Stealing DMA): Bộ điều khiển DMA cưỡng bức CPU treo tạm thời từng chu kỳ bus, DMAC chiếm bus thực hiện truyền một từ dữ liệu. DMA trong suốt (Transparent DMA): Bộ điều khiển DMA nhận biết những chu kỳ nào CPU không sử dụng bus thìchiếm bus để trao đổi một từ dữ liệu. DMA chiếm chu kỳ truyền 41 Bộ điều khiển DMA chiếm bus trong một chu kỳ Truyền một từ dữ liệu Không phải là gián đoạn (CPU không chuyển ngữ cảnh) CPU bị treo ngay trước khi nó truy cập bus (tức là trước khi truy xuất toán hạng, dữ liệu hoặc ghi dữ liệu) Làm chậm CPU nhưng không nhiều như CPU tự thực hiện truyền + 42 Cấu hình DMA (1) Bus đơn, bộ điều khiển DMA tách rời Mỗi lần truyền sử dụng bus 2 lần I/O - DMA rồi sau đó DMA - bộ nhớ CPU bị treo hai lần + 43 Cấu hình DMA (2) Bus đơn, bộ điều khiển DMA tích hợp Bộ điều khiển có thể hỗ trợ > 1 thiết bị Mỗi lần truyền sử dụng bus 1 lần DMA - bộ nhớ CPU bị treo một lần + 44 Cấu hình DMA (3) Bus I/O riêng Bus hỗ trợ tất cả các thiết bị có DMA Mỗi lần truyền sử dụng bus 1 lần DMA - bộ nhớ CPU bị treo một lần 45 Bộ điều khiển DMA Intel 8237A Giao tiếp với họ 80x86 và DRAM Khi module DMA cần bus nó sẽ gửi tín hiệu HOLD tới bộ vi xử lý CPU phản hồi HLDA - Mô-đun DMA có thể sử dụng bus Ví dụ: truyền dữ liệu từ bộ nhớ tới đĩa 1. Thiết bị yêu cầu DMA bằng cách nâng DREQ (yêu cầu DMA) 2. DMA đặt HRQ (yêu cầu giữ) lên cao 3. CPU kết thúc chu kỳ bus hiện tại và đặt HDLA lên cao. HOLD duy trì trong suốt thời gian DMA 4. DMA kích hoạt DACK (DMA ack), bảo thiết bị bắt đầu truyền 5. DMA bắt đầu truyền bằng cách đặt byte đầu tiên của địa chỉ lên bus địa chỉ và kích hoạt MEMR; sau đó kích hoạt IOW để ghi vào ngoại vi. DMA giảm bộ đếm và tăng con trỏ địa chỉ. Lặp lại cho đến khi đếm về 0 6. DMA hủy HRQ, trả bus trở lại CPU 8237 DMA 46 Cách sử dụng Bus Hệ thống + 47 Sự phát triển của chức năng vào/ra CPU trực tiếp điều khiển một thiết bị ngoại vi. Thêm 1 bộ điều khiển hoặc mô-đun I/O. CPU sử dụng I/O chương trình, không có gián đoạn. Tương tự bước 2, nhưng có sử dụng gián đoạn. CPU không phải tốn thời gian đợi hoạt động I/O thực hiện, do đó tăng hiệu quả. Mô đun I/O truy cập trực tiếp bộ nhớ qua DMA, di chuyển 1 khối dữ liệu đến/từ bộ nhớ mà không liên quan đến CPU, ngoại trừ khi bắt đầu và kết thúc truyền Mô đun I/O nâng cấp lên thành một bộ xử lý theo quyền riêng của nó, với một tập hợp chỉ lệnh dành riêng cho I/O Mô đun I/O có bộ nhớ cục bộ riêng (giống như một máy tính có quyền riêng) có thể kiểm soát tập hợp lớn các thiết bị I/O, giảm tối thiểu sự tham gia của CPU + 48 4. Kênh I/O và Bộ xử lý I/O mở rộng khái niệm DMA có khả năng thực thi các lệnh vào ra, do đó kênh I/O kiểm soát hoàn toàn các hoạt động vào ra không cần sự kiểm soát của CPU Việc điều khiển vào-ra được thực hiện bởi một bộ xử lý vào-ra chuyên dụng trong kênh I/O Chương trình của bộ xử lý vào-ra lưu trong bộ nhớ chính CPU ra lệnh cho kênh I/O thực hiện chương trình trong bộ nhớ Kênh I/O thực thi các lệnh và điều khiển việc truyền dữ liệu 2 loại: Kênh lựa chọn (selector channel) Kênh ghép (multiplexor channel) + Kiến trúc kênh I/O 7. Giao diện ngoại vi a. Các kiểu Giao diện + . Vào – ra song song . Vào – ra nối tiếp b. Các cấu hình kết nối . Điểm – điểm . Điểm – đa điểm 50 I/O song song „-- Tốc độ nhanh -- Nhiều đường kết nối mô-đun I/O - thiết bị ngoại vi -- Truyền nhiều bit đồng thời, giống như tất cả các bit của một từ được truyền đồng thời trên bus dữ liệu. -- Sử dụng cho các thiết bị ngoại vi tốc độ cao như băng và đĩa I/O nối tiếp -- Tốc độ chậm hơn -- Dùng một đường để truyền dữ liệu -- Truyền đi từng bit -- Sử dụng cho máy in và thiết bị đầu cuối. + Tổng kết 53 Input/Output Chương 7 Thiết bị ngoại vi Truy cập bộ nhớ trực tiếp Bàn phím / màn hình Nhược điểm của I/O chương Ổ đĩa trình và I/O điều khiển gián Mô đun I/O đoạn Chức năng mô-đun Chức năng DMA Bộ điều khiển Intel 8237A DMA Cấu trúc module I/O Các kênh I/O và bộ xử lý I/O bằng chương trình Sự phát triển của chức năng I/O Tổng quan về I/O chương trình Đặc điểm của các kênh I/O Lệnh I/O Giao diện ngoài I/O điều khiển bằng gián đoạn Các loại giao diện Xử lý gián đoạn Cấu hình điểm-điểm và đa điểm Các vấn đề thiết kế Bộ điều khiển gián đoạn Intel 82C59A + 54 Câu hỏi chương 7 1. Kể tên ba nhóm thiết bị ngoại vi. 2. IRA là gì? 3. Các chức năng chính của mô-đun I / O là gì? 4. Trình bày ba kỹ thuật để thực hiện I / O. 5. Sự khác nhau giữa I / O ánh xạ bộ nhớ và I / O bộ nhớ tách biệt là gì? 6. Khi một gián đoạn thiết bị xảy ra, bộ xử lý xác định thiết bị đã ban hành gián đoạn như thế nào ? 7. Khi một mô-đun DMA chiếm điều khiển bus, và trong khi nó vẫn kiểm soát được bus, bộ xử lý làm gì?

File đính kèm:

bai_giang_kien_truc_may_tinh_chuong_7_dau_vaodau_ra_nguyen_h.pdf

bai_giang_kien_truc_may_tinh_chuong_7_dau_vaodau_ra_nguyen_h.pdf