Bài giảng Kiến trúc máy tính - Chương 3: Chức năng và kết nối máy tính - Nguyễn Hằng Phương

NỘI DUNG

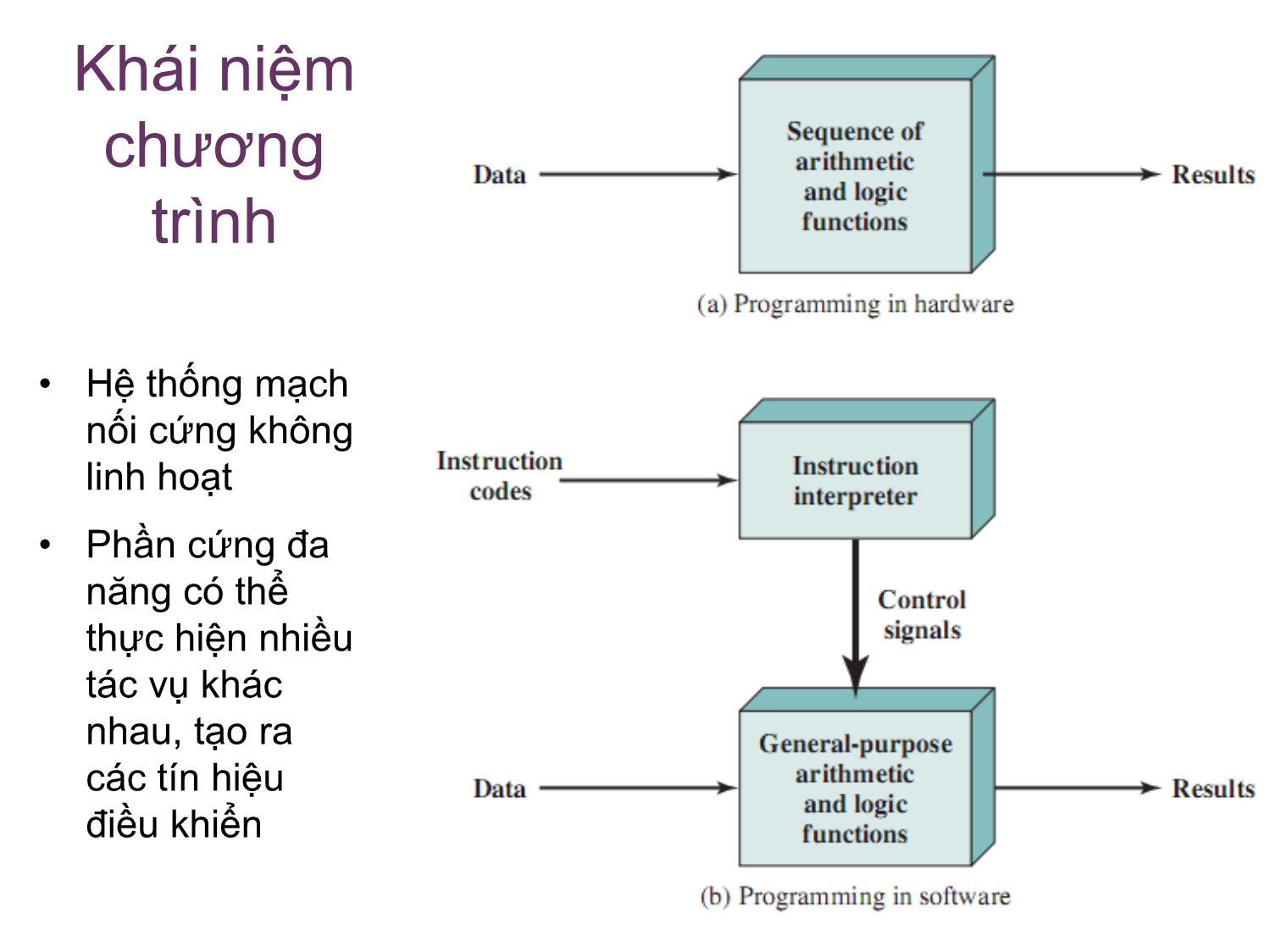

1. Các thành phần máy tính

2. Chức năng máy tính

Chu kỳ Truy xuất và Thực thi

Gián đoạn

Chức năng I/O

3. Cấu trúc kết nối

4. Kết nối bus

Cấu trúc Bus

Đa Bus

Các yếu tố thiết kế bus

5. Kết nối điểm-điểm QPI

6. PCI Express

Trang 1

Trang 2

Trang 3

Trang 4

Trang 5

Trang 6

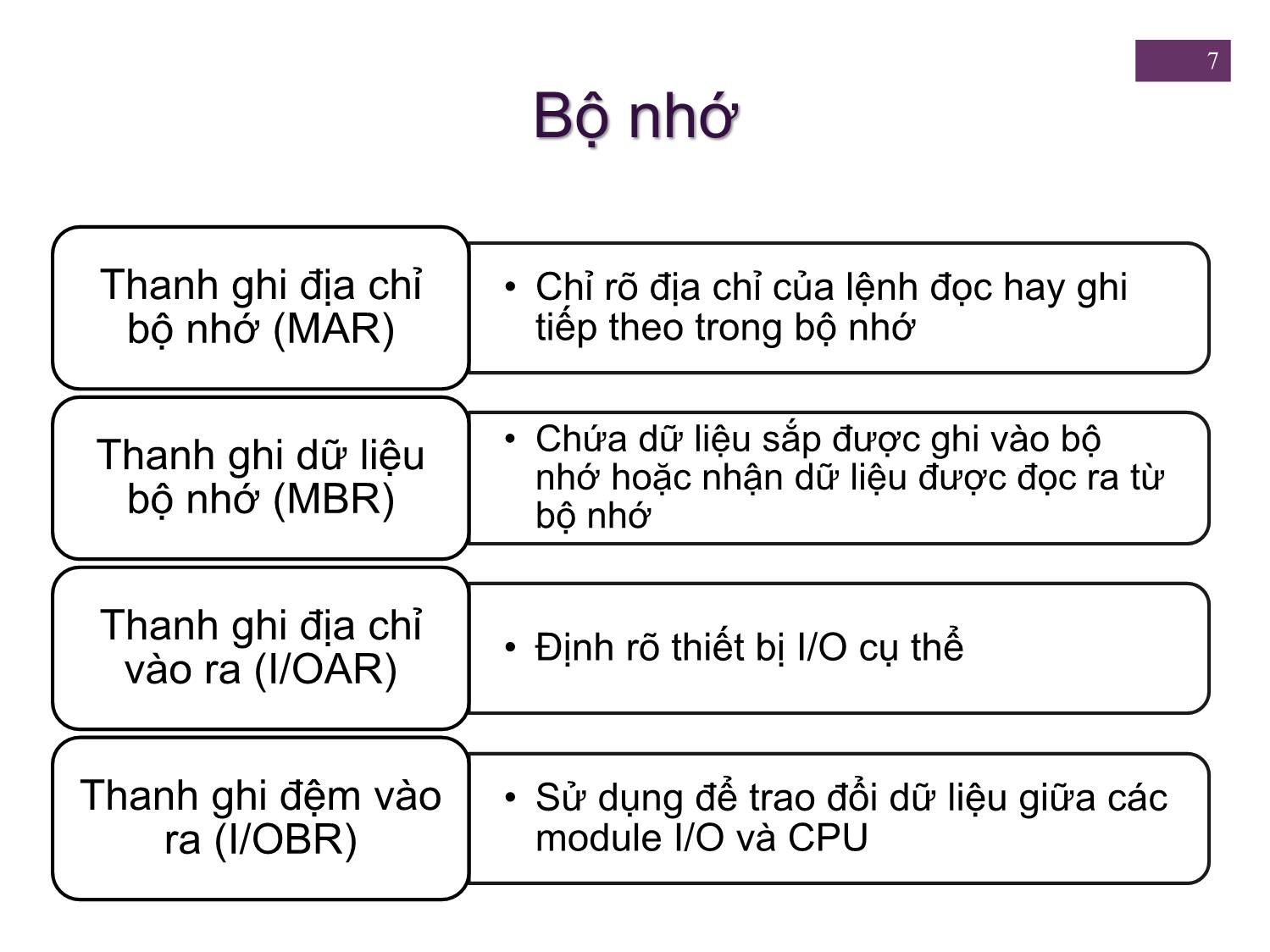

Trang 7

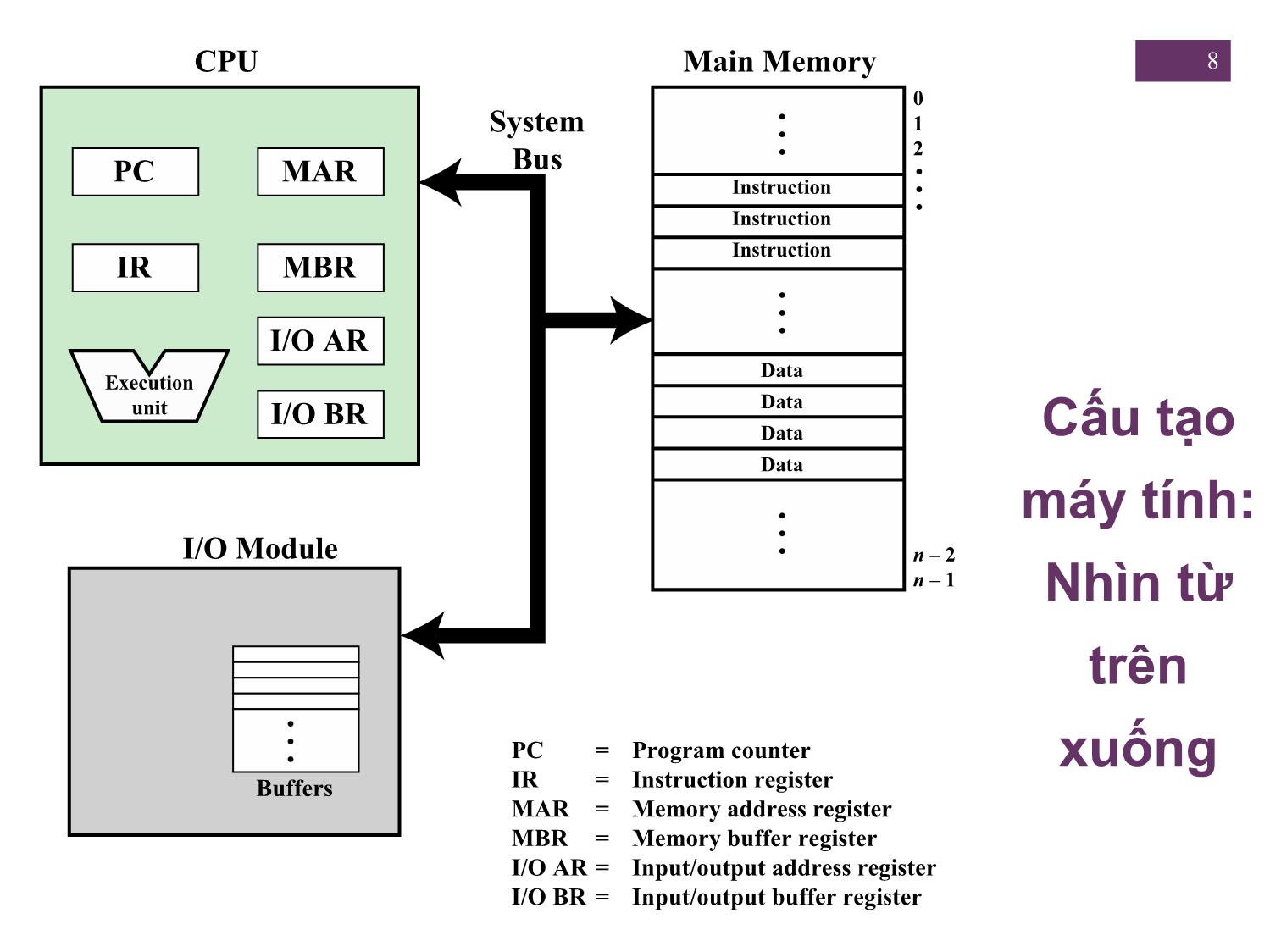

Trang 8

Trang 9

Trang 10

Tải về để xem bản đầy đủ

Bạn đang xem 10 trang mẫu của tài liệu "Bài giảng Kiến trúc máy tính - Chương 3: Chức năng và kết nối máy tính - Nguyễn Hằng Phương", để tải tài liệu gốc về máy hãy click vào nút Download ở trên

Tóm tắt nội dung tài liệu: Bài giảng Kiến trúc máy tính - Chương 3: Chức năng và kết nối máy tính - Nguyễn Hằng Phương

lý và được kiểm tra sau khi gián đoạn đầu tiên đã được xử lý gián đoạn được xử lý theo trình tự xuất hiện Độ ưu tiên Các gián đoạn ưu tiên thấp có thể bị ngắt bởi các gián đoạn ưu tiên cao hơn Khi gián đoạn ưu tiên cao hơn đã được xử lý xong, bộ xử lý quay trở lại gián đoạn trước + Trình tự thời gian của nhiều gián đoạn 26 Ví dụ Printer Communication User program interrupt service routine interrupt service routine t = 0 15 0 = 1 t t = t = 25 t Disk t = = 25 40 interrupt service routine t = 35 Figure 3.14 Example Time Sequence of Multiple Interrupts 27 Chức năng I/O Module I/O có thể trao đổi dữ liệu trực tiếp với bộ xử lý Bộ xử lý có thể đọc dữ liệu từ/ghi dữ liệu lên module I/O Bộ xử lý xác định thiết bị nào được điều khiển bởi module I/O nào I/O đưa ra lệnh chứ không phải là bộ nhớ đưa ra lệnh Trong một số trường hợp, cần cho phép I/O trao đổi trực tiếp với bộ nhớ Bộ xử lý cấp cho module I/O quyền đọc/ghi vào bộ nhớ do đó việc truyền tin giữa module I/O và bộ nhớ có thể diễn ra trực tiếp mà không cần thông qua bộ xử lý Module I/O đưa ra yêu cầu đọc/ghi tới bộ nhớ và giải phóng nhiệm vụ chuyển dữ liệu cho bộ xử lý Truy cập bộ nhớ trực tiếp (Direct Memory Access - DMA) Read Memory 28 + Write N Words Address 0 Data Các module máy tính Data N – 1 Read I/O Module Internal Write Data External Address M Ports Data Internal Data Interrupt Signals External 3. Data Cấu trúc kết Instructions Address Control nối Data CPU Signals Interrupt Data Signals Figure 3.15 Computer Modules 29 Cấu trúc kết nối hỗ trợ các hình thức truyền sau: Bộ nhớ tới bộ xử • Bộ xử lý đọc 1 lệnh hoặc 1 đơn vị dữ lý liệu từ bộ nhớ Bộ xử lý tới bộ • Bộ xử lý ghi 1 đơn vị dữ liệu vào bộ nhớ nhớ • Bộ xử lý đọc dữ liệu từ thiết bị I/O I/O tới bộ xử lý thông qua I/O module Bộ xử lý tới I/O • Bộ xử lý gửi dữ liệu tới thiết bị I/O • Module I/O có thể trao đổi dữ liệu trực I/O tới/từ bộ nhớ tiếp với bộ nhớ mà không cần đi qua bộ xử lý nhờ DMA 30 4. BUS kết nối (1) . Bus là phương tiện truyền dẫn chung, là đường thông tin kết nối chung giữa 2 hay nhiều thiết bị . Tín hiệu truyền bởi 1 thiết bị có thể được nhận bởi tất cả các thiết bị khác cùng kết nối với bus đó . Nếu 2 thiết bị cùng truyền 1 lúc, tín hiệu của chúng sẽ bị chồng nhau và bị méo . 1 bus thường gồm nhiều đường thông tin . Mỗi đường có khả năng truyền tín hiệu dưới dạng bit 1 và bit 0 31 4. BUS kết nối (2) . Hệ thống máy tính có một số loại bus khác nhau cung cấp đường kết nối giữa các thành phần thuộc các cấp khác nhau của hệ thống máy tính . Bus hệ thống: Đường bus kết nối các thành phần chính của máy tính (bộ xử lý, bộ nhớ, I/O) . Cấu trúc kết nối máy tính phổ biến nhất dựa trên việc sử dụng một hoặc nhiều bus hệ thống . Bus dữ liệu, bus địa chỉ, bus điều khiển 32 Bus dữ liệu Bus dữ liệu là đường kết nối dùng để truyền dữ liệu giữa các module hệ thống Bao gồm 32, 64, 128 đường hay nhiều hơn Số lượng đường nối được xem là độ rộng của bus dữ liệu Số lượng đường nối quyết định bao nhiêu bit có thể truyền đi cùng một lúc Độ rộng bus dữ liệu là yếu tố chính quyết định hiệu suất toàn hệ thống 33 Bus địa chỉ Được sử dụng để xác định địa chỉ nguồn/đích của dữ liệu trên bus dữ liệu. Nếu bộ xử lý muốn đọc 1 word từ bộ nhớ, nó sẽ đặt địa chỉ của word đó lên đường bus địa chỉ. Độ rộng bus xác định dung lượng nhớ tối đa của hệ thống Cũng được sử dụng để xác định cổng vào/ra. Các bit bậc cao được sử dụng để lựa chọn module cụ thể trên bus còn bit bậc thấp dùng để chọn vị trí bộ nhớ hoặc cổng vào/ra trong module. 34 Bus điều khiển Được sử dụng để điều khiển việc truy nhập và sử dụng bus dữ liệu và bus địa chỉ. Bởi vì bus dữ liệu và bus địa chỉ được chia sẻ cho tất cả các thành phần nên cần phải có một công cụ kiểm soát việc sử dụng chúng. Các tín hiệu điều khiển truyền cả thông tin lệnh và định thời giữa các mô đun hệ thống. Tín hiệu định thời xác định tính hợp lệ của dữ liệu và thông tin địa chỉ. Tín hiệu lệnh chỉ ra hành động (operation) cần được thực hiện. 35 Sơ đồ kết nối BUS CPU Memory Memory I/O I/O Control lines Address lines Bus Data lines Bus? • Các đườngFigur songe 3.16 songBus Inter trênconnection bo mạch Scheme • Dây cáp • Dải giắc cắm kết nối trên bo mạch chủ (ví dụ. PCI) 36 Vấn đề của đơn BUS . Khi số lượng lớn thiết bị được kết nối với bus, hiệu suất sẽ bị ảnh hưởng. . Càng nhiều thiết bị gắn vào bus, bus càng dài trễ truyền càng lớn. . Bus có thể trở thành nút cổ chai nếu lượng dữ liệu truyền tổng cộng gần bằng dung lượng bus . Các hệ thống sử dụng đa bus để khắc phục các vấn đề của đơn bus Cấu hình đa bus 37 Kiến trúc truyền thống (Có cache) Local Bus Processor Cache Local I/O controller Main Memory System Bus Network Expansion bus interface Serial SCSI Modem Expansion Bus (a) Traditional Bus Architecture Main Memory Local Bus Cache Processor /Bridge System Bus SCSI FireWire Graphic Video LAN High-Speed Bus FAX Expansion bus interface Serial Modem Expansion Bus (b) High-Performance Architecture Figure 3.17 Example Bus Configurations Local Bus Processor Cache Local I/O controller Main Memory System Bus Network Expansion bus interface Serial SCSI Modem 38 Cấu hìnhExpansion đa Bus bus Kiến trúc hiệu suất cao (a) Traditional Bus Architecture Main Memory Local Bus Cache Processor /Bridge System Bus SCSI FireWire Graphic Video LAN High-Speed Bus FAX Expansion bus interface Serial Modem Expansion Bus (b) High-Performance Architecture Figure 3.17 Example Bus Configurations + 39 Các yếu tố trong thiết kế Bus Type Bus Width Dedicated Address Multiplexed Data Method of Arbitration Data Transfer Type Centralized Read Distributed Write Timing Read-modify-write Synchronous Read-after-write Asynchronous Block 40 T1 T2 T3 Clock Phân chia Status Status signals lines thời gian Address Stable address lines hoạt động Address enable trên BUS Data Valid data in Read lines đồng bộ cycle Read Data Valid data out Write lines cycle Write Figure 3.18 Timing of Synchronous Bus Operations 41 Phân chia thời gian hoạt động trên BUS đồng bộ Status Status signals lines Address lines Stable address Read Data lines Valid data Acknowledge (a) System bus read cycle Status Status signals lines Address lines Stable address Data lines Valid data Write Acknowledge (b) System bus write cycle Figure 3.19 Timing of Asynchronous Bus Operations Status Status signals lines Address lines Stable address Read Data lines Valid data Acknowledge 42 Phân chia thời gian hoạt động trên BUS(a) System đồng bus rbộead cycle Status Status signals lines Address lines Stable address Data lines Valid data Write Acknowledge (b) System bus write cycle Figure 3.19 Timing of Asynchronous Bus Operations 43 5. Kết nối điểm - điểm Lý do chính dẫn tới sự thay đổi từ BUS sang kết nối điểm-điểm là những hạn chế về điện gặp phải khi tăng tần số của các bus đồng bộ Tốc độ dữ liệu càng cao thì càng khó thực hiện chức năng đồng bộ và phân xử một cách kịp thời Chia sẻ bus trên cùng 1 chip làm tăng thêm khó khăn trong việc tăng tốc độ dữ liệu bus và làm giảm độ trễ trến bus để bắt kịp với vi xử lý. Có độ trễ thấp, tốc độ dữ liệu cao, và khả năng mở rộng tốt hơn. 44 QPI Kết nối đường dẫn nhanh (Quick Path Interconnect) . Được giới thiệu vào năm 2008 . Nhiều kết nối trực tiếp . Các kết nối từng cặp trực tiếp tới các thành phần khác giúp loại bỏ việc phân xử thường thấy trong các hệ thống truyền dẫn chia sẻ. . Kiến trúc giao thức phân lớp . Các kết nối của bộ xử lý sử dụng kiến trúc giao thức phân lớp chứ không chỉ đơn giản sử dụng tín hiệu điều khiển thường thấy trong sắp xếp các bus chia sẻ. . Truyền dữ liệu đóng gói . Dữ liệu được gửi thành 1 chuỗi các gói chứa tiêu đề điều khiển (header) và mã kiểm soát lỗi. e e 45 c c i i v v e e I/O Hub d d O O / / I I Cấu hình M M Core Core A A chip đa R R A B D D nhân sử dụng M M Core Core A A R R C D QPI D D e e c c i i v v e e I/O Hub d d O O / / I I QPI PCI Express Memory bus Figure 3.20 Multicore Configuration Using QPI 46 Các lớp QPI Packets Protocol Protocol Routing Routing Flits Link Link Physical Phits Physical Figure 3.21 QPI Layers 47 Lớp liên kết QPI Chức năng điều khiển luồng Thực hiện hai chức Cần thiết để đảm bảo rằng 1 năng chính: điều khiển thực thể QPI gửi không áp luồng và điều khiển lỗi. đảo 1 thực thể QPI nhận bằng cách gửi dữ liệu nhanh Vận hành trên cấp flit hơn khả năng xử lý dữ liệu Mỗi flit gồm tải tin 72- và xoá bộ đệm để nhiều dữ bit và một mã kiểm liệu mới đến của phía nhận soát lỗi 8-bit được gọi là cyclic redundancy Chức năng điều khiển lỗi check (CRC) Phát hiện và khắc phục lỗi bit, do đó tránh cho các lớp cao hơn gặp lỗi bit + 48 Lớp Giao thức và Định tuyến QPI Lớp Định tuyến Lớp Giao thức Gói (packet) là đơn vị truyền Được sử dụng để xác định đường đi mà một gói sẽ đi Một chức năng quan trọng qua các kết nối hệ thống được thực hiện ở lớp này là có sẵn giao thức liên kết bộ nhớ cache - đảm bảo rằng các giá trị bộ Xác định bởi phần sụn và nhớ chính được giữ trong nhiều mô tả các đường dẫn mà cache là phù hợp một gói tin có thể đi theo Một tải gói dữ liệu điển hình là một khối dữ liệu được gửi đến hoặc từ một bộ nhớ cache + 49 Kết nối thiết bị ngoại vi Peripheral Component Interconnect (PCI) Một bus băng thông cao, độc lập với bộ xử lý, có thể hoạt động như một bus ngoại vi Cung cấp hiệu suất hệ thống tốt hơn cho các hệ thống con I / O tốc độ cao Nhóm quan tâm đặc biệt PCI (Special Interest Group - SIG) Được tạo ra để phát triển và duy trì tính tương thích của các đặc tính PCI PCI Express (PCIe) Cơ chế kết nối điểm-điểm nhằm thay thế cơ chế dựa trên bus như PCI Yêu cầu chính là dung lượng cao để hỗ trợ nhu cầu của thiết bị I / O tốc độ dữ liệu cao hơn, như Gigabit Ethernet Một yêu cầu khác là phải hỗ trợ các luồng dữ liệu phụ thuộc thời gian Core Core Cấu hình Gigabit PCIe Memory Ethernet PCIe Chipset PCIe–PCI PCIe Memory Bridge PCIe PCIe PCIe Switch PCIe PCIe Legacy PCIe PCIe PCIe endpoint endpoint endpoint endpoint Figure 3.24 Typical Configuration Using PCIe + 51 Các lớp giao thức PCIe Transaction layer packets (TLP) Transaction Transaction Data link layer packets (DLLP) Data Link Data Link Physical Physical Figure 3.25 PCIe Protocol Layers + 52 Phân phối đa đường PCIe B4 B0 128b/ PCIe 130b lane 0 byte stream B5 B1 128b/ PCIe 130b lane 1 B7 B6 B5 B4 B3 B2 B1 B0 B6 B2 128b/ PCIe 130b lane 2 B7 B3 128b/ PCIe 130b lane 3 Figure 3.26 PCIe Multilane Distribution Nhận các yêu cầu đọc và ghi từ + phần mềm phía trên TL và tạo ra các gói tin yêu cầu truyền tới đích qua Lớp giao dịch lớp liên kết (link layer) PCIe Các giao dịch sử dụng kỹ thuật giao dịch phân chia (split transaction) Transaction Layer Một thiết bị PCIe nguồn gửi 1 gói tin (TL) yêu cầu đi, sau đó đợi 1 phản hồi gọi là gói hoàn thành Bản tin TL và một số giao dịch ghi là giao dịch gửi (posted transaction) không cần phản hồi Định dạng gói TL hỗ trợ địa chỉ bộ nhớ 32-bit và địa chỉ bộ nhớ 64-bit mở rộng + 54 TL hỗ trợ bốn không gian địa chỉ: Bộ nhớ I / O Không gian bộ nhớ bao Không gian địa chỉ này gồm bộ nhớ chính của hệ được sử dụng cho thiết bị thống và thiết bị I / O PCIe PCI kế thừa, với dải địa chỉ Các khoảng địa chỉ bộ dành riêng dùng để xác nhớ nhất định được ánh định các thiết bị I / O kế xạ vào các thiết bị I / O thừa Message Cấu hình Không gian địa chỉ này Không gian địa chỉ này dành cho các tín hiệu điều cho phép TL đọc / ghi các khiển liên quan đến gián thanh ghi cấu hình kết hợp đoạn, xử lý lỗi, và quản lý với các thiết bị I / O năng lượng 55 Các kiểu giao dịch TLP PCIe Address Space TLP Type Purpose Memory Read Request Transfer data to or from a location in the Memory Memory Read Lock Request system memory map. Memory Write Request I/O Read Request Transfer data to or from a location in the I/O I/O Write Request system memory map for legacy devices. Config Type 0 Read Request Config Type 0 Write Request Transfer data to or from a location in the Configuration Config Type 1 Read Request configuration space of a PCIe device. Config Type 1 Write Request Message Request Provides in-band messaging and event Message Message Request with Data reporting. Completion Memory, I/O, Completion with Data Returned for certain requests. Configuration Completion Locked Completion Locked with Data + 0 to 4096 Number of octets 12 or 0 or 16 (a) (a) 4 1 4 2 1 T ransaction Layer Sequence number STP STP F Header LCRC ECRC Data framing framing i g u r e 3 Packet . 2 8 P Created by Transaction Layer C I e Appended by Data Link Layer P r o t o Appended by Physical Layer c o l D 1 1 2 4 a (b) Data Link Layer t a U n DLLP i Start CRC End t F o r m Packet a t Created by DLL Đơn vị dữ liệu Đơn vịdữliệu Appended by PL Định dạng Giao thức Giao thức PCIe 56 + 57 Tổng kết Chức năng máy tính và kết nối Chương 3 Kết nối điểm-điểm Thành phần máy tính Lớp vật lý QPI Chức năng máy tính Lớp liên kết QPI Lệnh truy xuất và thi hành Lớp định tuyến QPI Gián đoạn Lớp giao thức QPI Chức năng I / O PCI Express Cấu trúc kết nối Kiến trúc vật lý và logic PCI Kết nối bus Lớp vật lý PCIe Cấu trúc bus Lớp giao dịch PCIe Nhiều phân cấp bus Lớp liên kết dữ liệu PCIe Các yếu tố thiết kế bus + 58 Câu hỏi chương 3 1. Chức năng chính của máy tính? 2. Xác định các trạng thái trong 1 vòng thực thi lệnh. 3. Trình bày hai cách xử lý khi có nhiều gián đoạn. 4. Cấu trúc kết nối bên trong máy tính (ví dụ: bus) hỗ trợ những kiểu truyền gì? 5. Lợi ích của việc sử dụng kiến trúc đa bus so với kiến trúc đơn bus? 6. Định nghĩa ngắn gọn các lớp giao thức QPI. 7. Định nghĩa ngắn gọn các lớp giao thức PCIe

File đính kèm:

bai_giang_kien_truc_may_tinh_chuong_3_chuc_nang_va_ket_noi_m.pdf

bai_giang_kien_truc_may_tinh_chuong_3_chuc_nang_va_ket_noi_m.pdf