Bài giảng Kiến trúc máy tính - Bài 5: Các chip bổ trợ - Phan Thanh Toàn

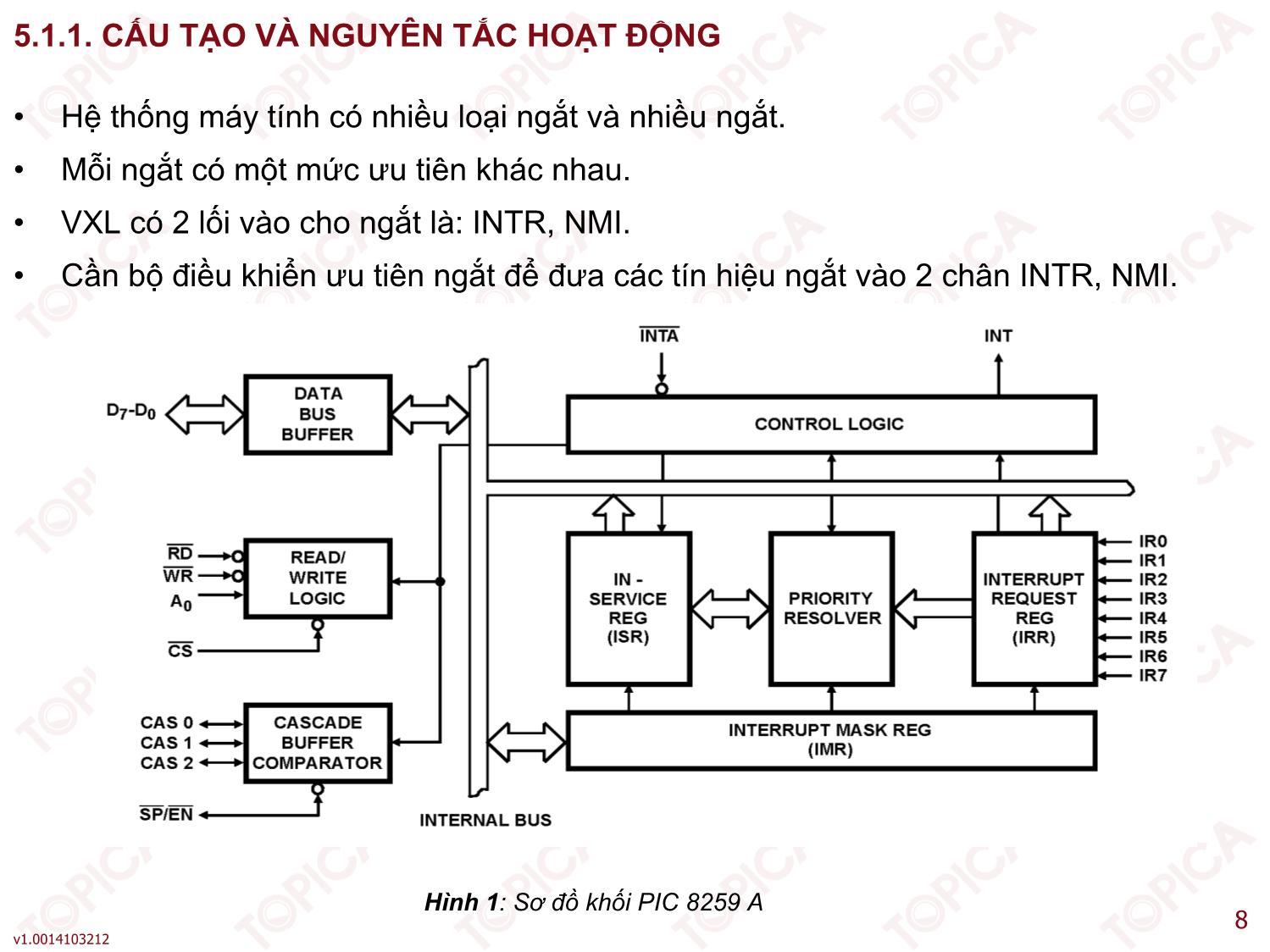

Hệ thống máy tính có nhiều loại ngắt và nhiều ngắt.

• Mỗi ngắt có một mức ưu tiên khác nhau.

• VXL có 2 lối vào cho ngắt là: INTR, NMI.

• Cần bộ điều khiển ưu tiên ngắt để đưa các tín hiệu ngắt vào 2 chân INTR, NMI

Trang 1

Trang 2

Trang 3

Trang 4

Trang 5

Trang 6

Trang 7

Trang 8

Trang 9

Trang 10

Tải về để xem bản đầy đủ

Bạn đang xem 10 trang mẫu của tài liệu "Bài giảng Kiến trúc máy tính - Bài 5: Các chip bổ trợ - Phan Thanh Toàn", để tải tài liệu gốc về máy hãy click vào nút Download ở trên

Tóm tắt nội dung tài liệu: Bài giảng Kiến trúc máy tính - Bài 5: Các chip bổ trợ - Phan Thanh Toàn

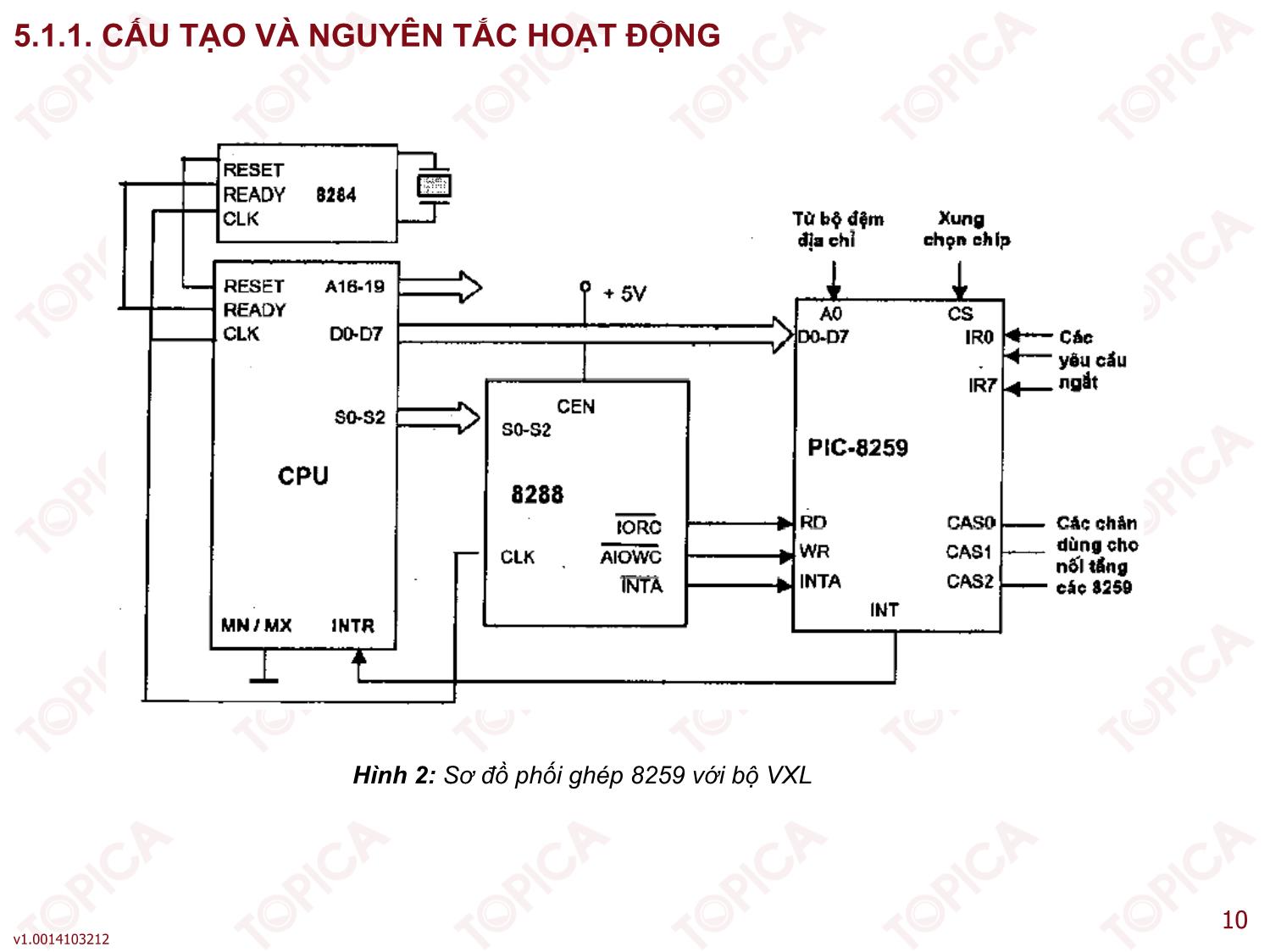

1 v1.0014103212 KIẾN TRÚC MÁY TÍNH Giảng viên: ThS. Phan Thanh Toàn 2 v1.0014103212 BÀI 5 CÁC CHIP BỔ TRỢ Giảng viên: ThS. Phan Thanh Toàn 3 v1.0014103212 • Liệt kê được các chip bổ trợ trong máy vi tính. • Liệt kê được các công dụng của các chip bổ trợ trong máy tính. • Mô tả được cấu tạo và nguyên tắc hoạt động của các chip bổ trợ như: 8259, 8255, MỤC TIÊU BÀI HỌC 4 v1.0014103212 Để hiểu rõ bài này, yêu cầu sinh viên cần có các kiến thức cơ bản liên quan đến các môn học sau: • Kỹ thuật số; • Kỹ thuật điện tử số. CÁC KIẾN THỨC CẦN CÓ 5 v1.0014103212 • Đọc tài liệu và tóm tắt những nội dung chính của từng bài. • Luôn liên hệ và lấy ví dụ thực tế khi học đến từng vấn đề̀ và khái niệm. • Sử dụng các ngôn ngữ lập trình cơ bản như Pascal, C, • Làm bài tập và luyện thi trắc nghiệm theo yêu cầu từng bài. HƯỚNG DẪN HỌC 6 v1.0014103212 5.1. Chip điều khiển ngắt 8259 5.2. Chip ghép nối ngoại vi khả trình PPI-8255A 5.3. Chip định thời PIT-8253 5.4. Chip điều khiển truy nhập bộ nhớ trực tiếp DMA-8237A CẤU TRÚC NỘI DUNG 7 v1.0014103212 5.1.1. Cấu tạo và nguyên tắc hoạt động 5.1.2. Lập trình cho PIC 8259A 5.1. CHIP ĐIỀU KHIỂN NGẮT 8259A 8 v1.0014103212 • Hệ thống máy tính có nhiều loại ngắt và nhiều ngắt. • Mỗi ngắt có một mức ưu tiên khác nhau. • VXL có 2 lối vào cho ngắt là: INTR, NMI. • Cần bộ điều khiển ưu tiên ngắt để đưa các tín hiệu ngắt vào 2 chân INTR, NMI. Hình 1: Sơ đồ khối PIC 8259 A 5.1.1. CẤU TẠO VÀ NGUYÊN TẮC HOẠT ĐỘNG 9 v1.0014103212 5.1.1. CẤU TẠO VÀ NGUYÊN TẮC HOẠT ĐỘNG • Các thanh ghi IRR, ISR, IMR: 8 bit. • Tín hiệu yêu cầu ngắt: IR0, IR1, , IR7. • Thanh ghi che ngắt (IMR – Interrupt Mask Register): Cấm/cho phép ngắt. • IRR: Thanh ghi yêu cầu ngắt. • IR: Thanh ghi ngắt được phục vụ. • PR: Mạch logic giải quyết ưu tiên ngắt. 10 v1.0014103212 5.1.1. CẤU TẠO VÀ NGUYÊN TẮC HOẠT ĐỘNG Hình 2: Sơ đồ phối ghép 8259 với bộ VXL 11 v1.0014103212 5.1.1. CẤU TẠO VÀ NGUYÊN TẮC HOẠT ĐỘNG (tiếp theo) 12 v1.0014103212 • 8259 là vi mạch khả trình. • Việc lập trình cho PIC 8259 gồm 2 công đoạn: Thiết lập chế độ làm việc của PIC 8259; Lập trình truyền tin qua 8259. • 8259 có 4 từ điều khiển khởi động: ICW1 – ICW4 và 3 từ điều khiển hoạt động OCW1 – OCW3. • Các thanh ghi của PIC 8259 được truy cập qua địa chỉ: 020h và 021h. 5.1.2. LẬP TRÌNH CHO PIC 8259A 13 v1.0014103212 5.1.2. LẬP TRÌNH CHO PIC 8259A Không • Khởi động PIC cùng PC theo lưu đồ sau: VXL: Viết từ điều khiển khởi động ICW1. VXL: Viết từ điều khiển khởi động ICW2. Nếu có ghép tầng VXL ghi tiếp ICW3. Nếu có đòi hỏi ICW4 thì sẽ viết tiếp từ điều khiển khởi động ICW4. Ghép PIC? Viết từ ICW1 Viết từ ICW1 Viết từ ICW3 Yêu cầu ICW4 Viết từ ICW4 Không Có Có 14 v1.0014103212 Có 4 từ điều khiển khởi tạo A0 Khởi tạo 0 0 ICW1 0 1 ICW2, ICW3, ICW4 1 X Không chọn 8259 CS 5.1.2. LẬP TRÌNH CHO PIC 8259A (tiếp theo) 15 v1.0014103212 5.1.2. LẬP TRÌNH CHO PIC 8259A (tiếp theo) Cấu trúc các từ điều khiển ICW1 – ICW4 16 v1.0014103212 • ICW2: Xác định số hiệu ngắt 5.1.2. LẬP TRÌNH CHO PIC 8259A (tiếp theo) 17 v1.0014103212 5.1.2. LẬP TRÌNH CHO PIC 8259A (tiếp theo) • ICW3: Làm việc ở chế độ chủ và khách 18 v1.0014103212 5.1.2. LẬP TRÌNH CHO PIC 8259A (tiếp theo) • ICW4 19 v1.0014103212 • Định dạng các thanh ghi điều khiển hoạt động OCW1-OCW3 OCW1: Thanh ghi thiết lập và đọc trạng thái yêu cầu ngắt 5.1.2. LẬP TRÌNH CHO PIC 8259A (tiếp theo) 20 v1.0014103212 5.1.2. LẬP TRÌNH CHO PIC 8259A (tiếp theo) OCW2: Xác định việc xử lí các yêu cầu ngắt của 8259 21 v1.0014103212 OCW3 Chọn các thanh ghi để đọc; Thăm dò trạng thái yêu cầu ngắt; Thao tác với thanh ghi mặt nạ. D0D1D2D3D4D5D6D7A0 RISRRP10SMMESMM00 Đọc thanh ghi IRR ở lần sau Đọc thanh ghi IRR ở lần sau Không làm gì 1100 1010 Đăt mặt nạ đặc biệt Xóa mặt nạ đặc biệt Không làm gì 1100 1010 1 = thăm dò yêu cầu ngắt 0 = Không thăm dò 5.1.2. LẬP TRÌNH CHO PIC 8259A (tiếp theo) 22 v1.0014103212 5.1.2. LẬP TRÌNH CHO PIC 8259A (tiếp theo) • Các chế độ ngắt: Có 4 chế độ Chế độ Chức năng, Ý nghĩa Ưu tiên cố định Mỗi ngắt được gán 1 mức ưu tiên cố định. Mức 0 là cao nhất, mức 7 là thấp nhất. Ưu tiên vòng tự động Ưu tiên đồng đều, mỗi mức sau khi được phục vụ trở thành mức thấp nhất cho đến khi có ngắt tiếp theo xảy ra. Ưu tiên vòng theo quy định Phần mềm của hệ quy định mức ưu tiên thấp nhất. Thứ tự ưu tiên được lập dựa trên cơ sở quy định này. Thăm dò ngắt Phần mềm của hệ đọc thanh ghi trạng thái của 8259, từ đó xác định nguồn ngắt và quyết định phục vụ ngắt. 23 v1.0014103212 5.2.1. Cấu tạo và nguyên tắc hoạt động của 8255A 5.2.2 Lập trình với 8255A 5.2. CHIP GHÉP NỐI NGOẠI VI KHẢ TRÌNH PPI-8255A 24 v1.0014103212 • PPI-8255A (Programmable Peripheral Interface) Là chip vào/ra lập trình được; Truyền dữ liệu theo phương thức song song. Hình 3: Sơ đồ khối và các chân của 8255A 5.2.1. CẤU TẠO VÀ NGUYÊN TẮC HOẠT ĐỘNG CỦA 8255A 25 v1.0014103212 5.2.1. CẤU TẠO VÀ NGUYÊN TẮC HOẠT ĐỘNG CỦA 8255A • 24 chân cho 3 cổng vào/ra. • PA0-PA7: 8 chân cho cổng A. • PB0-PB7: 8 chân cho cổng B. • PC0-PC7: 8 chân cho cổng C. • Nhóm A: Gồm cổng A và 4 bit cao của cổng C. • Nhóm B: Gồm cổng B và 4 bit thấp của cổng C. • 8255 có thể hoạt động ở 3 chế độ (0,1,2). 26 v1.0014103212 • Chân chọn chip 8255A để làm việc cùng với bộ xử lý. • Chân : Đọc dữ liệu từ 8255A. • Chân : Ghi dữ liệu vào 8255A. • Hai chân A0, A1 kết hợp với tín hiệu , và cho phép truy cập 1 trong 3 cổng PA, PB, PC hoặc thanh ghi từ điều khiển. CS RD WR RD WR A1 A0 Ý nghĩa 0 0 0 1 Đọc cổng A vào bus dữ liệu 0 1 0 1 Đọc cổng B vào bus dữ liệu 1 0 0 1 Đọc cổng C vào bus dữ liệu 1 1 0 1 Đọc từ điều khiển vào bus dữ liệu 0 0 1 0 Viết từ bus dữ liệu vào cổng A 0 1 1 0 Viết từ bus dữ liệu vào cổng B 1 0 1 0 Viết từ bus dữ liệu vào cổng C 1 1 1 0 Viết từ bus dữ liệu vào từ điều khiển RD WR 5.2.1. CẤU TẠO VÀ NGUYÊN TẮC HOẠT ĐỘNG CỦA 8255A (tiếp theo) 27 v1.0014103212 5.2.1. CẤU TẠO VÀ NGUYÊN TẮC HOẠT ĐỘNG CỦA 8255A (tiếp theo) • Chọn chế độ hoạt động cho 8255A 8255A có thể hoạt động ở 3 chế độ: Chế độ 0, 1, 2. Tất cả các cổng của 8255A đều làm việc như cổng vào. Để chọn chế độ cho 8255A ta ghi dữ liệu vào từ điều khiển của 8255A. 28 v1.0014103212 • Đặt/xóa các bit của cổng C Các bit của cổng C có thể được đặt/xóa thông qua việc viết từ điều khiển với bit D7=0. 5.2.2. LẬP TRÌNH VỚI 8255A (tiếp theo) 29 v1.0014103212 5.2.2. LẬP TRÌNH VỚI 8255A (tiếp theo) • Các chế độ hoạt động của 8255A Chế độ 0: Vào/ra một chiều không có móc nối Vi mạch gồm 2 cổng 8 bit; Các cổng có thể là cổng vào/ra; Các tín hiệu ra được chốt; Các tín hiệu vào không được chốt; 8255 có 16 cấu hình hoạt động vào/ra nhờ sử dụng từ điều khiển. 30 v1.0014103212 • Các chế độ hoạt động của 8255A Chế độ 1: Vào/ra hai chiều có móc nối qua các bit cao của cổng C Vi mạch hoạt động gồm 2 nhóm: Nhóm A và B; Mỗi nhóm có 1 cổng 8 bit và 1 cổng điều khiển 4 bit; Cổng 8 bit có thể là cổng vào/ra, chốt dữ liệu. 5.2.2. LẬP TRÌNH VỚI 8255A (tiếp theo) 31 v1.0014103212 5.2.2. LẬP TRÌNH VỚI 8255A (tiếp theo) • Các chế độ hoạt động của 8255A Chế độ 3: Vào/ra hai chiều qua cổng A có móc nối qua các bit cao của cổng C Vi mạch chỉ có nhóm A hoạt động; Cổng A là cổng vào/ra hai chiều 8 bit; Các tín hiệu vào/ra đều được chốt lại; 5 bit của cổng C được sử dụng làm cổng điều khiển, trạng thái cho cổng A. 32 v1.0014103212 5.3.1. Cấu tạo và nguyên tắc hoạt động 5.3.2 Lập trình với 8253 5.3. CHIP ĐỊNH THỜI KHẢ TRÌNH PIT-8253 33 v1.0014103212 5.3.1. CẤU TẠO VÀ NGUYÊN TẮC HOẠT ĐỘNG 34 v1.0014103212 5.3.1. CẤU TẠO VÀ NGUYÊN TẮC HOẠT ĐỘNG • 3 bộ đếm C0, C1, C2: Các bộ đếm lùi, 16 bit. • Bộ đệm số liệu: 8 bit, sử dụng để phối ghép với bus hệ thống của bộ VXL. • Chân : Cho phép đọc dữ liệu từ 8253. • Chân : Cho phép ghi dữ liệu vào 8253. • Chân : Chọn chip 8253 RD WR CS A1 A0 Ý nghĩa 0 0 0 1 Đọc bộ đếm 0 0 1 0 1 Đọc bộ đếm 1 1 0 0 1 Đọc bộ đếm 2 1 1 0 1 Đọc từ điều khiển 0 0 1 0 Viết vào bộ đếm 0 0 1 1 0 Viết vào bộ đếm 1 1 0 1 0 Viết vào bộ đếm 2 1 1 1 0 Viết từ điều khiển vào thanh ghi điều khiển RD WR 35 v1.0014103212 • Địa chỉ các thanh ghi và định dạng từ điều khiển Địa chỉ các cổng của PIT như sau: Cổng 1 Cổng 2 Thanh ghi Hoạt động 040h 048h Bộ đếm 0 Đọc/viết 041h 049h Bộ đếm 1 Đọc/viết 042h 04ah Bộ đếm 2 Đọc/viết 043h 04bh Điều khiển Đọc/viết 5.3.2. LẬP TRÌNH CHO 8253 36 v1.0014103212 5.3.2. LẬP TRÌNH CHO 8253 • Địa chỉ các thanh ghi và định dạng từ điều khiển Định dạng từ điều khiển SC0, SC1: Chọn bộ đếm, 00: bộ đếm 0, 01: bộ đếm 1, 10: bộ đếm 2. RW0, RW1: Phương thức đọc/ghi 00: Lệnh chốt bộ đếm; 01: Chỉ đọc/viết byte thấp; 10: Chỉ đọc/viết byte cao; 11: Đọc/viết byte thấp trước, byte cao sau. SC1 SC0 RW1 RW0 M2 M1 M0 BCD D0D1D2D3D4D5D6D7 37 v1.0014103212 • Các chế độ đếm Chế độ 0: Phát ra tại một sườn xung lên khi kết thúc đếm. Hình 5: Chế độ đếm 0 với số đếm là 4 5.3.2. LẬP TRÌNH CHO 8253 (tiếp theo) 38 v1.0014103212 5.3.2. LẬP TRÌNH CHO 8253 (tiếp theo) Chế độ 1: Phát ra một xung đơn với thời gian tồn tại xung biến đổi được. Hình 6: Chế độ đếm 1 với số đếm là 4 39 v1.0014103212 5.3.2. LẬP TRÌNH CHO 8253 (tiếp theo) Chế độ 2: Các xung nhịp đưa vào bộ đếm được chia bởi giá trị nạp trong thanh ghi bộ đếm. Hình 7: Chế độ đếm 2 với số đếm là 4 40 v1.0014103212 5.3.2. LẬP TRÌNH CHO 8253 (tiếp theo) Chế độ 3: Phát ra sóng hình vuông. Hình 8: Chế độ đếm 3 với số đếm là 4 Chế độ 4: Tạo xung bằng phần mềm. Chế độ 5: Tạo xung bằng xung của cửa GATE, giống như chế độ 2. 41 v1.0014103212 • Viết bộ đếm Viết từ điều khiển để xác lập chế độ làm việc. Nạp số đếm ban đầu. Ví dụ sử dụng bộ đếm 2, phát xung hình vuông (chế độ 3), tần số 10KHz, tần số Clock: 1.19318MHz, hệ số chia viết vào bộ đếm 2 là: 119. MOV AL, 1001 0110 b; nạp từ điều khiển vào AL. OUT 43h, AL; viết từ điều khiển qua cổng 43h vào thanh ghi điều khiển. MOV AL, 119; nạp byte thấp vào AL. OUT 42h, AL; viết giá trị đếm vào bộ đếm C2. 5.3.2. LẬP TRÌNH CHO 8253 (tiếp theo) 42 v1.0014103212 5.3.2. LẬP TRÌNH CHO 8253 (tiếp theo) • Đọc bộ đếm Nếu cần đọc giá trị tức thời của bộ đếm khi quá trình đếm chưa kết thúc thì phải sử dụng các lệnh chốt bộ đếm hoặc lệnh đọc thanh ghi từ điều khiển. Tại thời điểm lệnh chốt bộ đếm được viết vào thanh ghi từ điều khiển, giá trị đếm được chốt vào thanh ghi đệm ra của PIT 8253. SC1, SC0: 2 bit chọn bộ đếm được chốt. 00: Bộ đếm 0 được chọn. 01: Bộ đếm 1 được chọn. 10: Bộ đếm 2 được chọn. X: Không có nghĩa. SC1 SC0 0 0 x x x x D0D1D2D3D4D5D6D7 43 v1.0014103212 5.3.2. LẬP TRÌNH CHO 8253 (tiếp theo) • Các chức năng của bộ đếm trong máy vi tính Cập nhật đồng hồ hệ thống: Bộ đếm hoạt động ở chế độ 2; Lối vào có xung nhịp: 1.19318MHz; Lối vào cổng Gate đặt ở mức logic 1; Giá trị ban đầu là 0 hoặc 65535. Làm tươi bộ nhớ RAM; Phát sóng âm với tần số biến đổi ra loa. 44 v1.0014103212 5.4.1. Phương pháp truy nhập bộ nhớ trực tiếp 5.4.2. Chip điều khiển DMAC 5.4. CHIP TRUY NHẬP BỘ NHỚ TRỰC TIẾP DMA-8237 45 v1.0014103212 • Phương pháp vào/ra bằng ngắt đảm bảo thời gian vào/ra số liệu ngắn, nhưng phải thực hiện bằng phần mềm Cần sự tham gia của bộ VXL. • Khi cần chuyển lượng dữ liệu nhiều Không đủ nhanh để đáp ứng. • Sử dụng một mạch phần cứng thực hiện việc truyền dữ liệu giữa bộ nhớ và các TBNV không cần qua bộ VXL Gọi là phương pháp truy nhập bộ nhớ trực tiếp (DMA – Direct MemoryAccess). Hình 9: Các đường liên hệ trực tiếp trong quá trình DMA Không gian vào/ra Vi xử lý Không gian bộ nhớ DMAC 5.4.1. PHƯƠNG PHÁP TRUY NHẬP BỘ NHỚ TRỰC TIẾP 46 v1.0014103212 5.4.1. PHƯƠNG PHÁP TRUY NHẬP BỘ NHỚ TRỰC TIẾP • DMAC chia sẻ thời gian sử dụng các bus dữ liệu, địa chỉ và điều khiển. Hình 10: Sơ đồ phối ghép DMAC với bộ nhớ, TBNV, và bộ VXL Thiết bị I/O CPU DMAC HRQ HACK DRQ DACK DRQ DACK HOLD HLDA Bộ nhớ 47 v1.0014103212 • Sơ đồ nguyên lý của DMAC 5.4.2. CHIP ĐIỀU KHIỂN DMAC 48 v1.0014103212 5.4.2. CHIP ĐIỀU KHIỂN DMAC • DMAC gồm 3 khối chính Timing Control: Sinh ra các tín hiệu định thời bên trong và tín hiệu điều khiển bên ngoài 8237. Program Command Control Giải mã các lệnh gửi tới 8237 trước khi phục vụ yêu cầu DMA. Giải mã từ điều khiển chế độ xác định kiểu DMA trong khi phục vụ yêu cầu DMA. Priority Encoder: Giải quyết xung đột yêu cầu DMA đồng thời. 49 v1.0014103212 • Các chân tín hiệu của DMAC : DMAC đang đọc tín hiệu từ thiết bị ngoại vi; : DMAC đang viết dữ liệu ra thiết bị ngoại vi; : Dữ liệu được đọc từ bộ nhớ chính; : Dữ liệu được ghi vào bộ nhớ chính; READY: Tín hiệu vào từ bộ nhớ hoặc thiết bị ngoại vi; HLDA: CPU báo cho DMAC biết CPU đã rời khỏi bus, trao bus cho DMAC; ADSTB: Nhận byte cao và chốt địa chỉ ngoài của DMA; AEN: Kích hoạt chốt địa chỉ của DMA; HRQ: Tín hiệu yêu cầu DMA từ chip 8237. MEMW MEMR IOW IOR 5.4.2. CHIP ĐIỀU KHIỂN DMAC (tiếp theo) 50 v1.0014103212 5.4.2. CHIP ĐIỀU KHIỂN DMAC (tiếp theo) • Các chân tín hiệu của DMAC: : Tín hiệu chọn chip; CLK: Lối vào xung đồng hồ; RESET: Khởi động lại chip; : Chấp nhận DMA; DREQ0-DREQ3: Đòi hỏi DMA từ TBNV; DB0-DB7: Bus dữ liệu 2 chiều; A0-A7: Tín hiệu địa chỉ; : Kết thúc xử lí DMA. CS EOP DACK 0 – DACK 3 51 v1.0014103212 5.4.2. CHIP ĐIỀU KHIỂN DMAC (tiếp theo) • Hoạt động của 8237: Bao gồm 2 chu kỳ hoạt động Chu kỳ rỗi Kiểm tra các tín hiệu DREQ xem có thiết bị nào yêu cầu DMA; Kiểm tra CS nếu CPU có yêu cầu đọc/ghi các thanh ghi bên trong. Chu kỳ hoạt động Diễn ra khi có yêu cầu DREQ từ thiết bị ngoại vi; Gửi tín hiệu HRQ tới CPU; Hoạt động 1 trong 4 chế độ: Chế độ chuyển từng từ, chế độ chuyển mảng, chế độ chuyển theo nhu cầu, chế độ ghép tầng. 52 v1.0014103212 Trong bài này chúng ta đã tìm hiểu các nội dung sau: • Các chip bổ trợ trong hệ thống máy tính; • Cấu tạo và nguyên tắc hoạt động của các chip bổ trợ cơ bản như: 8255, 8259, 8237, TÓM LƯỢC CUỐI BÀI

File đính kèm:

bai_giang_kien_truc_may_tinh_bai_5_cac_chip_bo_tro_phan_than.pdf

bai_giang_kien_truc_may_tinh_bai_5_cac_chip_bo_tro_phan_than.pdf