Ứng dụng công cụ mới trên nền tảng FPGA vào xử lý ảnh và video

Tóm tắt

Bài báo này đề xuất phát triển các ứng dụng xử lý ảnh và video thời gian thực trên thiết bị FPGA mới

được phát triển bởi hãng Xilinx: bộ công cụ Xilinx ZVIK. Bộ ZVIK được xây dựng trên nền tảng bộ

Zynq-7000 ZC702, bao gồm cả phần cứng, phần mềm và các thành phần IP dùng trong phát triển các

ứng dụng video. Trong bài báo này, bộ công cụ zynq-7000 được dùng trong xử lý ảnh và video thời gian

thực, được hỗ trợ với giao diện người dùng trên nền web, giúp cho việc tùy chỉnh các thông số trong hệ

thống xử lý ảnh trở nên dễ dàng và thân thiện hơn. Ở đây, một giải thuật nhận dạng chuyển động thời

gian thực được triển khai trên phần cứng, đồng thời sử dụng hệ thống nhúng để điều khiển phần mềm.

Từ đó có thể được ứng dụng trong các hệ thống giám sát, an ninh.

Trang 1

Trang 2

Trang 3

Trang 4

Trang 5

Trang 6

Trang 7

Trang 8

Trang 9

Trang 10

Tóm tắt nội dung tài liệu: Ứng dụng công cụ mới trên nền tảng FPGA vào xử lý ảnh và video

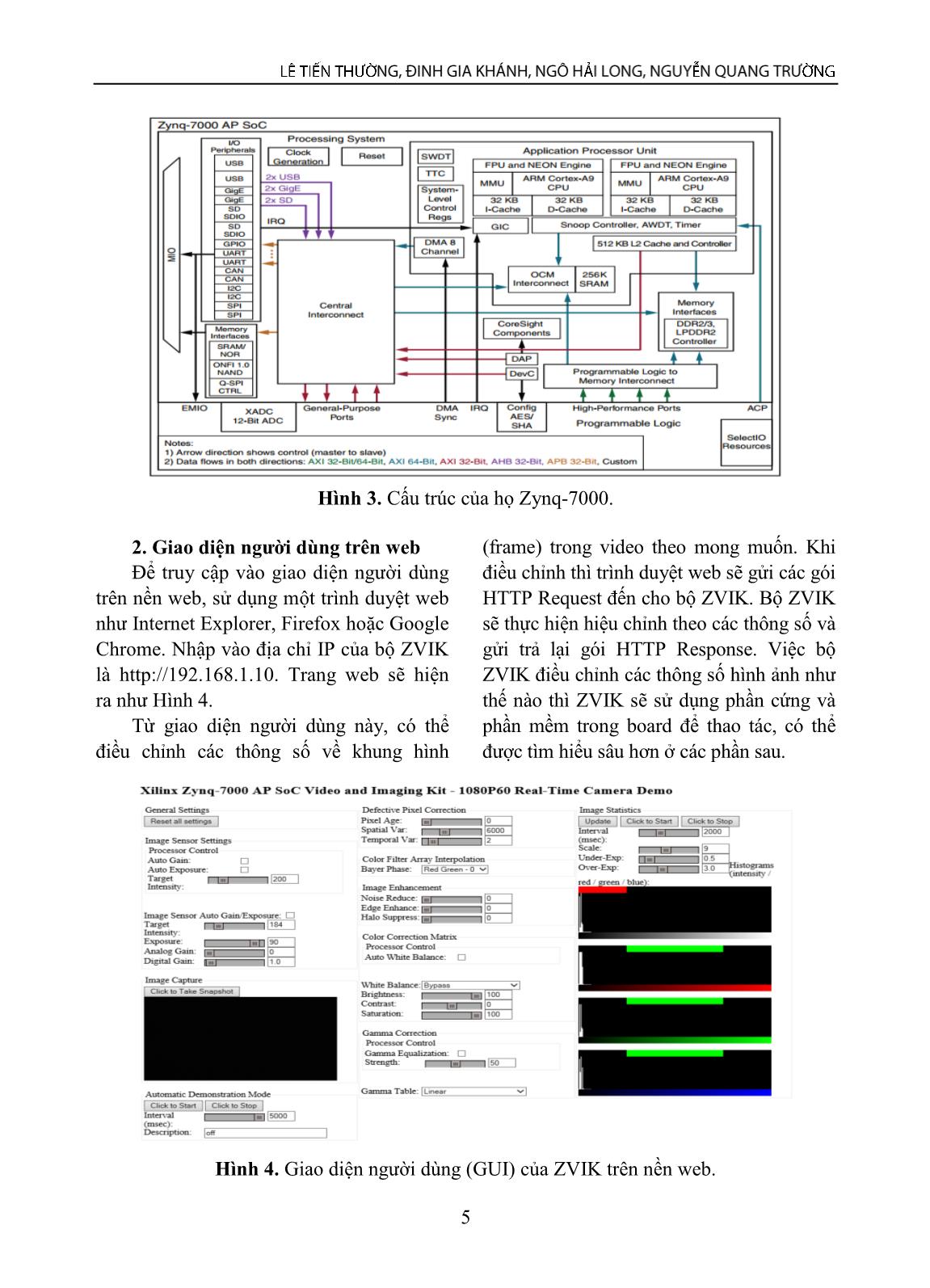

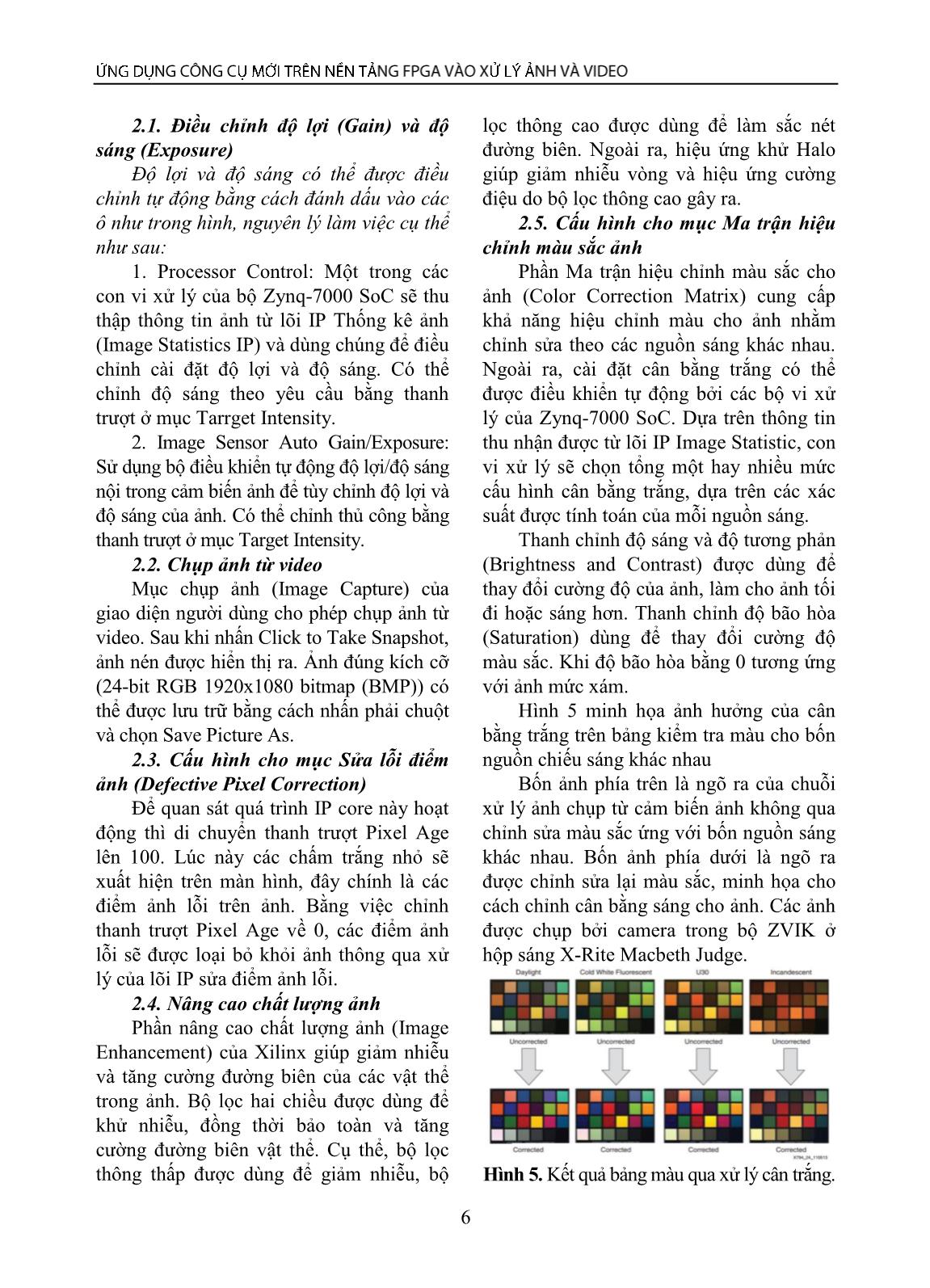

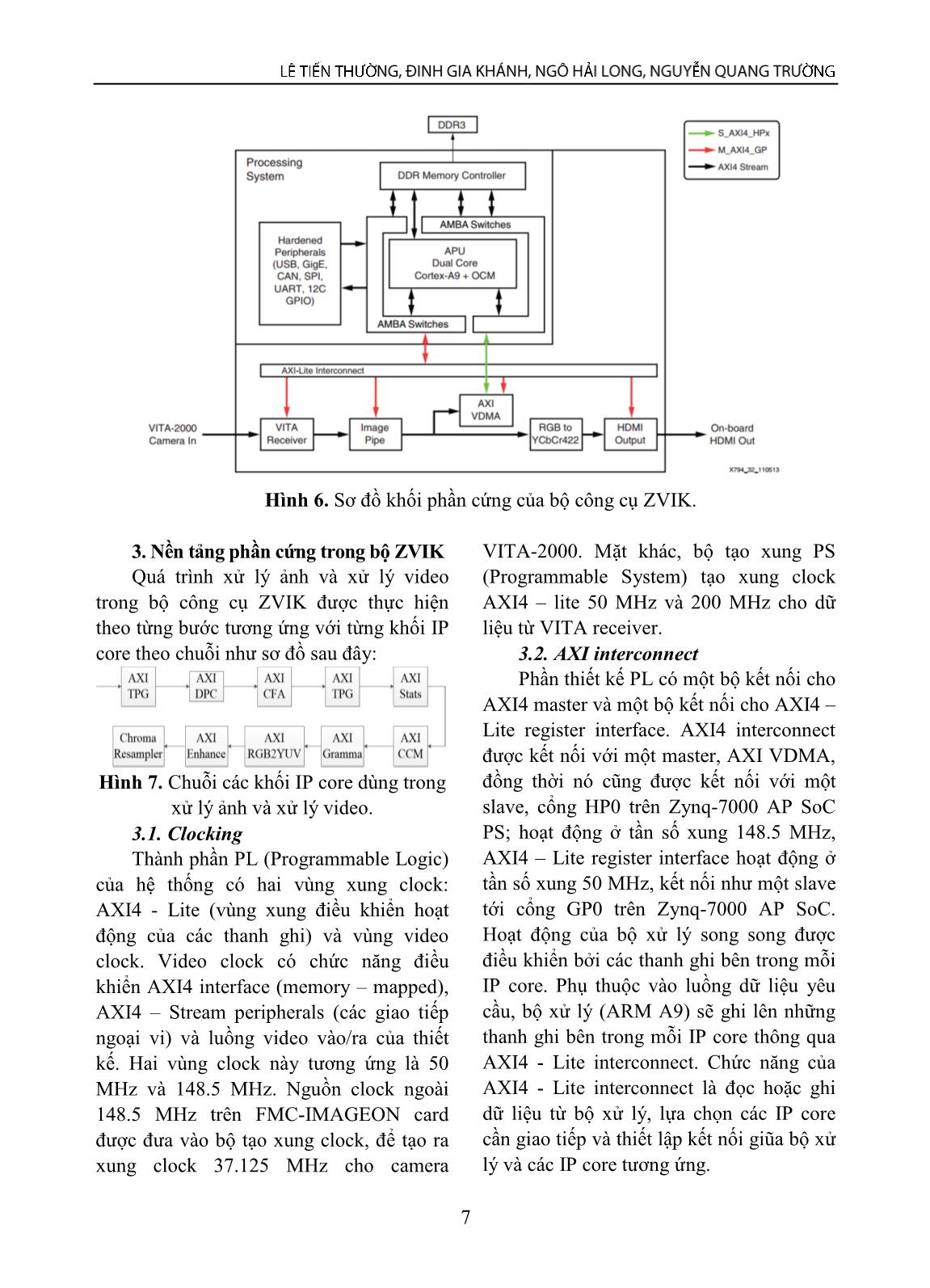

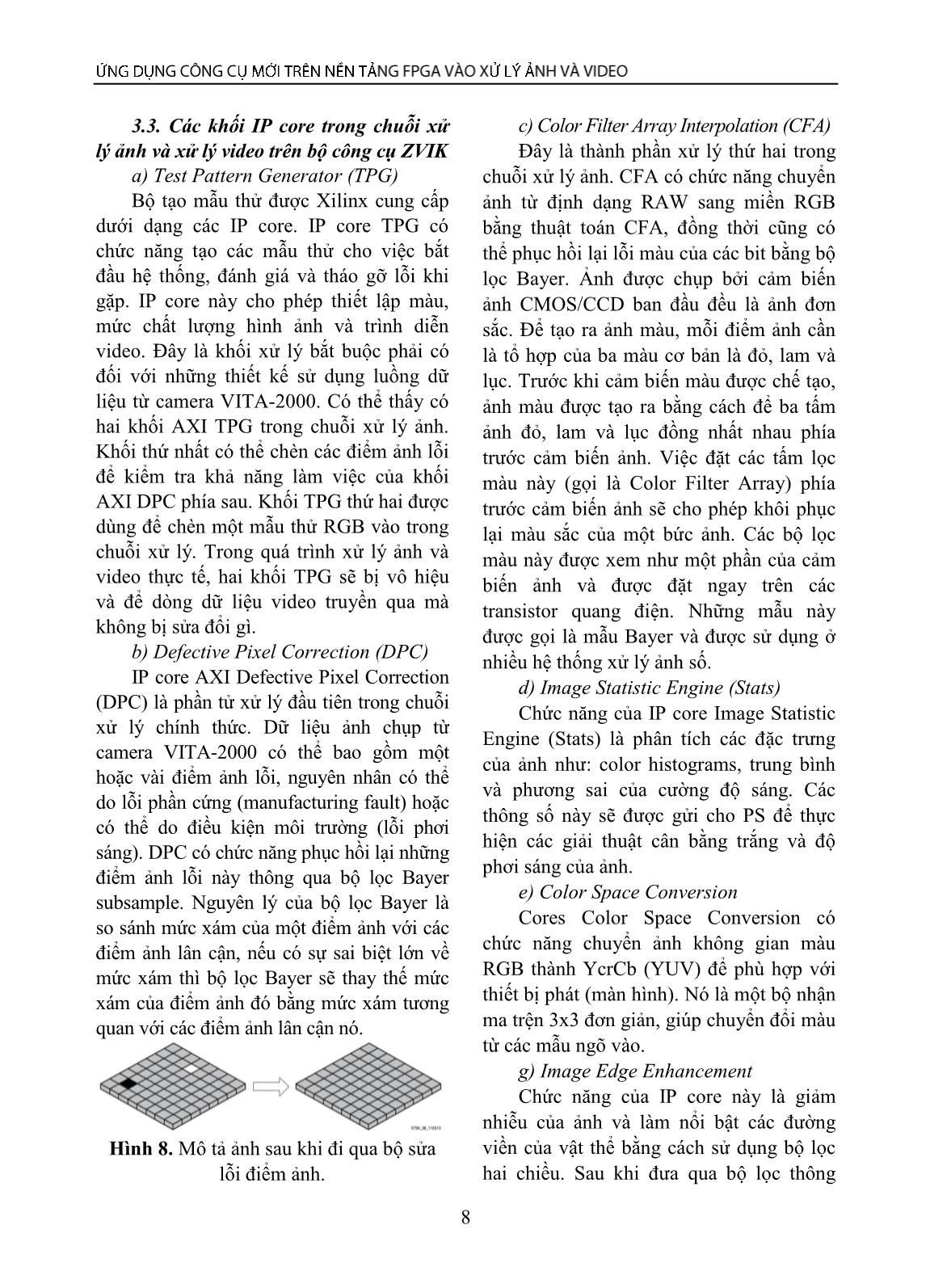

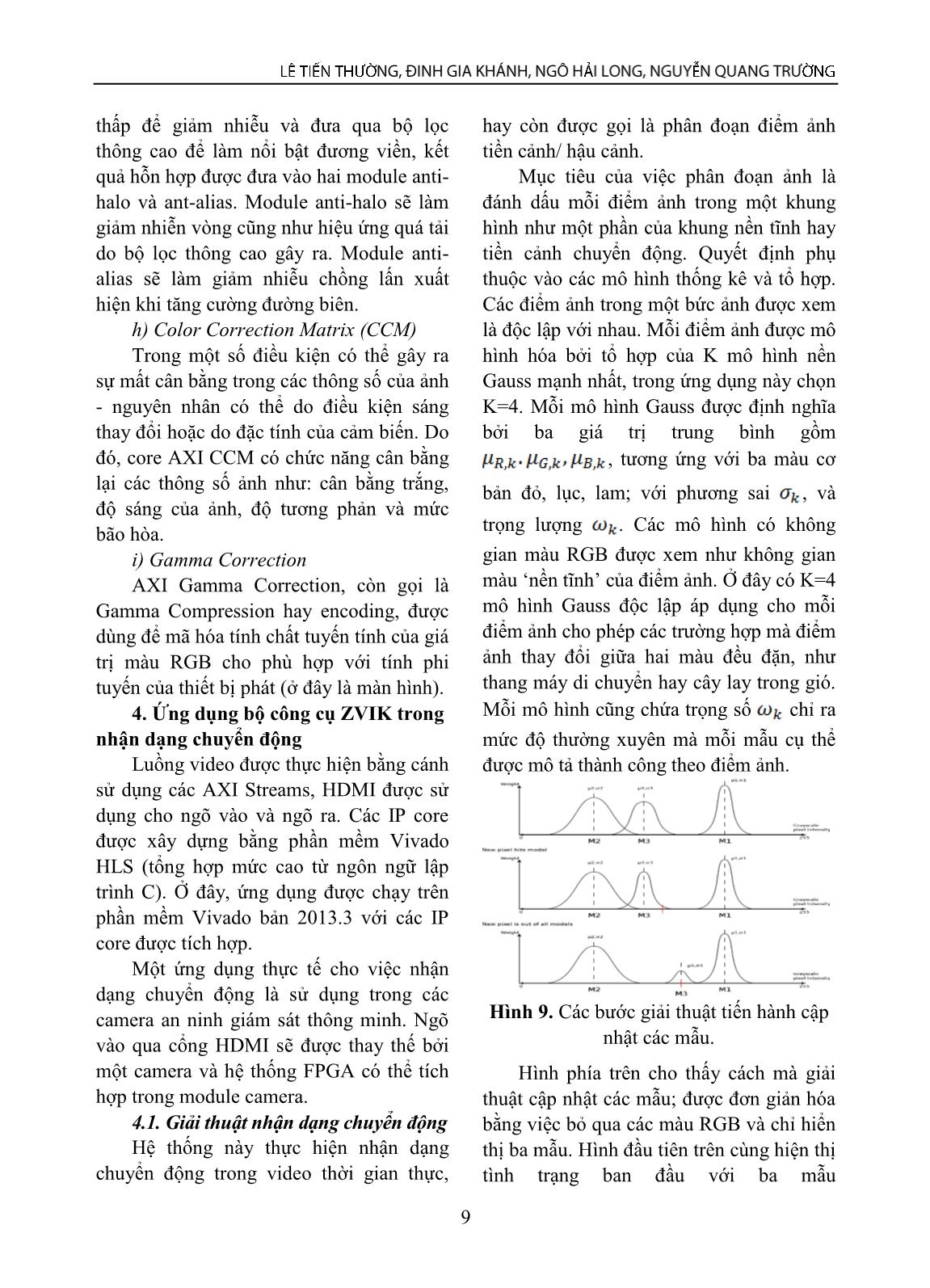

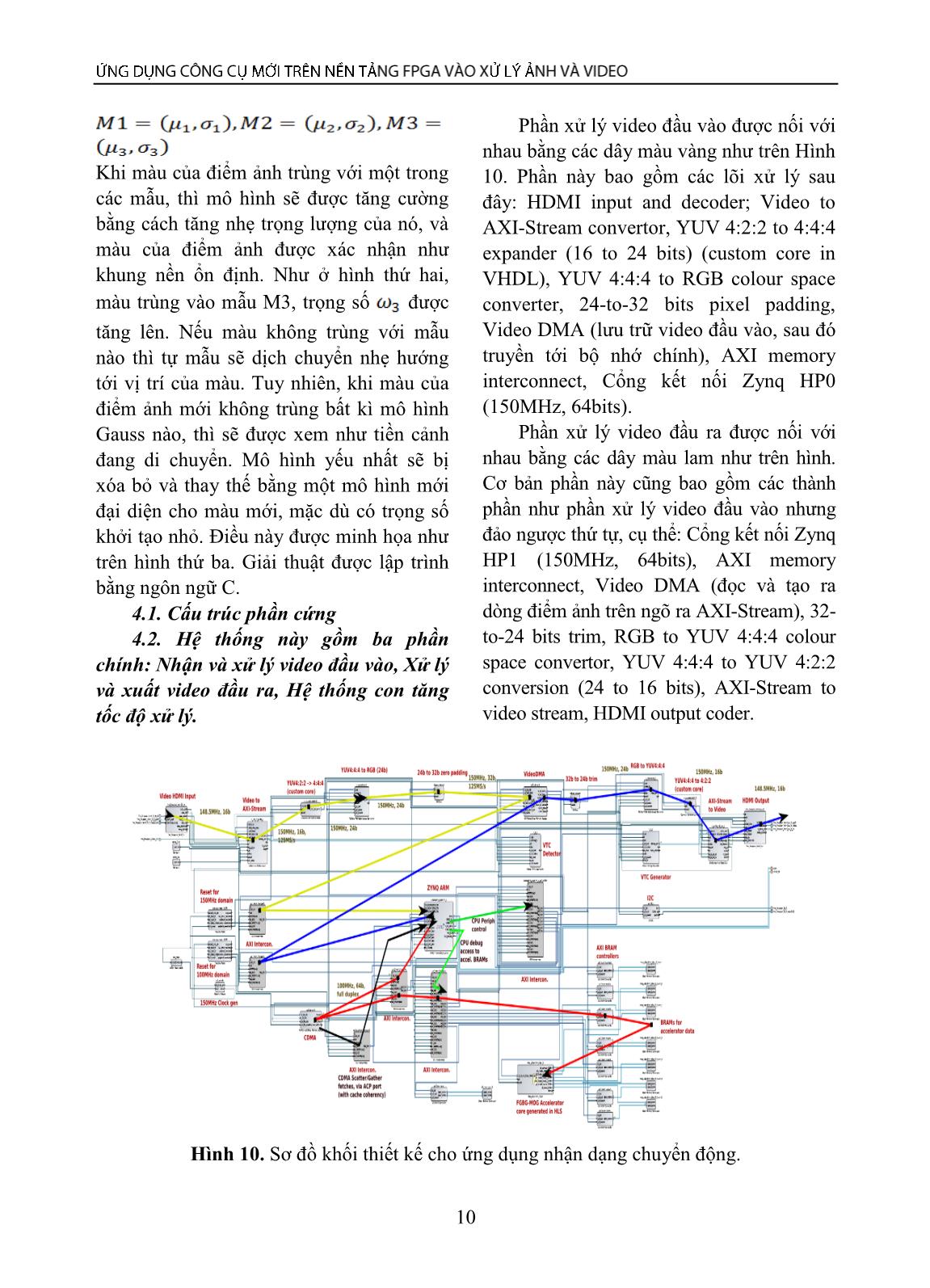

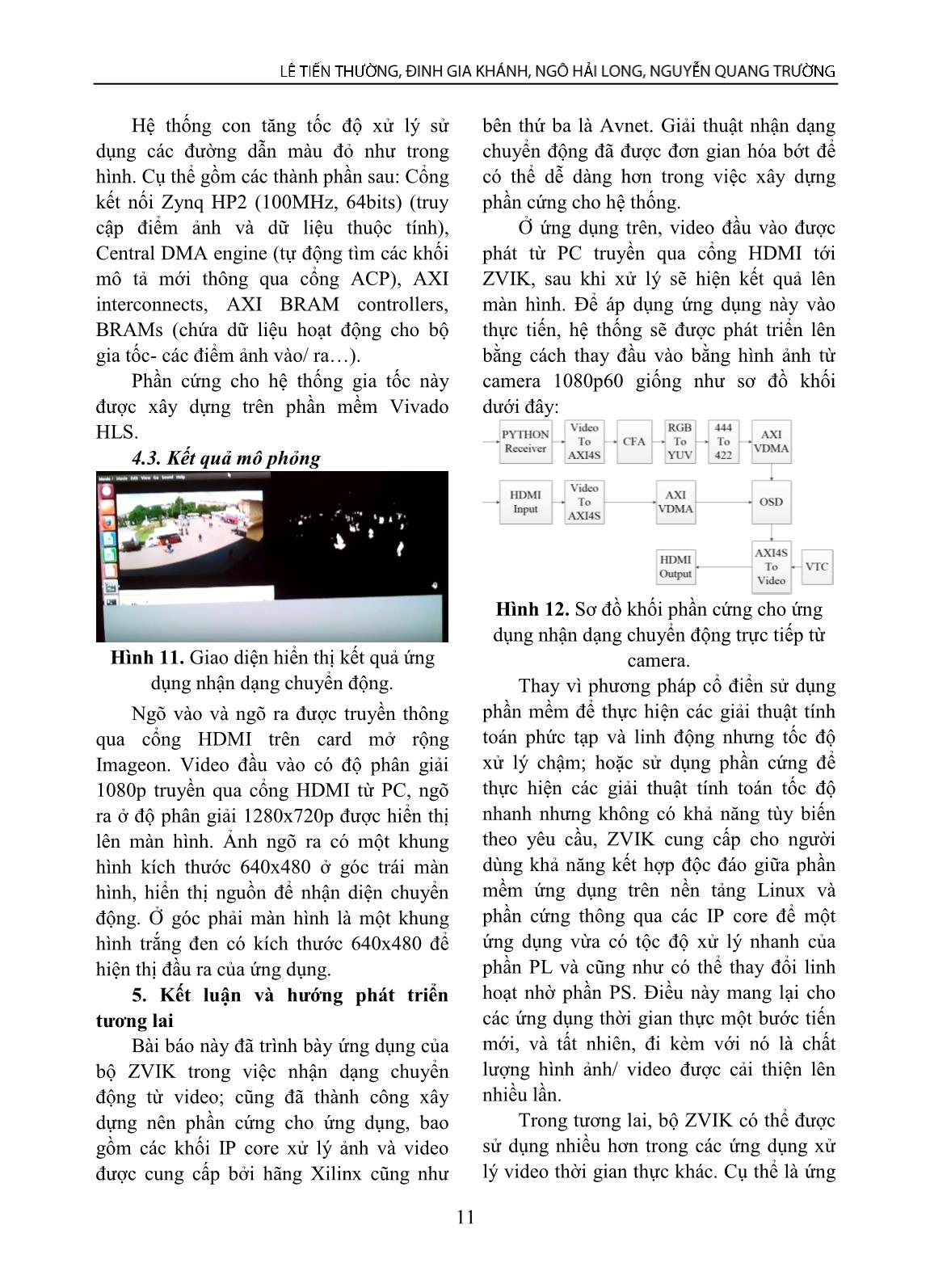

ideo clock. Video clock có chức năng điều khiển AXI4 interface (memory – mapped), AXI4 – Stream peripherals (các giao tiếp ngoại vi) và luồng video vào/ra của thiết kế. Hai vùng clock này tương ứng là 50 MHz và 148.5 MHz. Nguồn clock ngoài 148.5 MHz trên FMC-IMAGEON card được đưa vào bộ tạo xung clock, để tạo ra xung clock 37.125 MHz cho camera VITA-2000. Mặt khác, bộ tạo xung PS (Programmable System) tạo xung clock AXI4 – lite 50 MHz và 200 MHz cho dữ liệu từ VITA receiver. 3.2. AXI interconnect Phần thiết kế PL có một bộ kết nối cho AXI4 master và một bộ kết nối cho AXI4 – Lite register interface. AXI4 interconnect được kết nối với một master, AXI VDMA, đồng thời nó cũng được kết nối với một slave, cổng HP0 trên Zynq-7000 AP SoC PS; hoạt động ở tần số xung 148.5 MHz, AXI4 – Lite register interface hoạt động ở tần số xung 50 MHz, kết nối như một slave tới cổng GP0 trên Zynq-7000 AP SoC. Hoạt động của bộ xử lý song song được điều khiển bởi các thanh ghi bên trong mỗi IP core. Phụ thuộc vào luồng dữ liệu yêu cầu, bộ xử lý (ARM A9) sẽ ghi lên những thanh ghi bên trong mỗi IP core thông qua AXI4 - Lite interconnect. Chức năng của AXI4 - Lite interconnect là đọc hoặc ghi dữ liệu từ bộ xử lý, lựa chọn các IP core cần giao tiếp và thiết lập kết nối giũa bộ xử lý và các IP core tương ứng. 8 3.3. Các khối IP core trong chuỗi xử lý ảnh và xử lý video trên bộ công cụ ZVIK a) Test Pattern Generator (TPG) Bộ tạo mẫu thử được Xilinx cung cấp dưới dạng các IP core. IP core TPG có chức năng tạo các mẫu thử cho việc bắt đầu hệ thống, đánh giá và tháo gỡ lỗi khi gặp. IP core này cho phép thiết lập màu, mức chất lượng hình ảnh và trình diễn video. Đây là khối xử lý bắt buộc phải có đối với những thiết kế sử dụng luồng dữ liệu từ camera VITA-2000. Có thể thấy có hai khối AXI TPG trong chuỗi xử lý ảnh. Khối thứ nhất có thể chèn các điểm ảnh lỗi để kiểm tra khả năng làm việc của khối AXI DPC phía sau. Khối TPG thứ hai được dùng để chèn một mẫu thử RGB vào trong chuỗi xử lý. Trong quá trình xử lý ảnh và video thực tế, hai khối TPG sẽ bị vô hiệu và để dòng dữ liệu video truyền qua mà không bị sửa đổi gì. b) Defective Pixel Correction (DPC) IP core AXI Defective Pixel Correction (DPC) là phần tử xử lý đầu tiên trong chuỗi xử lý chính thức. Dữ liệu ảnh chụp từ camera VITA-2000 có thể bao gồm một hoặc vài điểm ảnh lỗi, nguyên nhân có thể do lỗi phần cứng (manufacturing fault) hoặc có thể do điều kiện môi trường (lỗi phơi sáng). DPC có chức năng phục hồi lại những điểm ảnh lỗi này thông qua bộ lọc Bayer subsample. Nguyên lý của bộ lọc Bayer là so sánh mức xám của một điểm ảnh với các điểm ảnh lân cận, nếu có sự sai biệt lớn về mức xám thì bộ lọc Bayer sẽ thay thế mức xám của điểm ảnh đó bằng mức xám tương quan với các điểm ảnh lân cận nó. Hình 8. Mô tả ảnh sau khi đi qua bộ sửa lỗi điểm ảnh. c) Color Filter Array Interpolation (CFA) Đây là thành phần xử lý thứ hai trong chuỗi xử lý ảnh. CFA có chức năng chuyển ảnh từ định dạng RAW sang miền RGB bằng thuật toán CFA, đồng thời cũng có thể phục hồi lại lỗi màu của các bit bằng bộ lọc Bayer. Ảnh được chụp bởi cảm biến ảnh CMOS/CCD ban đầu đều là ảnh đơn sắc. Để tạo ra ảnh màu, mỗi điểm ảnh cần là tổ hợp của ba màu cơ bản là đỏ, lam và lục. Trước khi cảm biến màu được chế tạo, ảnh màu được tạo ra bằng cách để ba tấm ảnh đỏ, lam và lục đồng nhất nhau phía trước cảm biến ảnh. Việc đặt các tấm lọc màu này (gọi là Color Filter Array) phía trước cảm biến ảnh sẽ cho phép khôi phục lại màu sắc của một bức ảnh. Các bộ lọc màu này được xem như một phần của cảm biến ảnh và được đặt ngay trên các transistor quang điện. Những mẫu này được gọi là mẫu Bayer và được sử dụng ở nhiều hệ thống xử lý ảnh số. d) Image Statistic Engine (Stats) Chức năng của IP core Image Statistic Engine (Stats) là phân tích các đặc trưng của ảnh như: color histograms, trung bình và phương sai của cường độ sáng. Các thông số này sẽ được gửi cho PS để thực hiện các giải thuật cân bằng trắng và độ phơi sáng của ảnh. e) Color Space Conversion Cores Color Space Conversion có chức năng chuyển ảnh không gian màu RGB thành YcrCb (YUV) để phù hợp với thiết bị phát (màn hình). Nó là một bộ nhận ma trện 3x3 đơn giản, giúp chuyển đổi màu từ các mẫu ngõ vào. g) Image Edge Enhancement Chức năng của IP core này là giảm nhiễu của ảnh và làm nổi bật các đường viền của vật thể bằng cách sử dụng bộ lọc hai chiều. Sau khi đưa qua bộ lọc thông 9 thấp để giảm nhiễu và đưa qua bộ lọc thông cao để làm nổi bật đương viền, kết quả hỗn hợp được đưa vào hai module anti- halo và ant-alias. Module anti-halo sẽ làm giảm nhiễn vòng cũng như hiệu ứng quá tải do bộ lọc thông cao gây ra. Module anti- alias sẽ làm giảm nhiễu chồng lấn xuất hiện khi tăng cường đường biên. h) Color Correction Matrix (CCM) Trong một số điều kiện có thể gây ra sự mất cân bằng trong các thông số của ảnh - nguyên nhân có thể do điều kiện sáng thay đổi hoặc do đặc tính của cảm biến. Do đó, core AXI CCM có chức năng cân bằng lại các thông số ảnh như: cân bằng trắng, độ sáng của ảnh, độ tương phản và mức bão hòa. i) Gamma Correction AXI Gamma Correction, còn gọi là Gamma Compression hay encoding, được dùng để mã hóa tính chất tuyến tính của giá trị màu RGB cho phù hợp với tính phi tuyến của thiết bị phát (ở đây là màn hình). 4. Ứng dụng bộ công cụ ZVIK trong nhận dạng chuyển động Luồng video được thực hiện bằng cánh sử dụng các AXI Streams, HDMI được sử dụng cho ngõ vào và ngõ ra. Các IP core được xây dựng bằng phần mềm Vivado HLS (tổng hợp mức cao từ ngôn ngữ lập trình C). Ở đây, ứng dụng được chạy trên phần mềm Vivado bản 2013.3 với các IP core được tích hợp. Một ứng dụng thực tế cho việc nhận dạng chuyển động là sử dụng trong các camera an ninh giám sát thông minh. Ngõ vào qua cổng HDMI sẽ được thay thế bởi một camera và hệ thống FPGA có thể tích hợp trong module camera. 4.1. Giải thuật nhận dạng chuyển động Hệ thống này thực hiện nhận dạng chuyển động trong video thời gian thực, hay còn được gọi là phân đoạn điểm ảnh tiền cảnh/ hậu cảnh. Mục tiêu của việc phân đoạn ảnh là đánh dấu mỗi điểm ảnh trong một khung hình như một phần của khung nền tĩnh hay tiền cảnh chuyển động. Quyết định phụ thuộc vào các mô hình thống kê và tổ hợp. Các điểm ảnh trong một bức ảnh được xem là độc lập với nhau. Mỗi điểm ảnh được mô hình hóa bởi tổ hợp của K mô hình nền Gauss mạnh nhất, trong ứng dụng này chọn K=4. Mỗi mô hình Gauss được định nghĩa bởi ba giá trị trung bình gồm , tương ứng với ba màu cơ bản đỏ, lục, lam; với phương sai , và trọng lượng . Các mô hình có không gian màu RGB được xem như không gian màu ‘nền tĩnh’ của điểm ảnh. Ở đây có K=4 mô hình Gauss độc lập áp dụng cho mỗi điểm ảnh cho phép các trường hợp mà điểm ảnh thay đổi giữa hai màu đều đặn, như thang máy di chuyển hay cây lay trong gió. Mỗi mô hình cũng chứa trọng số chỉ ra mức độ thường xuyên mà mỗi mẫu cụ thể được mô tả thành công theo điểm ảnh. Hình 9. Các bước giải thuật tiến hành cập nhật các mẫu. Hình phía trên cho thấy cách mà giải thuật cập nhật các mẫu; được đơn giản hóa bằng việc bỏ qua các màu RGB và chỉ hiển thị ba mẫu. Hình đầu tiên trên cùng hiện thị tình trạng ban đầu với ba mẫu 10 Khi màu của điểm ảnh trùng với một trong các mẫu, thì mô hình sẽ được tăng cường bằng cách tăng nhẹ trọng lượng của nó, và màu của điểm ảnh được xác nhận như khung nền ổn định. Như ở hình thứ hai, màu trùng vào mẫu M3, trọng số được tăng lên. Nếu màu không trùng với mẫu nào thì tự mẫu sẽ dịch chuyển nhẹ hướng tới vị trí của màu. Tuy nhiên, khi màu của điểm ảnh mới không trùng bất kì mô hình Gauss nào, thì sẽ được xem như tiền cảnh đang di chuyển. Mô hình yếu nhất sẽ bị xóa bỏ và thay thế bằng một mô hình mới đại diện cho màu mới, mặc dù có trọng số khởi tạo nhỏ. Điều này được minh họa như trên hình thứ ba. Giải thuật được lập trình bằng ngôn ngữ C. 4.1. Cấu trúc phần cứng 4.2. Hệ thống này gồm ba phần chính: Nhận và xử lý video đầu vào, Xử lý và xuất video đầu ra, Hệ thống con tăng tốc độ xử lý. Phần xử lý video đầu vào được nối với nhau bằng các dây màu vàng như trên Hình 10. Phần này bao gồm các lõi xử lý sau đây: HDMI input and decoder; Video to AXI-Stream convertor, YUV 4:2:2 to 4:4:4 expander (16 to 24 bits) (custom core in VHDL), YUV 4:4:4 to RGB colour space converter, 24-to-32 bits pixel padding, Video DMA (lưu trữ video đầu vào, sau đó truyền tới bộ nhớ chính), AXI memory interconnect, Cổng kết nối Zynq HP0 (150MHz, 64bits). Phần xử lý video đầu ra được nối với nhau bằng các dây màu lam như trên hình. Cơ bản phần này cũng bao gồm các thành phần như phần xử lý video đầu vào nhưng đảo ngược thứ tự, cụ thể: Cổng kết nối Zynq HP1 (150MHz, 64bits), AXI memory interconnect, Video DMA (đọc và tạo ra dòng điểm ảnh trên ngõ ra AXI-Stream), 32- to-24 bits trim, RGB to YUV 4:4:4 colour space convertor, YUV 4:4:4 to YUV 4:2:2 conversion (24 to 16 bits), AXI-Stream to video stream, HDMI output coder. Hình 10. Sơ đồ khối thiết kế cho ứng dụng nhận dạng chuyển động. 11 Hệ thống con tăng tốc độ xử lý sử dụng các đường dẫn màu đỏ như trong hình. Cụ thể gồm các thành phần sau: Cổng kết nối Zynq HP2 (100MHz, 64bits) (truy cập điểm ảnh và dữ liệu thuộc tính), Central DMA engine (tự động tìm các khối mô tả mới thông qua cổng ACP), AXI interconnects, AXI BRAM controllers, BRAMs (chứa dữ liệu hoạt động cho bộ gia tốc- các điểm ảnh vào/ ra). Phần cứng cho hệ thống gia tốc này được xây dựng trên phần mềm Vivado HLS. 4.3. Kết quả mô phỏng Hình 11. Giao diện hiển thị kết quả ứng dụng nhận dạng chuyển động. Ngõ vào và ngõ ra được truyền thông qua cổng HDMI trên card mở rộng Imageon. Video đầu vào có độ phân giải 1080p truyền qua cổng HDMI từ PC, ngõ ra ở độ phân giải 1280x720p được hiển thị lên màn hình. Ảnh ngõ ra có một khung hình kích thước 640x480 ở góc trái màn hình, hiển thị nguồn để nhận diện chuyển động. Ở góc phải màn hình là một khung hình trắng đen có kích thước 640x480 để hiện thị đầu ra của ứng dụng. 5. Kết luận và hướng phát triển tương lai Bài báo này đã trình bày ứng dụng của bộ ZVIK trong việc nhận dạng chuyển động từ video; cũng đã thành công xây dựng nên phần cứng cho ứng dụng, bao gồm các khối IP core xử lý ảnh và video được cung cấp bởi hãng Xilinx cũng như bên thứ ba là Avnet. Giải thuật nhận dạng chuyển động đã được đơn gian hóa bớt để có thể dễ dàng hơn trong việc xây dựng phần cứng cho hệ thống. Ở ứng dụng trên, video đầu vào được phát từ PC truyền qua cổng HDMI tới ZVIK, sau khi xử lý sẽ hiện kết quả lên màn hình. Để áp dụng ứng dụng này vào thực tiến, hệ thống sẽ được phát triển lên bằng cách thay đầu vào bằng hình ảnh từ camera 1080p60 giống như sơ đồ khối dưới đây: Hình 12. Sơ đồ khối phần cứng cho ứng dụng nhận dạng chuyển động trực tiếp từ camera. Thay vì phương pháp cổ điển sử dụng phần mềm để thực hiện các giải thuật tính toán phức tạp và linh động nhưng tốc độ xử lý chậm; hoặc sử dụng phần cứng để thực hiện các giải thuật tính toán tốc độ nhanh nhưng không có khả năng tùy biến theo yêu cầu, ZVIK cung cấp cho người dùng khả năng kết hợp độc đáo giữa phần mềm ứng dụng trên nền tảng Linux và phần cứng thông qua các IP core để một ứng dụng vừa có tộc độ xử lý nhanh của phần PL và cũng như có thể thay đổi linh hoạt nhờ phần PS. Điều này mang lại cho các ứng dụng thời gian thực một bước tiến mới, và tất nhiên, đi kèm với nó là chất lượng hình ảnh/ video được cải thiện lên nhiều lần. Trong tương lai, bộ ZVIK có thể được sử dụng nhiều hơn trong các ứng dụng xử lý video thời gian thực khác. Cụ thể là ứng 12 dụng làm hệ thống camera giám sát chuyển động, nhận dạng và theo dấu khuôn mặt của người đi đường, trong các tòa nhà, văn phòng. Ngoài ra, ZVIK cũng có thể được ứng dụng trong hệ thống automotive (lái xe hơi tự động), các tác vụ cụ thể của camera như là nhận dạng làn đường, biển báo giao thông, cảnh báo các chướng ngại vật trên đường đi, tránh vật cản, hạn chế va chạm với các phương tiện đang lưu thông khác. Ngoài ra, camera cũng có thể được dùng để kiểm soát trạng thái của lái xe như là buồn ngủ, không tỉnh táo khi lái xe Lời cảm ơn: Nghiên cứu này được hổ trợ bởi Đại Học Quốc Gia Thành phố Hồ Chí Minh theo mã số B2015-20-02. TÀI LIỆU THAM KHẢO 1. Jim Beneke, Designing High Pixel - Rate Video Systems with Xilinx FPGAs, 2012, Avnet Inc. 2. Cecile Belleudy et al, “Fall Detection Application on an ARM and FPGA Heterogeneous Computing Platform”, IJAREEIE, vol.3, issue 8, August 2014. 3. Louise H. Crockett. Ross A. Elliot, Martin A. Enderwitz and Robert W. Stewart, The Zynq Book- Embedded Processing with the ARM® Cortex®-A9 on the Xilinx® Zynq®-7000 All Programmable SoC, Department of Electronic and Electrical Engineering, University of Strathclyde, Glasgow, Scotland, UK, 2014. 4. Christopher V. Dobson, An Architecture Study on a Xilinx Zynq Cluster with Software Defined Radio Applications, Virginia Polytechnic Institute and State University, 2014. 5. P. KaewTraKulPong and R. Bowden, “An Improved Adaptive Background Mixture Model for Realtime Tracking with Shadow Detection”, Proc. 2nd European Workshop on Advanced Video Based Surveillance Systems, AVBS01. Sept. 2001, Kluwer Academic Publishers. 6. Sofia Nayak, Shashank Sekhar Pujari, “Moving Object Tracking Application: FPGA And Model Based”, (2015) International Conference on Computing Communication Control and Automation. 7. S. Pleshkova, “Development of Embedded Motion Detection in Thermo Visual System with Audio Visual Interface to Information Networks”, Recent Advances in Systems Science, pp. 143 - 148. 8. Peyman Sabouri, Hamid GholamHosseini and John Collins, Border Detection of Melanoma Skin Lesions on a Single System on Chip (SoC), Auckland University of Technology Auckland, New Zealand. 9. Mohammadsadegh Sadri et al, Energy and Performance Exploration of Accelerator Coherency Port Using Xilinx ZYNQ, Technische Universitat Kaiserslautern. 10. Sheng Yang at al, Adaptive Energy Minimization of Embedded Heterogeneous Systems using Regression-based Learning, University of Southampton and Imperial College, UK. PHỤ LỤC: TỪ VIẾT TẮT [1] AXI: Advanced eXtensible Interface. [2] FPGA: Field-Programmable Gate Array. [3] GUI: Graphical User Interface. [4] IP: Intellectual Property core. [5] ZVIK: Xilinx Zynq®-7000 All Program- mable (AP) SoC Video and Imaging Kit. Ngày nhận bài: 06/6/2016 Biên tập xong: 15/01/2017 Duyệt đăng: 20/01/2017

File đính kèm:

ung_dung_cong_cu_moi_tren_nen_tang_fpga_vao_xu_ly_anh_va_vid.pdf

ung_dung_cong_cu_moi_tren_nen_tang_fpga_vao_xu_ly_anh_va_vid.pdf