Thiết kế kênh đo thông lượng nơtron sử dụng buồng ion hóa KNK-3 tại lò phản ứng hạt nhân Đà Lạt

Kênh đo thông lượng nơtron được thiết kế bao gồm buồng ion hóa (CIC) loại KNK-3 chứa

Boron có bù trừ gamma, hoạt động ở chế độ dòng; bộ biến đổi dòng điện thành tần số (I/F); và khối

đo và kiểm soát thông lượng nơtron (FPGA-WR). Kênh đo cho phép đo và kiểm soát mật độ thông

lượng nơtron từ 1,0x106 đến 1,2x1010 n/cm2.s tương ứng với giá trị công suất lò từ 0,1 đến 120%

công suất danh định 500 kW. Khối đo và kiểm soát dùng FPGA Artix-7 và các thuật toán xử lý tín hiệu

số để đo đạc và tính toán các giá trị về công suất, chu kỳ của lò phản ứng và hình thành các tín hiệu

cảnh báo, sự cố về công suất và chu kỳ. Kênh đo đã được kiểm tra bằng tín hiệu mô phỏng tần số lối

vào và sau đó đã được thử nghiệm trên lò phản ứng để so sánh với một kênh đo sử dụng khối đo và

kiểm soát thông lượng nơtron BPM-107R của hệ điều khiển ASUZ-14R của lò phản ứng hạt nhân Đà

Lạt.

Kết quả so sánh cho thấy, kênh đo thiết kế đáp ứng đầy đủ các yêu cầu về độ chính xác của

các giá trị về công suất và chu kỳ lò phản ứng cũng như đáp ứng tốt về thời gian hình thành các tín

hiệu sự cố về công suất và chu kỳ. Vì vậy, kênh đo có thể được sử dụng để thử nghiệm, nghiên cứu và

đào tạo và khối đo và kiểm soát FPGA-WR có thể thay thế cho khối BPM-107R ở dải làm việc của lò

phản ứng hạt nhân Đà Lạt.

Trang 1

Trang 2

Trang 3

Trang 4

Trang 5

Trang 6

Trang 7

Tóm tắt nội dung tài liệu: Thiết kế kênh đo thông lượng nơtron sử dụng buồng ion hóa KNK-3 tại lò phản ứng hạt nhân Đà Lạt

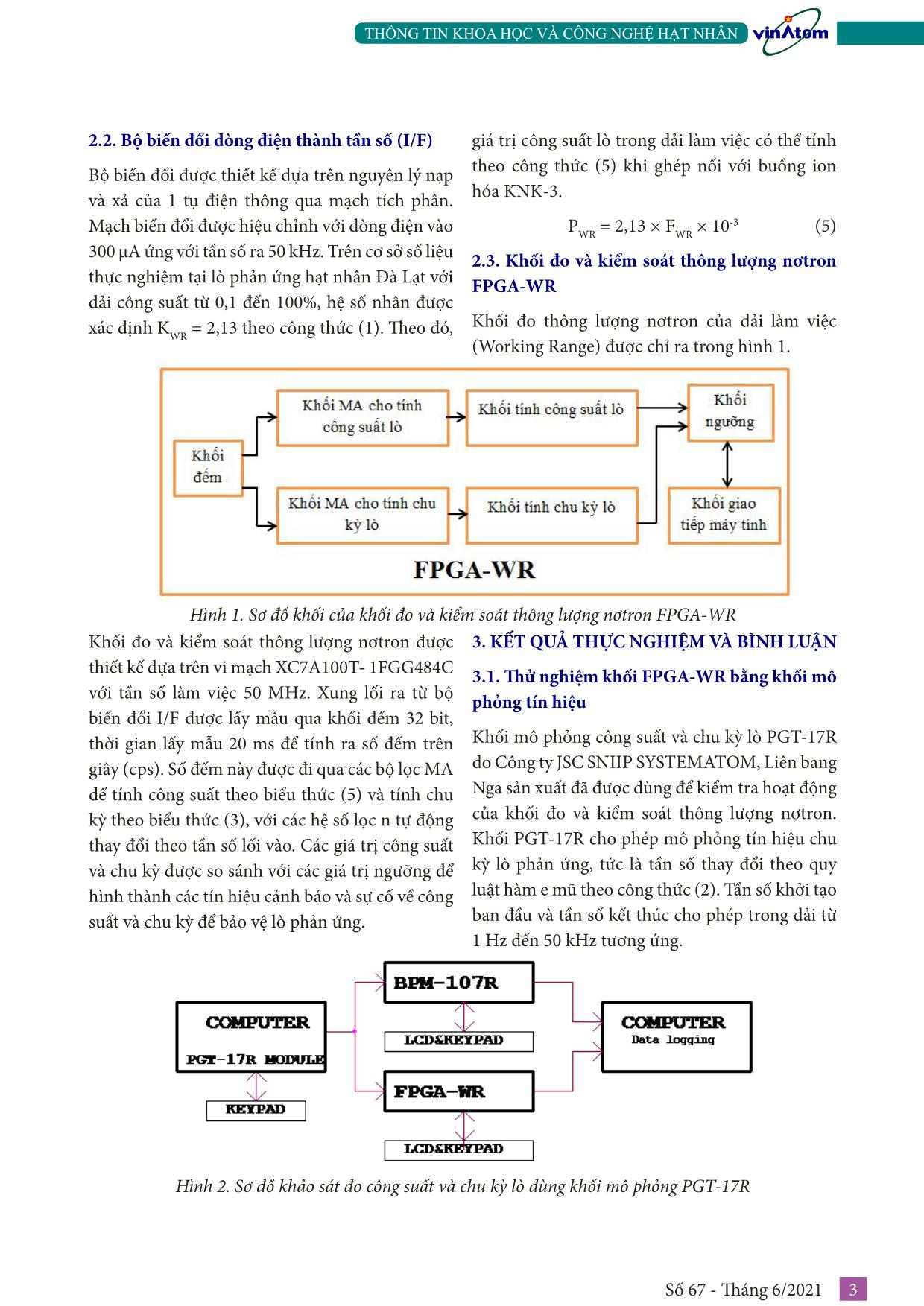

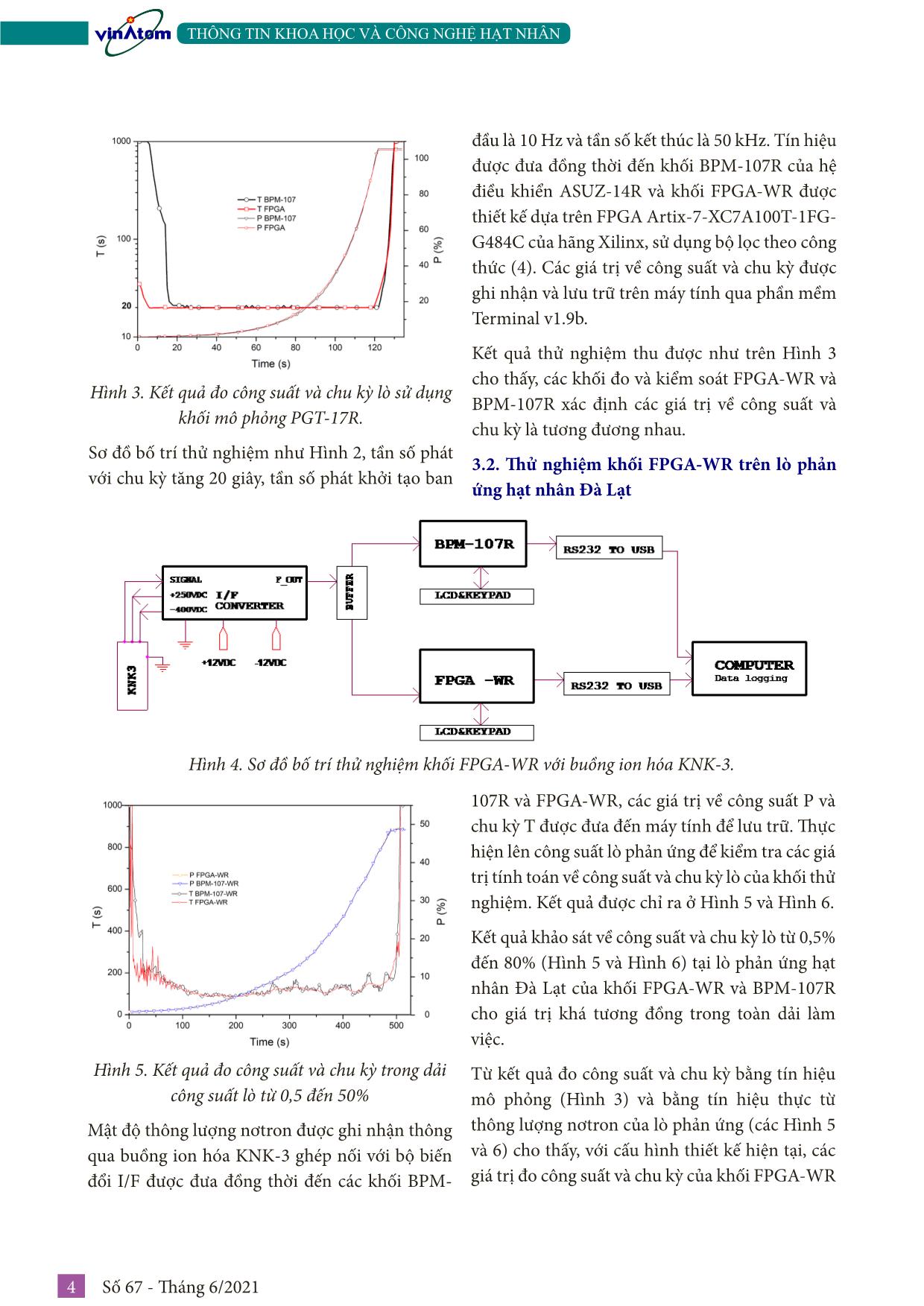

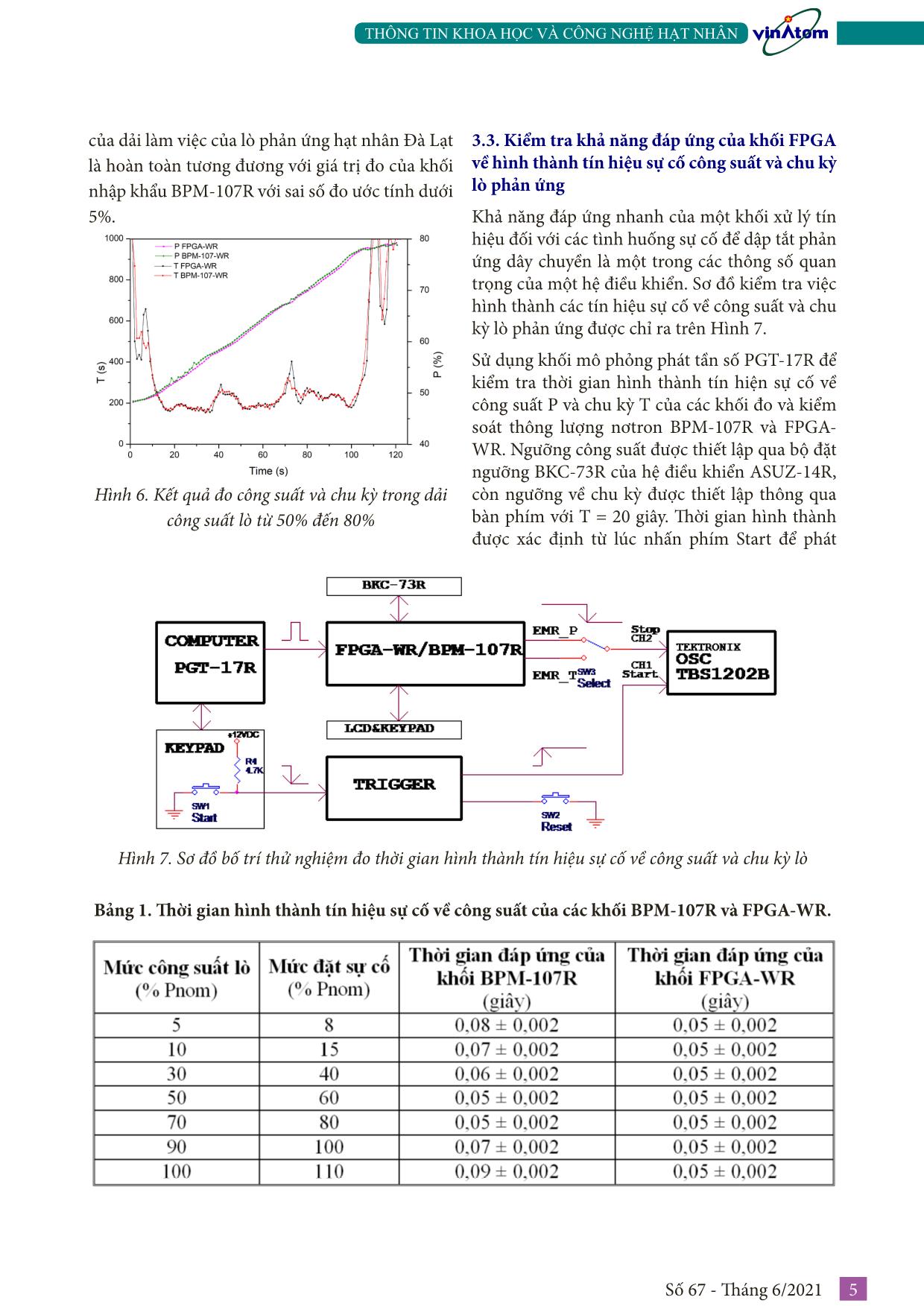

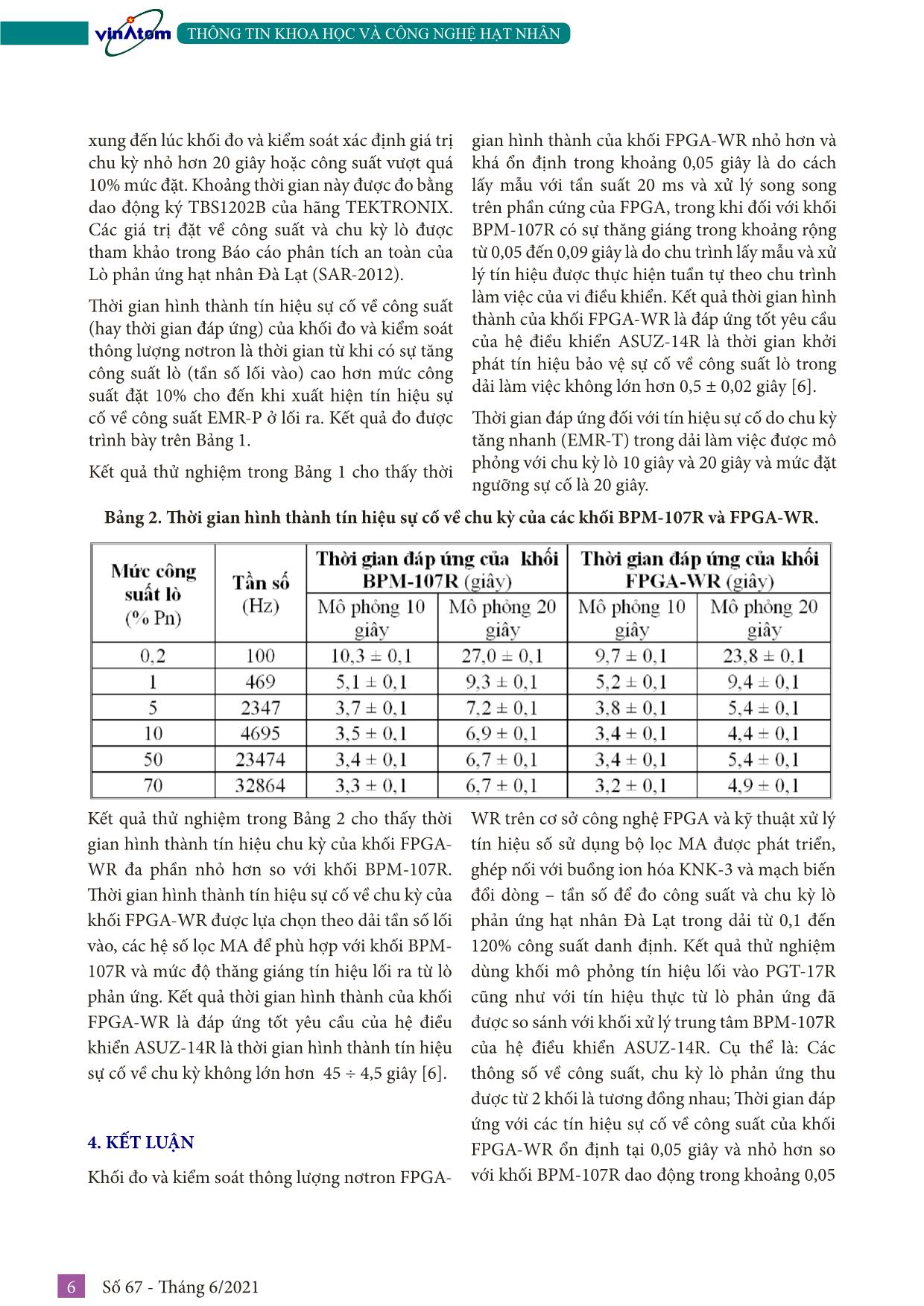

ừa hành theo Trong hệ thống điều khiển và bảo vệ (CPS) lò nguyên lý “chọn 2 từ 3”. Mỗi kênh có nhiệm vụ phản ứng hạt nhân, kênh đo và kiểm soát thông đo và kiểm soát mật độ thông lượng nơtron từ 0 10 2 lượng nơtron (NFME) đóng vai trò quan trọng 1,0×10 đến 1,2×10 n/cm .s và được chia làm 2 0 7 2 trong việc xác định các tham số về công suất, chu dải: dải khởi động từ 1,0×10 đến 1,0×10 n/cm .s 6 10 2 kỳ, các ngưỡng đặt sự cố, để điều khiển và bảo và dải làm việc từ 1,0×10 đến 1,2×10 n/cm .s vệ lò phản ứng. Mật độ thông lượng nơtron được [2]. Với mục đích xây dựng thêm một kênh đo theo dõi thông qua công suất lò (P) và khoảng độc lập với hệ điều khiển để phục vụ công tác thời gian mức công suất thay đổi được biểu thị thử nghiệm, nghiên cứu và đào tạo, bài viết này qua chu kỳ lò phản ứng (T). Từ năm 2007, hệ giới thiệu một kênh đo và kiểm soát thông lượng điều khiển tương tự (AKNP-5A) của lò phản ứng nơtron sử dụng buồng ion hóa KNK-3 ghép nối hạt nhân Đà Lạt (LPƯĐL) đã được thay thế bằng với khối thu nhận và xử lý tín hiệu được thiết kế hệ điều khiển dùng kỹ thuật số (ASUZ-14R), dựa trên FPGA và bộ lọc dịch chuyển trung bình nhưng nguyên tắc hoạt động và các chức năng cơ (MA) để tính toán công suất và chu kỳ lò phản bản vẫn được tuân thủ như hệ cũ trước đây [1], ứng. So sánh với khối xử lý trung tâm BPM-107R công suất và chu kỳ lò được theo dõi bởi ba kênh được thiết kế trên cơ sở vi xử lý 8-bit hiện đang sử Số 67 - Tháng 6/2021 1 THÔNG TIN KHOA HỌC VÀ CÔNG NGHỆ HẠT NHÂN dụng cho hệ điều khiển của LPƯĐL cho thấy, các Công suất của lò phản ứng hạt nhân thay đổi tuân kết quả thử nghiệm thu được bằng tín hiệu mô theo quy luật hàm e mũ theo thời gian như hàm phỏng cũng như bằng tín hiệu thực từ lò phản (2): ứng là khá tương đồng về các tham số như công P = P × et/T (2) suất, chu kỳ lò phản ứng và thời gian hình thành (t) 0 các tín hiệu sự cố về công suất và chu kỳ trong Chu kỳ lò phản ứng hạt nhân T được định nghĩa dải làm việc. Vì vậy, khối đo và kiểm soát thông là khoảng thời gian mà mật độ thông lượng lượng nơtron FPGA-WR với thuật toán xử lý tín nơtron (công suất lò) tăng lên hoặc giảm đi e lần hiệu số có thể thay thế cho khối xử lý trung tâm (e = 2,718). Vì tần số lối ra từ bộ biến đổi I/F tỷ lệ BPM-107R thuộc kênh đo NFME để kiểm soát lò với công suất lò, từ (2) ta xác định được chu kỳ T phản ứng trong dải làm việc với cấu hình thiết kế bằng biểu thức (3) dưới đây [3]. hiện tại và có thể mở rộng ra cả dải khởi động của (3) hệ điều khiển và bảo vệ lò phản ứng hạt nhân Đà Lạt. Khi đó, nếu được ghép nối với hệ điều khiển, Trong đó Fk-1, Fk là thứ tự (k-1) và k trong quá các tín hiệu về sự cố công suất và chu kỳ sẽ đưa trình lấy mẫu tần số từ lối ra của bộ biến đổi I/F, đến hệ thừa hành để đưa lò về trạng thái dưới tới ∆t là thời gian lấy mẫu. Từ mẫu số của (3) cho hạn bằng việc thả rơi các thanh hấp thụ nơtron thấy xu hướng tăng (chu kỳ dương) và xu hướng vào vùng hoạt. giảm (chu kỳ âm) về công suất, mà trong tính toán nếu giá trị chu kỳ lớn hơn 999 giây được xem là vô cùng. Trong thực tế, các quá trình vật lý trong 2. PHƯƠNG PHÁP VÀ THIẾT KẾ lò phản ứng được phản ánh thông qua tín hiệu từ 2.1. Phương pháp xác định giá trị công suất và bộ biến đổi, đặc biệt các thăng giáng lớn thường chu kỳ lò phản ứng xảy ra ở số đếm thấp nên các bộ lọc dịch chuyển trung bình (MA) được sử dụng để xác định giá trị Buồng ion hóa KNK-3 chứa Boron, để ghi nhận thực. Bộ lọc MA hoạt động như một bộ lọc tần nơtron và có khả năng bù trừ gamma, đã được sử số hữu hạn, được sử dụng để xác định xu hướng dụng cho dải năng lượng của hệ điều khiển tương tăng hoặc giảm về công suất hay chu kỳ lò phản tự AKNP-5A. Buồng được đặt trong kênh khô kín ứng. Khi thực hiện các phép toán lấy trung bình, nước nằm phía ngoài vùng hoạt, với thông lượng một giá trị tần số hiện hành được cập nhật đến nơtron tại vị trí đặt buồng nhỏ hơn 3 đến 4 bậc một mảng dữ liệu và giá trị tần số cũ sẽ bị loại bỏ so với thông lượng tại trung tâm vùng hoạt của lò theo công thức (4): phản ứng. Dòng điện lối ra của KNK-3 tỷ lệ với mật độ thông lượng nơtron tại vị trí đặt buồng. (4) Tín hiệu dòng từ lối ra của buồng được biến đổi thành tần số FWR, sau đó đưa đến khối đo và kiểm Trong đó là giá trị trung bình hiện hành, là giá trị soát công suất FPGA-WR, nên công suất của lò trung bình trước đó, là tần số hiện hành, là tần số phản ứng hạt nhân Đà Lạt tại dải làm việc được ở vị trí thứ n, với n là số điểm lấy trung bình. Giá tính theo công thức (1): trị n sẽ được thay đổi trong quá trình hoạt động -3 tùy theo mức độ thăng giáng và giá trị tần số lấy PWR = KWR × FWR × 10 (1) mẫu hiện hành, đó là ưu điểm của kỹ thuật xử lý Trong đó P là công suất lò phản ứng, K là hệ WR WR tín hiệu số và FPGA so với kỹ thuật sử dụng vi xử số nhân. lý với chu trình làm việc tuần tự đã định trước. 2 Số 67 - Tháng 6/2021 THÔNG TIN KHOA HỌC VÀ CÔNG NGHỆ HẠT NHÂN 2.2. Bộ biến đổi dòng điện thành tần số (I/F) giá trị công suất lò trong dải làm việc có thể tính theo công thức (5) khi ghép nối với buồng ion Bộ biến đổi được thiết kế dựa trên nguyên lý nạp hóa KNK-3. và xả của 1 tụ điện thông qua mạch tích phân. -3 Mạch biến đổi được hiệu chỉnh với dòng điện vào PWR = 2,13 × FWR × 10 (5) 300 µA ứng với tần số ra 50 kHz. Trên cơ sở số liệu 2.3. Khối đo và kiểm soát thông lượng nơtron thực nghiệm tại lò phản ứng hạt nhân Đà Lạt với FPGA-WR dải công suất từ 0,1 đến 100%, hệ số nhân được Khối đo thông lượng nơtron của dải làm việc xác định KWR = 2,13 theo công thức (1). Theo đó, (Working Range) được chỉ ra trong hình 1. Hình 1. Sơ đồ khối của khối đo và kiểm soát thông lượng nơtron FPGA-WR Khối đo và kiểm soát thông lượng nơtron được 3. KẾT QUẢ THỰC NGHIỆM VÀ BÌNH LUẬN thiết kế dựa trên vi mạch XC7A100T- 1FGG484C 3.1. Thử nghiệm khối FPGA-WR bằng khối mô với tần số làm việc 50 MHz. Xung lối ra từ bộ phỏng tín hiệu biến đổi I/F được lấy mẫu qua khối đếm 32 bit, thời gian lấy mẫu 20 ms để tính ra số đếm trên Khối mô phỏng công suất và chu kỳ lò PGT-17R giây (cps). Số đếm này được đi qua các bộ lọc MA do Công ty JSC SNIIP SYSTEMATOM, Liên bang để tính công suất theo biểu thức (5) và tính chu Nga sản xuất đã được dùng để kiểm tra hoạt động kỳ theo biểu thức (3), với các hệ số lọc n tự động của khối đo và kiểm soát thông lượng nơtron. thay đổi theo tần số lối vào. Các giá trị công suất Khối PGT-17R cho phép mô phỏng tín hiệu chu và chu kỳ được so sánh với các giá trị ngưỡng để kỳ lò phản ứng, tức là tần số thay đổi theo quy hình thành các tín hiệu cảnh báo và sự cố về công luật hàm e mũ theo công thức (2). Tần số khởi tạo suất và chu kỳ để bảo vệ lò phản ứng. ban đầu và tần số kết thúc cho phép trong dải từ 1 Hz đến 50 kHz tương ứng. Hình 2. Sơ đồ khảo sát đo công suất và chu kỳ lò dùng khối mô phỏng PGT-17R Số 67 - Tháng 6/2021 3 THÔNG TIN KHOA HỌC VÀ CÔNG NGHỆ HẠT NHÂN đầu là 10 Hz và tần số kết thúc là 50 kHz. Tín hiệu được đưa đồng thời đến khối BPM-107R của hệ điều khiển ASUZ-14R và khối FPGA-WR được thiết kế dựa trên FPGA Artix-7-XC7A100T-1FG- G484C của hãng Xilinx, sử dụng bộ lọc theo công thức (4). Các giá trị về công suất và chu kỳ được ghi nhận và lưu trữ trên máy tính qua phần mềm Terminal v1.9b. Kết quả thử nghiệm thu được như trên Hình 3 cho thấy, các khối đo và kiểm soát FPGA-WR và Hình 3. Kết quả đo công suất và chu kỳ lò sử dụng BPM-107R xác định các giá trị về công suất và khối mô phỏng PGT-17R. chu kỳ là tương đương nhau. Sơ đồ bố trí thử nghiệm như Hình 2, tần số phát 3.2. Thử nghiệm khối FPGA-WR trên lò phản với chu kỳ tăng 20 giây, tần số phát khởi tạo ban ứng hạt nhân Đà Lạt Hình 4. Sơ đồ bố trí thử nghiệm khối FPGA-WR với buồng ion hóa KNK-3. 107R và FPGA-WR, các giá trị về công suất P và chu kỳ T được đưa đến máy tính để lưu trữ. Thực hiện lên công suất lò phản ứng để kiểm tra các giá trị tính toán về công suất và chu kỳ lò của khối thử nghiệm. Kết quả được chỉ ra ở Hình 5 và Hình 6. Kết quả khảo sát về công suất và chu kỳ lò từ 0,5% đến 80% (Hình 5 và Hình 6) tại lò phản ứng hạt nhân Đà Lạt của khối FPGA-WR và BPM-107R cho giá trị khá tương đồng trong toàn dải làm việc. Hình 5. Kết quả đo công suất và chu kỳ trong dải Từ kết quả đo công suất và chu kỳ bằng tín hiệu công suất lò từ 0,5 đến 50% mô phỏng (Hình 3) và bằng tín hiệu thực từ Mật độ thông lượng nơtron được ghi nhận thông thông lượng nơtron của lò phản ứng (các Hình 5 qua buồng ion hóa KNK-3 ghép nối với bộ biến và 6) cho thấy, với cấu hình thiết kế hiện tại, các đổi I/F được đưa đồng thời đến các khối BPM- giá trị đo công suất và chu kỳ của khối FPGA-WR 4 Số 67 - Tháng 6/2021 THÔNG TIN KHOA HỌC VÀ CÔNG NGHỆ HẠT NHÂN của dải làm việc của lò phản ứng hạt nhân Đà Lạt 3.3. Kiểm tra khả năng đáp ứng của khối FPGA là hoàn toàn tương đương với giá trị đo của khối về hình thành tín hiệu sự cố công suất và chu kỳ nhập khẩu BPM-107R với sai số đo ước tính dưới lò phản ứng 5%. Khả năng đáp ứng nhanh của một khối xử lý tín hiệu đối với các tình huống sự cố để dập tắt phản ứng dây chuyền là một trong các thông số quan trọng của một hệ điều khiển. Sơ đồ kiểm tra việc hình thành các tín hiệu sự cố về công suất và chu kỳ lò phản ứng được chỉ ra trên Hình 7. Sử dụng khối mô phỏng phát tần số PGT-17R để kiểm tra thời gian hình thành tín hiện sự cố về công suất P và chu kỳ T của các khối đo và kiểm soát thông lượng nơtron BPM-107R và FPGA- WR. Ngưỡng công suất được thiết lập qua bộ đặt ngưỡng BKC-73R của hệ điều khiển ASUZ-14R, Hình 6. Kết quả đo công suất và chu kỳ trong dải còn ngưỡng về chu kỳ được thiết lập thông qua công suất lò từ 50% đến 80% bàn phím với T = 20 giây. Thời gian hình thành được xác định từ lúc nhấn phím Start để phát Hình 7. Sơ đồ bố trí thử nghiệm đo thời gian hình thành tín hiệu sự cố về công suất và chu kỳ lò Bảng 1. Thời gian hình thành tín hiệu sự cố về công suất của các khối BPM-107R và FPGA-WR. Số 67 - Tháng 6/2021 5 THÔNG TIN KHOA HỌC VÀ CÔNG NGHỆ HẠT NHÂN xung đến lúc khối đo và kiểm soát xác định giá trị gian hình thành của khối FPGA-WR nhỏ hơn và chu kỳ nhỏ hơn 20 giây hoặc công suất vượt quá khá ổn định trong khoảng 0,05 giây là do cách 10% mức đặt. Khoảng thời gian này được đo bằng lấy mẫu với tần suất 20 ms và xử lý song song dao động ký TBS1202B của hãng TEKTRONIX. trên phần cứng của FPGA, trong khi đối với khối Các giá trị đặt về công suất và chu kỳ lò được BPM-107R có sự thăng giáng trong khoảng rộng tham khảo trong Báo cáo phân tích an toàn của từ 0,05 đến 0,09 giây là do chu trình lấy mẫu và xử Lò phản ứng hạt nhân Đà Lạt (SAR-2012). lý tín hiệu được thực hiện tuần tự theo chu trình làm việc của vi điều khiển. Kết quả thời gian hình Thời gian hình thành tín hiệu sự cố về công suất thành của khối FPGA-WR là đáp ứng tốt yêu cầu (hay thời gian đáp ứng) của khối đo và kiểm soát của hệ điều khiển ASUZ-14R là thời gian khởi thông lượng nơtron là thời gian từ khi có sự tăng phát tín hiệu bảo vệ sự cố về công suất lò trong công suất lò (tần số lối vào) cao hơn mức công dải làm việc không lớn hơn 0,5 ± 0,02 giây [6]. suất đặt 10% cho đến khi xuất hiện tín hiệu sự cố về công suất EMR-P ở lối ra. Kết quả đo được Thời gian đáp ứng đối với tín hiệu sự cố do chu kỳ trình bày trên Bảng 1. tăng nhanh (EMR-T) trong dải làm việc được mô phỏng với chu kỳ lò 10 giây và 20 giây và mức đặt Kết quả thử nghiệm trong Bảng 1 cho thấy thời ngưỡng sự cố là 20 giây. Bảng 2. Thời gian hình thành tín hiệu sự cố về chu kỳ của các khối BPM-107R và FPGA-WR. Kết quả thử nghiệm trong Bảng 2 cho thấy thời WR trên cơ sở công nghệ FPGA và kỹ thuật xử lý gian hình thành tín hiệu chu kỳ của khối FPGA- tín hiệu số sử dụng bộ lọc MA được phát triển, WR đa phần nhỏ hơn so với khối BPM-107R. ghép nối với buồng ion hóa KNK-3 và mạch biến Thời gian hình thành tín hiệu sự cố về chu kỳ của đổi dòng – tần số để đo công suất và chu kỳ lò khối FPGA-WR được lựa chọn theo dải tần số lối phản ứng hạt nhân Đà Lạt trong dải từ 0,1 đến vào, các hệ số lọc MA để phù hợp với khối BPM- 120% công suất danh định. Kết quả thử nghiệm 107R và mức độ thăng giáng tín hiệu lối ra từ lò dùng khối mô phỏng tín hiệu lối vào PGT-17R phản ứng. Kết quả thời gian hình thành của khối cũng như với tín hiệu thực từ lò phản ứng đã FPGA-WR là đáp ứng tốt yêu cầu của hệ điều được so sánh với khối xử lý trung tâm BPM-107R khiển ASUZ-14R là thời gian hình thành tín hiệu của hệ điều khiển ASUZ-14R. Cụ thể là: Các sự cố về chu kỳ không lớn hơn 45 ÷ 4,5 giây [6]. thông số về công suất, chu kỳ lò phản ứng thu được từ 2 khối là tương đồng nhau; Thời gian đáp ứng với các tín hiệu sự cố về công suất của khối 4. KẾT LUẬN FPGA-WR ổn định tại 0,05 giây và nhỏ hơn so Khối đo và kiểm soát thông lượng nơtron FPGA- với khối BPM-107R dao động trong khoảng 0,05 6 Số 67 - Tháng 6/2021 THÔNG TIN KHOA HỌC VÀ CÔNG NGHỆ HẠT NHÂN đến 0,09 giây do khả năng uyển chuyển của khối tection System ASUZ-14R of Dalat Nuclear Re- FPGA-WR trong việc thay đổi tần suất lấy mẫu search Reactor, Passport RUNK.506319.004 PS- và xử lý song song kết hợp phần cứng của FPGA E, Chief Designer А. А. Zaikin, 2006. và xử lý tín hiệu số; Thời gian đáp ứng với các tín hiệu sự cố về chu kỳ của 2 khối tương đồng nhau và nằm trong giải 27 đến 4,5 giây. Các giá trị về thời gian đáp ứng với các tín hiệu sứ cố về công suất và chu kỳ của khối FPGA-WR được thiết kế là đáp ứng tốt với yêu cầu về thời gian đáp ứng của hệ điều khiển ASUZ-14R nhập khẩu [6]. Kết quả thu được cho phép kết luận có thể sử dụng kênh đo thông lượng nơtron độc lập với khối đo và kiểm soát thông lượng nơtron FPGA-WR kết nối với buồng ion hóa KNK-3 để phục vụ mục đích thử nghiệm, nghiên cứu và đào tạo và với cấu hình thiết kế hiện tại có thể thay thế cho khối BPM-107R hoạt động ở dải làm việc của lò phản ứng hạt nhân Đà Lạt. Võ Văn Tài, Nguyễn Văn Kiên, Nguyễn Nhị Điền và cộng sự Viện Nghiên cứu hạt nhân TÀI LIỆU THAM KHẢO [1] Complex of Equipment for Control and Protec- tion System ASUZ-14R of Dalat Nuclear Research Reactor, Operating Manual RUNK.506319.004 RE-E, Chief Designer А. А. Zaikin, 2006. [2] Huasheng Xiong, Duo Li, Nuclear reactor doubling time calculation using FIR filter, En- ergy Procedia 39 ( 2013 ) 3 – 11. [3] A digital nuclear reactor control system, E. P. Gytfopoulos, P. M. Coble, 1960. [4] “Moving average” https://en.wikipedia.org/ wiki/Moving_average [5] The Scientist and Engineer’s Guide to Digital Signal Processing, by Steven W. Smith, Chapter 15 “Moving average filters” pp. 277-284, https:// dspguide.com. [6] Complex of Equipment for Control and Pro- Số 67 - Tháng 6/2021 7

File đính kèm:

thiet_ke_kenh_do_thong_luong_notron_su_dung_buong_ion_hoa_kn.pdf

thiet_ke_kenh_do_thong_luong_notron_su_dung_buong_ion_hoa_kn.pdf