Đề cương chi tiết học phần Thiết kế logic mạch số

2. MÔ TẢ HỌC PHẦN

Trang bị cho người học những kiến thức mới về tối thiểu hoá hàm logic, các phương

pháp biểu diễn và thiết kế mạch dãy. Và cuối cùng là phương pháp thiết kế dùng vi mạch

(ROM, PLA, GAL, MUX.)

3. MỤC TIÊU CỦA HỌC PHẦN ĐỐI VỚI NGƯỜI HỌC

Kiến thức

Hiểu được những kiến thức để thiết kế các mạch logic: Mạch tổ hợp, mạch dãy đồng bộ,

mạch dãy không đồng bộ. Thiết kế dùng các vi mạch MSI và LSI.

Kỹ năng

Thiết kế được các mạch tổ hợp cũng như các mạch dãy2

Phẩm chất đạo đức và trách nhiệm

Nghiêm túc, trách nhiệm, chủ động, tích cực, chăm chỉ, cẩn thận

Trang 1

Trang 2

Trang 3

Trang 4

Trang 5

Trang 6

Trang 7

Trang 8

Trang 9

Trang 10

Tải về để xem bản đầy đủ

Bạn đang xem 10 trang mẫu của tài liệu "Đề cương chi tiết học phần Thiết kế logic mạch số", để tải tài liệu gốc về máy hãy click vào nút Download ở trên

Tóm tắt nội dung tài liệu: Đề cương chi tiết học phần Thiết kế logic mạch số

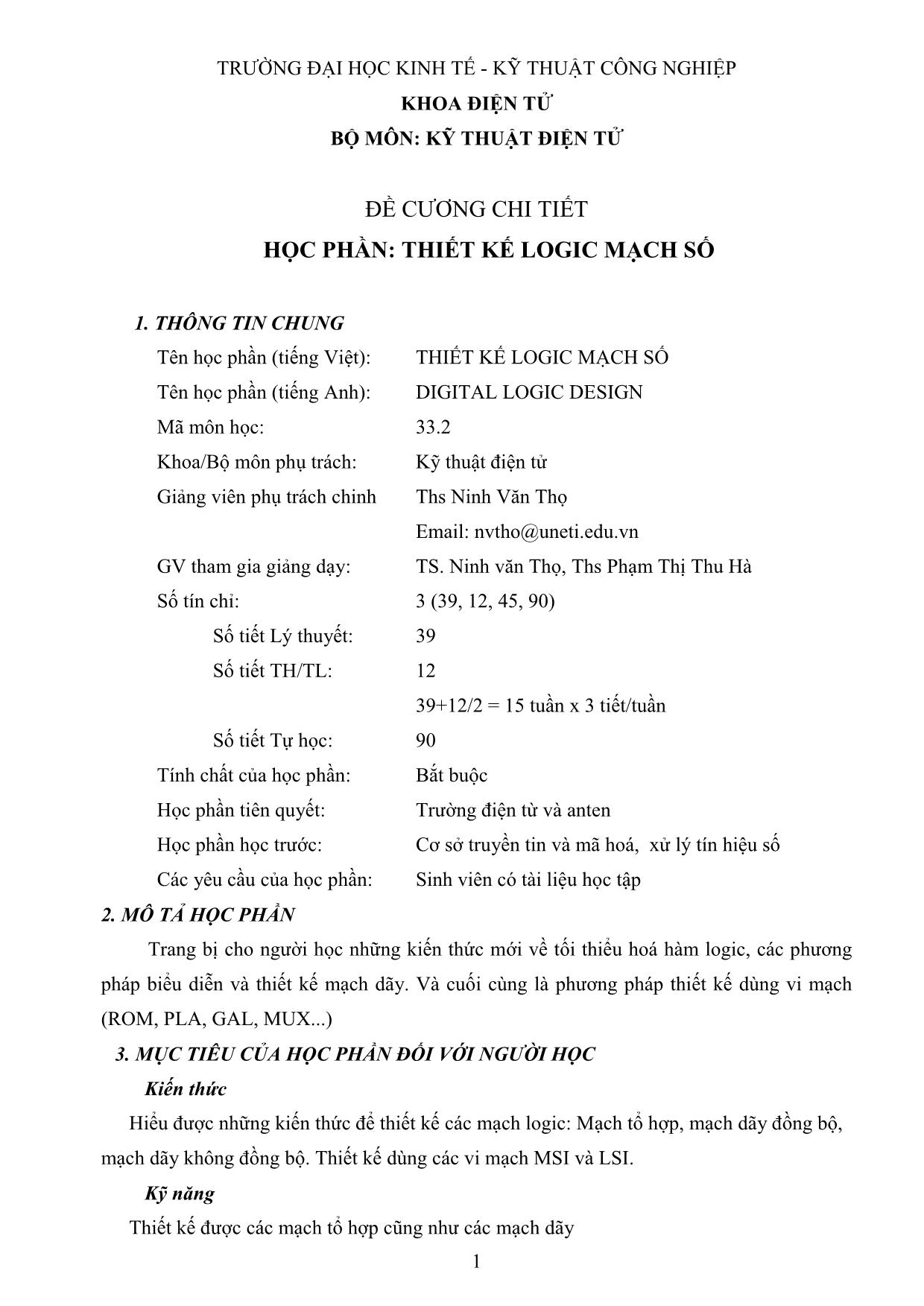

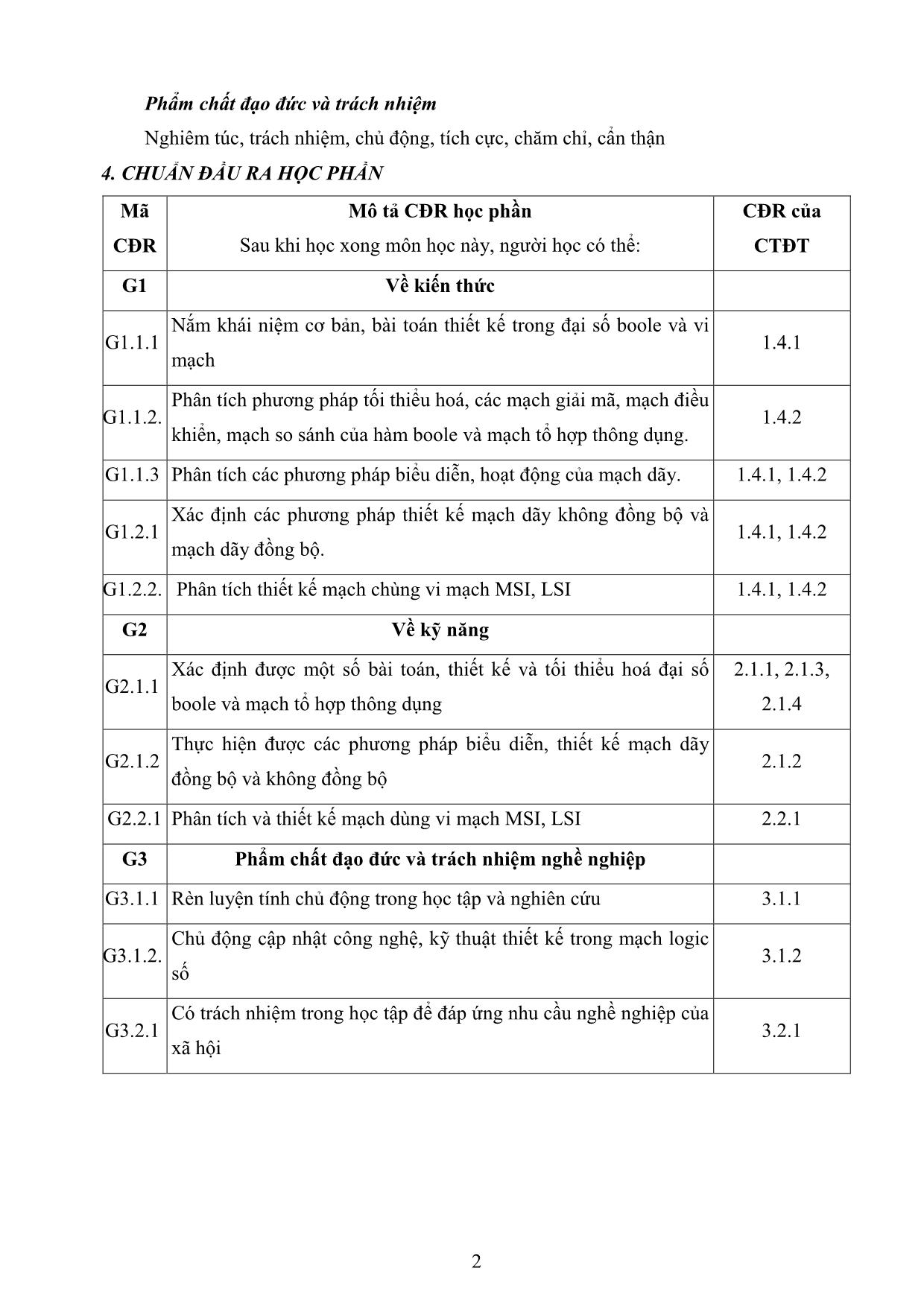

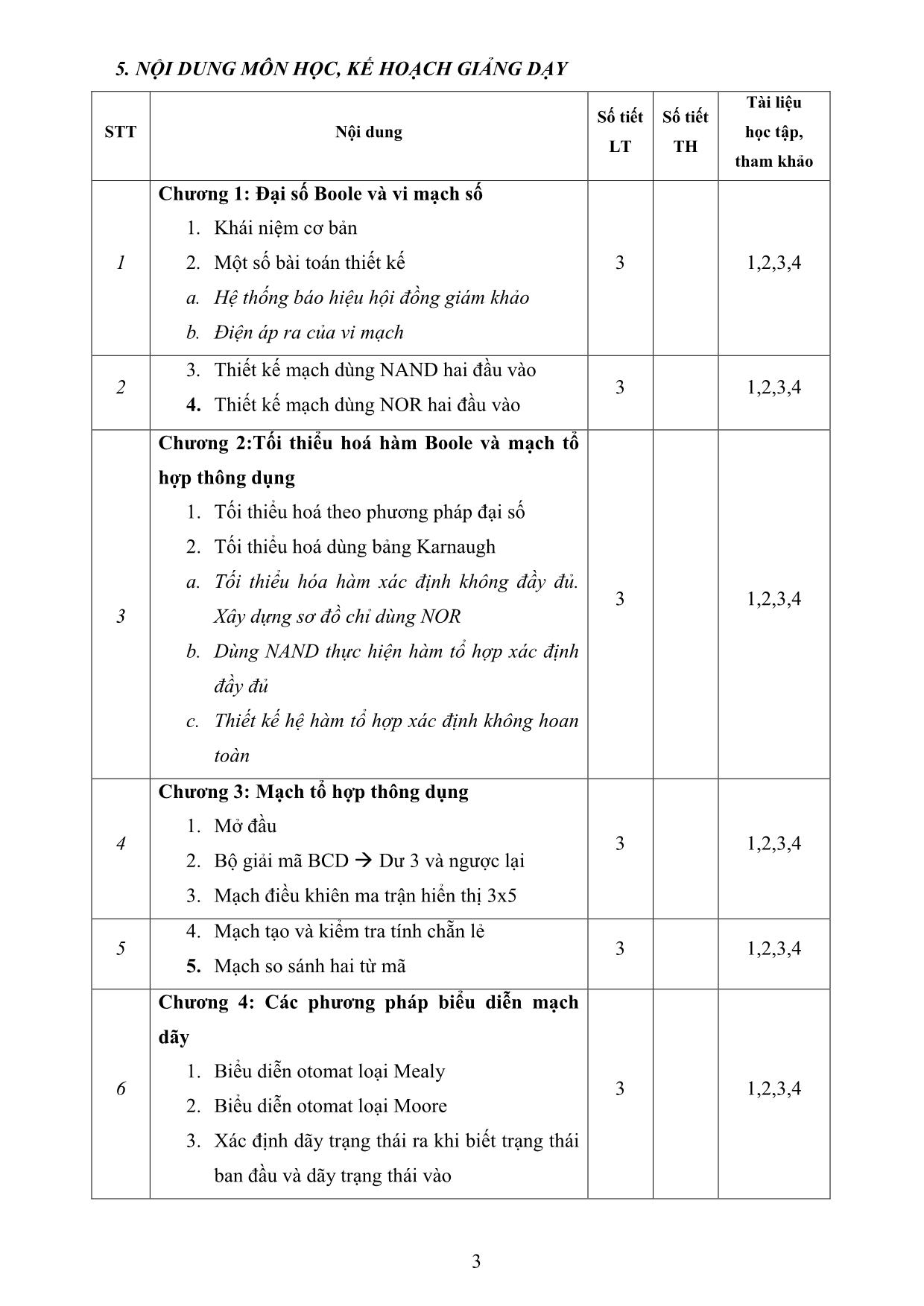

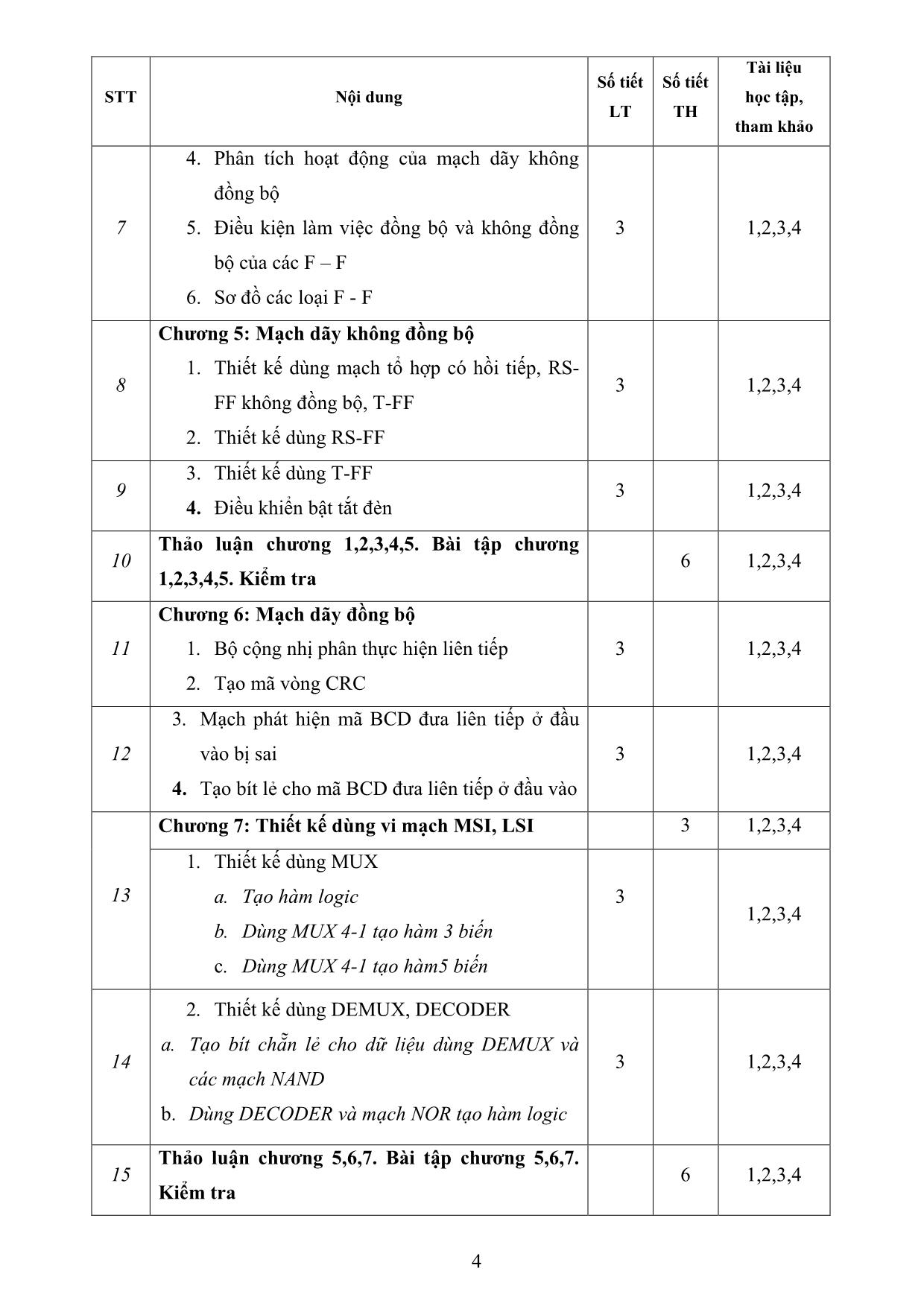

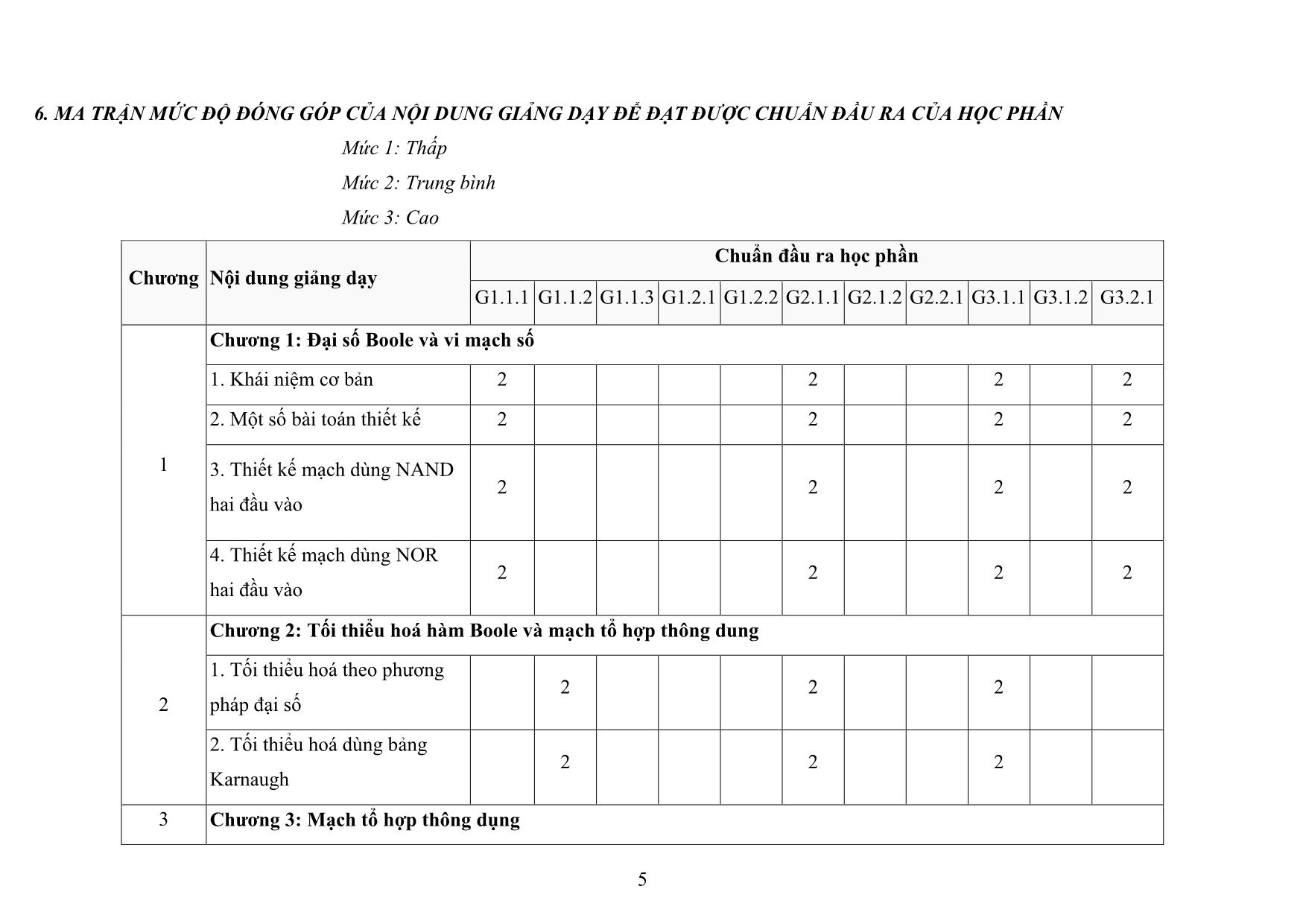

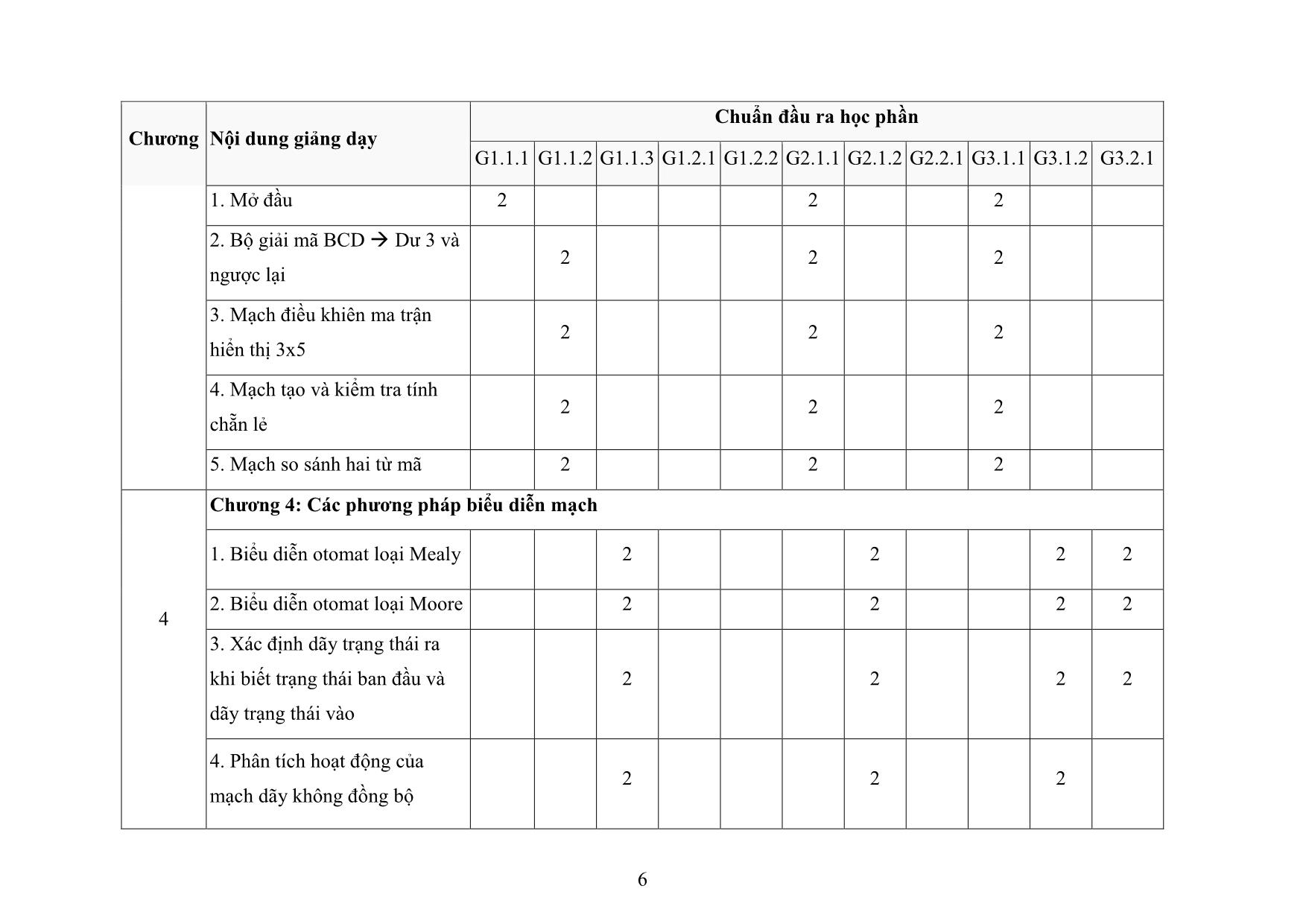

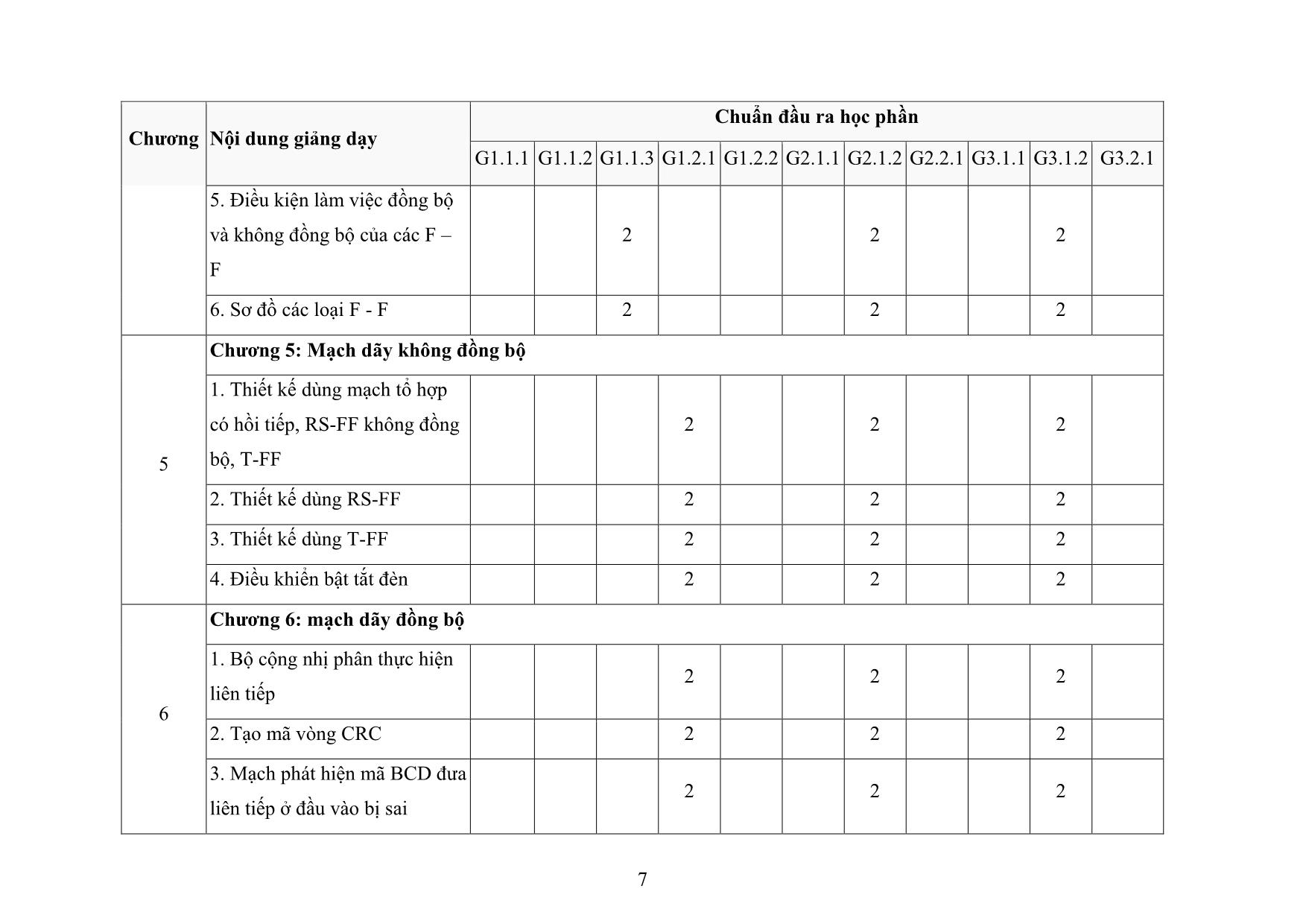

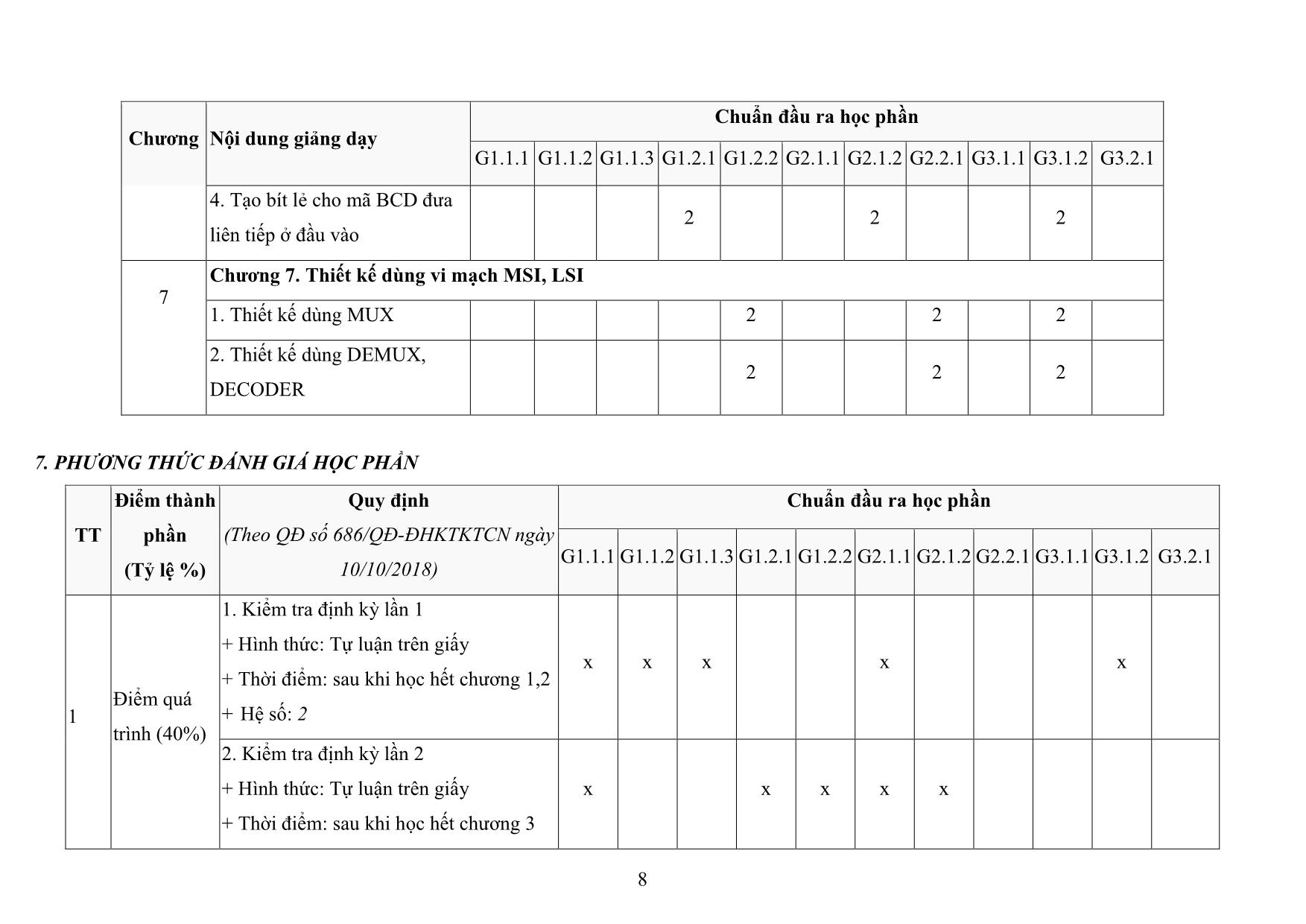

TRƯỜNG ĐẠI HỌC KINH TẾ - KỸ THUẬT CÔNG NGHIỆP KHOA ĐIỆN TỬ BỘ MÔN: KỸ THUẬT ĐIỆN TỬ ĐỀ CƯƠNG CHI TIẾT HỌC PHẦN: THIẾT KẾ LOGIC MẠCH SỐ 1. THÔNG TIN CHUNG Tên học phần (tiếng Việt): THIẾT KẾ LOGIC MẠCH SỐ Tên học phần (tiếng Anh): DIGITAL LOGIC DESIGN Mã môn học: 33.2 Khoa/Bộ môn phụ trách: Kỹ thuật điện tử Giảng viên phụ trách chinh Ths Ninh Văn Thọ Email: nvtho@uneti.edu.vn GV tham gia giảng dạy: TS. Ninh văn Thọ, Ths Phạm Thị Thu Hà Số tín chỉ: 3 (39, 12, 45, 90) Số tiết Lý thuyết: 39 Số tiết TH/TL: 12 39+12/2 = 15 tuần x 3 tiết/tuần Số tiết Tự học: 90 Tính chất của học phần: Bắt buộc Học phần tiên quyết: Trường điện từ và anten Học phần học trước: Cơ sở truyền tin và mã hoá, xử lý tín hiệu số Các yêu cầu của học phần: Sinh viên có tài liệu học tập 2. MÔ TẢ HỌC PHẦN Trang bị cho người học những kiến thức mới về tối thiểu hoá hàm logic, các phương pháp biểu diễn và thiết kế mạch dãy. Và cuối cùng là phương pháp thiết kế dùng vi mạch (ROM, PLA, GAL, MUX...) 3. MỤC TIÊU CỦA HỌC PHẦN ĐỐI VỚI NGƯỜI HỌC Kiến thức Hiểu được những kiến thức để thiết kế các mạch logic: Mạch tổ hợp, mạch dãy đồng bộ, mạch dãy không đồng bộ. Thiết kế dùng các vi mạch MSI và LSI. Kỹ năng Thiết kế được các mạch tổ hợp cũng như các mạch dãy 1 Phẩm chất đạo đức và trách nhiệm Nghiêm túc, trách nhiệm, chủ động, tích cực, chăm chỉ, cẩn thận 4. CHUẨN ĐẦU RA HỌC PHẦN Mã Mô tả CĐR học phần CĐR của CĐR Sau khi học xong môn học này, người học có thể: CTĐT G1 Về kiến thức Nắm khái niệm cơ bản, bài toán thiết kế trong đại số boole và vi G1.1.1 1.4.1 mạch Phân tích phương pháp tối thiểu hoá, các mạch giải mã, mạch điều G1.1.2. 1.4.2 khiển, mạch so sánh của hàm boole và mạch tổ hợp thông dụng. G1.1.3 Phân tích các phương pháp biểu diễn, hoạt động của mạch dãy. 1.4.1, 1.4.2 Xác định các phương pháp thiết kế mạch dãy không đồng bộ và G1.2.1 1.4.1, 1.4.2 mạch dãy đồng bộ. G1.2.2. Phân tích thiết kế mạch chùng vi mạch MSI, LSI 1.4.1, 1.4.2 G2 Về kỹ năng Xác định được một số bài toán, thiết kế và tối thiểu hoá đại số 2.1.1, 2.1.3, G2.1.1 boole và mạch tổ hợp thông dụng 2.1.4 Thực hiện được các phương pháp biểu diễn, thiết kế mạch dãy G2.1.2 2.1.2 đồng bộ và không đồng bộ G2.2.1 Phân tích và thiết kế mạch dùng vi mạch MSI, LSI 2.2.1 G3 Phẩm chất đạo đức và trách nhiệm nghề nghiệp G3.1.1 Rèn luyện tính chủ động trong học tập và nghiên cứu 3.1.1 Chủ động cập nhật công nghệ, kỹ thuật thiết kế trong mạch logic G3.1.2. 3.1.2 số Có trách nhiệm trong học tập để đáp ứng nhu cầu nghề nghiệp của G3.2.1 3.2.1 xã hội 2 5. NỘI DUNG MÔN HỌC, KẾ HOẠCH GIẢNG DẠY Tài liệu Số tiết Số tiết STT Nội dung học tập, LT TH tham khảo Chương 1: Đại số Boole và vi mạch số 1. Khái niệm cơ bản 1 2. Một số bài toán thiết kế 3 1,2,3,4 a. Hệ thống báo hiệu hội đồng giám khảo b. Điện áp ra của vi mạch 3. Thiết kế mạch dùng NAND hai đầu vào 2 3 1,2,3,4 4. Thiết kế mạch dùng NOR hai đầu vào Chương 2:Tối thiểu hoá hàm Boole và mạch tổ hợp thông dụng 1. Tối thiểu hoá theo phương pháp đại số 2. Tối thiểu hoá dùng bảng Karnaugh a. Tối thiểu hóa hàm xác định không đầy đủ. 3 1,2,3,4 3 Xây dựng sơ đồ chỉ dùng NOR b. Dùng NAND thực hiện hàm tổ hợp xác định đầy đủ c. Thiết kế hệ hàm tổ hợp xác định không hoan toàn Chương 3: Mạch tổ hợp thông dụng 1. Mở đầu 4 3 1,2,3,4 2. Bộ giải mã BCD Dư 3 và ngược lại 3. Mạch điều khiên ma trận hiển thị 3x5 4. Mạch tạo và kiểm tra tính chẵn lẻ 5 3 1,2,3,4 5. Mạch so sánh hai từ mã Chương 4: Các phương pháp biểu diễn mạch dãy 1. Biểu diễn otomat loại Mealy 6 3 1,2,3,4 2. Biểu diễn otomat loại Moore 3. Xác định dãy trạng thái ra khi biết trạng thái ban đầu và dãy trạng thái vào 3 Tài liệu Số tiết Số tiết STT Nội dung học tập, LT TH tham khảo 4. Phân tích hoạt động của mạch dãy không đồng bộ 7 5. Điều kiện làm việc đồng bộ và không đồng 3 1,2,3,4 bộ của các F – F 6. Sơ đồ các loại F - F Chương 5: Mạch dãy không đồng bộ 1. Thiết kế dùng mạch tổ hợp có hồi tiếp, RS- 8 3 1,2,3,4 FF không đồng bộ, T-FF 2. Thiết kế dùng RS-FF 3. Thiết kế dùng T-FF 9 3 1,2,3,4 4. Điều khiển bật tắt đèn Thảo luận chương 1,2,3,4,5. Bài tập chương 10 6 1,2,3,4 1,2,3,4,5. Kiểm tra Chương 6: Mạch dãy đồng bộ 11 1. Bộ cộng nhị phân thực hiện liên tiếp 3 1,2,3,4 2. Tạo mã vòng CRC 3. Mạch phát hiện mã BCD đưa liên tiếp ở đầu 12 vào bị sai 3 1,2,3,4 4. Tạo bít lẻ cho mã BCD đưa liên tiếp ở đầu vào Chương 7: Thiết kế dùng vi mạch MSI, LSI 3 1,2,3,4 1. Thiết kế dùng MUX 13 a. Tạo hàm logic 3 1,2,3,4 b. Dùng MUX 4-1 tạo hàm 3 biến c. Dùng MUX 4-1 tạo hàm5 biến 2. Thiết kế dùng DEMUX, DECODER a. Tạo bít chẵn lẻ cho dữ liệu dùng DEMUX và 14 3 1,2,3,4 các mạch NAND b. Dùng DECODER và mạch NOR tạo hàm logic Thảo luận chương 5,6,7. Bài tập chương 5,6,7. 15 6 1,2,3,4 Kiểm tra 4 6. MA TRẬN MỨC ĐỘ ĐÓNG GÓP CỦA NỘI DUNG GIẢNG DẠY ĐỂ ĐẠT ĐƯỢC CHUẨN ĐẦU RA CỦA HỌC PHẦN Mức 1: Thấp Mức 2: Trung bình Mức 3: Cao Chuẩn đầu ra học phần Chương Nội dung giảng dạy G1.1.1 G1.1.2 G1.1.3 G1.2.1 G1.2.2 G2.1.1 G2.1.2 G2.2.1 G3.1.1 G3.1.2 G3.2.1 Chương 1: Đại số Boole và vi mạch số 1. Khái niệm cơ bản 2 2 2 2 2. Một số bài toán thiết kế 2 2 2 2 1 3. Thiết kế mạch dùng NAND 2 2 2 2 hai đầu vào 4. Thiết kế mạch dùng NOR 2 2 2 2 hai đầu vào Chương 2: Tối thiểu hoá hàm Boole và mạch tổ hợp thông dung 1. Tối thiểu hoá theo phương 2 2 2 2 pháp đại số 2. Tối thiểu hoá dùng bảng 2 2 2 Karnaugh 3 Chương 3: Mạch tổ hợp thông dụng 5 Chuẩn đầu ra học phần Chương Nội dung giảng dạy G1.1.1 G1.1.2 G1.1.3 G1.2.1 G1.2.2 G2.1.1 G2.1.2 G2.2.1 G3.1.1 G3.1.2 G3.2.1 1. Mở đầu 2 2 2 2. Bộ giải mã BCD Dư 3 và 2 2 2 ngược lại 3. Mạch điều khiên ma trận 2 2 2 hiển thị 3x5 4. Mạch tạo và kiểm tra tính 2 2 2 chẵn lẻ 5. Mạch so sánh hai từ mã 2 2 2 Chương 4: Các phương pháp biểu diễn mạch 1. Biểu diễn otomat loại Mealy 2 2 2 2 2. Biểu diễn otomat loại Moore 2 2 2 2 4 3. Xác định dãy trạng thái ra khi biết trạng thái ban đầu và 2 2 2 2 dãy trạng thái vào 4. Phân tích hoạt động của 2 2 2 mạch dãy không đồng bộ 6 Chuẩn đầu ra học phần Chương Nội dung giảng dạy G1.1.1 G1.1.2 G1.1.3 G1.2.1 G1.2.2 G2.1.1 G2.1.2 G2.2.1 G3.1.1 G3.1.2 G3.2.1 5. Điều kiện làm việc đồng bộ và không đồng bộ của các F – 2 2 2 F 6. Sơ đồ các loại F - F 2 2 2 Chương 5: Mạch dãy không đồng bộ 1. Thiết kế dùng mạch tổ hợp có hồi tiếp, RS-FF không đồng 2 2 2 5 bộ, T-FF 2. Thiết kế dùng RS-FF 2 2 2 3. Thiết kế dùng T-FF 2 2 2 4. Điều khiển bật tắt đèn 2 2 2 Chương 6: mạch dãy đồng bộ 1. Bộ cộng nhị phân thực hiện 2 2 2 liên tiếp 6 2. Tạo mã vòng CRC 2 2 2 3. Mạch phát hiện mã BCD đưa 2 2 2 liên tiếp ở đầu vào bị sai 7 Chuẩn đầu ra học phần Chương Nội dung giảng dạy G1.1.1 G1.1.2 G1.1.3 G1.2.1 G1.2.2 G2.1.1 G2.1.2 G2.2.1 G3.1.1 G3.1.2 G3.2.1 4. Tạo bít lẻ cho mã BCD đưa 2 2 2 liên tiếp ở đầu vào Chương 7. Thiết kế dùng vi mạch MSI, LSI 7 1. Thiết kế dùng MUX 2 2 2 2. Thiết kế dùng DEMUX, 2 2 2 DECODER 7. PHƯƠNG THỨC ĐÁNH GIÁ HỌC PHẦN Điểm thành Quy định Chuẩn đầu ra học phần TT phần (Theo QĐ số 686/QĐ-ĐHKTKTCN ngày G1.1.1 G1.1.2 G1.1.3 G1.2.1 G1.2.2 G2.1.1 G2.1.2 G2.2.1 G3.1.1 G3.1.2 G3.2.1 (Tỷ lệ %) 10/10/2018) 1. Kiểm tra định kỳ lần 1 + Hình thức: Tự luận trên giấy x x x x x + Thời điểm: sau khi học hết chương 1,2 Điểm quá 1 + Hệ số: 2 trình (40%) 2. Kiểm tra định kỳ lần 2 + Hình thức: Tự luận trên giấy x x x x x + Thời điểm: sau khi học hết chương 3 8 + Hệ số: 2 3. Kiểm tra định kỳ lần 3 + Hình thức: Tự luận trên giấy. x x x + Thời điểm: sau khi học hết chương 4 + Hệ số: 2 4. Kiểm tra thường xuyên + Hình thức: Tham gia thảo luận, kiểm tra 15 phút, hỏi đáp, bài tập trên lớp x x x x x x x x x x x + Số lần: Tối thiểu 1 lần/sinh viên + Hệ số: 1 5. Kiểm tra chuyên cần + Hình thức: Điểm danh theo thời gian tham gia học trên lớp x x x x x x x x x x x + Số lần: 1 lần, vào thời điểm kết thúc học phần + Hệ số: 3 Điểm thi kết + Hình thức: Tự luận trên giấy 2 thúc học + Thời điểm: Theo lịch thi học kỳ x x x x x x x x x phần (60%) + Tính chất: Bắt buộc 9 8. PHƯƠNG PHÁP DẠY VÀ HỌC Giảng viên giới thiệu học phần, tài liệu học tập, tài liệu tham khảo, các địa chỉ website để tìm tư liệu liên quan đến môn học. Nêu nội dung cốt lõi của chương và tổng kết chương, sử dụng bài giảng điện tử và các mô hình giáo cụ trực quan trong giảng dạy. Tập trung hướng d n học, tư vấn học, phản hồi kết quả thảo luận, bài tập lớn, kết quả kiểm tra và các nội dung l thuyết chính m i chương. Giảng viên sẽ mô tả các hoạt động thực tế trong các hệ thống cần lập trình trong đời sống, khoa học và công nghệ. Ứng dụng của các hệ thống lập trình từ đơn giản đến phức tạp. Các phương pháp giảng dạy có thể áp dụng: Phương pháp thuyết trình; Phương pháp thảo luận nhóm; Phương pháp minh họa; Phương pháp miêu tả, làm m u. Sinh viên chuẩn bị bài từng chương, làm bài tập đầy đủ, trau dồi kỹ năng làm việc nhóm để chuẩn bị bài thảo luận. Trong quá trình học tập, sinh viên được khuyến khích đặt câu hỏi phản biện, trình bày quan điểm, các tưởng sáng tạo mới dưới nhiều hình thức khác nhau. 9. QUY ĐỊNH CỦA HỌC PHẦN 9.1. Quy định về tham dự lớp học Sinh viên/học viên có trách nhiệm tham dự đầy đủ các buổi học. Trong trường hợp nghỉ học do lý do bất khả kháng thì phải có giấy tờ chứng minh đầy đủ và hợp lý. Sinh viên vắng quá 50% buổi học dù có l do hay không có l do đều bị coi như không hoàn thành khóa học và phải đăng k học lại vào học kỳ sau. Tham dự các tiết học lý thuyết Thực hiện đầy đủ các bài tập được giao trong cuốn sách tài liệu học tập Kỹ thuật lập trình. Tham dự kiểm tra giữa học kỳ Tham dự thi kết thúc học phần Chủ động tổ chức thực hiện giờ tự học 9.2. Quy định về hành vi lớp học Học phần được thực hiện trên nguyên tắc tôn trọng người học và người dạy. Mọi hành vi làm ảnh hưởng đến quá trình dạy và học đều bị nghiêm cấm. Sinh viên phải đi học đúng giờ quy định. Sinh viên đi trễ quá 15 phút sau khi giờ học bắt đầu sẽ không được tham dự buổi học. Tuyệt đối không làm ồn, gây ảnh hưởng đến người khác trong quá trình học. 10 Tuyệt đối không được ăn uống, nhai kẹo cao su, sử dụng các thiết bị như điện thoại, máy nghe nhạc trong giờ học. 10. TÀI LIỆU HỌC TẬP, THAM KHẢO 10.1. Tài liệu học tập: [1]. Nguyễn Thu Vân, Thiết kế logic mạch số, NXB Khoa học Kỹ thuật, năm 2005 10.2. Tài liệu tham khảo: [2]. Nguyễn Thuý Vân, Kỹ thuật số, NXB Khoa học Kỹ thuật, năm 2006 [3]. Huỳnh Đắc Thắng, Kỹ Thuật số thực hành, NXB Khoa học và kỹ thuật, 2006 [4]. Vũ Đức Thọ, Đ Xuân Thụ, Cơ sở kỹ thuật điện tử số, NXB Giáo dục, 2003 11. HƯỚNG DẪN THỰC HIỆN Các Khoa, Bộ môn phổ biến đề cương chi tiết cho toàn thể giáo viên thực hiện. Giảng viên phổ biến đề cương chi tiết cho sinh viên vào buổi học đầu tiên của học phần. Giảng viên thực hiện theo đúng đề cương chi tiết đã được duyệt. Hà Nội, ngày . tháng . năm 2018 Trưởng khoa Trưởng bộ môn Người biên soạn (Ký và ghi rõ họ tên) (Ký và ghi rõ họ tên) (Ký và ghi rõ họ tên) Bùi Huy Hải Nguyễn Mai Anh 11

File đính kèm:

de_cuong_chi_tiet_hoc_phan_thiet_ke_logic_mach_so.pdf

de_cuong_chi_tiet_hoc_phan_thiet_ke_logic_mach_so.pdf