Bài giảng Thiết kế hệ thống nhúng - Chương 2: Cấu trúc phần cứng hệ thống nhúng - Bài 6: Công nghệ IC

Tổng quan

• Cấu trúc IC

• Công nghệ IC chức năng chung (VLSI)

• Công nghệ IC chức năng chuyên biệt (ASIC)

• Công nghệ IC có thể lập trình (PLD)3

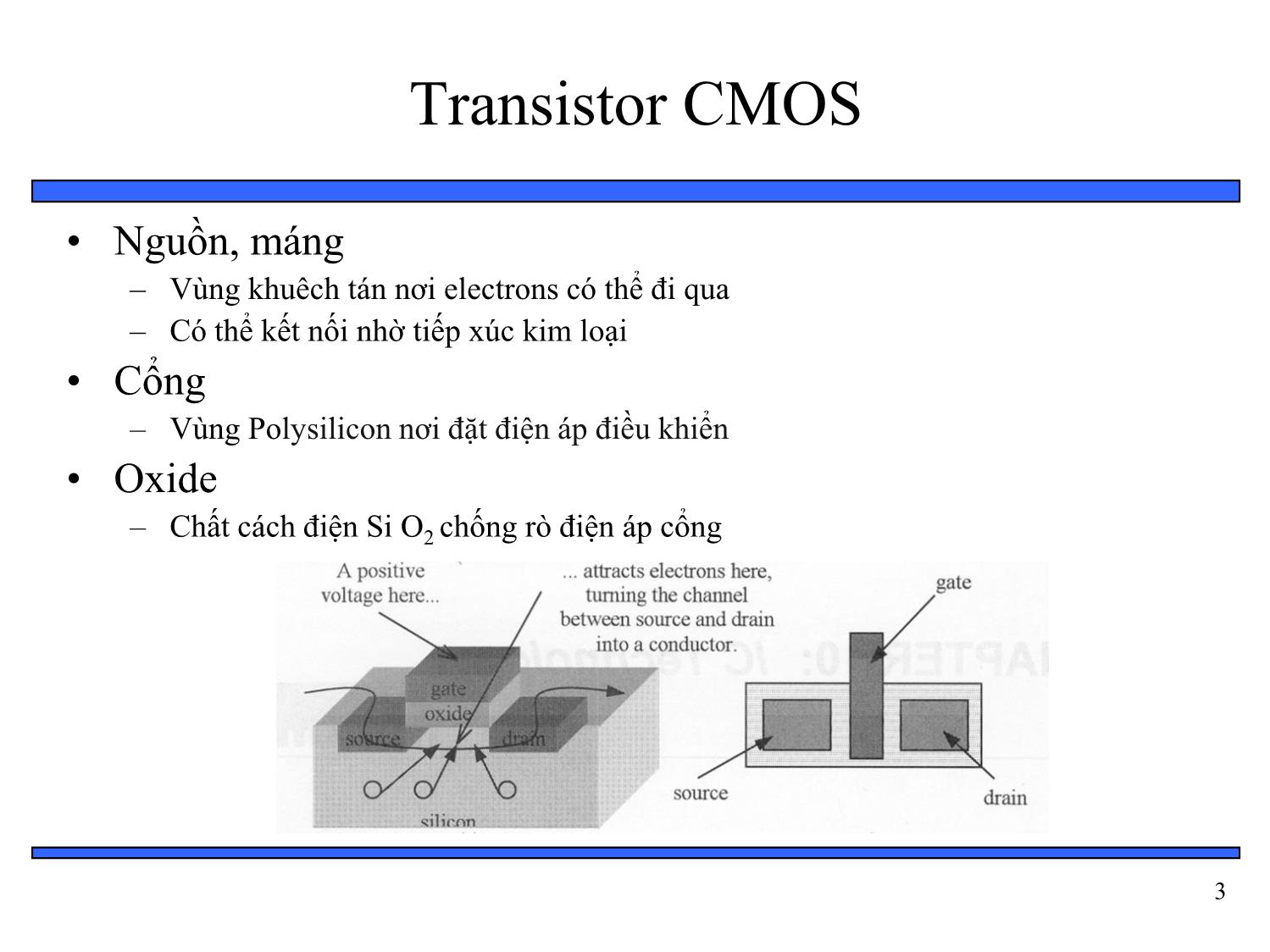

Transistor CMOS

• Nguồn, máng

– Vùng khuêch tán nơi electrons có thể đi qua

– Có thể kết nối nhờ tiếp xúc kim loại

• Cổng

– Vùng Polysilicon nơi đặt điện áp điều khiển

• Oxide

– Chất cách điện Si O2 chống rò điện áp cổng

Trang 1

Trang 2

Trang 3

Trang 4

Trang 5

Trang 6

Trang 7

Trang 8

Trang 9

Trang 10

Tải về để xem bản đầy đủ

Bạn đang xem 10 trang mẫu của tài liệu "Bài giảng Thiết kế hệ thống nhúng - Chương 2: Cấu trúc phần cứng hệ thống nhúng - Bài 6: Công nghệ IC", để tải tài liệu gốc về máy hãy click vào nút Download ở trên

Tóm tắt nội dung tài liệu: Bài giảng Thiết kế hệ thống nhúng - Chương 2: Cấu trúc phần cứng hệ thống nhúng - Bài 6: Công nghệ IC

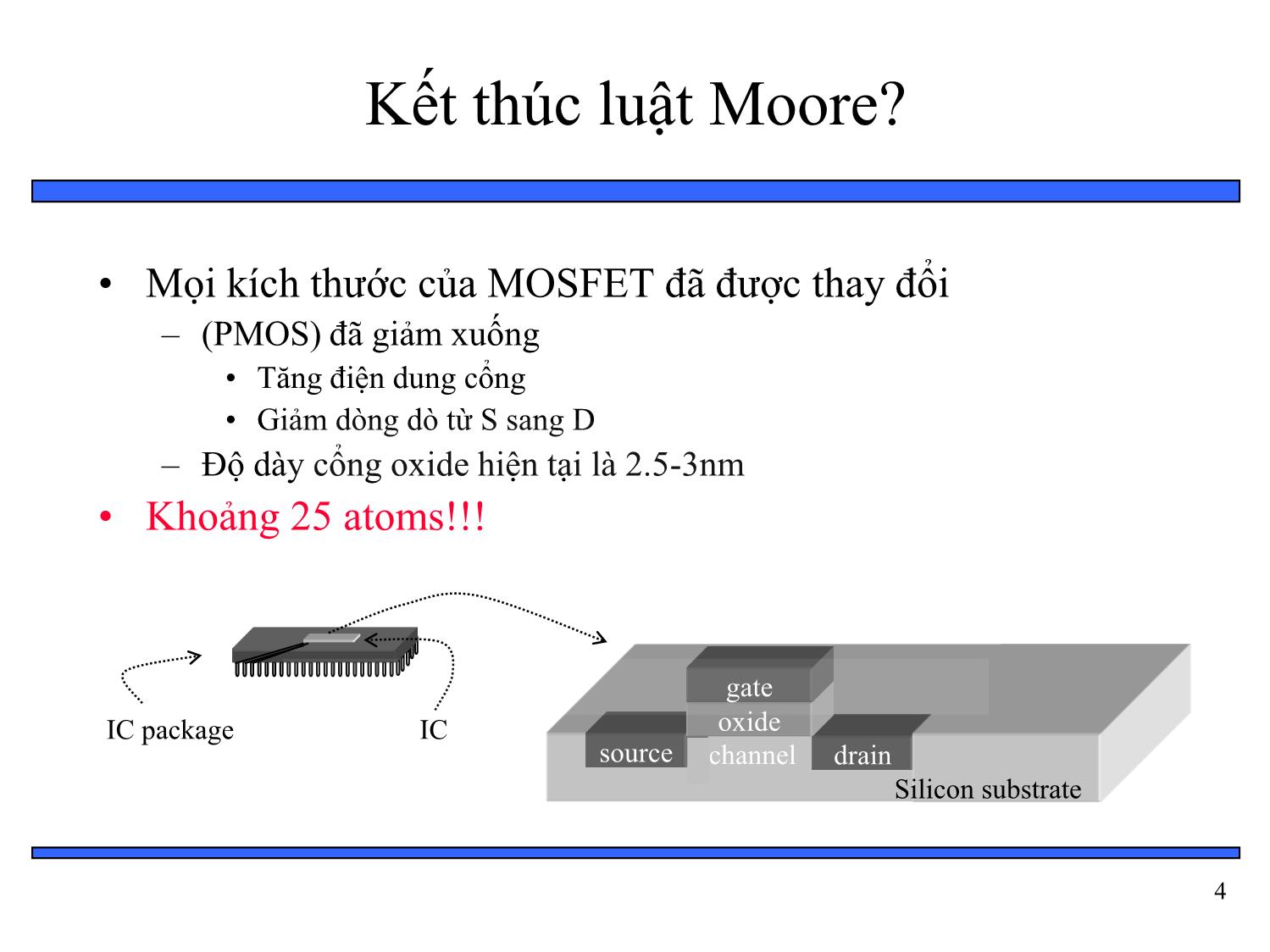

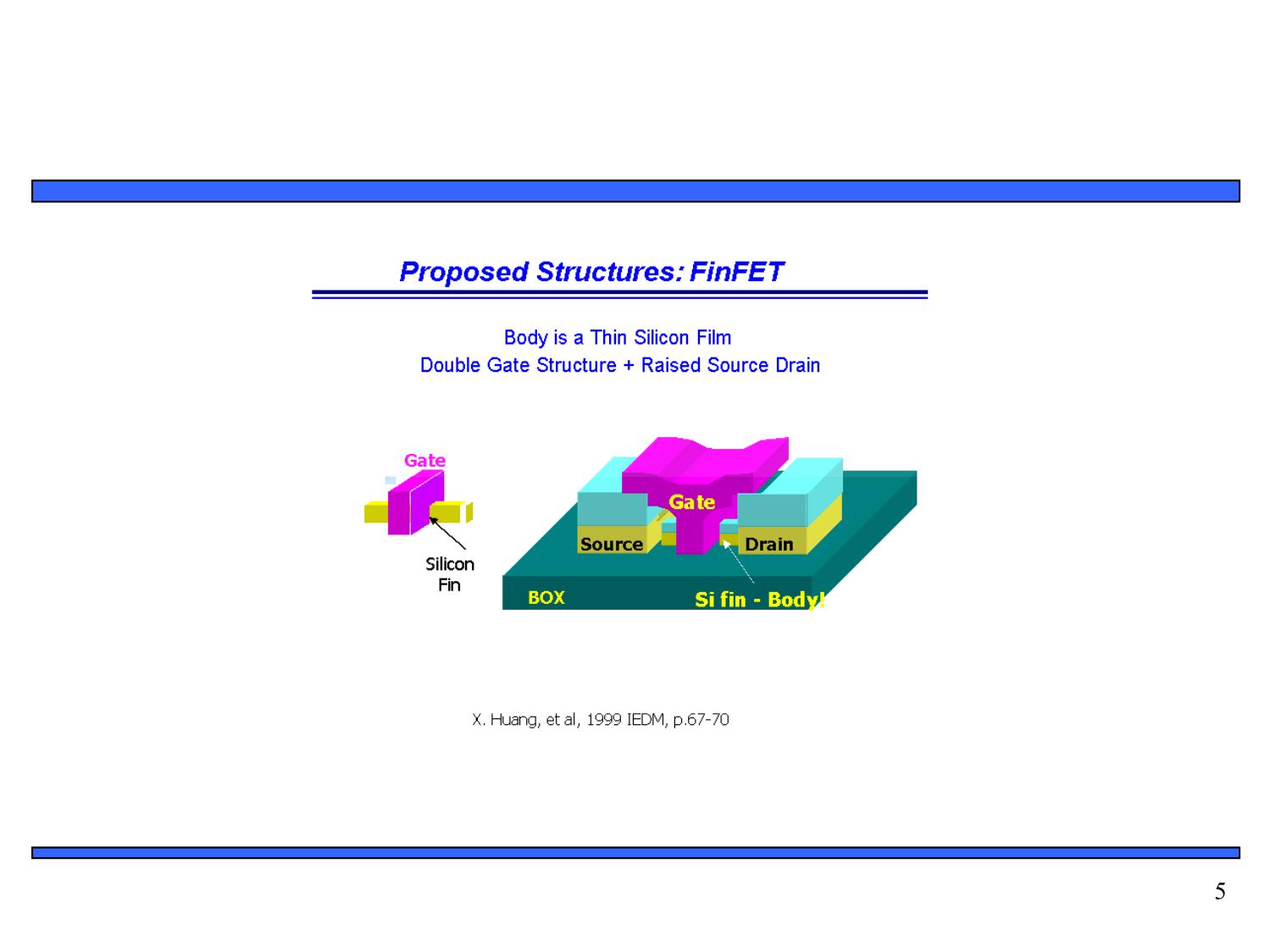

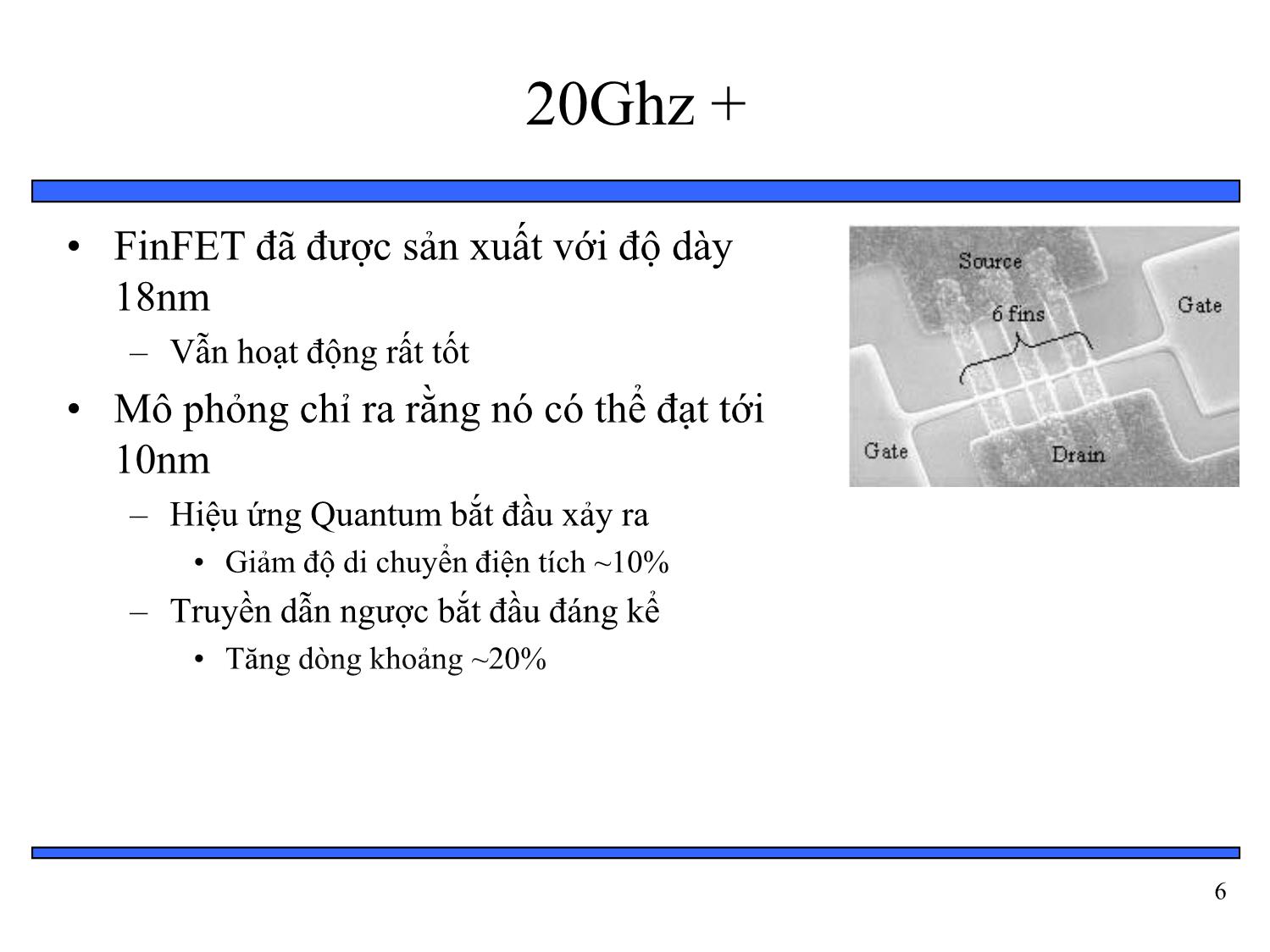

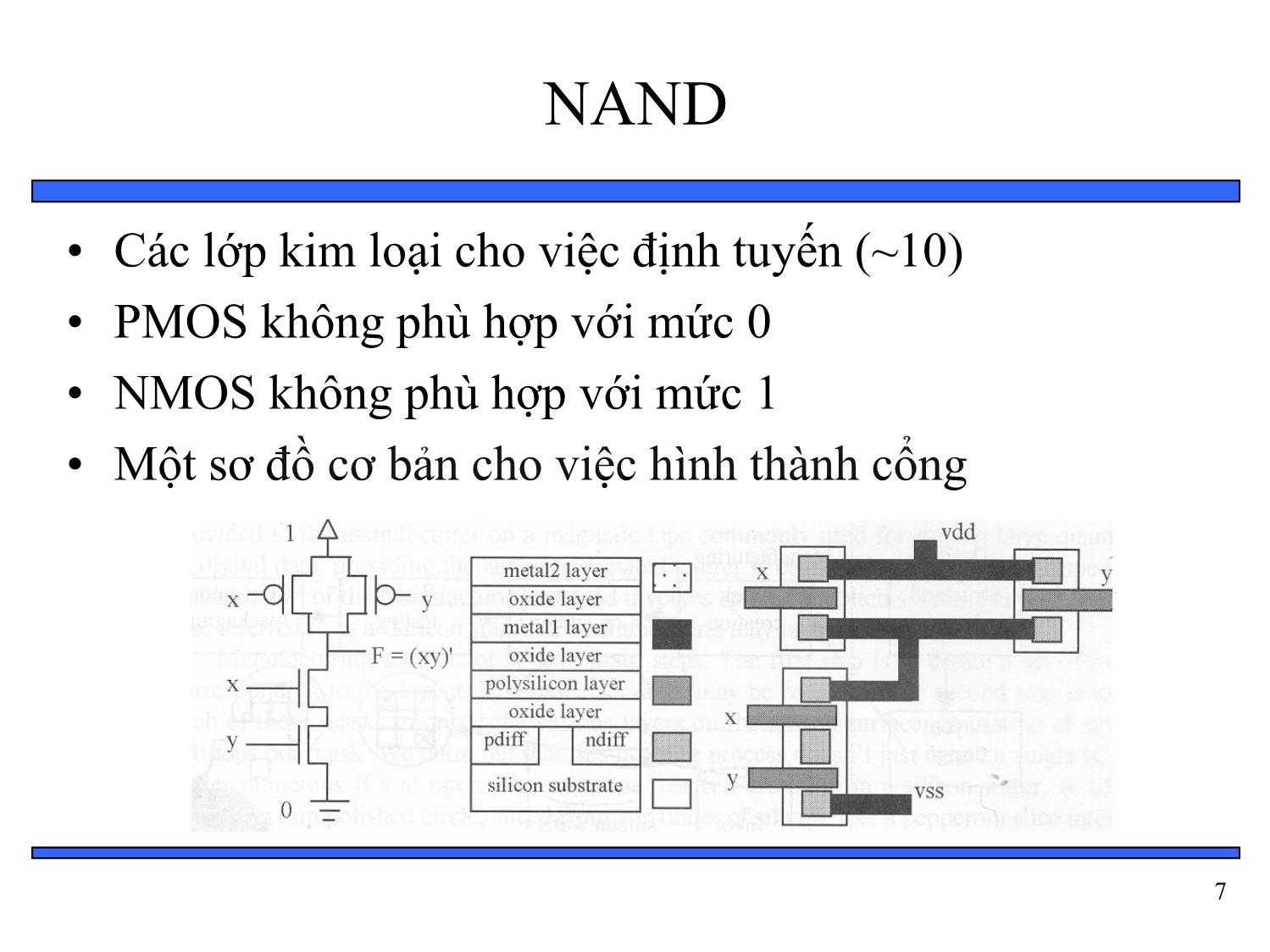

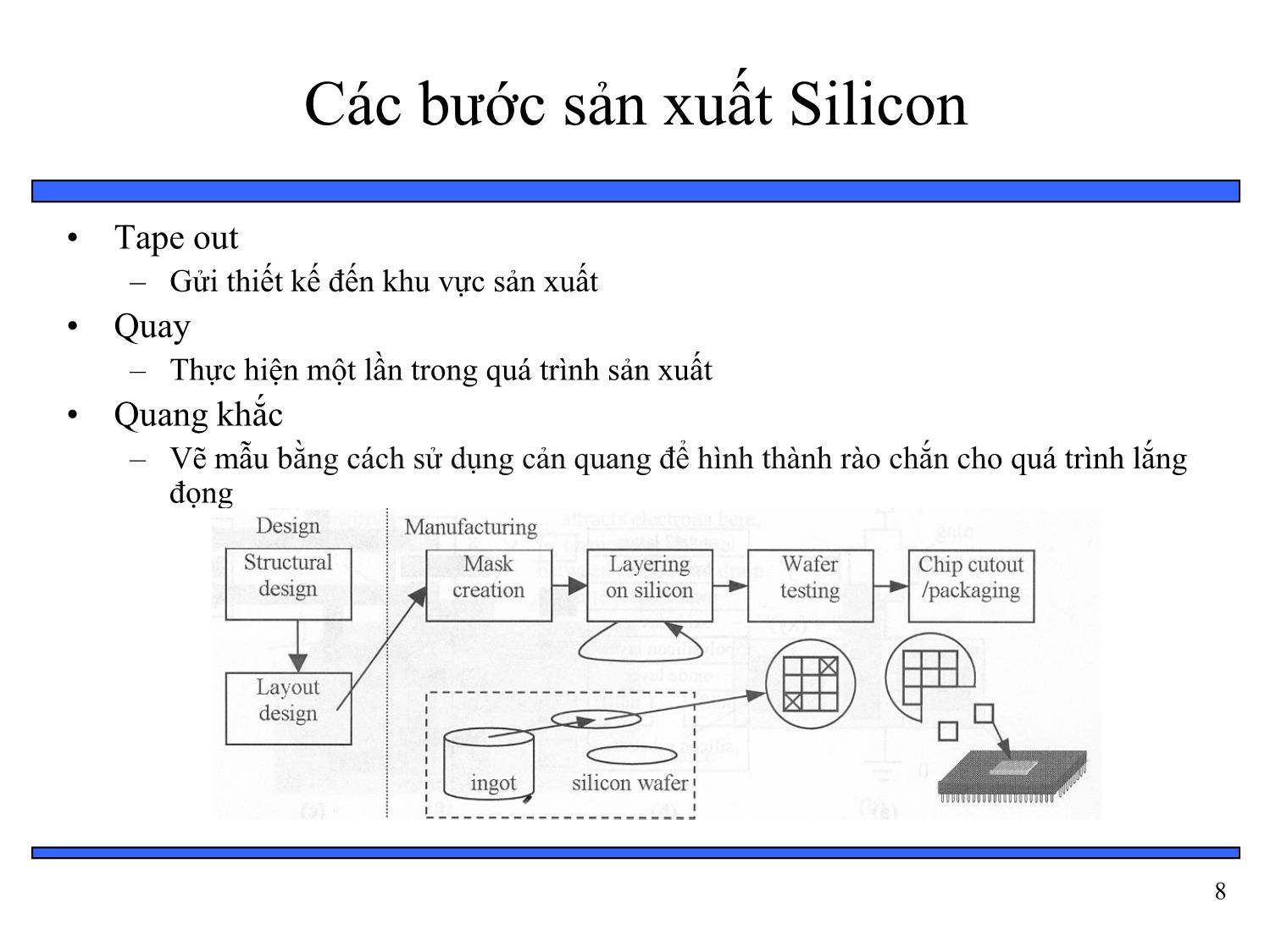

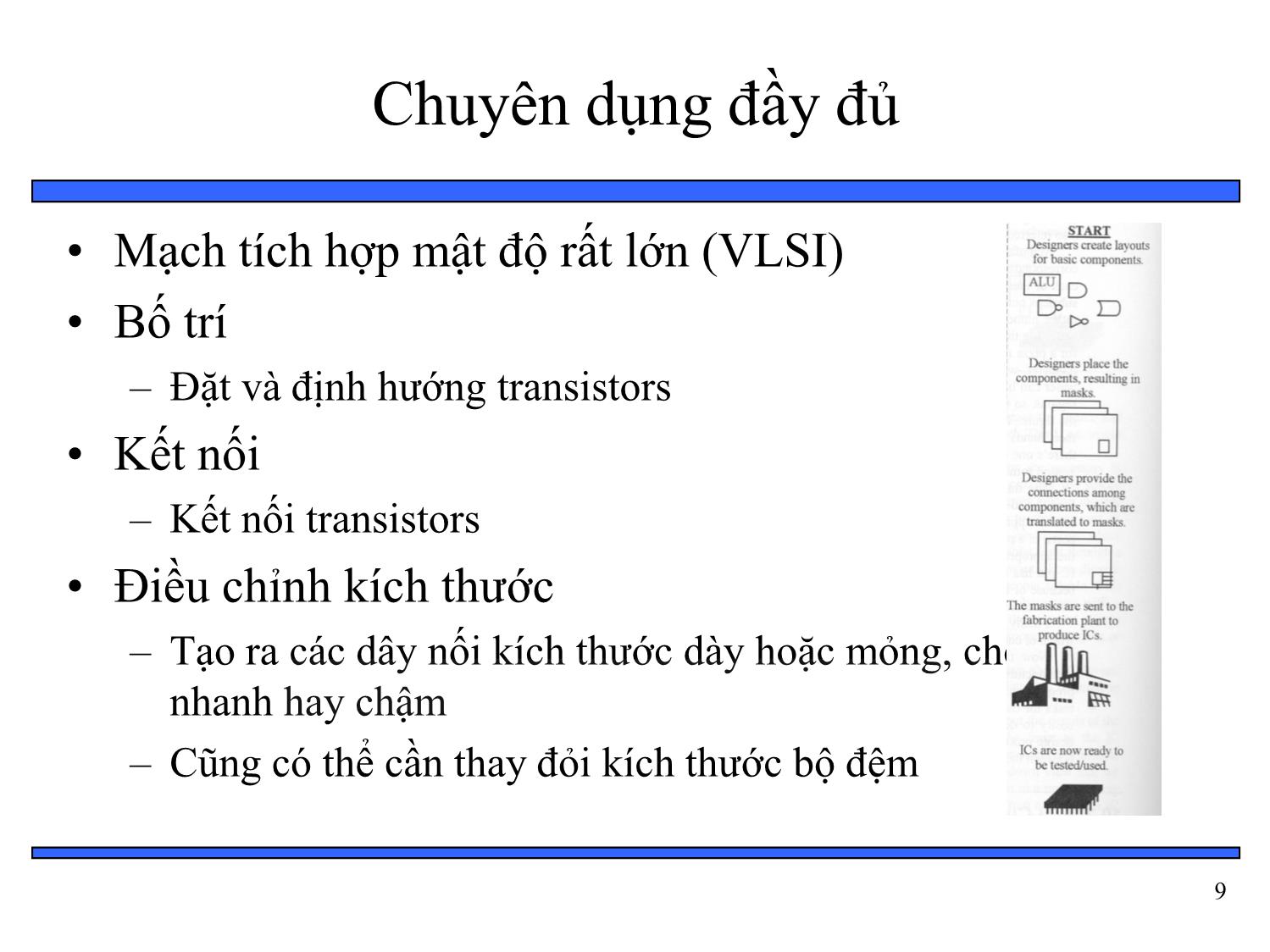

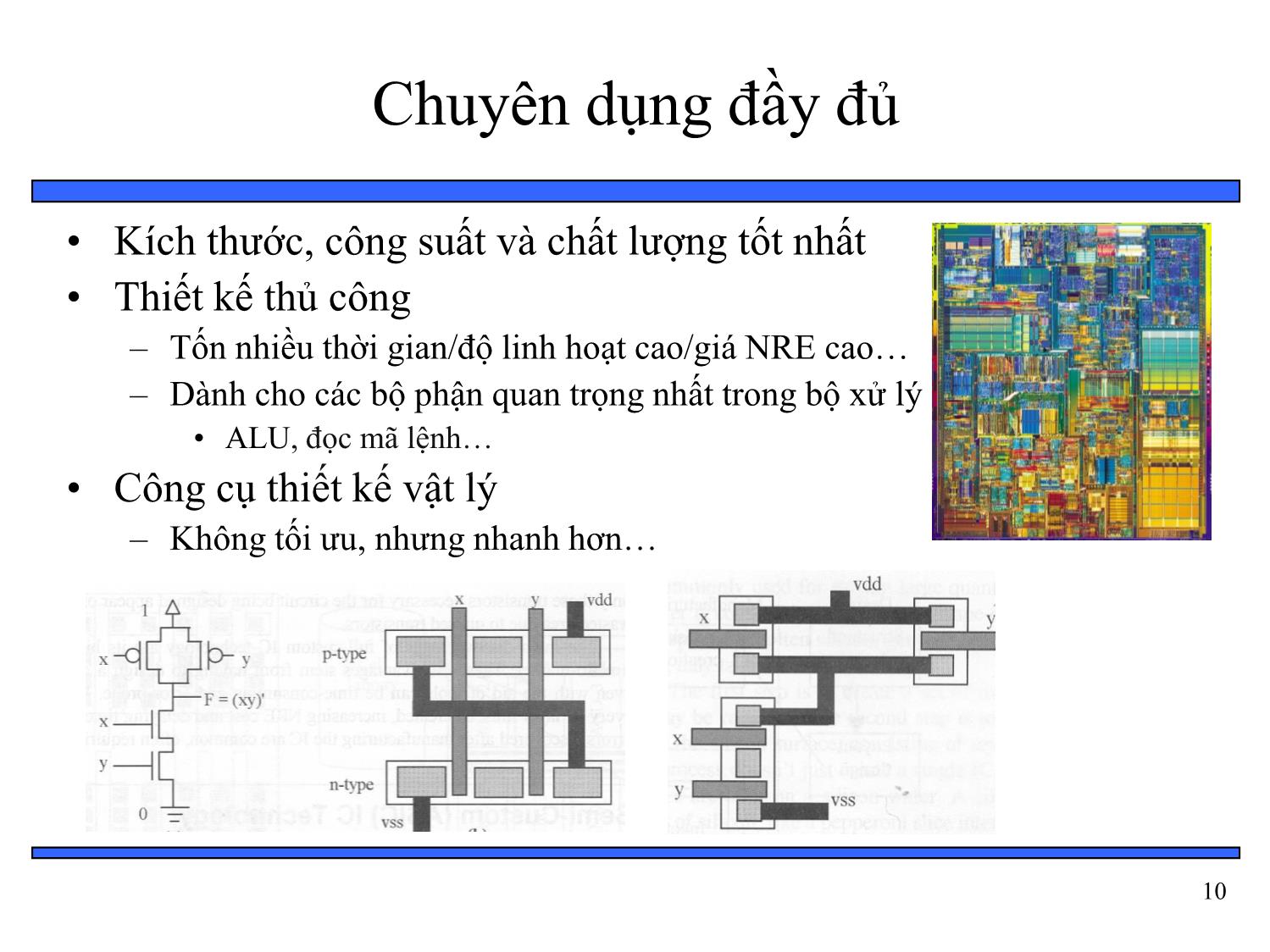

EmbeddedCHƢƠNG Systems Design: 2: CẤU A Unified TRÚC Hardware/Software PHẦN IntroductionCỨNG HỆ THỐNG NHÚNG Bài 6: Công nghệ IC 1 Tổng quan • Cấu trúc IC • Công nghệ IC chức năng chung (VLSI) • Công nghệ IC chức năng chuyên biệt (ASIC) • Công nghệ IC có thể lập trình (PLD) 2 Transistor CMOS • Nguồn, máng – Vùng khuêch tán nơi electrons có thể đi qua – Có thể kết nối nhờ tiếp xúc kim loại • Cổng – Vùng Polysilicon nơi đặt điện áp điều khiển • Oxide – Chất cách điện Si O2 chống rò điện áp cổng 3 Kết thúc luật Moore? • Mọi kích thƣớc của MOSFET đã đƣợc thay đổi – (PMOS) đã giảm xuống • Tăng điện dung cổng • Giảm dòng dò từ S sang D – Độ dày cổng oxide hiện tại là 2.5-3nm • Khoảng 25 atoms!!! gate IC package IC oxide source channel drain Silicon substrate 4 5 20Ghz + • FinFET đã đƣợc sản xuất với độ dày 18nm – Vẫn hoạt động rất tốt • Mô phỏng chỉ ra rằng nó có thể đạt tới 10nm – Hiệu ứng Quantum bắt đầu xảy ra • Giảm độ di chuyển điện tích ~10% – Truyền dẫn ngƣợc bắt đầu đáng kể • Tăng dòng khoảng ~20% 6 NAND • Các lớp kim loại cho việc định tuyến (~10) • PMOS không phù hợp với mức 0 • NMOS không phù hợp với mức 1 • Một sơ đồ cơ bản cho việc hình thành cổng 7 Các bƣớc sản xuất Silicon • Tape out – Gửi thiết kế đến khu vực sản xuất • Quay – Thực hiện một lần trong quá trình sản xuất • Quang khắc – Vẽ mẫu bằng cách sử dụng cản quang để hình thành rào chắn cho quá trình lắng đọng 8 Chuyên dụng đầy đủ • Mạch tích hợp mật độ rất lớn (VLSI) • Bố trí – Đặt và định hƣớng transistors • Kết nối – Kết nối transistors • Điều chỉnh kích thƣớc – Tạo ra các dây nối kích thƣớc dày hoặc mỏng, cho tốc độ nhanh hay chậm – Cũng có thể cần thay đỏi kích thƣớc bộ đệm 9 Chuyên dụng đầy đủ • Kích thƣớc, công suất và chất lƣợng tốt nhất • Thiết kế thủ công – Tốn nhiều thời gian/độ linh hoạt cao/giá NRE cao – Dành cho các bộ phận quan trọng nhất trong bộ xử lý • ALU, đọc mã lệnh • Công cụ thiết kế vật lý – Không tối ƣu, nhƣng nhanh hơn 10 Bán chuyên dụng • Mảng các cổng logic – Gồm một mảng các cổng đƣợc chế tạo sẵn – “bố trí” và kết nối – Mật độ cao hơn, thời gian đƣa ra thị trƣờng nhanh hơn – Không tích hợp cao nhƣ các vi mạch chức năng chuyên dụng đầy đủ • Các “Ô” tiêu chuẩn – Một thƣ viện các ô đƣợc thiết kế trƣớc – Bố trí và kết nối – Mật độ thấp hơn, độ phức tạp cao hơn – Tích hợp tốt nhất với chuyên dụng đầy đủ 11 Bán chuyên dụng • Kiểu thiết kế phổ biến nhất • Phù hợp với các loại – Tốt • Công suất, thời gian đƣa ra thị trƣờng, chất lƣợng, giá NRE, giá đơn chiếc • Tích hợp – Tích hợp với thiết bị chuyên dụng đầy đủ cho các vùng thiết kế quan trọng 12 13 PLD • Thiết bị logic khả trình – Programmable Logic Array (PLA), Programmable Array Logic (PAL), Field Programmable Gate Array (FPGA) • Tất cả các lớp đã có sẵn – Ngƣời thiết kế có thể mua một IC – Để thực hiện chức năng mong muốn • Các kết nối trên IC đƣợc tạo ra hoặc hủy để thực hiện chức năng • Lợi ích – Giá NRE rất thấp – Thời gian đƣa ra thị trƣờng ngắn • Hạn chế – Giá cao, không tốt cho sản xuất hàng loạt – Công suất • Ngoại trừ PLA loại đặc biệt 1600 usable gate, 7.5 ns – Chậm hơn $7 list price 14 Xilinx FPGA 15 Khối logic có thể cấu hình đƣợc (CLB) 16 Khối I/O 17

File đính kèm:

bai_giang_thiet_ke_he_thong_nhung_chuong_2_cau_truc_phan_cun.pdf

bai_giang_thiet_ke_he_thong_nhung_chuong_2_cau_truc_phan_cun.pdf