Bài giảng Thiết kế hệ thống nhúng - Chương 2: Cấu trúc phần cứng hệ thống nhúng - Bài 5: Giao diện

Tổng quan

• Khái niệm cơ bản

• Giao diện vi xử lý

– Địa chỉ I/O

– Ngắt

– Truy cập bộ nhớ trực tiếp (DMA)

• Bus phân cấp

• Thủ tục - Protocols

– Nối tiếp

– Song song

– Không dây3

• Chức năng của một hệ thống nhúng

– Xử lý

• Biến đổi dữ liệu

• Thực hiện công việc dùng bọ xử lý

– Lƣu trữ

• Lƣu trữ dữ liệu

• Thực hiện dùng bộ nhớ

– Truyền thông

• Trao đổi dữ liệu giữa bộ xử lý và bộ nhớ

• Hực hiện sử dụng bus

• Thƣờng đƣợc gọi là giao diện - interfacing

Trang 1

Trang 2

Trang 3

Trang 4

Trang 5

Trang 6

Trang 7

Trang 8

Trang 9

Trang 10

Tải về để xem bản đầy đủ

Bạn đang xem 10 trang mẫu của tài liệu "Bài giảng Thiết kế hệ thống nhúng - Chương 2: Cấu trúc phần cứng hệ thống nhúng - Bài 5: Giao diện", để tải tài liệu gốc về máy hãy click vào nút Download ở trên

Tóm tắt nội dung tài liệu: Bài giảng Thiết kế hệ thống nhúng - Chương 2: Cấu trúc phần cứng hệ thống nhúng - Bài 5: Giao diện

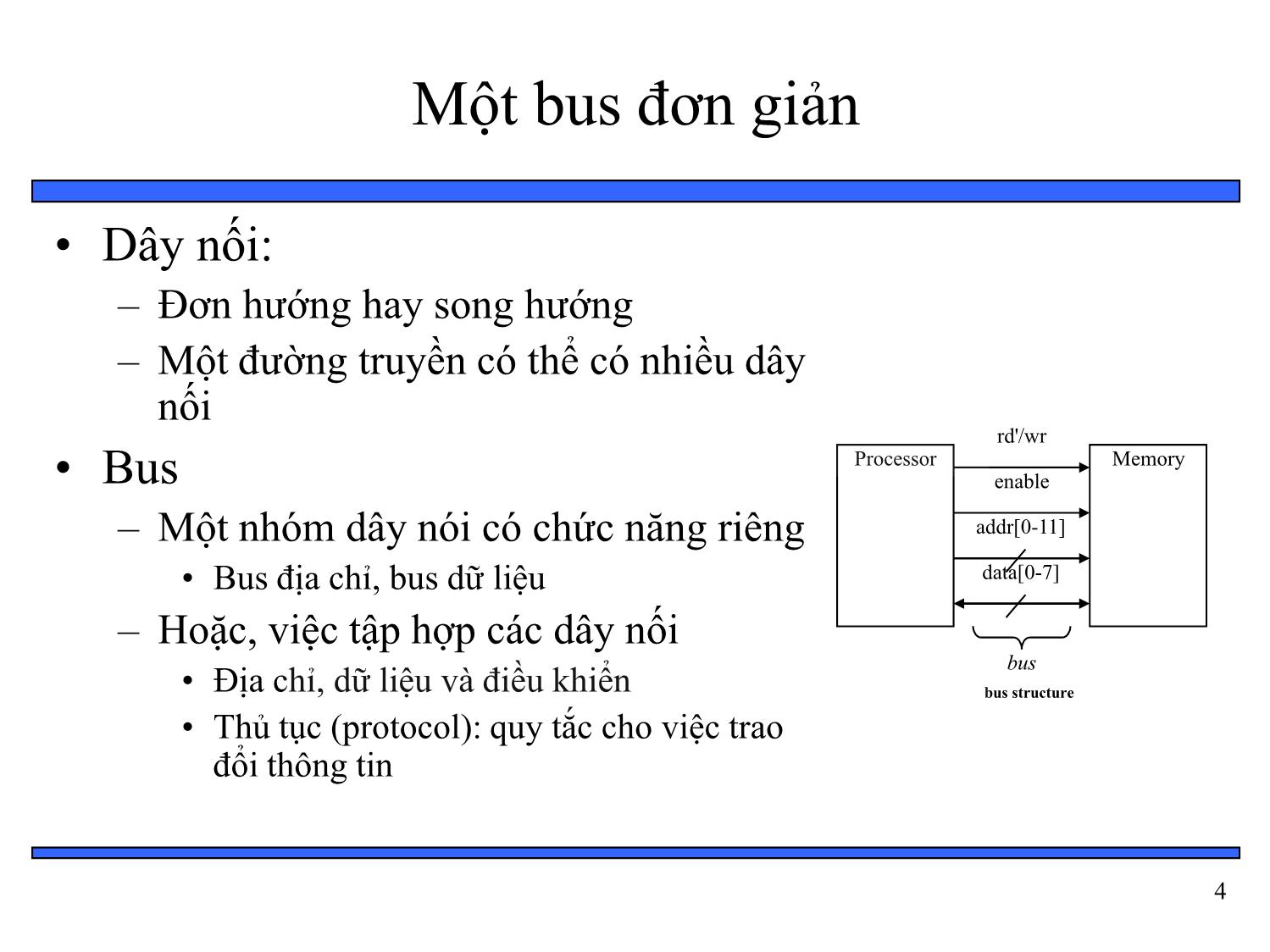

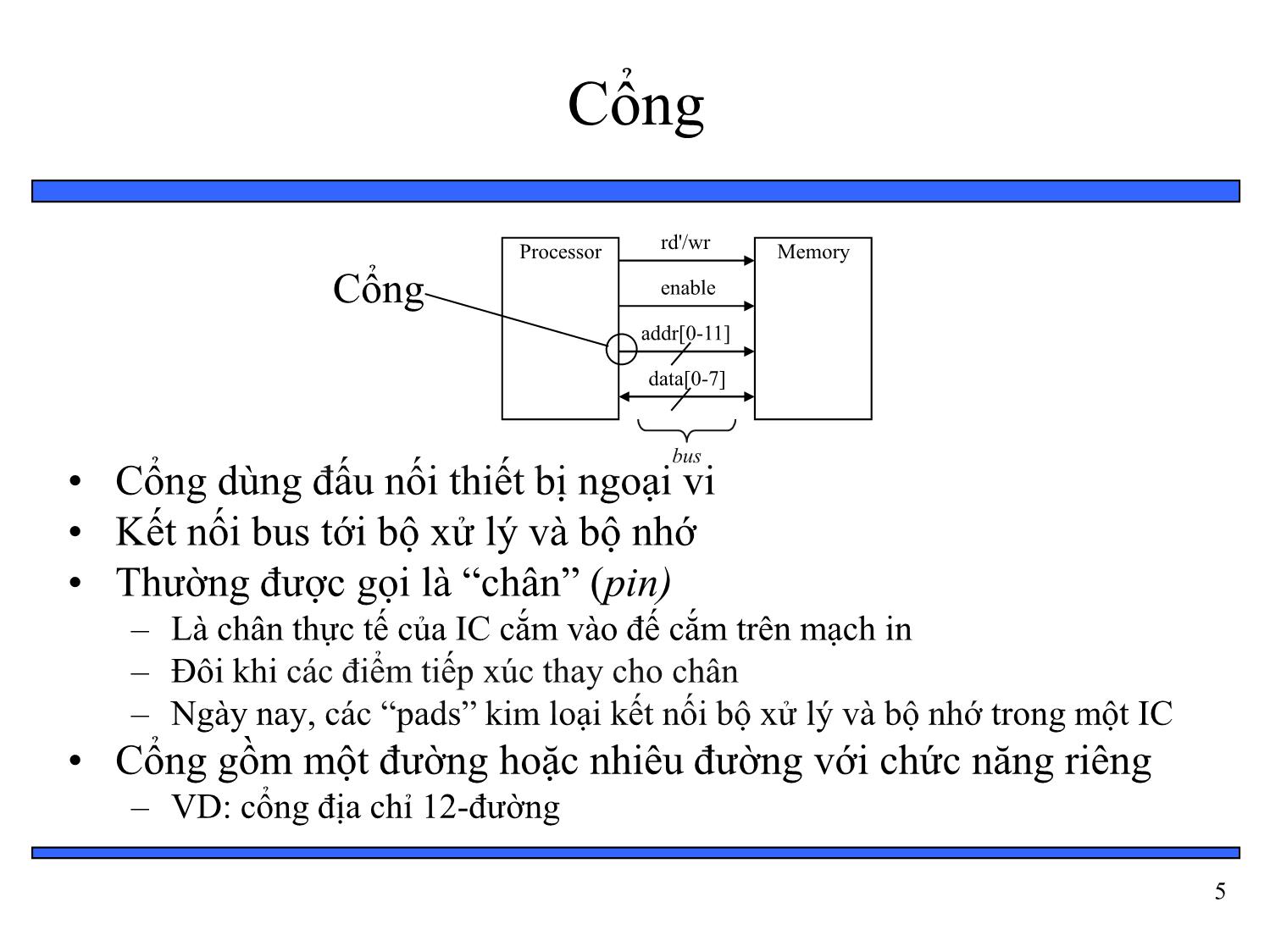

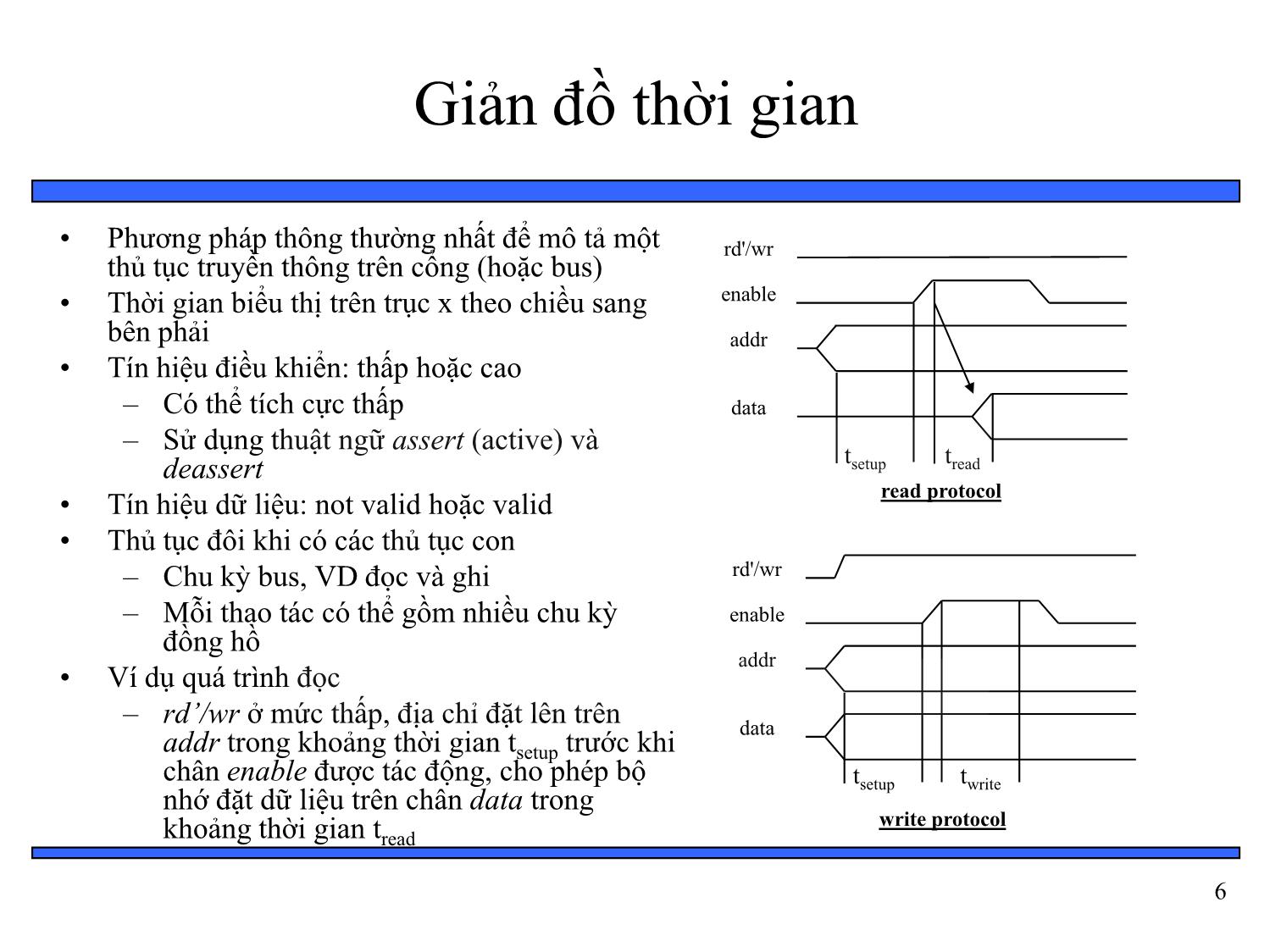

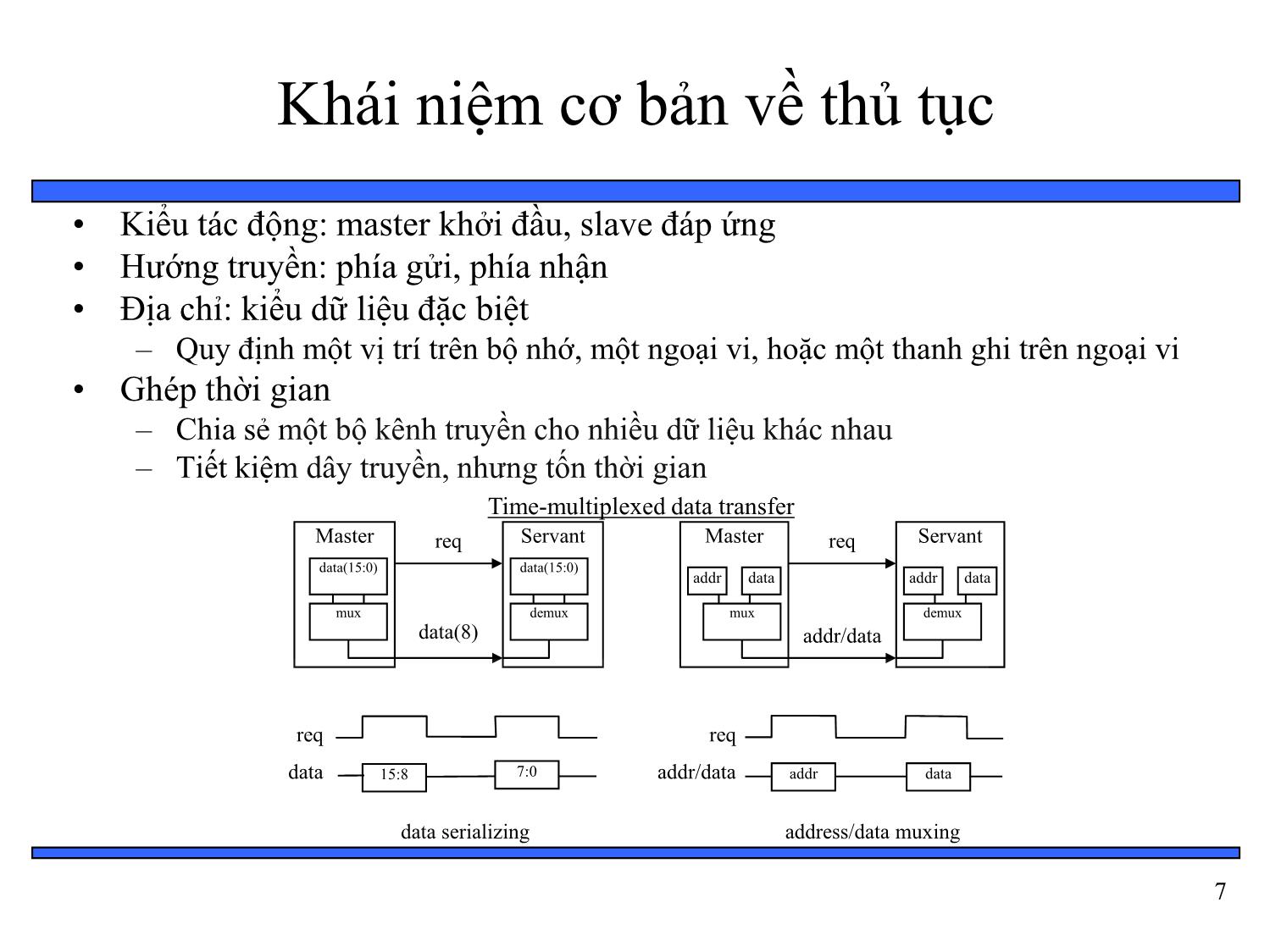

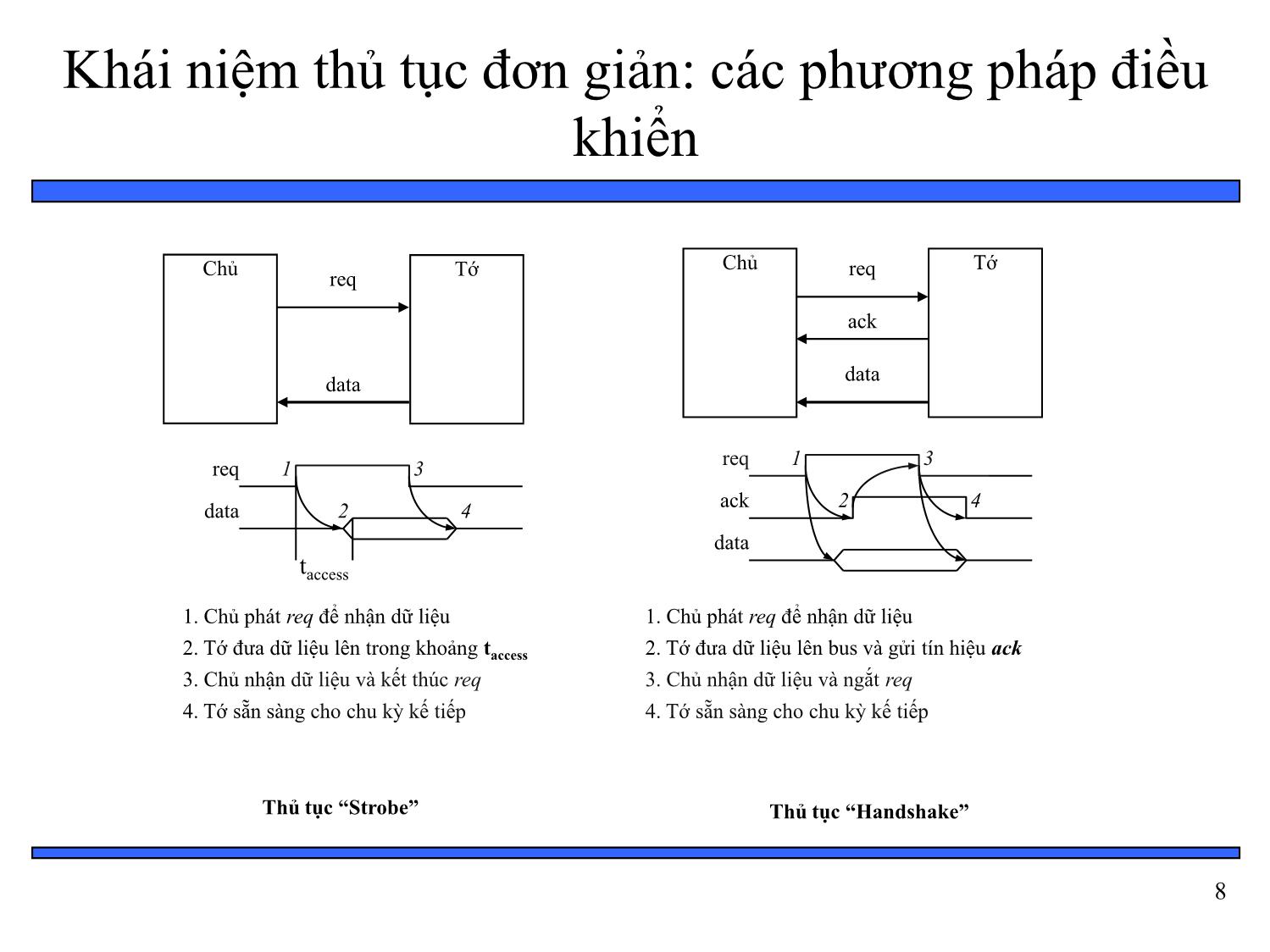

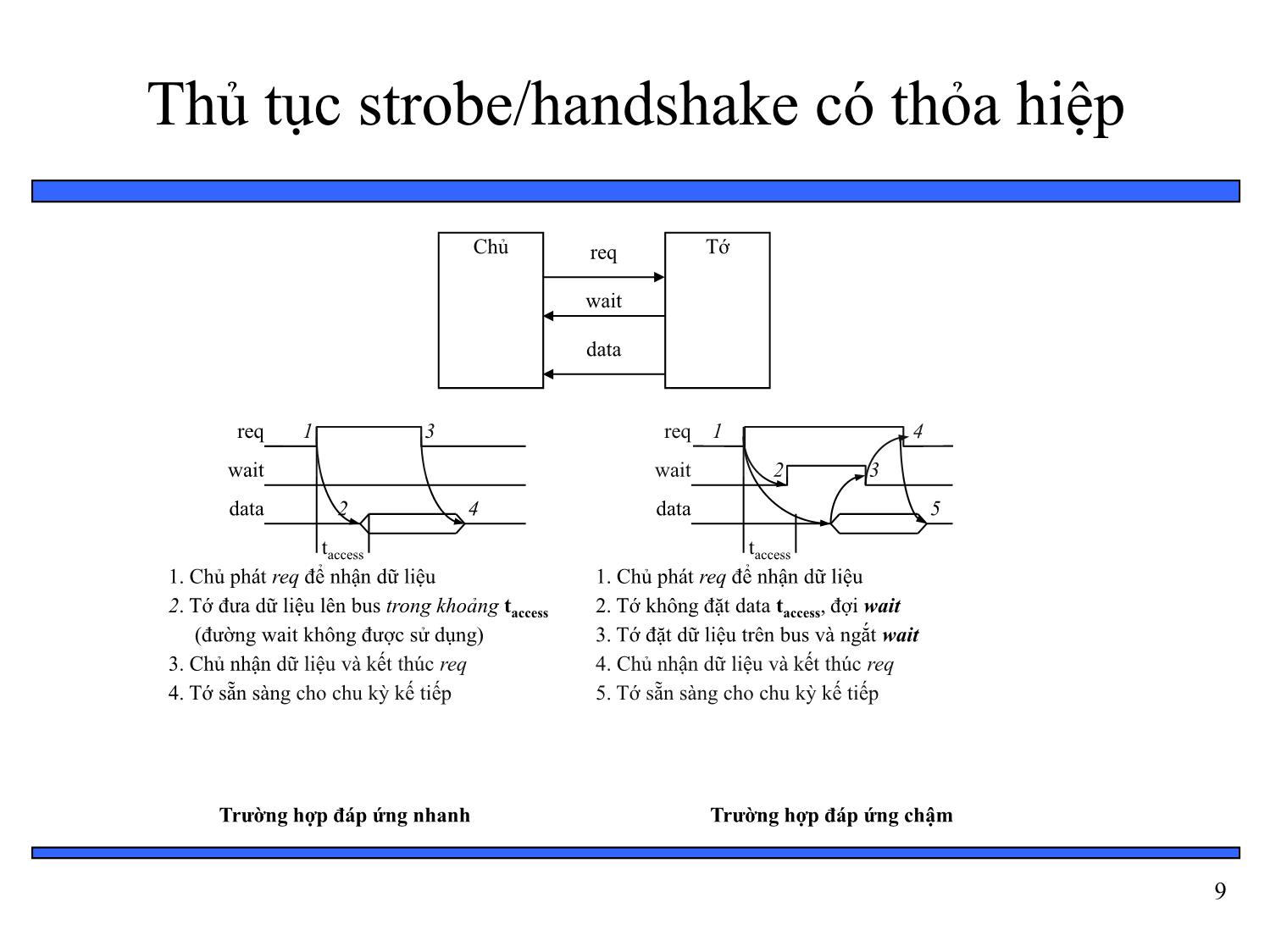

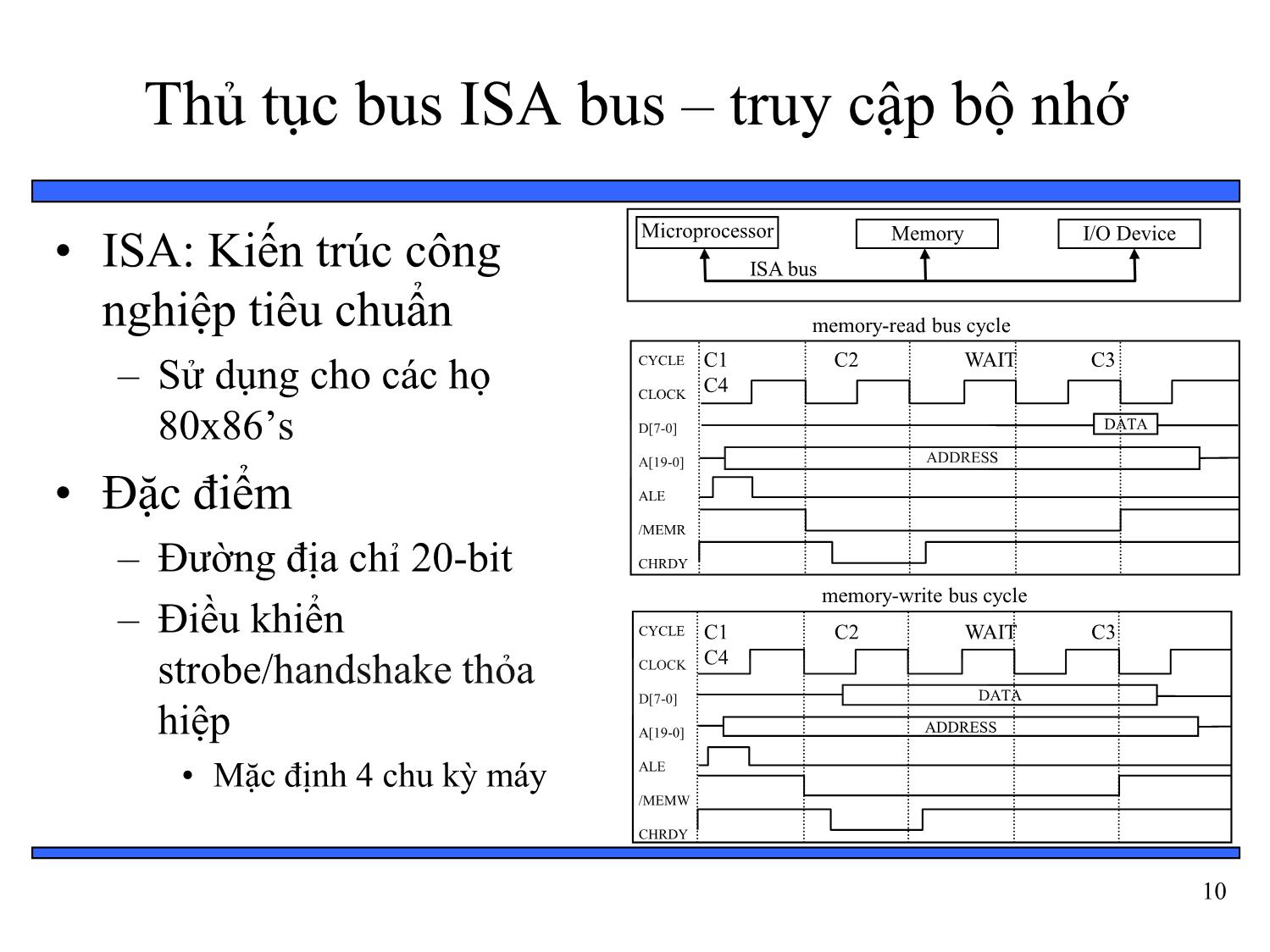

phân cấp • Thủ tục - Protocols – Nối tiếp – Song song – Không dây 2 Giới thiệu • Chức năng của một hệ thống nhúng – Xử lý • Biến đổi dữ liệu • Thực hiện công việc dùng bọ xử lý – Lƣu trữ • Lƣu trữ dữ liệu • Thực hiện dùng bộ nhớ – Truyền thông • Trao đổi dữ liệu giữa bộ xử lý và bộ nhớ • Hực hiện sử dụng bus • Thƣờng đƣợc gọi là giao diện - interfacing 3 Một bus đơn giản • Dây nối: – Đơn hƣớng hay song hƣớng – Một đƣờng truyền có thể có nhiều dây nối rd'/wr Processor Memory • Bus enable – Một nhóm dây nói có chức năng riêng addr[0-11] • Bus địa chỉ, bus dữ liệu data[0-7] – Hoặc, việc tập hợp các dây nối bus • Địa chỉ, dữ liệu và điều khiển bus structure • Thủ tục (protocol): quy tắc cho việc trao đổi thông tin 4 Cổng Processor rd'/wr Memory Cổng enable addr[0-11] data[0-7] bus • Cổng dùng đấu nối thiết bị ngoại vi • Kết nối bus tới bộ xử lý và bộ nhớ • Thƣờng đƣợc gọi là “chân” (pin) – Là chân thực tế của IC cắm vào đế cắm trên mạch in – Đôi khi các điểm tiếp xúc thay cho chân – Ngày nay, các “pads” kim loại kết nối bộ xử lý và bộ nhớ trong một IC • Cổng gồm một đƣờng hoặc nhiêu đƣờng với chức năng riêng – VD: cổng địa chỉ 12-đƣờng 5 Giản đồ thời gian • Phƣơng pháp thông thƣờng nhất để mô tả một rd'/wr thủ tục truyền thông trên cổng (hoặc bus) • Thời gian biểu thị trên trục x theo chiều sang enable bên phải addr • Tín hiệu điều khiển: thấp hoặc cao – Có thể tích cực thấp data – Sử dụng thuật ngữ assert (active) và deassert tsetup tread • Tín hiệu dữ liệu: not valid hoặc valid read protocol • Thủ tục đôi khi có các thủ tục con – Chu kỳ bus, VD đọc và ghi rd'/wr – Mỗi thao tác có thể gồm nhiều chu kỳ enable đồng hồ addr • Ví dụ quá trình đọc – rd’/wr ở mức thấp, địa chỉ đặt lên trên data addr trong khoảng thời gian tsetup trƣớc khi chân enable đƣợc tác động, cho phép bộ tsetup twrite nhớ đặt dữ liệu trên chân data trong write protocol khoảng thời gian tread 6 Khái niệm cơ bản về thủ tục • Kiểu tác động: master khởi đầu, slave đáp ứng • Hƣớng truyền: phía gửi, phía nhận • Địa chỉ: kiểu dữ liệu đặc biệt – Quy định một vị trí trên bộ nhớ, một ngoại vi, hoặc một thanh ghi trên ngoại vi • Ghép thời gian – Chia sẻ một bộ kênh truyền cho nhiều dữ liệu khác nhau – Tiết kiệm dây truyền, nhƣng tốn thời gian Time-multiplexed data transfer Master req Servant Master req Servant data(15:0) data(15:0) addr data addr data mux demux mux demux data(8) addr/data req req data 15:8 7:0 addr/data addr data data serializing address/data muxing 7 Khái niệm thủ tục đơn giản: các phƣơng pháp điều khiển Chủ Tớ Chủ req Tớ req ack data data req 1 3 req 1 3 data 2 4 ack 2 4 data taccess 1. Chủ phát req để nhận dữ liệu 1. Chủ phát req để nhận dữ liệu 2. Tớ đƣa dữ liệu lên trong khoảng taccess 2. Tớ đƣa dữ liệu lên bus và gửi tín hiệu ack 3. Chủ nhận dữ liệu và kết thúc req 3. Chủ nhận dữ liệu và ngắt req 4. Tớ sẵn sàng cho chu kỳ kế tiếp 4. Tớ sẵn sàng cho chu kỳ kế tiếp Thủ tục “Strobe” Thủ tục “Handshake” 8 Thủ tục strobe/handshake có thỏa hiệp Chủ req Tớ wait data req 1 3 req 1 4 wait wait 2 3 data 2 4 data 5 taccess taccess 1. Chủ phát req để nhận dữ liệu 1. Chủ phát req để nhận dữ liệu 2. Tớ đƣa dữ liệu lên bus trong khoảng taccess 2. Tớ không đặt data taccess, đợi wait (đƣờng wait không đƣợc sử dụng) 3. Tớ đặt dữ liệu trên bus và ngắt wait 3. Chủ nhận dữ liệu và kết thúc req 4. Chủ nhận dữ liệu và kết thúc req 4. Tớ sẵn sàng cho chu kỳ kế tiếp 5. Tớ sẵn sàng cho chu kỳ kế tiếp Trường hợp đáp ứng nhanh Trường hợp đáp ứng chậm 9 Thủ tục bus ISA bus – truy cập bộ nhớ Microprocessor Memory I/O Device • ISA: Kiến trúc công ISA bus nghiệp tiêu chuẩn memory-read bus cycle CYCLE C1 C2 WAIT C3 – Sử dụng cho các họ CLOCK C4 80x86’s D[7-0] DATA A[19-0] ADDRESS • Đặc điểm ALE /MEMR – Đƣờng địa chỉ 20-bit CHRDY memory-write bus cycle – Điều khiển CYCLE C1 C2 WAIT C3 C4 strobe/handshake thỏa CLOCK D[7-0] DATA hiệp A[19-0] ADDRESS • Mặc định 4 chu kỳ máy ALE /MEMW CHRDY 10 Giao tiếp vi xử lý: Địa chỉ I/O • Một bộ vi xử lý giao tiếp với các thiết bị khác qua chân của nó – I/O dựa trên cổng (I/O song song) • Bộ xử lý có một hoặc nhiều cổng N-bit • Chƣơng trình của bộ xử lý đọc và ghi một cổng nhƣ đối với một thanh ghi • VD: P0 = 0xFF; v = P1.2; P0 và P1 là cổng 8-bit – I/O dựa trên bus • Bộ xử lý có cổng địa chỉ, dữ liệu và điều khiển trên một bus đơn • Thủ tục truyền thông đƣợc xây dựng bên trong bộ xử lý • Một lệnh sẽ thực hiện việc ghi hay đọc trên bus 11 Thỏa hiệp/mở rộng • Ngoại vi I/O song song Processor Memory – Khi bộ xử lý chỉ có I/O dựa trên bus nhƣng System bus chúng ta muốn I/O song song Parallel I/O peripheral – Mỗi cổng trên ngoại vi kết nối với một thanh ghi trong ngoại vi đƣợc read/written bởi bộ xử lý Port A Port B Port C Adding parallel I/O to a bus- • I/O song song mở rộng based I/O processor – Khi bộ xử lý chỉ có I/O dựa trên cổng nhƣng Processor Port 0 Port 1 chúng ta cần nhiều cổng hơn Port 2 – Một hoặc nhiểu cổng của bộ xử lý giao tiếp với Port 3 ngoại vi I/O song song sẽ mở rộng tổng số cổng Parallel I/O peripheral I/O – VD: mở rộng 4 cổng thành 6 cổng nhƣ hình bên Port A Port B Port C Extended parallel I/O 12 Các kiểu I/O dựa trên bus: I/O bản đồ nhớ và I/O tiêu chuẩn • Bộ xử lý trao đổi với cả bộ nhớ và ngoại vi sử dụng chung bus – có hai cách để trao đổi với ngoại vi – I/O bản đồ nhớ • Thanh ghi của ngoại vi chiếm địa chỉ trong cùng không gian địa chỉ của bộ nhớ • VD: Bus có địa chỉ 16-bit – Địa chỉ 32k vùng thấp dùng cho bộ nhớ – Địa chỉ 32k vùng cao dùng cho ngoại vi – I/O tiêu chuẩn (I/O-mapped I/O) • Các chân bổ sung (M/IO) trên bus biểu thị bộ nhớ hoặc ngoại vi đƣợc truy cập • VD: Bus có địa chỉ 16-bit – Tất cả 64K địa chỉ dùng cho bộ nhớ khi chân M/IO ở mức 0 – Tất cả 64K địa chỉ dùng cho ngoại vi khi chân M/IO ở mức 1 13 So sánh I/O bản đồ nhớ và I/O tiêu chuẩn • I/O bản đồ nhớ – Không yêu cầu lệnh đặc biệt • Lệnh assembly có các lệnh nhƣ MOV và ADD cngx cho phép làm việc với ngoại vi • I/O tiêu chuẩn yêu cầu các lệnh đặc biệt (VD: IN, OUT) để di chuyển dữ liệu giữa thanh ghi của ngoại vi và bộ nhớ • I/O tiêu chuẩn – Không mất địa chỉ nhớ cho ngoại vi – Bộ giải mã địa chỉ đơn giản hơn • Khi số ngoại vi phải nhỏ hơn không gian địa chỉ thì các bit địa chỉ vùng cao có thể bỏ trống – Bộ so sánh nhỏ hơn và/hoặc nhanh hơn 14 Bus ISA • ISA cung cấp I/O tiêu chuẩn – /IOR khác với /MEMR để cho phép đọc từ thiết bị ngoại vi ISA I/O bus read protocol CYCLE C1 C2 WAIT C3 • /IOW sử dụng cho ghi CLOCK C4 DATA – Không gian địa chỉ 16-bit cho D[7-0] ADDRESS I/O vs. không gian địa chỉ 20- A[15-0] ALE bit cho bộ nhớ /IOR – Ngoài ra nó tƣơng tự với thủ CHRDY tục truy cập bộ nhớ 15 Một thủ tục truy cập bộ nhớ đơn giản D P0 Adr. 7..0 Data P0 D Q A /CS P2 Adr. 158 /OE ALE G /WE Q Adr. 70 74373 CS2 /CS1 8 HM6264 ALE P2 /WR /CS /RD /RD D /PSEN A /OE 8051 27C256 • Giao tiếp 8051 với bộ nhớ ngoài – Cổng P0 và P2 hỗ trợ I/O dựa trên cổng khi bộ nhớ trong của 8051 đƣợc sử dụng – Các cổng này phục vụ nhƣ bus dữ liệu/địa chỉ khi bộ nhớ ngoài đƣợc sử dụng – Địa chỉ 16-bit và dữ liệu 8-bit đƣợc ghép theo thời gian; 8-bits thấp của địa chỉ phải đƣợc chốt nhờ tín hiệu ALE 16 Giao tiếp vi xử lý: ngắt • Giả sử một thiết bị ngoại vi yêu cầu đƣợc thu nhận dữ liệu lập tức bởi bộ xử lý – Bộ xử lý có thể kiểm tra liên tục ngoại vi xem dữ liệu đã đến hay chƣa – rất kém hiệu quả – Ngoại vi có thể ngắt bộ xử lý khi nó có dữ liệu • Yêu cầu phải có thêm chân: Int – Nếu Int là 1, bộ xử lý dừng chƣơng trình đang thực hiện, nhảy tới một Interrupt Service Routine, hoặc ISR – Đƣợc biết nhƣ đầu vào điều khiển ngắt I/O 17 Giao tiếp vi xử lý: ngắt • Địa chỉ của ISR (interrupt address vector) là gì? – Ngắt cố định • Địa chỉ ngắt đƣợc thiết lập sẵn trong bộ xử lý, không thể thay đổi – Ngắt vector • Ngoại vi phải cung cấp địa chỉ • Thƣờng sử dụng khi bộ xử lý có nhiều ngoại vi kết nối chung một bus – Phối hợp: bảng địa chỉ ngắt 18 Truyền thông song song • Nhiều chân dữ liệu, điều khiển, và có thể cả công suất – Mỗi dây một bit • Tốc độ dữ liệu cao, cự ly truyền dẫn ngắn • Thƣờng sử dụng khi kết nối các thiết bị trên cùng IC hoặc trên cùng bo mạch – Bus phải đủ ngắn • Dây dài dẫn đến điện dung ký sinh cao • Nhiễu xuyên kênh tăng khi dây dài • Giá cao hơn 19 Truyền thông nối tiếp • Dây dữ liệu đơn, có thể bao gồm dây điều khiển và công suất • Từ đƣợc truyền đi từng bít một • Truyền dữ liệu tốt hơn với cự ly dài – Điện dung ký sinh ít • Rẻ hơn • Thủ tục truyền thông và giao tiếp linh hoạt hơn – Phía gửi phải tách từ thành các bit – Phía thu làm ngƣợc lại – Tín hiệu điều khiển thƣờng gửi cùng trên một dây với dữ liệu làm cho thủ tục truyền phức tạp hơn 20 Truyền thông không dây • Hồng noại (IR) – Tần số dƣới phổ ánh sáng nhìn thấy – Đi ốt phát ánh sáng hồng ngoại để tạo tín hiệu – Transistor hồng ngoại xác định tín hiệu, dẫn khi có ánh sáng hồng ngoại – Giá rẻ – Cần đƣờng truyền thắng, phạm vi hẹp • Sóng vô tuyến (RF) – Sóng điện từ trong phổ radio – Mạch tƣơng tự và anten ở cả hai phía phát và thu – Không càn đƣờng truyền thẳng, phạm vi hoạt động phụ thuộc vào công suất phát 21 Xác định lỗi và sửa lỗi • Thƣờng là một phần của thủ tục truyền • Xác định lỗi: là khả năng của bộ thu xác định lỗi trong quá trình truyền • Sửa lỗi: khả năng phối hợp giữa bọ thu và bộ phát để khôi phục lỗi • bit lỗi đơn: sử dụng một bit • Bit lỗi nhóm: sử dụng nhóm bit • Chẵn lẻ: bit bổ sung cho việc xác định lỗi • Kiểm tra tóng: từ bổ sung với gói dữ liệu nhiều từ 22 Thủ tục nối tiếp: I2C • I2C (Inter-IC) – Thủ tục bus nối tiếp 2 dây phát triển bởi Philips Semiconductors gần 20 năm trƣớc – Cho phép các ngoại vi của ICs giao tiếp với nhau sử dụng phần cứng truyền thông đơn giản – Tốc độ truyền dữ liệu lên tới 100 kbits/s và địa chỉ 7-bit ở chế độ hoạt động thông thƣờng – 3.4 Mbits/s và dịa chỉ 10-bit ở chế độ nhanh – Các thiết bị có thể giao tiếp với bus I2C: • EPROMS, Flash, và một vài bộ nhớ RAM, đồng hồ thời gian thực và vi điều khiển, 23 Kiến trúc bus I2C SCL SDA Micro- EEPROM Temp. LCD- controller (servant) Sensor controller (master) (servant) (servant) < 400 pF Addr=0x01 Addr=0x02 Addr=0x03 SDA SDA SDA SDA SCL SCL SCL SCL Start condition Sending 0 Sending 1 Stop condition From From Servant receiver D C S A A A A R A D D D A S O T R 6 5 0 / C 8 7 0 C T P T w K K Typical read/write cycle 24 Thủ tục nối tiếp: CAN • CAN (Controller area network) – Thủ tục cho ứng dụng thời gian thực – Phát triển bởi Robert Bosch GmbH – Thƣờng sử dụng trong các hệ thống thông tin trong oto – Các ứng dụng sử dụng CAN ngày nay bao gồm: • Điều khiển thang máy, máy photo, hệ thống điều khiển tự động, thiết bị y tế – Tốc độ truyền dữ liệu lên tới 1 Mbit/s và địa chỉ 11-bit – Các thiết bị có thể giao tiếp với CAN: • 8051-tƣơng thích bộ xử lý 8592 và bộ điều khiển CAN – Thiết kế vật lý thực tế của bus CAN không quy định trong thủ tục 25 Thủ tục nối tiếp: FireWire • FireWire (a.k.a. I-Link, Lynx, IEEE 1394) – Bus nối tiếp chất lƣợng cao phát triển bởi Apple Computer Inc. – Thiết kế cho việc giao tiếp các thiết bị điện tử độc lập • e.g., Desktop, scanner – Tốc độ truyền dữ liệu từ 12.5 tới 400 Mbits/s, 64-bit địa chỉ – Khả năng Plug-and-play – Thiết kế theo cấu trúc góc dữ liệu – Các ứng dụng sử dụng FireWire bao gồm: • disk drives, printers, scanners, cameras 26 Thủ tục nối tiếp: USB • USB (Universal Serial Bus) – Dễ kết nối hơn giữa PC và màn hình, máy in, modem, máy scanner, camera, vv – Có hai tốc độ dữ liệu: • 12 Mbps đối với thiết bị băng rộng • 1.5 Mbps đối với thiết bị tốc độ thấp – Cấu hình sao có thể đƣợc sử dụng • Một thiết bị USB (hub) kết nối với PC – Hub có thể nhúng trong thiết bị nhƣ màn hình, máy in, hoặc bàn phím • Nhiều thiết bị USB có thể kết nói với hub • Tối đa 127 thiết bị có thể kết nối kiểu này – Bộ điều khiển USB host • Quản lý và điều khiển độ rộng băng truyền và phần mềm điều khiển cần thiết cho mỗi ngoại vi • Điều khiển công suất tùy theo thiết bị đƣợc kết nối 27 Thủ tục song song: bus PCI • PCI Bus (Peripheral Component Interconnect) – Bus chất lƣợng cao đƣợc đƣa ra bởi Intel vào đầu những năm 1990’s – Tiêu chuẩn đƣợc lựa chọn cho công nghiệp và đƣợc quản lý bởi PCISIG (PCI Special Interest Group) – Liên kết chíp, board mở rộng, bộ nhớ con của hệ vi xử lý – Tốc độ truyền dữ liệu từ 127.2 đến 508.6 Mbits/s và 32-bit địa chỉ • Sau đó đƣợc mở rộng tới 64-bit trong khi đó vẫn cho phép tƣơng hợp với cấu trúc 32- bit – Kiến trúc bus đồng bộ – Đƣờng địa chỉ/dữ liệu ghép 28 Thủ tục song song: bus ARM • ARM Bus – Thiết kế và sử dụng bởi tập đoàn ARM – Giao tiếp với vi xử lý ARM – Nhiều công ty thiết kế IC có chuẩn bus riêng – Tốc độ truyền dữ liệu là một hàm số của chu kỳ đồng hồ • Nếu tốc độ đồng hồ của bus là X, tốc độ truyền là = 16 x X bits/s – 32-bit địa chỉ 29 Thủ tục không dây: IrDA • IrDA – Thủ tục cho phép truyền dữ liệu bằng sóng hồng ngoại điểm tới điểm với cự ly ngắn – Đƣợc tạo ra bởi Infrared Data Association (IrDA) – Tốc độ truyền dữ liệu 9.6 kbps và 4 Mbps – Phần cứng IrDA có trong máy notebook, máy in, PDAs, cameras số, điện thoại 30 Thủ tục không dây: Bluetooth • Bluetooth – Mới, chuẩn quốc tế cho kết nối không dây – Dựa trên vô tuyến cụ ly ngắn, giá thấp – Kết nối trong phạm vi 10m – Không yêu cầu đƣờng truyền thẳng • VD: kết nối với máy in của phòng khác 31 Thủ tục không dây: IEEE 802.11 • IEEE 802.11 – Tiêu chuẩn cho mạng LANs không dây – Các thông số cụ thể cho các lớp PHY và MAC của mạng • Lớp PHY – Lớp vật lý – Xử lý việc truyền dữ liệu giữa các lớp – Cung cấp tốc độ truyền 1 hoặc 2 Mbps – Oạt động trong băng tần từ 2.4 đến 2.4835 GHz (RF) – Hoặc 300 đến 428,000 GHz (IR) • Lớp MAC – Lớp điều khiển truy cập – Thủ tục cho việc duy trì thứ tự trong truyền thông nhiều điểm (nút) – Tránh xung đột dữ liệu 32 Tóm tắt • Các khái niệm về thủ tục – Hƣớng truyền, ghép kênh theo thời gian, phƣơng pháp điều khiển • Bộ xử lý chức năng chung – I/O dựa trên cổng hoặc dựa trên bus – Địa chỉ I/O: I/O bản đồ nhớ hoặc I/O tiêu chuẩn – Xử lý ngắt: cố định hay vector – Truy cập bộ nhớ trực tiếp • Phân cấp bus • Thông tin – Song song hay nối tiếp, hữu tuyến hay không dây, xác định và sửa lỗi, các lớp – Thủ tục nối tiếp: I2C, CAN, FireWire, và USB; – Song song: PCI và ARM. – Thủ tục không dây nối tiếp: IrDA, Bluetooth, và IEEE 802.11. 33

File đính kèm:

bai_giang_thiet_ke_he_thong_nhung_chuong_2_cau_truc_phan_cun.pdf

bai_giang_thiet_ke_he_thong_nhung_chuong_2_cau_truc_phan_cun.pdf