Bài giảng Kiến trúc máy tính - Chương 3: Bộ xử lý Khối điều khiển và Đường dữ liệu - Tạ Kim Huệ

Nội dung

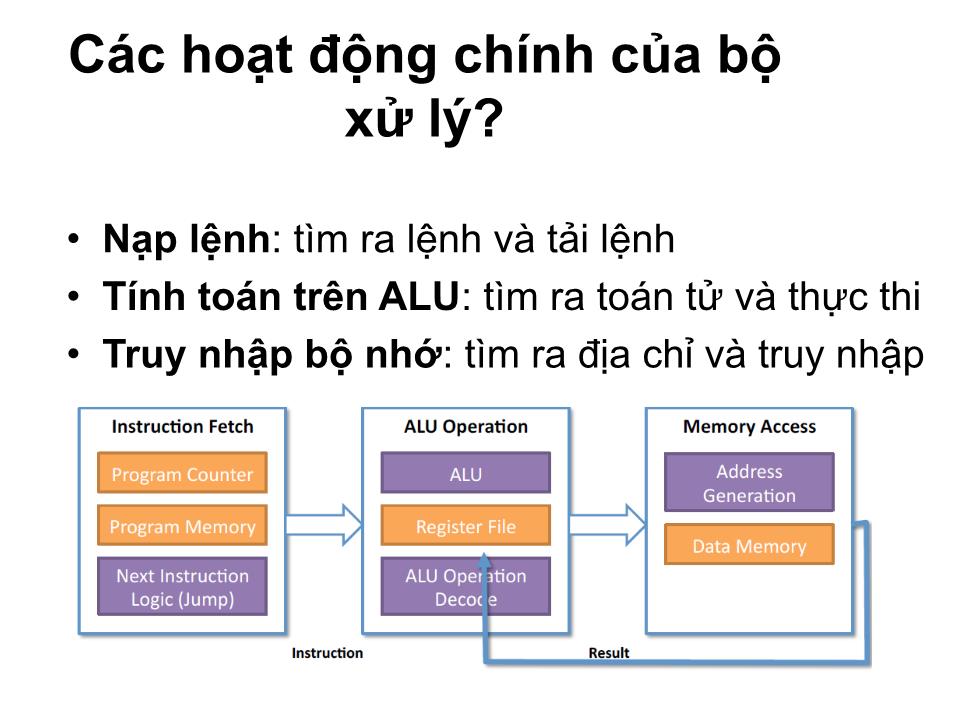

Thành phần cơ bản của bộ xử lý

– Lệnh truy cập

– Các toán tử ALU

– Toán tử bộ nhớ

Kết nối các thành phần

– Các tín hiệu điều khiển và bộ đồn kênh MUXes

– Các chỉ thị giải mã lệnh

Trang 1

Trang 2

Trang 3

Trang 4

Trang 5

Trang 6

Trang 7

Trang 8

Trang 9

Trang 10

Tải về để xem bản đầy đủ

Bạn đang xem 10 trang mẫu của tài liệu "Bài giảng Kiến trúc máy tính - Chương 3: Bộ xử lý Khối điều khiển và Đường dữ liệu - Tạ Kim Huệ", để tải tài liệu gốc về máy hãy click vào nút Download ở trên

Tóm tắt nội dung tài liệu: Bài giảng Kiến trúc máy tính - Chương 3: Bộ xử lý Khối điều khiển và Đường dữ liệu - Tạ Kim Huệ

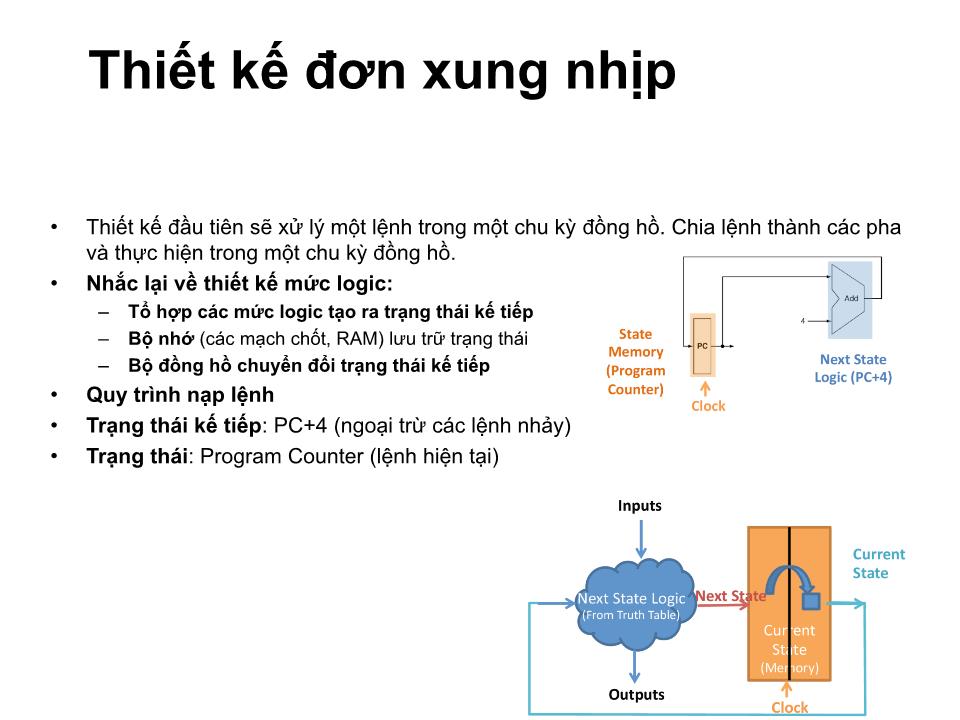

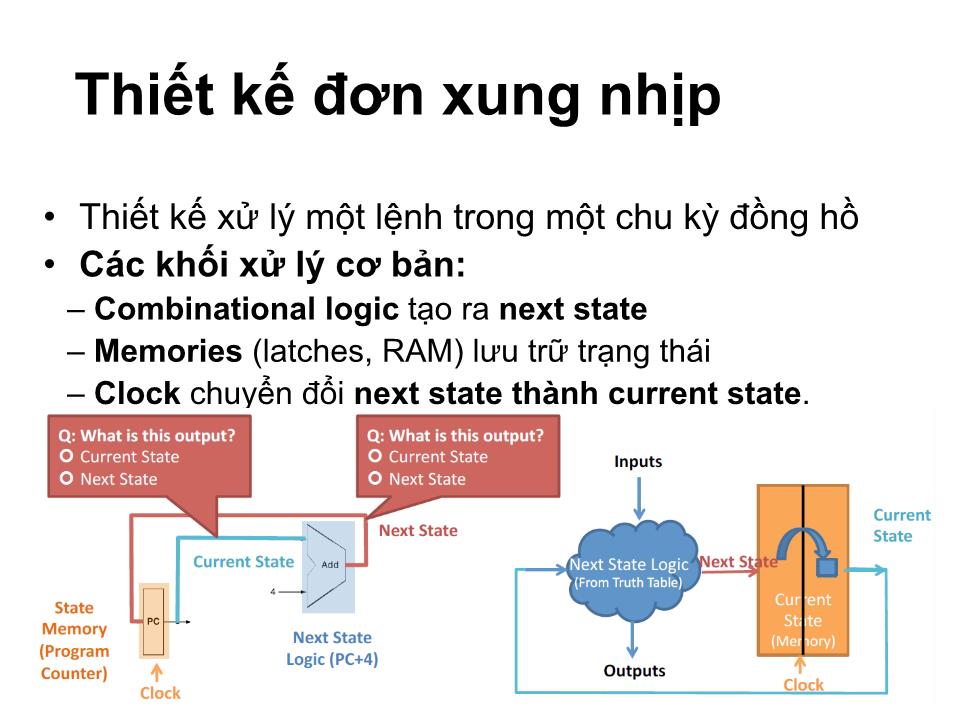

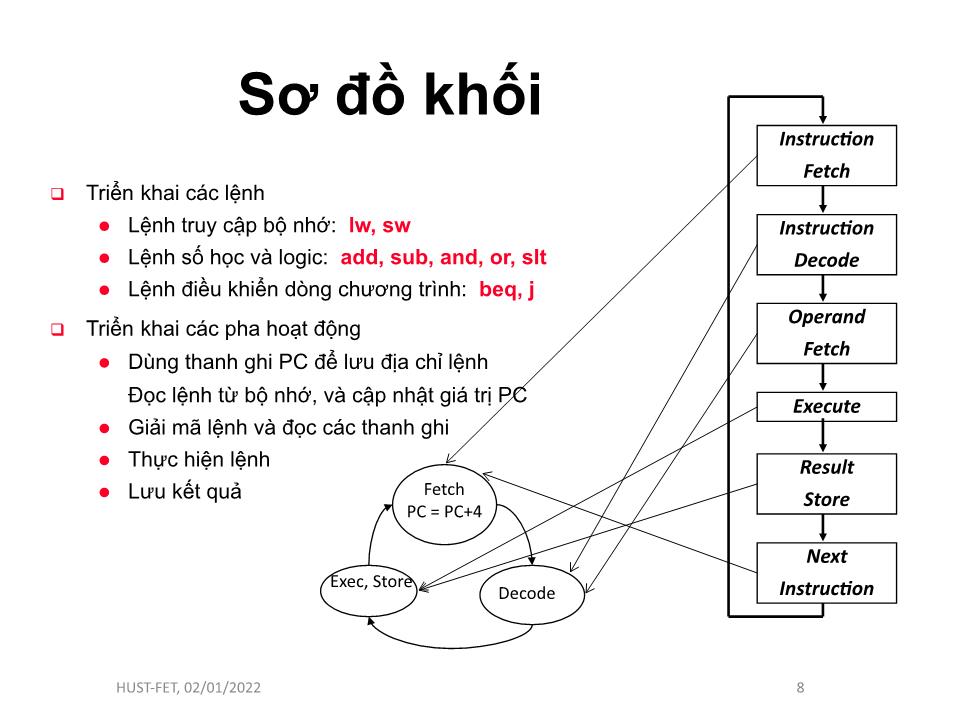

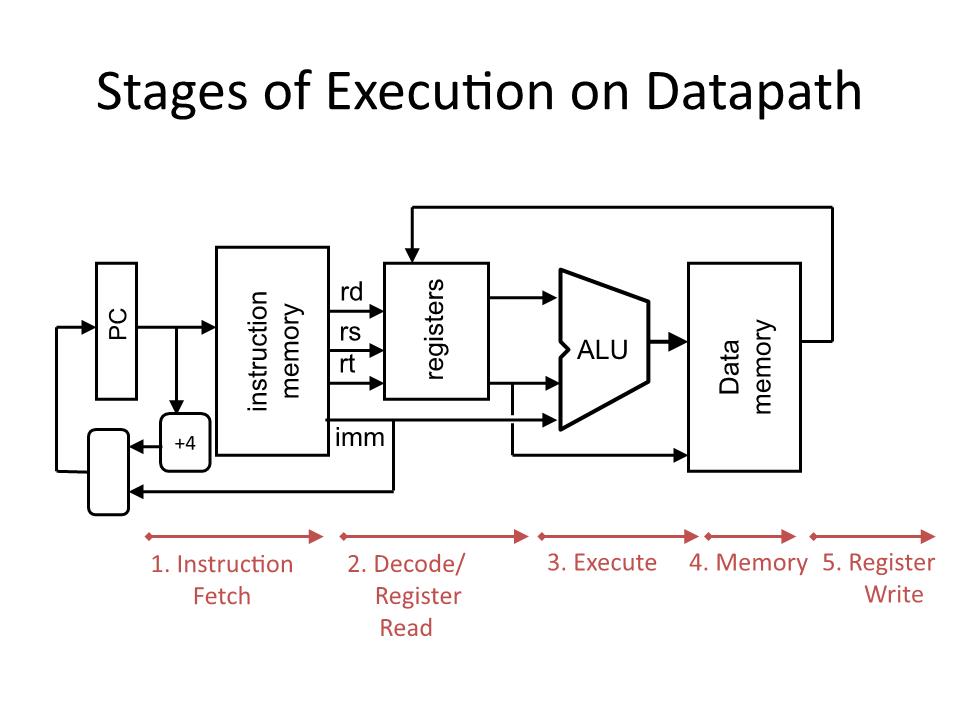

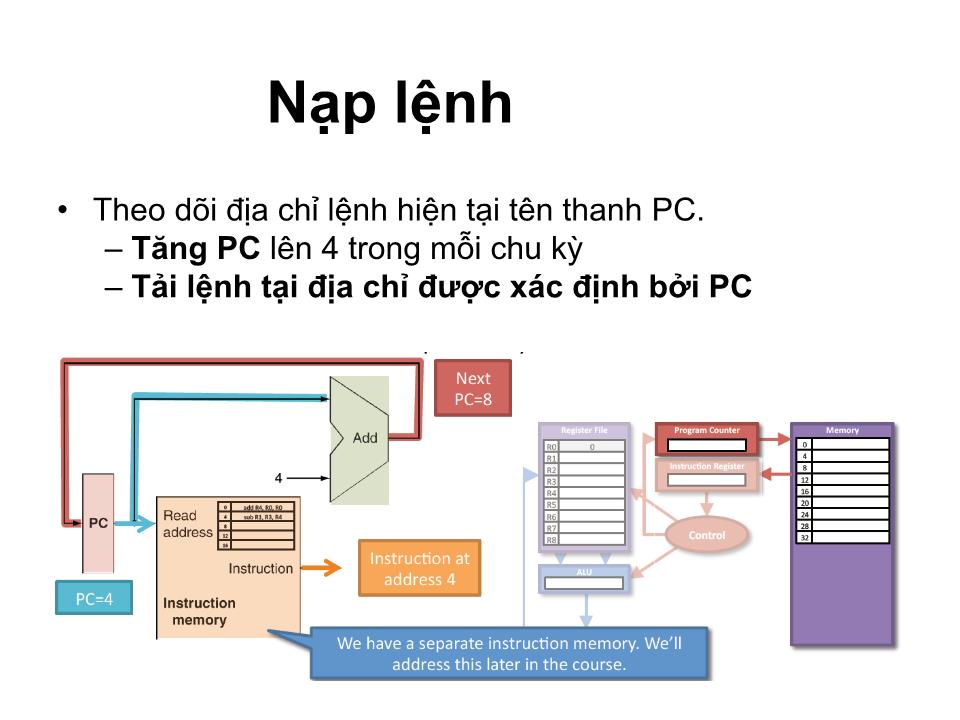

uction Decode Operand Fetch Execute Result Store Next Instruction Thực hiện lệnh HUST-FET, 03/01/2022 19 Thực hiện phép toán (mã hóa bới op và funct ) trên giá trị toán hạng opA và opB Các phép toán của lệnh R và I Phép toán tính địa chỉ trong lệnh lw, sw Phép toán so sánh trong lệnh beq, bne Instruction Fetch Instruction Decode Operand Fetch Execute Result Store Next Instruction opB ALU overflow zero ALU control opA result Tính toán trên ALU (các chỉ thị lệnh dạng R-type) Các bước thực hiện? – Đ ọc dữ liệu từ tệp thanh ghi (specify rs and rt ) – Thực thi tính toán ALU – Ghi dữ liệu về tệp thanh ghi (specify rd ) Tính toán trên ALU Các bước thực hiện? – Đ ọc dữ liệu từ tệp thanh ghi (xác định rõ rs và rt ) – Thực hiện tính toán ALU – Ghi dữ liệu trở lại tệp thanh ghi (xác định rõ rd ) Ghi kết quả HUST-FET, 03/01/2022 22 Từ ALU với các lệnh tính toán Từ bộ nhớ với các lệnh truy cập bộ nhớ Write Data Read Addr 1 Read Addr 2 Write Addr Register File Read Data 1 Read Data 2 RegWrite Instruction Fetch Instruction Decode Operand Fetch Execute Result Store Next Instruction Truy cập bộ nhớ HUST-FET, 03/01/2022 23 MemWrite MemRead Data Memory Address Write Data Read Data Địa chỉ theo byte Dữ liệu từ thanh ghi rt Instruction Fetch Instruction Decode Operand Fetch Execute Result Store Next Instruction Truy cập bộ nhớ Các bước thực hiện? – Tính toán địa chỉ – Gửi địa chỉ đến bộ nhớ dữ liệu (write: data) – Đọc: nhận kết quả trả về và đưa vào tệp thanh ghi Q: Điều gì xảy ra nếu đọc ghi vào bộ nhớ cùng một thời điểm 1/ không thể xảy ra 2/ dữ liệu sẽ bị sai lệch hoặc không hợp lệ 3/ không có vấn để gì cả vì có đầu ra đọc dữ liệu và đầu vào ghi dữ liệu A: 2 Hoạt động của RAM: kích hoạt một hàng đọc/ghi dữ liệu. Nếu thực hiện cả 2 cùng lúc sẽ làm các bit bị xáo trộn. Ngoài ra cần phải 2 địa chỉ cho quá trình ghi đọc Kết nối các thành phần • Bộ tính toán ALU – tải lệnh – tính toán giá trị tiếp theo của PC – đọc từ tệp thanh ghi – thực thi tính toán – ghi lại tệp thanh ghi • Truy nhập bộ nhớ (load/store) – tải lệnh – tính toán giá trị tiếp theo củaPC – đọc từ tệp thanh ghi – tính toán địa chỉ – Read/Write dữ liệu bộ – Write dữ liệu vào tệp thanh ghi • Nạp lệnh (branch) – tải lệnh – tính toán giá trị tiếp theo của PC – đọc từ tệp thanh ghi Tính toán địa chỉ rẽ nhánh: không sử dụng ALU cho phép toán so sánh và tính toán địa chỉ cùng một thời điểm . – thực thi các nhánh so sánh – cập nhật lại giá trị của PC Kết nối RF và ALU Kết nối ALU với bộ nhớ Kết nối giá trị tức thời để tính toán địa chỉ Thêm vào bộ dồn kênh Lựa chọn tín hiệu bằng Bộ dồn kênh MUX Định tuyến tính hiệu (control) • MUX lựa chọn ALU input (tệp thanh ghi hoặc các giá trị hằng số có dấu tức thời) • MUX lựa chọn tệp thanh ghi ghi dữ liệu (kết quả tính toán được tại ALU hoặc dữ liệu từ bộ nhớ) Các tín hiệu điều khiển xác định hoạt động: Lệnh addi Định nghĩa về tín hiệu điều khiển: ALUSrc (ALU source) và MemtoReg (Memory to Register File) Các tín hiệu điều khiển xác định hoạt động: lệnh add Xây dựng các khối rẽ nhánh có điều kiện Các bước thực hiện? – Mặc định: PC = PC + 4 – Trường hợp có điều kiện : PC = PC + 4 + [Sign-extended immediate << 2] if branch Tín hiệu PCSrc Các bước thực hiện? – Mặc định: PC = PC + 4 – Trường hợp có điều kiện: PC = PC+4+[Sign-extended immediate << 2] if branch Đường tín hiệu đơn xung nhịp trong MIPS Các dữ liệu nguồn (dữ liệu lấy ra ở đâu? ) Các dữ liệu đích (dữ liệu đi đến đâu?) Ví dụ: addi Lặp lại quá trình Thực hiện lệnh loại R và ghi kết quả HUST-FET, 03/01/2022 40 Lệnh định dạng R ( add, sub, slt, and, or ) Thực hiện phép toán (mã hóa bới op và funct ) trên giá trị toạn hạng trong rs và rt Ghi kết quả vào tệp thanh ghi (tại vị trí rd ) Instruction Write Data Read Addr 1 Read Addr 2 Write Addr Register File Read Data 1 Read Data 2 ALU overflow zero ALU control RegWrite R-type: 31 25 20 15 5 0 op rs rt rd funct shamt 10 Tệp thanh ghi không được ghi ở mọi chu kỳ cần tín hiệu điều khiển ghi riêng biệt. Instruction Fetch Instruction Decode Operand Fetch Execute Result Store Next Instruction Đọc ghi bộ nhớ HUST-FET, 03/01/2022 41 Địa chỉ bộ nhớ tính ở bước EX: cộng thanh ghi cơ sở (đọc từ tệp thanh ghi khi giải mã lệnh) với giá trị offset ghi (sw) giá trị (được đọc từ tệp thanh ghi khi giải mã lệnh) vào bộ nhớ dữ liệu đọc (lw) giá trị từ bộ nhớ dữ liệu vào tệp thanh ghi Instruction Write Data Read Addr 1 Read Addr 2 Write Addr Register File Read Data 1 Read Data 2 ALU overflow zero ALU control RegWrite Data Memory Address Write Data Read Data Sign Extend MemWrite MemRead 16 32 Instruction Fetch Instruction Decode Operand Fetch Execute Result Store Next Instruction Lệnh rẽ nhánh có điều kiện HUST-FET, 03/01/2022 42 S o sánh toán hạng đọc từ tệp thanh ghi khi giải mã T ính địa chỉ đích bằng cách cộng giá trị PC (sau khi cập nhât) với trường offset 16 bit đã được mở rộng dấu. Instruction Write Data Read Addr 1 Read Addr 2 Write Addr Register File Read Data 1 Read Data 2 ALU zero ALU control Sign Extend 16 32 Shift left 2 Add 4 Add PC Branch target address (to branch control logic) Instruction Fetch Instruction Decode Operand Fetch Execute Result Store Next Instruction Lệnh nhảy không điều kiện HUST-FET, 03/01/2022 43 Thay 28 bit thấp của PC bằng 26 bít thấp của lệnh được nạp và 2 bít 0 Read Address Instruction Instruction Memory Add PC 4 Shift left 2 Jump address 26 4 28 Instruction Fetch Instruction Decode Operand Fetch Execute Result Store Next Instruction Đường dữ liệu: Lệnh R, I, lw,sw HUST-FET, 03/01/2022 44 MemtoReg Read Address Instruction Instruction Memory Add PC 4 Write Data Read Addr 1 Read Addr 2 Write Addr Register File Read Data 1 Read Data 2 ALU ovf zero ALU control RegWrite Data Memory Address Write Data Read Data MemWrite MemRead Sign Extend 16 32 ALUSrc Đường dữ liệu: Lệnh rẽ nhánh HUST-FET, 03/01/2022 45 Instr[5-0] Read Address Instr[31-0] Instruction Memory Add PC 4 Write Data Read Addr 1 Read Addr 2 Write Addr Register File Read Data 1 Read Data 2 ALU ovf zero RegWrite Sign Extend 16 32 ALUSrc Shift left 2 Add PCSrc RegDst ALU control 1 1 0 0 0 1 ALUOp Instr[15-0] Instr[25-21] Instr[20-16] Instr[15 -11] Control Unit Instr[31-26] Branch Đường dữ liệu: Lệnh R,I, lw, sw, beq, bne HUST-FET, 03/01/2022 46 Read Address Instr[31-0] Instruction Memory Add PC 4 Write Data Read Addr 1 Read Addr 2 Write Addr Register File Read Data 1 Read Data 2 ALU ovf zero RegWrite Data Memory Address Write Data Read Data MemWrite MemRead Sign Extend 16 32 MemtoReg ALUSrc Shift left 2 Add PCSrc RegDst ALU control 1 1 1 0 0 0 0 1 ALUOp Instr[5-0] Instr[15-0] Instr[25-21] Instr[20-16] Instr[15 -11] Control Unit Instr[31-26] Branch Bộ xử lý đơn xung nhịp (2) – Lệnh R HUST-FET, 03/01/2022 47 Read Address Instr[31-0] Instruction Memory Add PC 4 Write Data Read Addr 1 Read Addr 2 Write Addr Register File Read Data 1 Read Data 2 ALU ovf zero RegWrite Data Memory Address Write Data Read Data MemWrite MemRead Sign Extend 16 32 MemtoReg ALUSrc Shift left 2 Add PCSrc RegDst ALU control 1 1 1 0 0 0 0 1 ALUOp Instr[5-0] Instr[15-0] Instr[25-21] Instr[20-16] Instr[15 -11] Control Unit Instr[31-26] Branch BXL đơn xung nhịp (3) – Lệnh lw, sw HUST-FET, 03/01/2022 48 Read Address Instr[31-0] Instruction Memory Add PC 4 Write Data Read Addr 1 Read Addr 2 Write Addr Register File Read Data 1 Read Data 2 ALU ovf zero RegWrite Data Memory Address Write Data Read Data MemWrite MemRead Sign Extend 16 32 MemtoReg ALUSrc Shift left 2 Add PCSrc RegDst ALU control 1 1 1 0 0 0 0 1 ALUOp Instr[5-0] Instr[15-0] Instr[25-21] Instr[20-16] Instr[15 -11] Control Unit Instr[31-26] Branch BXL đơn xung nhịp (3) – Lệnh lw, sw HUST-FET, 03/01/2022 49 Read Address Instr[31-0] Instruction Memory Add PC 4 Write Data Read Addr 1 Read Addr 2 Write Addr Register File Read Data 1 Read Data 2 ALU ovf zero RegWrite Data Memory Address Write Data Read Data MemWrite MemRead Sign Extend 16 32 MemtoReg ALUSrc Shift left 2 Add PCSrc RegDst ALU control 1 1 1 0 0 0 0 1 ALUOp Instr[5-0] Instr[15-0] Instr[25-21] Instr[20-16] Instr[15 -11] Control Unit Instr[31-26] Branch BXL đơn xung nhịp (4) – Lệnh rẽ nhánh HUST-FET, 03/01/2022 50 Read Address Instr[31-0] Instruction Memory Add PC 4 Write Data Read Addr 1 Read Addr 2 Write Addr Register File Read Data 1 Read Data 2 ALU ovf zero RegWrite Data Memory Address Write Data Read Data MemWrite MemRead Sign Extend 16 32 MemtoReg ALUSrc Shift left 2 Add PCSrc RegDst ALU control 1 1 1 0 0 0 0 1 ALUOp Instr[5-0] Instr[15-0] Instr[25-21] Instr[20-16] Instr[15 -11] Control Unit Instr[31-26] Branch BXL đơn xung nhịp (4) – Lệnh rẽ nhánh HUST-FET, 03/01/2022 51 Read Address Instr[31-0] Instruction Memory Add PC 4 Write Data Read Addr 1 Read Addr 2 Write Addr Register File Read Data 1 Read Data 2 ALU ovf zero RegWrite Data Memory Address Write Data Read Data MemWrite MemRead Sign Extend 16 32 MemtoReg ALUSrc Shift left 2 Add PCSrc RegDst ALU control 1 1 1 0 0 0 0 1 ALUOp Instr[5-0] Instr[15-0] Instr[25-21] Instr[20-16] Instr[15 -11] Control Unit Instr[31-26] Branch BXL đơn xung nhịp – Thêm lệnh nhảy HUST-FET, 03/01/2022 52 Read Address Instr[31-0] Instruction Memory Add PC 4 Write Data Read Addr 1 Read Addr 2 Write Addr Register File Read Data 1 Read Data 2 ALU ovf zero RegWrite Data Memory Address Write Data Read Data MemWrite MemRead Sign Extend 16 32 MemtoReg ALUSrc Shift left 2 Add PCSrc RegDst ALU control 1 1 1 0 0 0 0 1 ALUOp Instr[5-0] Instr[15-0] Instr[25-21] Instr[20-16] Instr[15 -11] Control Unit Instr[31-26] Branch Shift left 2 0 1 Jump 32 Instr[25-0] 26 PC+4[31-28] 28 PC + 4 Thiết kế đồng bộ theo đồng hồ HUST-FET, 03/01/2022 Mạch đồng bộ theo đồng hồ: 1 phần tử trạng thái là hợp lệ và ổn định được quy định bởi xung đồng hồ Phần tử trạng thái - phần tử nhớ - VD. thanh ghi, bộ nhớ lệnh, bộ nhớ dữ liệu. Kích hoạt theo s ườn – các trạng thái thay đối khi có s ườn xung Đọc nội dung của phần tử trạng thái tính giá trị bằng logic tổ hợp ghi kết quả vào phần tử trạng thái Các phần tử trạng thái được ghi ở tất cả các chu kỳ đồng hồ. State element 1 State element 2 Combinational logic clock one clock cycle Đồng hồ ở đâu? Ví dụ: Lệnh addi thực thi như thế nào? Khi có tín hiệu đồng hồ, biến mới được lưu trữ Lặp lại quá trình Ví dụ lệnh: addi Các tuyến logic và các bộ trễ Tốc độ xử lý xác định như thế nào? Tính chu ky đồng hồ T c – Đường dài nhất HUST-FET, 03/01/2022 Instr. I Mem Reg Rd ALU Op D Mem Reg Wr Total R-type 2 1 2 1 6ns load 2 1 2 2 1 8ns store 2 1 2 2 7ns beq 2 1 2 5ns jump 2 2ns Tính chu kỳ đồng hồ trong trường hợp bỏ qua trễ ở bộ ghép, khối điều khiển, khối mở rộng dấu, khối đọc PC, khối dịch 2, dây dẫn, thời gian thiết lập và giữ. Cho biết độ trễ : - Truy cập bộ nhớ lệnh và bộ nhớ dữ liệu (2ns) - Khối số học logic và bộ cộng (2 ns) - Truy cập tệp thanh ghi (đọc hoặc ghi ) (1 ns) Hiệu năng thiết kế đơn xung nhịp HUST-FET, 03/01/2022 Độ trễ logic khi Truy cập lệnh 2 ns Đọc thanh ghi 1 ns Hoạt động ALU 2 ns Truy cập bộ nhớ DL 2 ns Ghi thanh ghi 1 ns Tổng 8 ns Tốc độ đồng hồ = 125 MHz Các loại lệnh: R-type 44% 6 ns Load 24% 8 ns Store 12% 7 ns Branch 18% 5 ns Jump 2% 4 ns Thời gian trung bình 6.38 ns CPI = 1. Thiết kế đơn xung nhịp – Ưu nhược điểm HUST-FET, 03/01/2022 63 Sử dụng chu kỳ đồng hồ không hiệu quả – chu kỳ đồng hồ được đặt theo lệnh chậm nhất . Các lệnh phức tạp như lệnh nhân dấu phẩy động: Tốn diện tích thiết kế vì cần nhân đôi một số khối chức năng (VD. bộ cộng) vì chúng không thể được chia sẻ trong cùng 1 chu kỳ đồng hồ Đơn giản và dễ hiểu Clk lw sw Waste Cycle 1 Cycle 2 Thiết kế đa xung nhịp HUST-FET, 03/01/2022 64 Chia lệnh thành các pha thực hiện: IF, ID, EX, MEM, WB. Mỗi pha thực hiện trong 1 chu kỳ xung nhịp Thời gian thực hiện (= số pha) của mỗi lệnh được điều chỉnh tùy thuộc độ phức tạp của lệnh Các khối chức năng được chia sẻ giữa các pha khác nhau của lệnh do một khối chức năng cụ thể không cần trong toàn bộ các pha thực hiện của lệnh Hiệu năng thiết kế đa xung nhịp HUST-FET, 03/01/2022 Các loại lệnh sử dụng số chu kỳ khác nhau R-type 44% 4 cycles Load 24% 5 cycles Store 12% 4 cycles Branch 18% 3 cycles Jump 2% 2 cycles Đóng góp vào số chu kỳ trung bình cần cho một lệnh: R-type Load Store Branch Jump _____________________________ CPI trung bình Hiệu năng thiết kế đa xung nhịp HUST-FET, 03/01/2022 66 Các loại lệnh sử dụng số chu kỳ khác nhau R-type 44% 4 cycles Load 24% 5 cycles Store 12% 4 cycles Branch 18% 3 cycles Jump 2% 2 cycles Tính số chu kỳ trung bình cần cho một lệnh: R-type 0.44 4 = 1.76 Load 0.24 5 = 1.20 Store 0.12 4 = 0.48 Branch 0.18 3 = 0.54 Jump 0.02 2 = 0.04 _____________________________ CPI trung bình 4.02 So sánh hiệu năng xử lý So sánh hiệu năng xử lý của thiết kế đa xung nhịp và thiết đơn xung nhịp, biết tần suất xuất hiện các lệnh như sau: lw : 20% sw: 20% R - : 45 % beq: 15% Thiết kế đơn xung nhịp HUST-FET, 03/01/2022 68 Clock rate = 125 MHz CPI = 1 (125 MIPS) Thiết kế đa xung nhịp HUST-FET, 03/01/2022 69 Clock rate = 500 MHz CPI 4 ( 125 MIPS) 2

File đính kèm:

bai_giang_kien_truc_may_tinh_chuong_3_bo_xu_ly_khoi_dieu_khi.pptx

bai_giang_kien_truc_may_tinh_chuong_3_bo_xu_ly_khoi_dieu_khi.pptx