Bài giảng Hệ thống máy tính và ngôn ngữ C - Chương 3: Các cấu trúc luận lý số

3.1 Transistor

3.2 Cổng luận lý (Logic gate)

3.3 Mạch tổ hợp (Combinational circuit)

3.4 Phần tử nhớ cơ bản

3.5 Bộ nhớ (Memory)

3.6 Mạch tuần tự (Sequential logic circuit)

3.7 Đƣờng truyền dữ liệu LC3

Trang 1

Trang 2

Trang 3

Trang 4

Trang 5

Trang 6

Trang 7

Trang 8

Trang 9

Trang 10

Tải về để xem bản đầy đủ

Bạn đang xem 10 trang mẫu của tài liệu "Bài giảng Hệ thống máy tính và ngôn ngữ C - Chương 3: Các cấu trúc luận lý số", để tải tài liệu gốc về máy hãy click vào nút Download ở trên

Tóm tắt nội dung tài liệu: Bài giảng Hệ thống máy tính và ngôn ngữ C - Chương 3: Các cấu trúc luận lý số

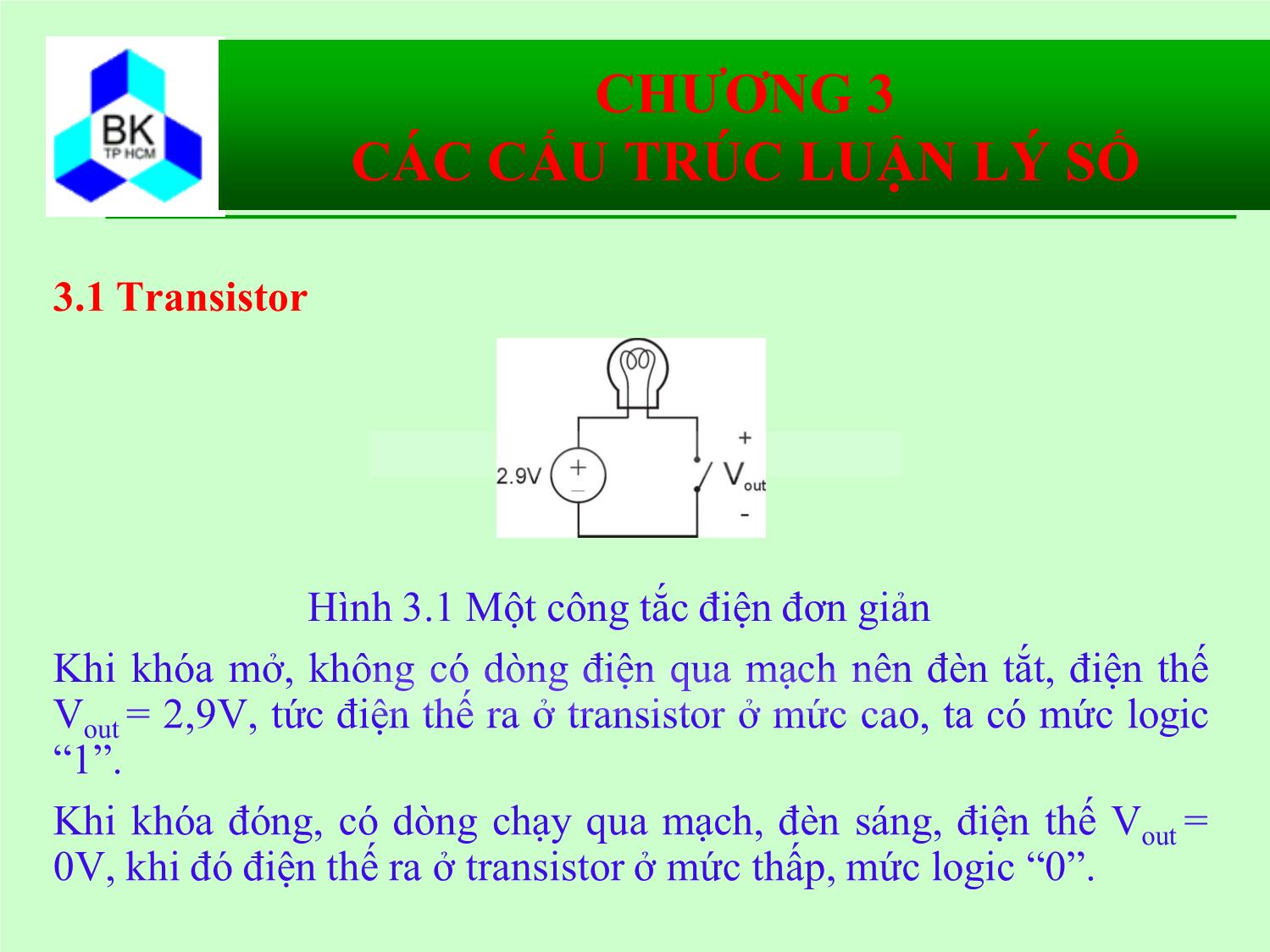

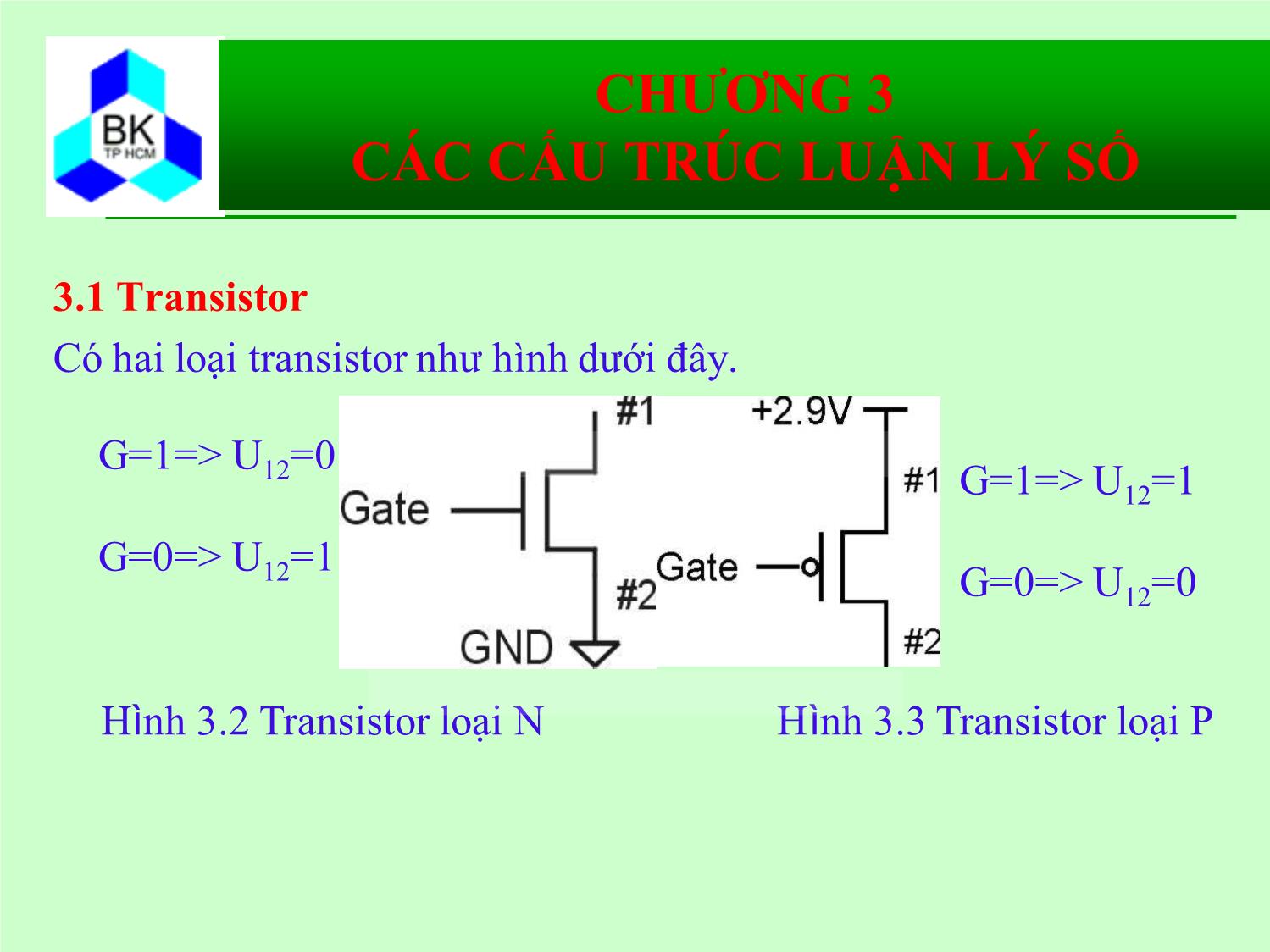

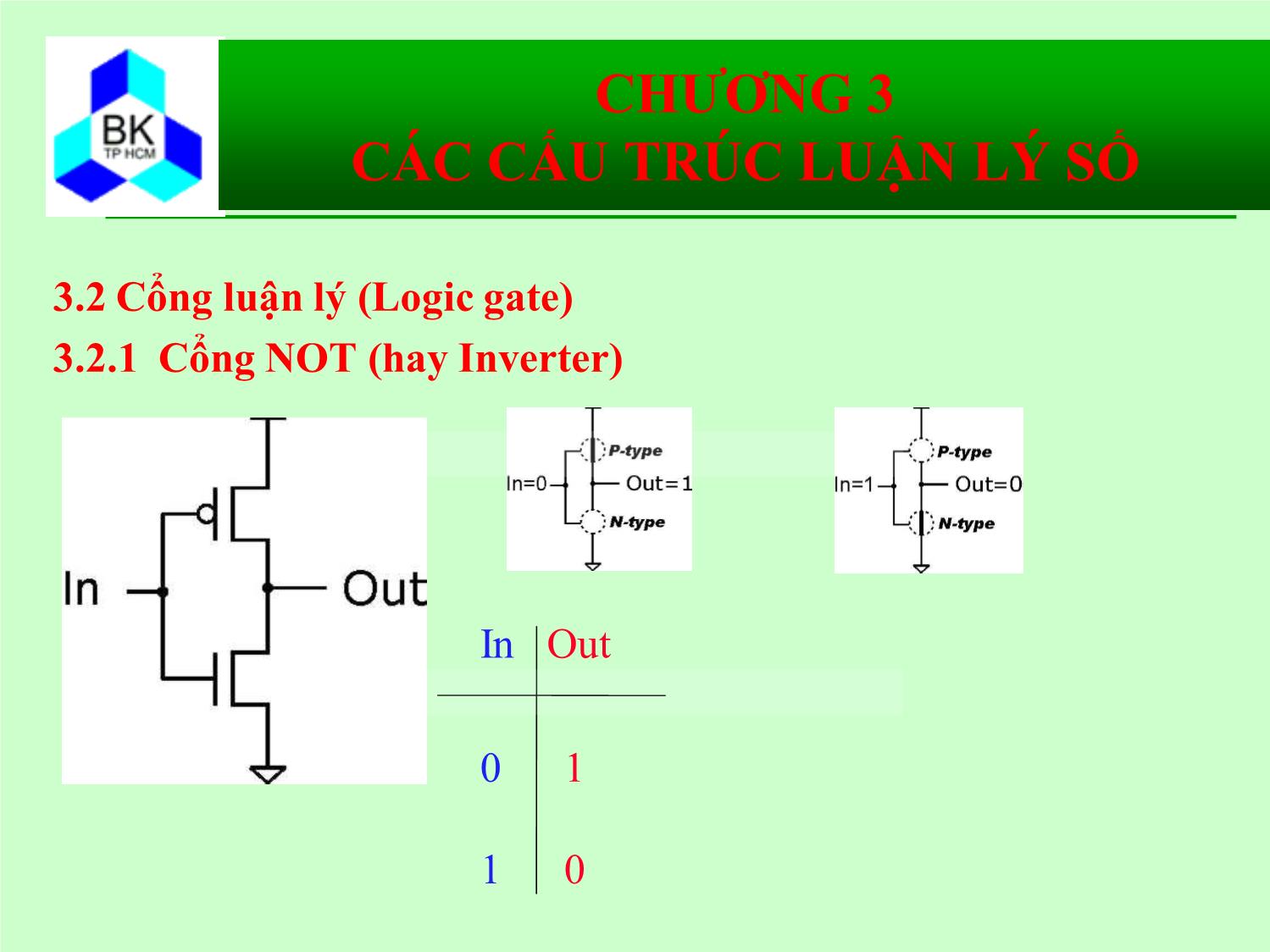

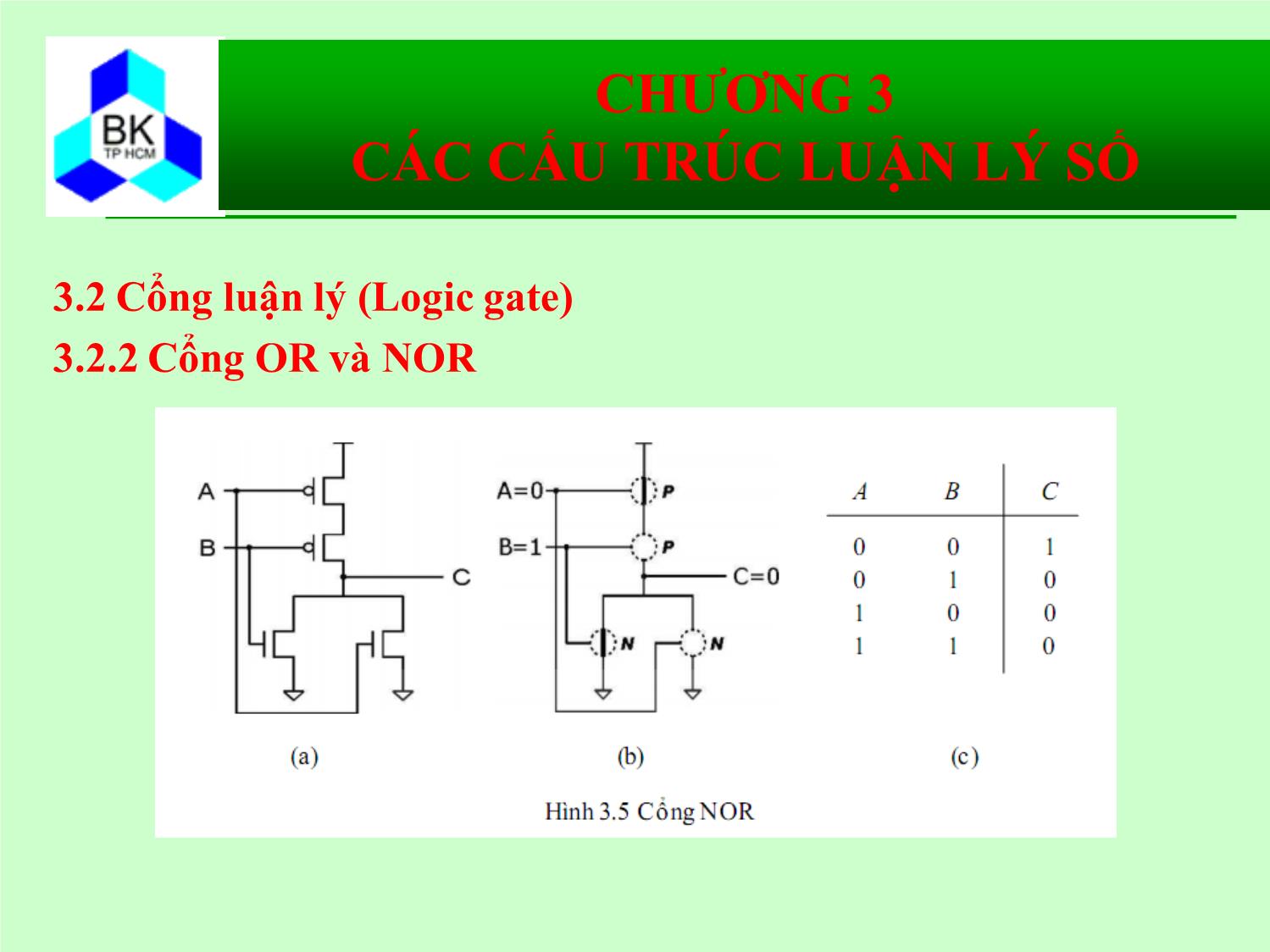

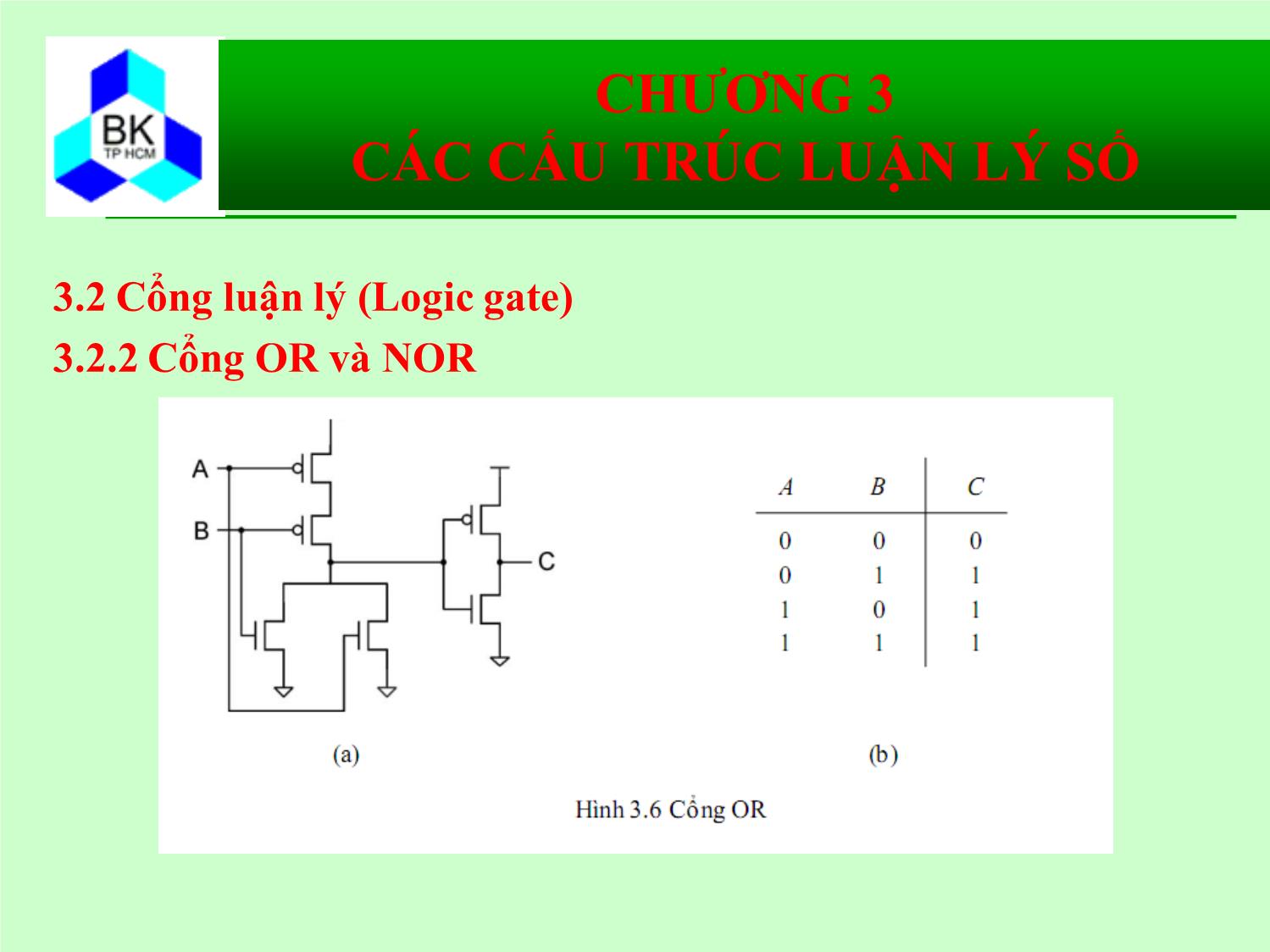

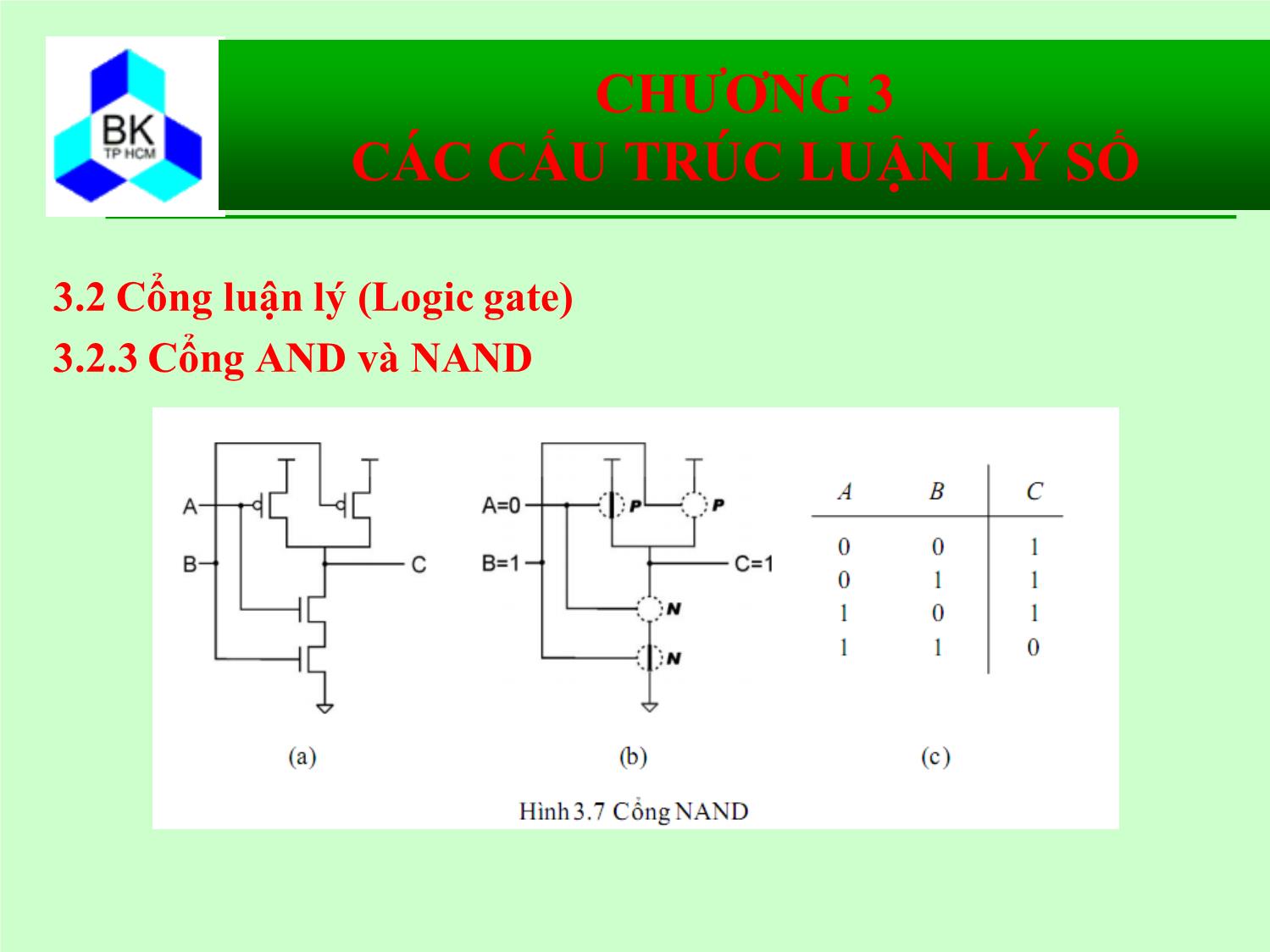

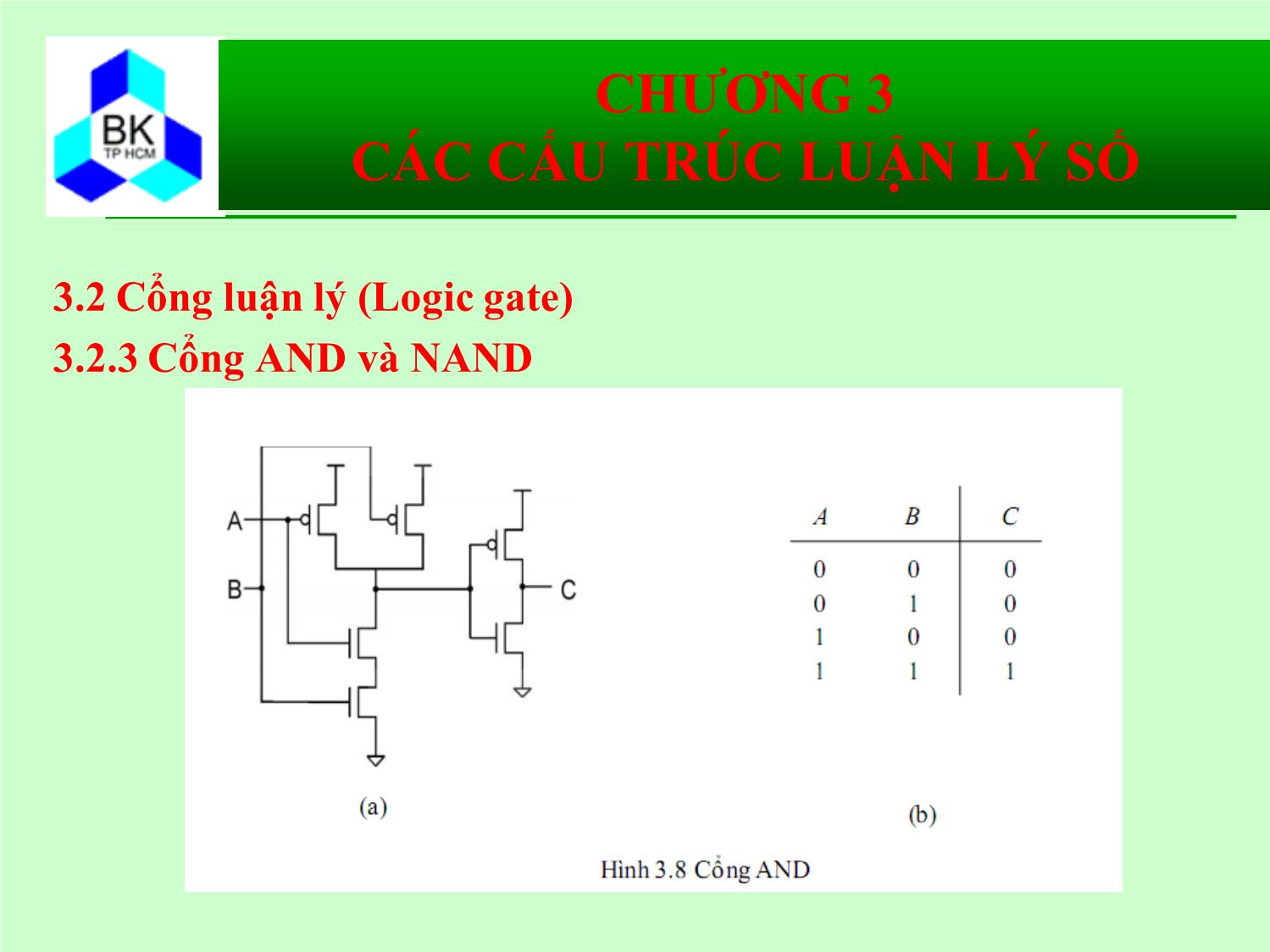

CHƢƠNG 3 CÁC CẤU TRÚC LUẬN LÝ SỐ CHƢƠNG 3 CÁC CẤU TRÚC LUẬN LÝ SỐ 3.1 Transistor 3.2 Cổng luận lý (Logic gate) 3.3 Mạch tổ hợp (Combinational circuit) 3.4 Phần tử nhớ cơ bản 3.5 Bộ nhớ (Memory) 3.6 Mạch tuần tự (Sequential logic circuit) 3.7 Đƣờng truyền dữ liệu LC3 CHƢƠNG 3 CÁC CẤU TRÚC LUẬN LÝ SỐ 3.1 Transistor Đa số máy tính ngày nay xử dụng các bộ vi xử lý (microprocessor) được tạo từ các transistor họ MOS. (metal-oxide-semiconductor). Có hai loại transistor MOS: loại P (Positive) và loại N (Negative). CHƢƠNG 3 CÁC CẤU TRÚC LUẬN LÝ SỐ 3.1 Transistor Hình 3.1 Một công tắc điện đơn giản Khi khóa mở, không có dòng điện qua mạch nên đèn tắt, điện thế Vout = 2,9V, tức điện thế ra ở transistor ở mức cao, ta có mức logic “1”. Khi khóa đóng, có dòng chạy qua mạch, đèn sáng, điện thế Vout = 0V, khi đó điện thế ra ở transistor ở mức thấp, mức logic “0”. CHƢƠNG 3 CÁC CẤU TRÚC LUẬN LÝ SỐ 3.1 Transistor Có hai loại transistor như hình dưới đây. Hình 3.2 Transistor loại N Hình 3.3 Transistor loại P G=1=> U12=0 G=0=> U12=1 G=1=> U12=1 G=0=> U12=0 CHƢƠNG 3 CÁC CẤU TRÚC LUẬN LÝ SỐ 3.2 Cổng luận lý (Logic gate) Các cổng luận lý cơ bản AND, OR, và NOT Tầm trị điện áp analog từ 0-2,9V: - Điện thế từ 0-0,5V => mức logic 0 - Điện thế từ 2,4V – 2,9V => mức logic 1 CHƢƠNG 3 CÁC CẤU TRÚC LUẬN LÝ SỐ 3.2 Cổng luận lý (Logic gate) 3.2.1 Cổng NOT (hay Inverter) In Out 0 1 1 0 CHƢƠNG 3 CÁC CẤU TRÚC LUẬN LÝ SỐ 3.2 Cổng luận lý (Logic gate) 3.2.2 Cổng OR và NOR CHƢƠNG 3 CÁC CẤU TRÚC LUẬN LÝ SỐ 3.2 Cổng luận lý (Logic gate) 3.2.2 Cổng OR và NOR CHƢƠNG 3 CÁC CẤU TRÚC LUẬN LÝ SỐ 3.2 Cổng luận lý (Logic gate) 3.2.3 Cổng AND và NAND CHƢƠNG 3 CÁC CẤU TRÚC LUẬN LÝ SỐ 3.2 Cổng luận lý (Logic gate) 3.2.3 Cổng AND và NAND CHƢƠNG 3 CÁC CẤU TRÚC LUẬN LÝ SỐ 3.2 Cổng luận lý (Logic gate) Các ký hiệu theo quy ước cho các cổng logic cơ bản: CHƢƠNG 3 CÁC CẤU TRÚC LUẬN LÝ SỐ 3.2 Cổng luận lý (Logic gate) Khi muốn biểu diễn nhiều đầu vào, chúng ta có thể sử dụng quy ước như hình 3.10, thay vì dùng nhiều tầng cổng AND. Các cổng khác cũng có sự tương tự. CHƢƠNG 3 CÁC CẤU TRÚC LUẬN LÝ SỐ 3.2 Cổng luận lý (Logic gate) 3.2.4 Định luật De Morgan Luật De Morgan cho phép chúng ta biểu diễn cổng OR bằng cổng AND kèm theo một số cổng NOT, hay ngược lại. Có hai luật De Morgan 1 và De Morgan 2 như sau: hay viết ở dạng khác là Với ký hiệu „+‟ đặc trưng cho phép OR, và „.‟ cho phép AND. CHƢƠNG 3 CÁC CẤU TRÚC LUẬN LÝ SỐ 3.2 Cổng luận lý (Logic gate) 3.2.4 Định luật De Morgan CHƢƠNG 3 CÁC CẤU TRÚC LUẬN LÝ SỐ 3.3 Mạch tổ hợp (Combinational circuit) Có hai loại cấu trúc luận lý cơ bản là mạch tổ hợp và mạch tuần tự. •Cấu trúc mạch tổ hợp là mạch luận lý mà các giá trị đầu ra của nó phụ thuộc vào tổ hợp các giá trị đầu vào của nó ở cùng thời điểm. •Mạch tuần tự có thể giữ được thông tin, và làm cơ sở cho cấu trúc bộ nhớ của máy tính. Có ba loại tổ hợp mà chúng ta xét trong phần này: mạch giải mã, mạch phân kênh, và bộ cộng toàn phần. CHƢƠNG 3 CÁC CẤU TRÚC LUẬN LÝ SỐ 3.3 Mạch tổ hợp (Combinational circuit) 3.3.1 Mạch giải mã (Decoder) n ngõ vào và 2n ngõ ra CHƢƠNG 3 CÁC CẤU TRÚC LUẬN LÝ SỐ 3.3 Mạch tổ hợp (Combinational circuit) 3.3.2 Mạch phân kênh (Multiplexer) 2n ngõ vào, n ngõ lựa chọn và 1 ngõ ra CHƢƠNG 3 CÁC CẤU TRÚC LUẬN LÝ SỐ 3.3 Mạch tổ hợp (Combinational circuit) 3.3.3 Mạch cộng toàn phần (Full adder) CHƢƠNG 3 CÁC CẤU TRÚC LUẬN LÝ SỐ 3.3 Mạch tổ hợp (Combinational circuit) 3.3.3 Mạch cộng toàn phần (Full adder) CHƢƠNG 3 CÁC CẤU TRÚC LUẬN LÝ SỐ 3.3 Mạch tổ hợp (Combinational circuit) 3.3.4 Một ví dụ về thiết kế mạch tổ hợp Ví dụ 3.1: Thiết kế mạch kiểm tra sự chiếm đa số của bit 1 từ ba bit đầu vào (majority function). Ta có bảng sự thật ở hình 3.17a. Vì là yêu cầu kiểm tra sự chiếm đa số của bit 1 từ ba bit đầu vào (A, B, C), nên đầu ra (M) sẽ là 1 khi số bit 1 ở đầu vào là từ 2 trở lên. Như vậy, ta có hàm logic sau đây: CHƢƠNG 3 CÁC CẤU TRÚC LUẬN LÝ SỐ 3.3 Mạch tổ hợp (Combinational circuit) 3.3.4 Một ví dụ về thiết kế mạch tổ hợp CHƢƠNG 3 CÁC CẤU TRÚC LUẬN LÝ SỐ 3.4 Phần tử nhớ cơ bản 3.4.1 Mạch cài R-S (R-S latch) CHƢƠNG 3 CÁC CẤU TRÚC LUẬN LÝ SỐ 3.4 Phần tử nhớ cơ bản 3.4.1 Mạch cài R-S (R-S latch) CHƢƠNG 3 CÁC CẤU TRÚC LUẬN LÝ SỐ 3.4 Phần tử nhớ cơ bản 3.4.1 Mạch cài R-S (R-S latch) CHƢƠNG 3 CÁC CẤU TRÚC LUẬN LÝ SỐ 3.4 Phần tử nhớ cơ bản 3.4.2 Mạch cài D (D latch) WE: Write Enable CHƢƠNG 3 CÁC CẤU TRÚC LUẬN LÝ SỐ 3.4 Phần tử nhớ cơ bản 3.4.3 Thanh ghi (Register) CHƢƠNG 3 CÁC CẤU TRÚC LUẬN LÝ SỐ 3.4 Phần tử nhớ cơ bản 3.4.3 Thanh ghi (Register) Nếu số nhị phân có n bit, thì bit ngoài cùng bên trái sẽ là bit [n-1]. Thí dụ, trong mẫu Q 16 bit sau: 0011101100011110 thì bit Q[15] là 0, bit Q[14] là 0, bit Q[13] là 1, Q[15 :13] là 001. CHƢƠNG 3 CÁC CẤU TRÚC LUẬN LÝ SỐ 3.5 Bộ nhớ (Memory) Bộ nhớ gồm nhiều ô nhớ (memory location), còn được gọi là từ, mỗi ô nhớ có địa chỉ riêng. Mỗi ô nhớ có nhiều bit, và mỗi bit là một bộ cài D. Như vậy, bộ nhớ được đặc trưng bởi hai yếu tố: số ô nhớ và số bit trong mỗi ô nhớ . CHƢƠNG 3 CÁC CẤU TRÚC LUẬN LÝ SỐ 3.5 Bộ nhớ (Memory) CHƢƠNG 3 CÁC CẤU TRÚC LUẬN LÝ SỐ 3.5 Bộ nhớ (Memory) Nếu ta có n bit địa chỉ cho tổ hợp địa chỉ nhị phân của ô nhớ thì dung lượng bộ nhớ sẽ là k = 2n ô nhớ. Thí dụ, khi nói máy tính có dung lượng 4 GB, có nghĩa là máy tính đó có số ô nhớ 4 x 230 và mỗi ô nhớ là một byte, tức bộ nhớ máy tính đó có hơn 4 tỷ byte. CHƢƠNG 3 CÁC CẤU TRÚC LUẬN LÝ SỐ 3.5 Bộ nhớ (Memory) CHƢƠNG 3 CÁC CẤU TRÚC LUẬN LÝ SỐ 3.5 Bộ nhớ (Memory) CHƢƠNG 3 CÁC CẤU TRÚC LUẬN LÝ SỐ 3.5 Bộ nhớ (Memory) Ví dụ 3.2: Thiết kế bộ nhớ 8K bằng 4 chip 2K x 8 bit. Với 4 chip nhớ này, mỗi chip nhớ có dung lương 2K, nên số đường địa chỉ cần để mã hóa cho mỗi ô nhớ trong từng chip là 211 (=2K), tức từ A0-A10. Hơn nữa, tổng dung lượng là 8K, tức cần 213 đường địa chỉ, tức từ A0-A12. Như vậy, các đường địa chỉ A11- A12 sẽ được dùng để giải mã chọn chip (CS-Chip select) như trong hình 3.26. CHƢƠNG 3 CÁC CẤU TRÚC LUẬN LÝ SỐ 3.5 Bộ nhớ (Memory) CHƢƠNG 3 CÁC CẤU TRÚC LUẬN LÝ SỐ 3.5 Bộ nhớ (Memory) Ví dụ 3.3: Thiết kế bộ nhớ 64K x16 bit bằng 16 chip 8K x 8 bit. CHƢƠNG 3 CÁC CẤU TRÚC LUẬN LÝ SỐ 3.6 Mạch tuần tự (Sequential logic circuit) Đầu ra của mạch tuần tự không chỉ phụ thuộc vào đầu vào hiện tại mà còn phụ thuộc vào trạng thái hiện tại của các phần tử nhớ trong mạch. Thông tin nhị phân đang có trong các phần tử nhớ của mạch xác định trạng thái của mạch ở bất kỳ thời điểm nào trong quá khứ. Như vậy, mạch tuần tự tiêu biểu sẽ gồm hai thành phần là mạch tổ hợp và các phần tử nhớ để trữ thông tin là trạng thái của mạch. CHƢƠNG 3 CÁC CẤU TRÚC LUẬN LÝ SỐ 3.6 Mạch tuần tự (Sequential logic circuit) CHƢƠNG 3 CÁC CẤU TRÚC LUẬN LÝ SỐ 3.6 Mạch tuần tự (Sequential logic circuit) Mạch logic tuần tự được dùng để thực hiện một trong những cơ chế quan trọng là máy hay bộ điều khiển trạng thái hữu hạn (finite state machine). Thí dụ, một bộ điều khiển đèn giao thông bật đèn đỏ, vàng, hay xanh tùy thuộc vào đèn hiện thời đang sáng (thông tin trong quá khứ) và thông tin nhập từ các bộ cảm ứng về xe trên đường và các thiết bị quang đang điều khiển lưu lượng xe. CHƢƠNG 3 CÁC CẤU TRÚC LUẬN LÝ SỐ 3.6 Mạch tuần tự (Sequential logic circuit) 3.6.1 Khái niệm về trạng thái Trạng thái của một hệ thống là một bức tranh chụp nhanh mà ở đó tất cả các thành phần thích hợp đều được biểu diễn một cách rõ ràng. Ví dụ: - Trạng thái của một trận bóng đá:? . CHƢƠNG 3 CÁC CẤU TRÚC LUẬN LÝ SỐ 3.6 Mạch tuần tự (Sequential logic circuit) 3.6.2 Máy trạng thái hữu hạn Việc một hệ thống thay đổi từ trạng thái này sang trạng thái khác với một số lượng trạng thái xác định hữu hạn biểu diễn tiến trình làm việc của hệ thống. Lúc này ta nói hệ thống là một máy hay bộ điều khiển trạng thái hữu hạn (finite state machine). CHƢƠNG 3 CÁC CẤU TRÚC LUẬN LÝ SỐ 3.6 Mạch tuần tự (Sequential logic circuit) 3.6.2 Máy trạng thái hữu hạn. Một máy trạng thái hữu hạn bao gồm năm thành phần : 1. một số hữu hạn các trạng thái 2. một số hữu hạn các đầu vào từ bên ngoài 3. một số hữu hạn các tín hiệu xuất (hay đầu ra) ra bên ngoài 4. một chỉ định rõ tất cả các chuyển trạng thái 5. một chỉ định rõ thành phần mỗi giá trị đầu ra. CHƢƠNG 3 CÁC CẤU TRÚC LUẬN LÝ SỐ 3.6 Mạch tuần tự (Sequential logic circuit) 3.6.2 Máy trạng thái hữu hạn CHƢƠNG 3 CÁC CẤU TRÚC LUẬN LÝ SỐ 3.6 Mạch tuần tự (Sequential logic circuit) 3.6.3 Một thí dụ về hiện thực một máy trạng thái hữu hạn CHƢƠNG 3 CÁC CẤU TRÚC LUẬN LÝ SỐ 3.6 Mạch tuần tự (Sequential logic circuit) 3.6.3 Một thí dụ về hiện thực một máy trạng thái hữu hạn CHƢƠNG 3 CÁC CẤU TRÚC LUẬN LÝ SỐ 3.6 Mạch tuần tự (Sequential logic circuit) 3.6.3 Một thí dụ về hiện thực một máy trạng thái hữu hạn CHƢƠNG 3 CÁC CẤU TRÚC LUẬN LÝ SỐ 3.6 Mạch tuần tự (Sequential logic circuit) CHƢƠNG 3 CÁC CẤU TRÚC LUẬN LÝ SỐ 3.6 Mạch tuần tự (Sequential logic circuit) * Phần tử nhớ Thành phần còn lại trong bộ điều khiển đèn báo hiệu nguy hiểm giao thông là mạch logic của hai phần tử nhớ. Hình 3.32c trình bày cấu trúc của một phần tử nhớ gồm cặp hai mạch cài D, và được gọi là mạch lật chủ tớ (master-slave flip-flop). CHƢƠNG 3 CÁC CẤU TRÚC LUẬN LÝ SỐ 3.7 Đƣờng truyền dữ liệu LC3 Để hiểu rõ hơn việc thực thi của một chương trình, người ta đưa ra khái niệm đường truyền dữ liệu (data path) của một bộ vi xử lý. Đường truyền dữ liệu thực ra là các mạch logic được trình bày theo chức năng để xử lý thông tin. Do đó nó còn được gọi là vi kiến trúc của bộ vi xử lý. Hình 3.36 sau là đường truyền dữ liệu của máy tính ảo LC3, cũng tương tự như hình 1.14, có nhiều cấu trúc cơ bản tạo thành máy tính và rất quen thuộc với chúng ta như các thanh ghi 16 bit PC, IR, MAR, và MDR. Mỗi đường dây có đường gạch chéo nhỏ kèm theo số 16 biểu diễn 16 đường dây, mỗi dây mang một bit thông tin. N, Z, P là các thanh ghi một bit, chúng có thể được thực hiện bằng các mạch lật chủ tớ. CHƢƠNG 3 CÁC CẤU TRÚC LUẬN LÝ SỐ 3.7 Đƣờng truyền dữ liệu LC3. Có năm bộ phân kênh, một bộ cung cấp một giá trị 16 bit cho thanh ghi PC (PCMUX), một bộ cung cấp địa chỉ cho thanh ghi MAR (MARMUX), một bộ để chọn dữ liệu nhập vào đầu B của ALU (SR2MUX), và hai bộ để chọn toán hạng nhập cho bộ cộng 16 bit (ADDR1MUX và ADDR2MUX). Để điều khiển các thành phần trong đường truyền dữ liệu hoạt động, ta cần các vi lệnh với các bit quy định cụ thể. Tập hợp các vi lệnh là một vi chương trình mà trong chương sau chúng ta sẽ hiểu rõ hơn khi học cấp kiến trúc tập lệnh (ISA) của CPU LC3. CHƢƠNG 3 CÁC CẤU TRÚC LUẬN LÝ SỐ CHƢƠNG 3 CÁC CẤU TRÚC LUẬN LÝ SỐ

File đính kèm:

bai_giang_he_thong_may_tinh_va_ngon_ngu_c_chuong_3_cac_cau_t.pdf

bai_giang_he_thong_may_tinh_va_ngon_ngu_c_chuong_3_cac_cau_t.pdf