Thiết kế, chế tạo thiết bị kiểm tra bảng mạch nhớ trong máy tính của tổ hợp điều khiển vũ khí trên máy bay SU-27

Tóm tắt: Trong bài báo này trình bày những nội dung chính của việc thiết kế,

chế tạo thiết bị kiểm tra, chẩn đoán các bo mạch nhớ của máy tính số chuyên dụng

trong tổ hợp điều khiển vũ khí (CYB) trên máy báy Su-27, Su-30 như phân tích các

bảng mạch nhớ đưa ra cơ sở cho việc thiết kế, tham khảo cấu trúc các thiết bị kiểm

tra bảng mạch điện tử của các nước đang được trang bị trong các đơn vị, từ đó đưa

ra cấu trúc thiết bị kiểm tra. Trên cơ sở cấu trúc thiết bị kiểm tra, tiến hành lựa

chọn và thiết kế các thiết bị, xây dựng thuật toán và phần mềm. Các kết quả thử

nghiệm tại nhà máy khi kiểm tra với các bảng mạch nhớ khác nhau chứng minh các

chức năng kiểm tra chẩn đoán của thiết bị kiểm tra làm việc tốt và đáp ứng các yêu

cầu thiết kế.

Trang 1

Trang 2

Trang 3

Trang 4

Trang 5

Trang 6

Trang 7

Tóm tắt nội dung tài liệu: Thiết kế, chế tạo thiết bị kiểm tra bảng mạch nhớ trong máy tính của tổ hợp điều khiển vũ khí trên máy bay SU-27

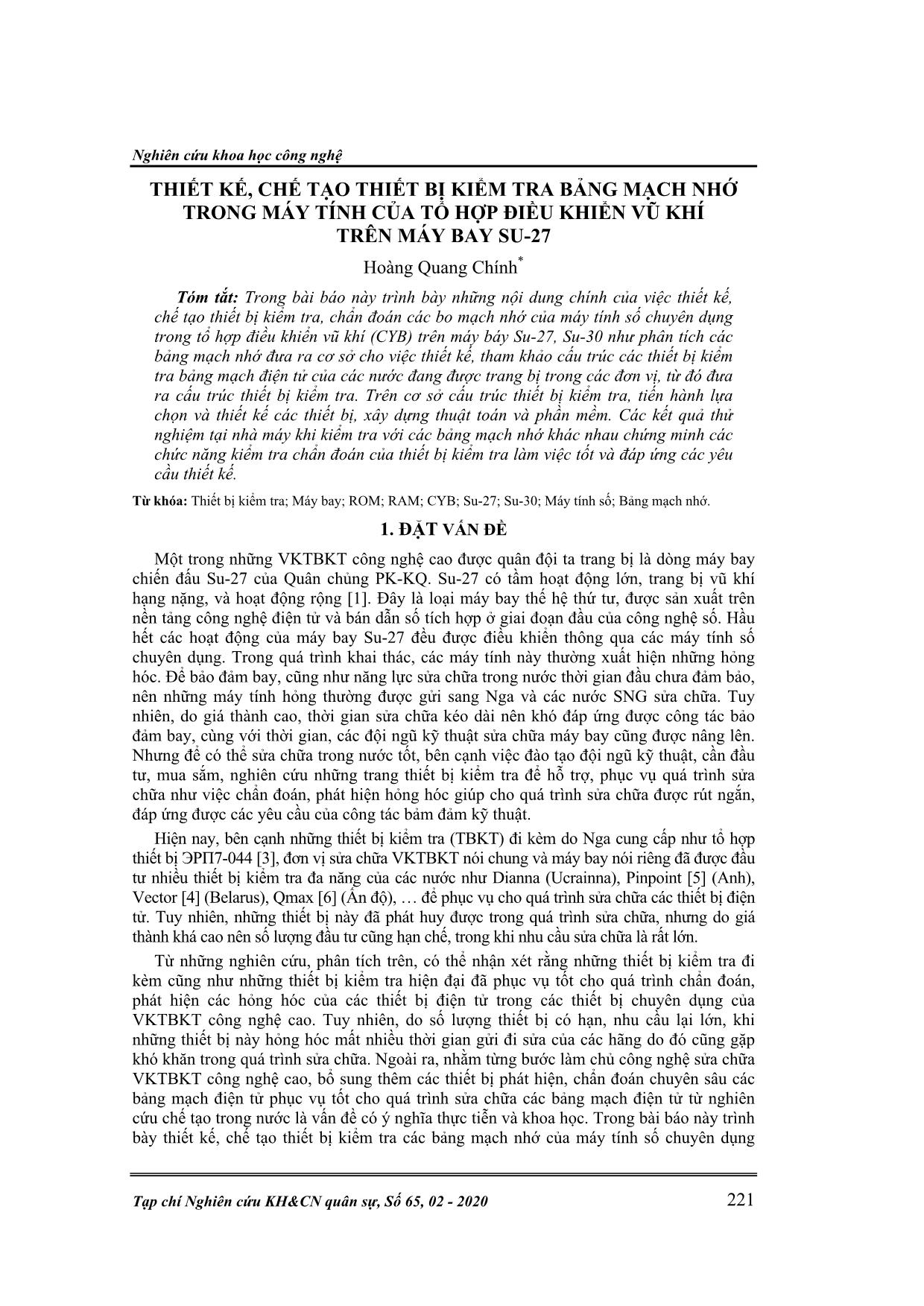

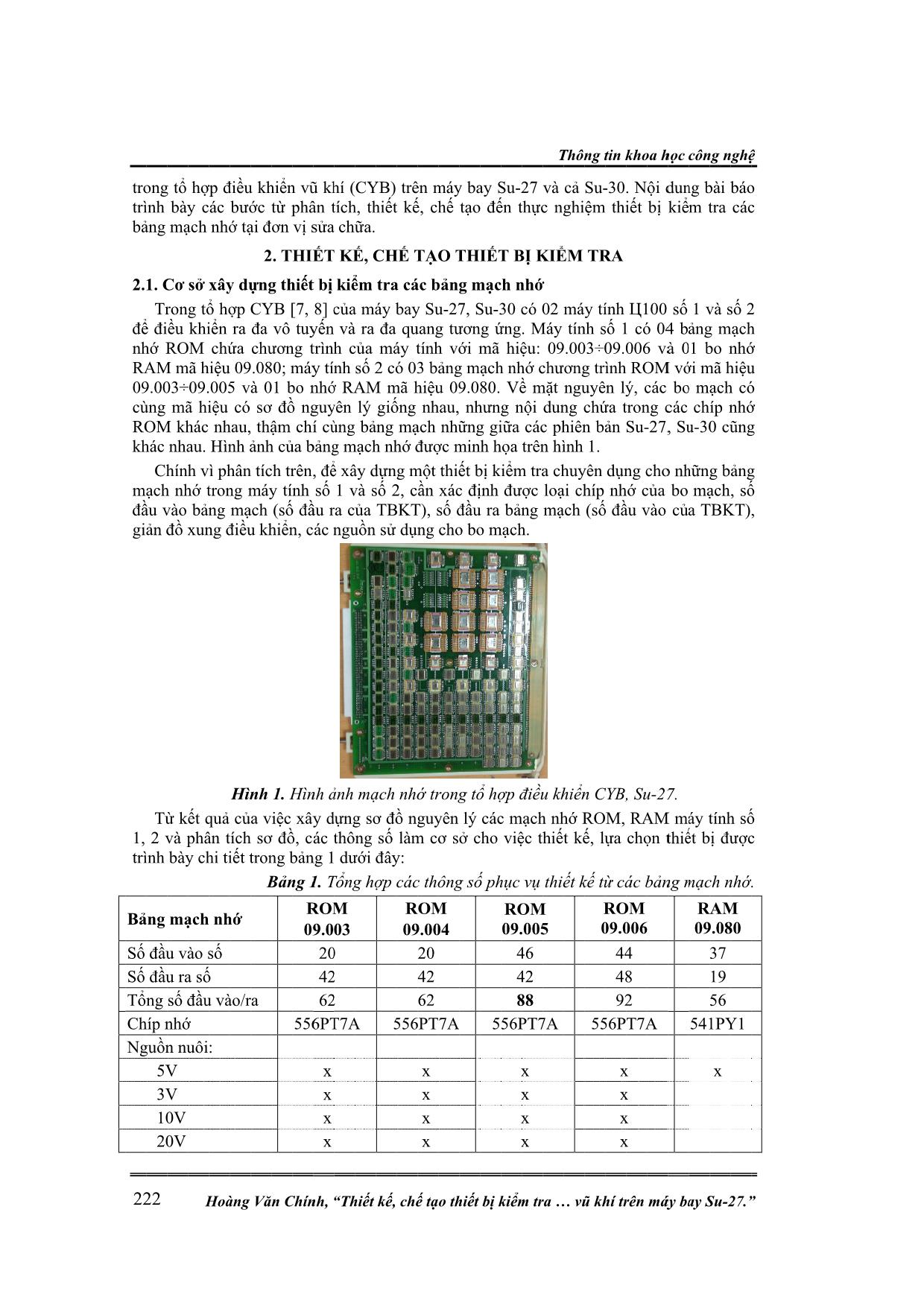

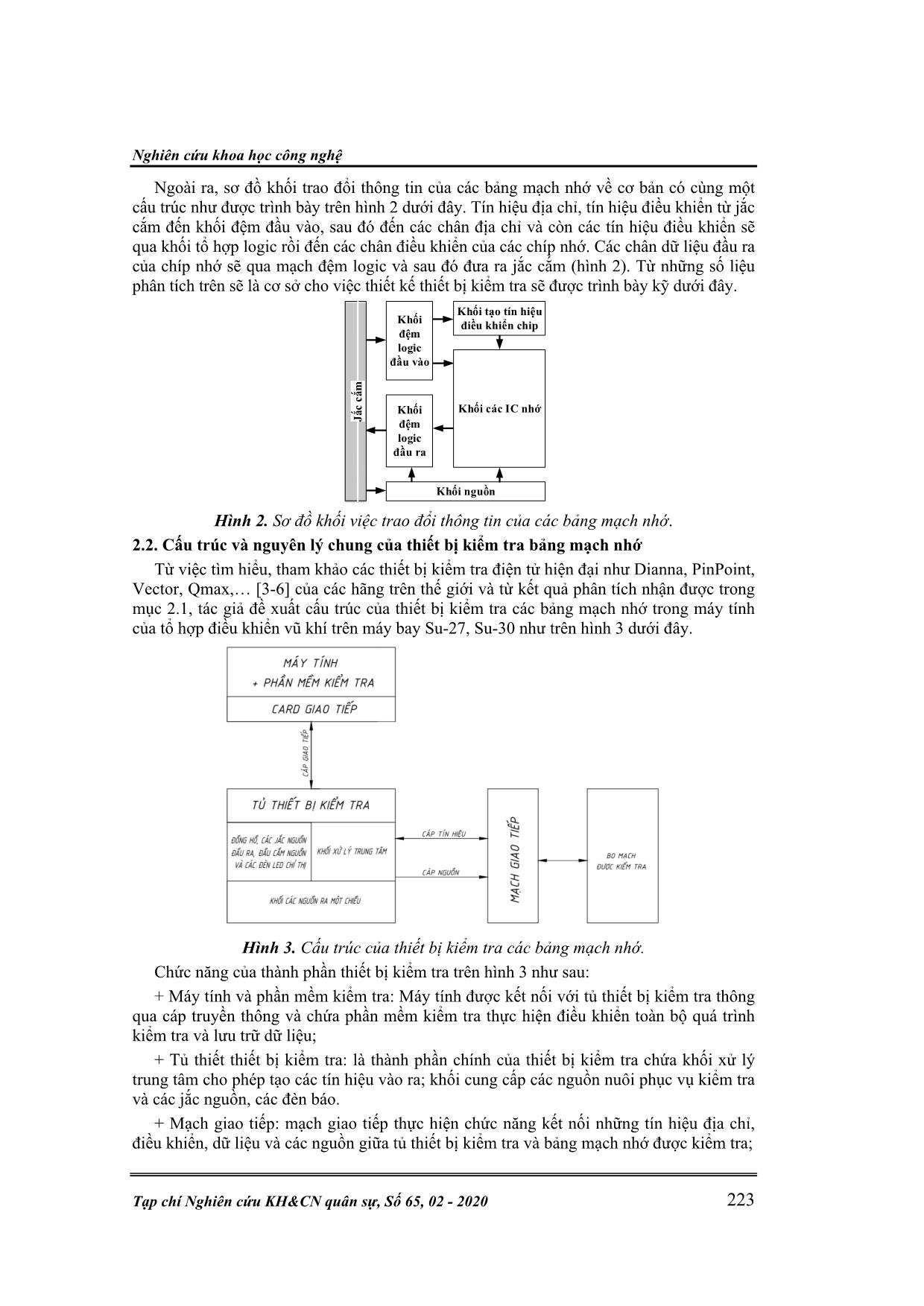

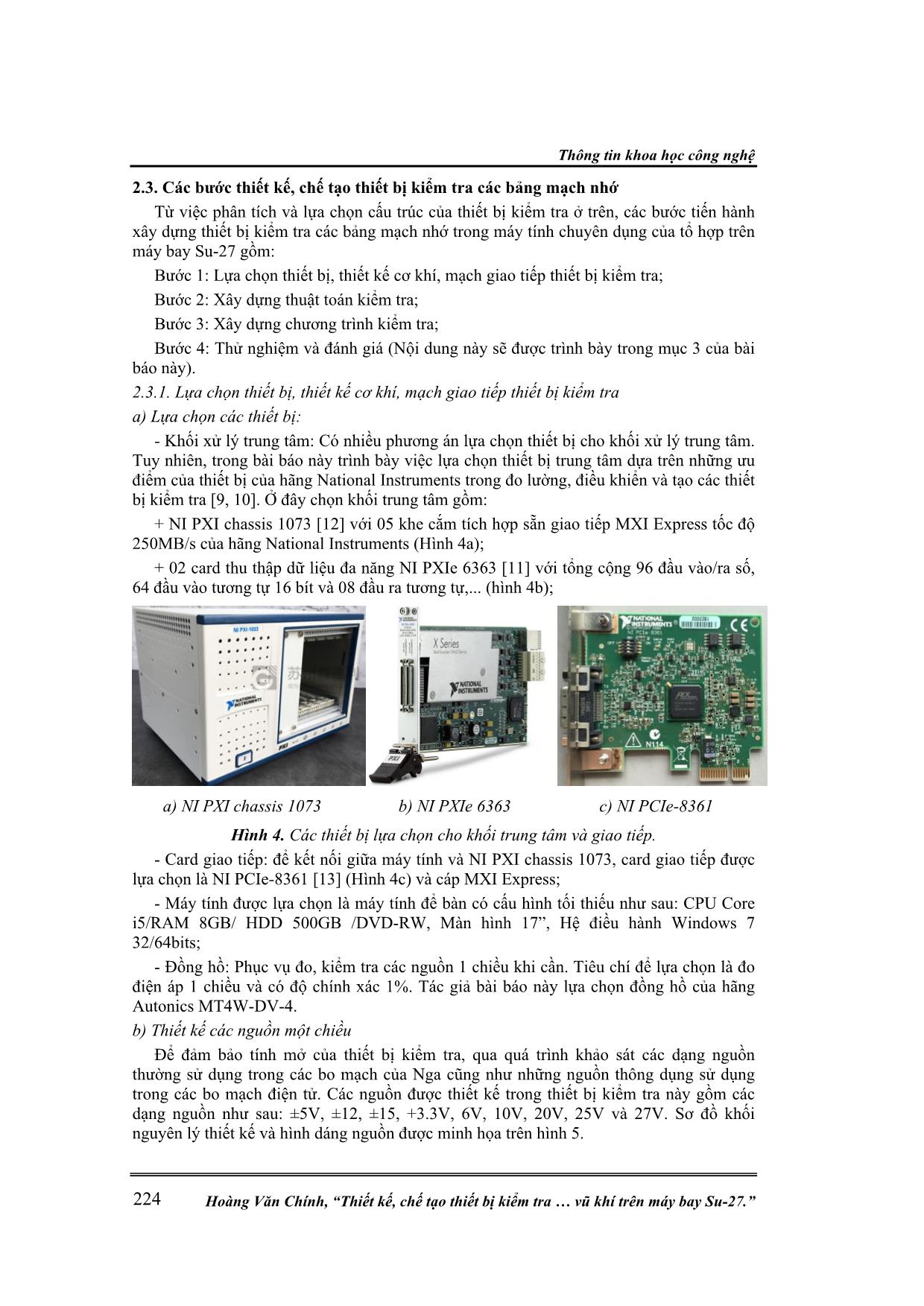

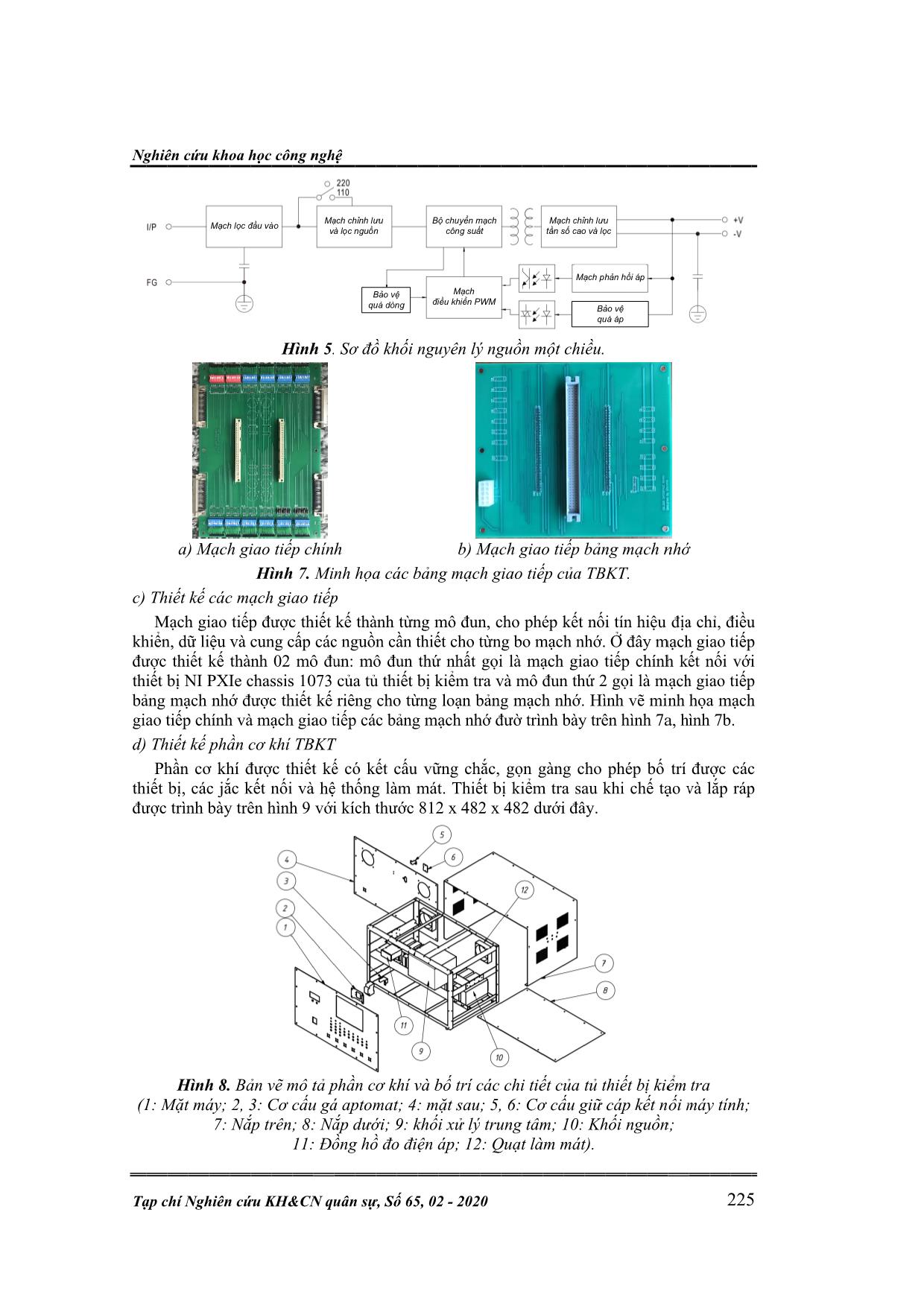

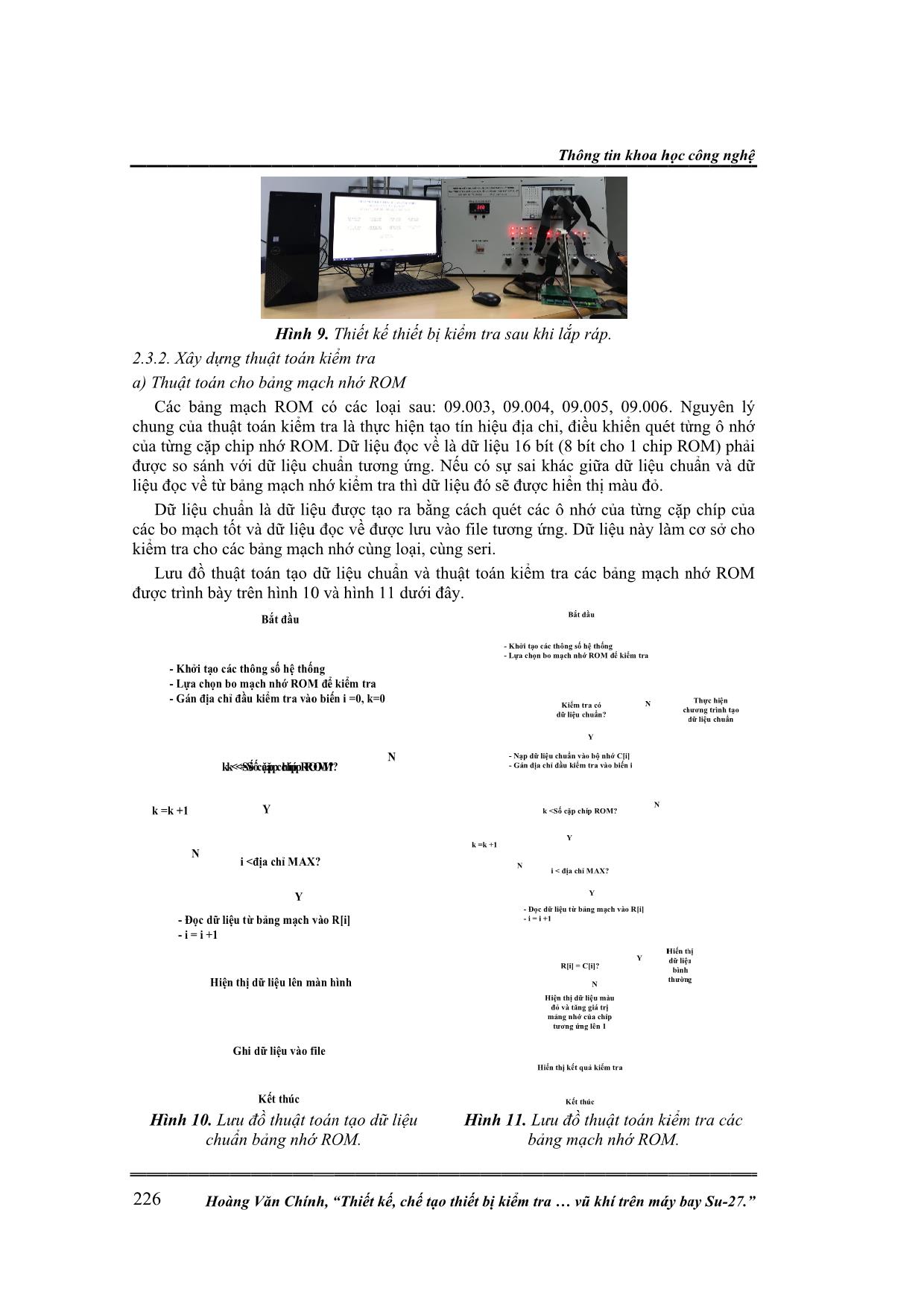

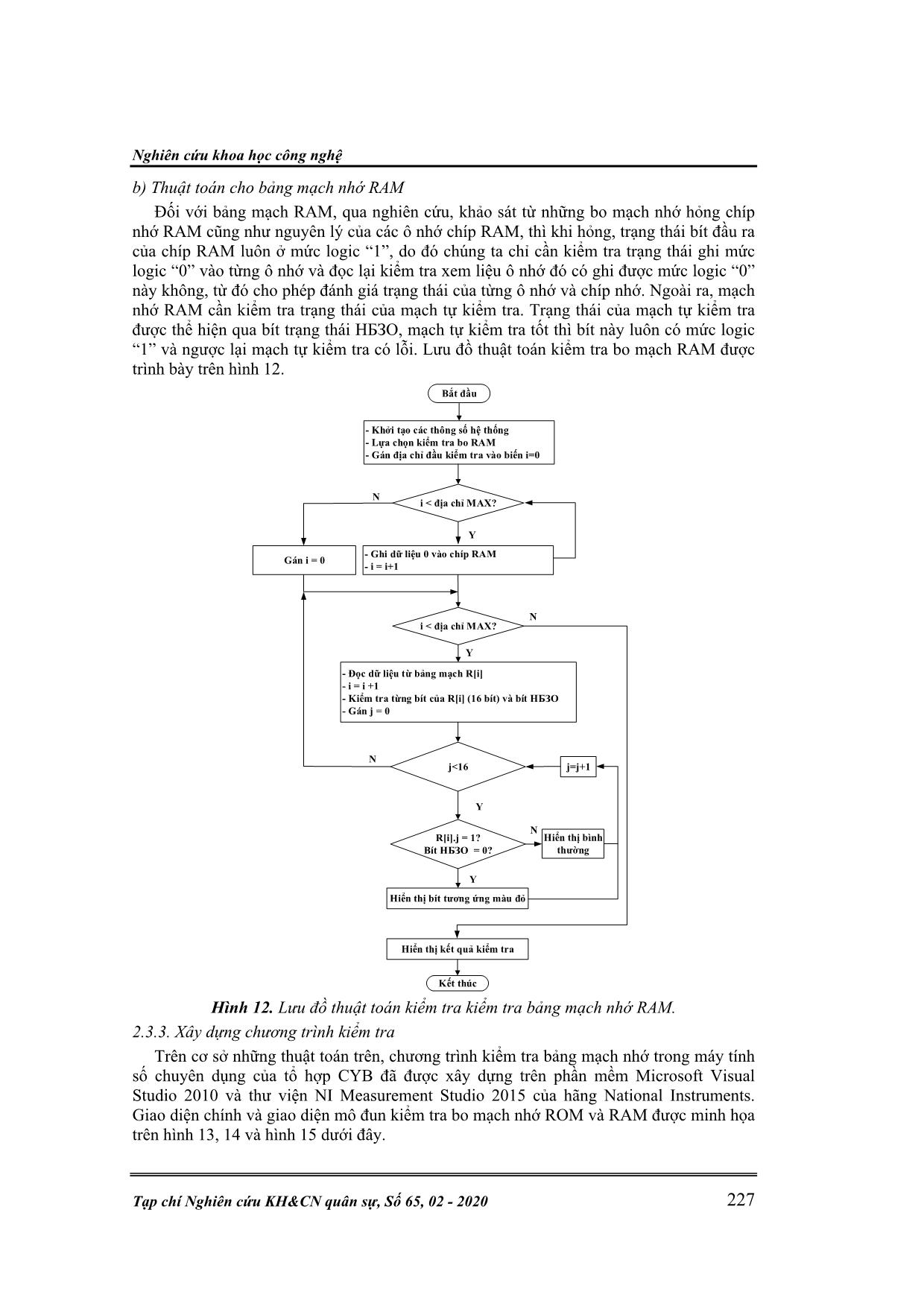

hệ thứ tư, được sản xuất trên nền tảng công nghệ điện tử và bán dẫn số tích hợp ở giai đoạn đầu của công nghệ số. Hầu hết các hoạt động của máy bay Su-27 đều được điều khiển thông qua các máy tính số chuyên dụng. Trong quá trình khai thác, các máy tính này thường xuất hiện những hỏng hóc. Để bảo đảm bay, cũng như năng lực sửa chữa trong nước thời gian đầu chưa đảm bảo, nên những máy tính hỏng thường được gửi sang Nga và các nước SNG sửa chữa. Tuy nhiên, do giá thành cao, thời gian sửa chữa kéo dài nên khó đáp ứng được công tác bảo đảm bay, cùng với thời gian, các đội ngũ kỹ thuật sửa chữa máy bay cũng được nâng lên. Nhưng để có thể sửa chữa trong nước tốt, bên cạnh việc đào tạo đội ngũ kỹ thuật, cần đầu tư, mua sắm, nghiên cứu những trang thiết bị kiểm tra để hỗ trợ, phục vụ quá trình sửa chữa như việc chẩn đoán, phát hiện hỏng hóc giúp cho quá trình sửa chữa được rút ngắn, đáp ứng được các yêu cầu của công tác bảm đảm kỹ thuật. Hiện nay, bên cạnh những thiết bị kiểm tra (TBKT) đi kèm do Nga cung cấp như tổ hợp thiết bị ЭРП7-044 [3], đơn vị sửa chữa VKTBKT nói chung và máy bay nói riêng đã được đầu tư nhiều thiết bị kiểm tra đa năng của các nước như Dianna (Ucrainna), Pinpoint [5] (Anh), Vector [4] (Belarus), Qmax [6] (Ấn độ), để phục vụ cho quá trình sửa chữa các thiết bị điện tử. Tuy nhiên, những thiết bị này đã phát huy được trong quá trình sửa chữa, nhưng do giá thành khá cao nên số lượng đầu tư cũng hạn chế, trong khi nhu cầu sửa chữa là rất lớn. Từ những nghiên cứu, phân tích trên, có thể nhận xét rằng những thiết bị kiểm tra đi kèm cũng như những thiết bị kiểm tra hiện đại đã phục vụ tốt cho quá trình chẩn đoán, phát hiện các hỏng hóc của các thiết bị điện tử trong các thiết bị chuyên dụng của VKTBKT công nghệ cao. Tuy nhiên, do số lượng thiết bị có hạn, nhu cầu lại lớn, khi những thiết bị này hỏng hóc mất nhiều thời gian gửi đi sửa của các hãng do đó cũng gặp khó khăn trong quá trình sửa chữa. Ngoài ra, nhằm từng bước làm chủ công nghệ sửa chữa VKTBKT công nghệ cao, bổ sung thêm các thiết bị phát hiện, chẩn đoán chuyên sâu các bảng mạch điện tử phục vụ tốt cho quá trình sửa chữa các bảng mạch điện tử từ nghiên cứu chế tạo trong nước là vấn đề có ý nghĩa thực tiễn và khoa học. Trong bài báo này trình bày thiết kế, chế tạo thiết bị kiểm tra các bảng mạch nhớ của máy tính số chuyên dụng 222 trong t trình bày các b bảng mạch nhớ tại đ 2.1. để điều khiển ra đa vô tuyến v nh RAM mã hi 09.003÷09.005 và 01 bo nh cùng mã hi ROM khác nhau, th khác nhau. mạch nhớ trong máy tính số 1 v đầu v giản đồ xung điều khiển, các nguồn sử dụng cho bo mạch. 1, 2 trình bày chi ti Bảng mạch nhớ Số đầu v Số đầu ra số Tổng số đầu v Chíp nh Ngu Cơ s Trong t ớ ROM chứa ch Chính vì phân tích trên, Từ kết quả của việc xây dựng s và phân tích sơ đ ồn nuôi: 5V 3V 10V 20V ổ hợp điều khiển vũ khí ào ào s ớ Hoàng Văn Chính ở xây dựng thiết bị kiểm tra các bảng mạch nhớ ổ hợp CYB [7, bảng mạch (số đầu ra của TBKT) ệu 09.080; máy tính số 2 có 03 bảng mạch nhớ ch ệu có s Hình ố ào/ra ước từ phân tích, thiết kế, chế tạo đến thực nghiệm thiết bị kiểm tra các ảnh của bảng mạch nhớ đ Hình 1. ết trong bảng 1 d ơn v 2. ương tr ơ đ ậm chí c B THI ồ nguy Hình ồ ảng 1. ị sửa chữa. ẾT KẾ, CHẾ TẠO THIẾT BỊ KIỂM TRA , các thông s ROM 09.003 556PT7A , “ 8] c ình c ớ RAM m ùng b để xây dựng một thiết bị kiểm tra chuy ản T 20 42 62 x x x x Thi (CYB) ủa máy bay Su à ra đa quang tương ên lý gi h m ư ổng hợp các thông số phục vụ thiết kế từ các bảng mạch nhớ ết kế, chế tạo thiết bị kiểm tra ủa má ảng mạch những giữa các phi à s ạch nhớ trong tổ hợp điều khiển CYB, Su ơ đ ới đây ống nhau, nh ố 2, cần xác định đ ồ nguy ố 556PT7A trên máy bay Su y tính v ã hi làm cơ s : ROM 09.004 20 42 62 ệu 09.080. Về mặt nguy ược minh họa tr , s x x x x -27, Su ới m ố đ ên lý các m ở cho việc ầu ra -30 có 02 máy tính ứng. Máy tính số 1 có 04 bảng mạch ã hi ưng n 556PT7A -27 và c ệu: 09.003÷09.006 v ược loại chíp nhớ của bo mạch, số bảng mạch (số đầu v ROM 09.005 46 42 88 x x x x ội dung chứa trong các chíp nhớ ên ạch nhớ ROM, RAM thi Thông tin khoa h ương tr hình ết kế vũ khí tr ả Su ên b - ình ROM v ên lý, các bo m ản Su 1. ên d , lựa chọn thiết bị ROM 09.006 556PT7A 30. N ụng c 44 48 92 x x x x ên máy bay Su ội dung b Ц100 s - à 01 bo nh 27, Su ho nh ào c -27. ọc công nghệ ố 1 v ới m ủa TBKT) máy tính s ạch có -30 c ững bảng RAM 09.080 37 19 56 541PY1 -27. ài báo à s ã hi ũng đư x ” ố 2 ớ ệu , ố ợc . Nghiên cứu khoa học công nghệ Tạp chí Nghiên cứu KH&CN quân sự, Số 65, 02 - 2020 223 Ngoài ra, sơ đồ khối trao đổi thông tin của các bảng mạch nhớ về cơ bản có cùng một cấu trúc như được trình bày trên hình 2 dưới đây. Tín hiệu địa chỉ, tín hiệu điều khiển từ jắc cắm đến khối đệm đầu vào, sau đó đến các chân địa chỉ và còn các tín hiệu điều khiển sẽ qua khối tổ hợp logic rồi đến các chân điều khiển của các chíp nhớ. Các chân dữ liệu đầu ra của chíp nhớ sẽ qua mạch đệm logic và sau đó đưa ra jắc cắm (hình 2). Từ những số liệu phân tích trên sẽ là cơ sở cho việc thiết kế thiết bị kiểm tra sẽ được trình bày kỹ dưới đây. Khối nguồn Khối đệm logic đầu vào Khối tạo tín hiệu điều khiển chip Khối các IC nhớKhối đệm logic đầu ra J ắc c ắm Hình 2. Sơ đồ khối việc trao đổi thông tin của các bảng mạch nhớ. 2.2. Cấu trúc và nguyên lý chung của thiết bị kiểm tra bảng mạch nhớ Từ việc tìm hiểu, tham khảo các thiết bị kiểm tra điện tử hiện đại như Dianna, PinPoint, Vector, Qmax, [3-6] của các hãng trên thế giới và từ kết quả phân tích nhận được trong mục 2.1, tác giả đề xuất cấu trúc của thiết bị kiểm tra các bảng mạch nhớ trong máy tính của tổ hợp điều khiển vũ khí trên máy bay Su-27, Su-30 như trên hình 3 dưới đây. Hình 3. Cấu trúc của thiết bị kiểm tra các bảng mạch nhớ. Chức năng của thành phần thiết bị kiểm tra trên hình 3 như sau: + Máy tính và phần mềm kiểm tra: Máy tính được kết nối với tủ thiết bị kiểm tra thông qua cáp truyền thông và chứa phần mềm kiểm tra thực hiện điều khiển toàn bộ quá trình kiểm tra và lưu trữ dữ liệu; + Tủ thiết thiết bị kiểm tra: là thành phần chính của thiết bị kiểm tra chứa khối xử lý trung tâm cho phép tạo các tín hiệu vào ra; khối cung cấp các nguồn nuôi phục vụ kiểm tra và các jắc nguồn, các đèn báo. + Mạch giao tiếp: mạch giao tiếp thực hiện chức năng kết nối những tín hiệu địa chỉ, điều khiển, dữ liệu và các nguồn giữa tủ thiết bị kiểm tra và bảng mạch nhớ được kiểm tra; Thông tin khoa học công nghệ Hoàng Văn Chính, “Thiết kế, chế tạo thiết bị kiểm tra vũ khí trên máy bay Su-27.” 224 2.3. Các bước thiết kế, chế tạo thiết bị kiểm tra các bảng mạch nhớ Từ việc phân tích và lựa chọn cấu trúc của thiết bị kiểm tra ở trên, các bước tiến hành xây dựng thiết bị kiểm tra các bảng mạch nhớ trong máy tính chuyên dụng của tổ hợp trên máy bay Su-27 gồm: Bước 1: Lựa chọn thiết bị, thiết kế cơ khí, mạch giao tiếp thiết bị kiểm tra; Bước 2: Xây dựng thuật toán kiểm tra; Bước 3: Xây dựng chương trình kiểm tra; Bước 4: Thử nghiệm và đánh giá (Nội dung này sẽ được trình bày trong mục 3 của bài báo này). 2.3.1. Lựa chọn thiết bị, thiết kế cơ khí, mạch giao tiếp thiết bị kiểm tra a) Lựa chọn các thiết bị: - Khối xử lý trung tâm: Có nhiều phương án lựa chọn thiết bị cho khối xử lý trung tâm. Tuy nhiên, trong bài báo này trình bày việc lựa chọn thiết bị trung tâm dựa trên những ưu điểm của thiết bị của hãng National Instruments trong đo lường, điều khiển và tạo các thiết bị kiểm tra [9, 10]. Ở đây chọn khối trung tâm gồm: + NI PXI chassis 1073 [12] với 05 khe cắm tích hợp sẵn giao tiếp MXI Express tốc độ 250MB/s của hãng National Instruments (Hình 4a); + 02 card thu thập dữ liệu đa năng NI PXIe 6363 [11] với tổng cộng 96 đầu vào/ra số, 64 đầu vào tương tự 16 bít và 08 đầu ra tương tự,... (hình 4b); a) NI PXI chassis 1073 b) NI PXIe 6363 c) NI PCIe-8361 Hình 4. Các thiết bị lựa chọn cho khối trung tâm và giao tiếp. - Card giao tiếp: để kết nối giữa máy tính và NI PXI chassis 1073, card giao tiếp được lựa chọn là NI PCIe-8361 [13] (Hình 4c) và cáp MXI Express; - Máy tính được lựa chọn là máy tính để bàn có cấu hình tối thiếu như sau: CPU Core i5/RAM 8GB/ HDD 500GB /DVD-RW, Màn hình 17”, Hệ điều hành Windows 7 32/64bits; - Đồng hồ: Phục vụ đo, kiểm tra các nguồn 1 chiều khi cần. Tiêu chí để lựa chọn là đo điện áp 1 chiều và có độ chính xác 1%. Tác giả bài báo này lựa chọn đồng hồ của hãng Autonics MT4W-DV-4. b) Thiết kế các nguồn một chiều Để đảm bảo tính mở của thiết bị kiểm tra, qua quá trình khảo sát các dạng nguồn thường sử dụng trong các bo mạch của Nga cũng như những nguồn thông dụng sử dụng trong các bo mạch điện tử. Các nguồn được thiết kế trong thiết bị kiểm tra này gồm các dạng nguồn như sau: ±5V, ±12, ±15, +3.3V, 6V, 10V, 20V, 25V và 27V. Sơ đồ khối nguyên lý thiết kế và hình dáng nguồn được minh họa trên hình 5. Nghiên c Tạp chí Nghi c) khi đư thi bảng mạch nhớ đ giao ti d) thi đư (1: M Thi M ển, dữ liệu v ợc thiết kế th ết bị NI PXIe chassis 1073 của tủ thiết bị kiểm tra v Thi Ph ết bị, các jắc kết nối v ợc tr a) M ết kế các mạch ạch giao tiếp đ ếp chính v ết kế phần c ần c ình bày trên hìn Hình 8. ặt máy ứu khoa học công nghệ ơ khí đư ên Mạch lọc đầu vào ạch giao tiếp chính ; 2, 3: Cơ c 7: N cứu KH&CN à cung c ành 02 mô đun: mô đun th à m Bản vẽ ắp tr Hình ư ược thiết kế ri ạch giao tiếp các bảng mạch nhớ đ ơ khí TBKT ợc thiết kế có kết cấu vững chắc, gọn g Hình giao ti ợc thiết kế th h mô t ên; 8: N 11: Đ 7. ấp các nguồn cần thiết cho từng bo mạch nhớ. Ở đây mạch giao tiếp à h 9 ấu gá aptomat; 4: mặt sau; 5, 6: C quân s Mạch chỉnh lưu và lọc nguồn 5. Minh h ếp ệ thống l với kích th ả phần c ắp d ồng hồ đo điện áp; 12: Quạt l Sơ đ êng cho t ự, Số Bảo vệ quá dòng ồ khối nguy ọa các bảng mạch giao tiếp của TBKT ành t ơ khí và ưới; 9: khối x àm mát. Thi ư 65 ừng mô đun, cho phép kết nối tín hiệu địa chỉ, điều ừng loạn bảng mạch nhớ. H ớc 812 x 482 x 482 d , 02 Bộ chuyển mạch điều khiển PWM ứ nhất gọi l b - 20 công suất Mạch ên lý ngu b) M ố trí ử lý 20 ết bị kiểm tra sau khi chế tạo v các chi ti ạch giao tiếp bảng mạch nhớ trung tâm; 10: Kh ồn một chiều à m à mô đun th ườ tr ạch giao tiếp ình bày trên hình 7a, hình 7b. ư ết của tủ thiết bị kiểm tra ơ c àm mát Mạch chỉnh lưu tần số cao và lọc àng cho phép b ới đây. ấu giữ cáp kết nối máy tính; Mạch phản hồi áp ) Bảo vệ quá áp . ứ 2 gọi l ình v . ối nguồn; . chính k à m ẽ minh họa mạch ạch giao tiếp ố trí đ ết nối với ược các à l 225 ắp ráp 226 2.3.2 a) chung c của từng cặp chip nhớ ROM. Dữ liệu đọc về l đư liệu đọc về từ bảng mạch nhớ kiểm tra th các bo m kiểm tra cho các bảng mạch nhớ c đư . Thu Các b ợc so sánh với dữ liệu chuẩn t Dữ liệu chuẩn l Lưu đ ợc tr k = Hình 10. Xây d ật toán cho bảng mạch nhớ ROM ủa thuật toán kiểm tra l ình bày trên hình 10 và hình 11 d - Khởi tạo các thông số hệ thống - Lựa chọn bo mạch nhớ ROM để kiểm tra - Gán địa chỉ đầu kiểm tra vào biến i k +1 - Đọc dữ liệu từ bảng mạch vào R - i Hoàng Văn Chính ảng mạch ROM có các loại sau: 09.003, 09.004, 09.005, ạch tốt v ồ thuật toán tạo dữ liệu chuẩn v N = i + chu ựng thuật toán kiểm tra k 1 Hiện thị dữ liệu lên màn hình k Lưu đ i < Ghi dữ liệu vào file < =Số cặp chíp ROM<Số cặp chíp ROM ẩn bảng nhớ ROM. à d à d Bắt đầu Kết thúc địa chỉ MAX Y ồ thuật toán tạo dữ Hình ữ liệu đ ữ liệu đọc về đ Y , “ 9. Thi ? ?? Thi à th ược tạo ra bằng cách quét các ô nhớ của từng cặp chíp của = [i] ết kế, chế tạo thiết bị kiểm tra ết kế thiết bị kiểm tra sau khi lắp ráp. ực hiện tạo tín hiệu địa chỉ, điều khiển quét từng ô nhớ ương ùng lo 0, k= ược l 0 N li ứng. Nếu có sự sai kh ì d ưu vào file tương ại, c ưới đây. ệu ữ liệu đó sẽ đ ùng seri. à thu à d ật toán kiểm tra các bảng mạch nhớ ROM ữ liệu 16 bít (8 bít cho 1 chip ROM) phải k = Hình 11. k +1 - Khởi tạo các thông số hệ thống - Lựa chọn bo mạch nhớ ROM để kiểm tra N - Nạp dữ liệu chuẩn vào bộ nhớ C - Gán địa chỉ đầu kiểm tra vào biến i ược hiển thị m ứng. Dữ Hiển thị kết quả kiểm tra k - Đọc dữ liệu từ bảng mạch vào R - i = i Lưu đ bảng mạch nhớ ROM. Thông tin khoa h ác gi Kiểm tra có dữ liệu chuẩn R Hiện thị dữ liệu màu đỏ và tăng giá trị mảng nhớ của chíp tương ứng lên i < địa chỉ MAX <Số cặp chíp ROM +1 vũ khí tr Bắt đầu [i] = C Kết thúc Y ồ thuật toán kiểm tra các ữa dữ liệu chuẩn v li ? [i]? 1 Y ? N Y 09.006. Nguyên lý àu đ ệu n [i ? ên máy bay Su ày làm cơ s N ] Y [i] ỏ. Hiển thị dữ liệu thường N ọc công nghệ chương trình tạo dữ liệu chuẩn bình Thực hiện ì -27. à d ở cho ” ữ Nghiên cứu khoa học công nghệ Tạp chí Nghiên cứu KH&CN quân sự, Số 65, 02 - 2020 227 b) Thuật toán cho bảng mạch nhớ RAM Đối với bảng mạch RAM, qua nghiên cứu, khảo sát từ những bo mạch nhớ hỏng chíp nhớ RAM cũng như nguyên lý của các ô nhớ chíp RAM, thì khi hỏng, trạng thái bít đầu ra của chíp RAM luôn ở mức logic “1”, do đó chúng ta chỉ cần kiểm tra trạng thái ghi mức logic “0” vào từng ô nhớ và đọc lại kiểm tra xem liệu ô nhớ đó có ghi được mức logic “0” này không, từ đó cho phép đánh giá trạng thái của từng ô nhớ và chíp nhớ. Ngoài ra, mạch nhớ RAM cần kiểm tra trạng thái của mạch tự kiểm tra. Trạng thái của mạch tự kiểm tra được thể hiện qua bít trạng thái НБЗО, mạch tự kiểm tra tốt thì bít này luôn có mức logic “1” và ngược lại mạch tự kiểm tra có lỗi. Lưu đồ thuật toán kiểm tra bo mạch RAM được trình bày trên hình 12. Bắt đầu - Khởi tạo các thông số hệ thống - Lựa chọn kiểm tra bo RAM - Gán địa chỉ đầu kiểm tra vào biến i=0 R[i].j = 1? Bít НБЗO = 0? Y N Kết thúc - Ghi dữ liệu 0 vào chíp RAM - i = i+1 i < địa chỉ MAX? N Y Gán i = 0 Hiển thị kết quả kiểm tra - Đọc dữ liệu từ bảng mạch R[i] - i = i +1 - Kiểm tra từng bít của R[i] (16 bít) và bít НБЗO - Gán j = 0 i < địa chỉ MAX? N Y Hiển thị bình thường Hiển thị bít tương ứng màu đỏ j<16 Y j=j+1 N Hình 12. Lưu đồ thuật toán kiểm tra kiểm tra bảng mạch nhớ RAM. 2.3.3. Xây dựng chương trình kiểm tra Trên cơ sở những thuật toán trên, chương trình kiểm tra bảng mạch nhớ trong máy tính số chuyên dụng của tổ hợp CYB đã được xây dựng trên phần mềm Microsoft Visual Studio 2010 và thư viện NI Measurement Studio 2015 của hãng National Instruments. Giao diện chính và giao diện mô đun kiểm tra bo mạch nhớ ROM và RAM được minh họa trên hình 13, 14 và hình 15 dưới đây.

File đính kèm:

thiet_ke_che_tao_thiet_bi_kiem_tra_bang_mach_nho_trong_may_t.pdf

thiet_ke_che_tao_thiet_bi_kiem_tra_bang_mach_nho_trong_may_t.pdf