Phương pháp mô hình hóa điện trở dây trong mảng vi điện trở nhớ ứng dụng trong mạng nơ-ron nhân tạo

Mảng vi điện trở nhớ được ứng dụng nhiều để thực thi các mạng nơ-ron nhân tạo. Một trong

các yếu tố ảnh hưởng đến hiệu năng của mảng vi điện trở nhớ là điện trở dây kim loại. Thông

thường, điện trở dây kim loại được mô hình hóa bằng các điện trở có giá trị nhỏ nằm giữa các

giao điểm. Phương pháp mô hình hóa này làm cho số lượng phần tử mạch tăng gấp 3 lần khi xét

đến sự có mặt của các điện trở dây và gây khó khăn cho quá trình phân tích và mô phỏng mạch.

Trong bài báo này, tác giả đề xuất phương pháp mô hình hóa điện trở dây sử dụng điện trở tương

đương. Điện trở tương đương được xác định bằng cách sử dụng phương pháp xếp chồng khi

phân tích mạch. Phương pháp đề xuất cho sai lệch chỉ 1.7% khi điện trở dây thay đổi từ 0.5 đến

2.5 Ω so với phương pháp thông thường. Số lượng phần tử mạch trong phương pháp đề xuất

giảm đi 1/3 lần so với phương pháp thông thường, góp phần làm cho quá trình phân tích và mô

phỏng mạch nhanh hơn. Cụ thể, sử dụng phương pháp mô hình hóa điện trở dây bằng điện trở

tương đương chỉ mất 11.7 giây để phân tích mô phỏng mạch bằng phần mềm Candence Spectre,

trong khi phương pháp thông thường mất 108.92 giây, khi sử dụng cùng phần mềm phân tích và

mô phỏng mạch. Phương pháp được đề xuất cho phép mô phỏng các mảng vi điện trở nhớ kích

thước lớn hơn mà phương pháp thông thường mất nhiều thời gian để phân tích và mô phỏng.

Trang 1

Trang 2

Trang 3

Trang 4

Trang 5

Trang 6

Tóm tắt nội dung tài liệu: Phương pháp mô hình hóa điện trở dây trong mảng vi điện trở nhớ ứng dụng trong mạng nơ-ron nhân tạo

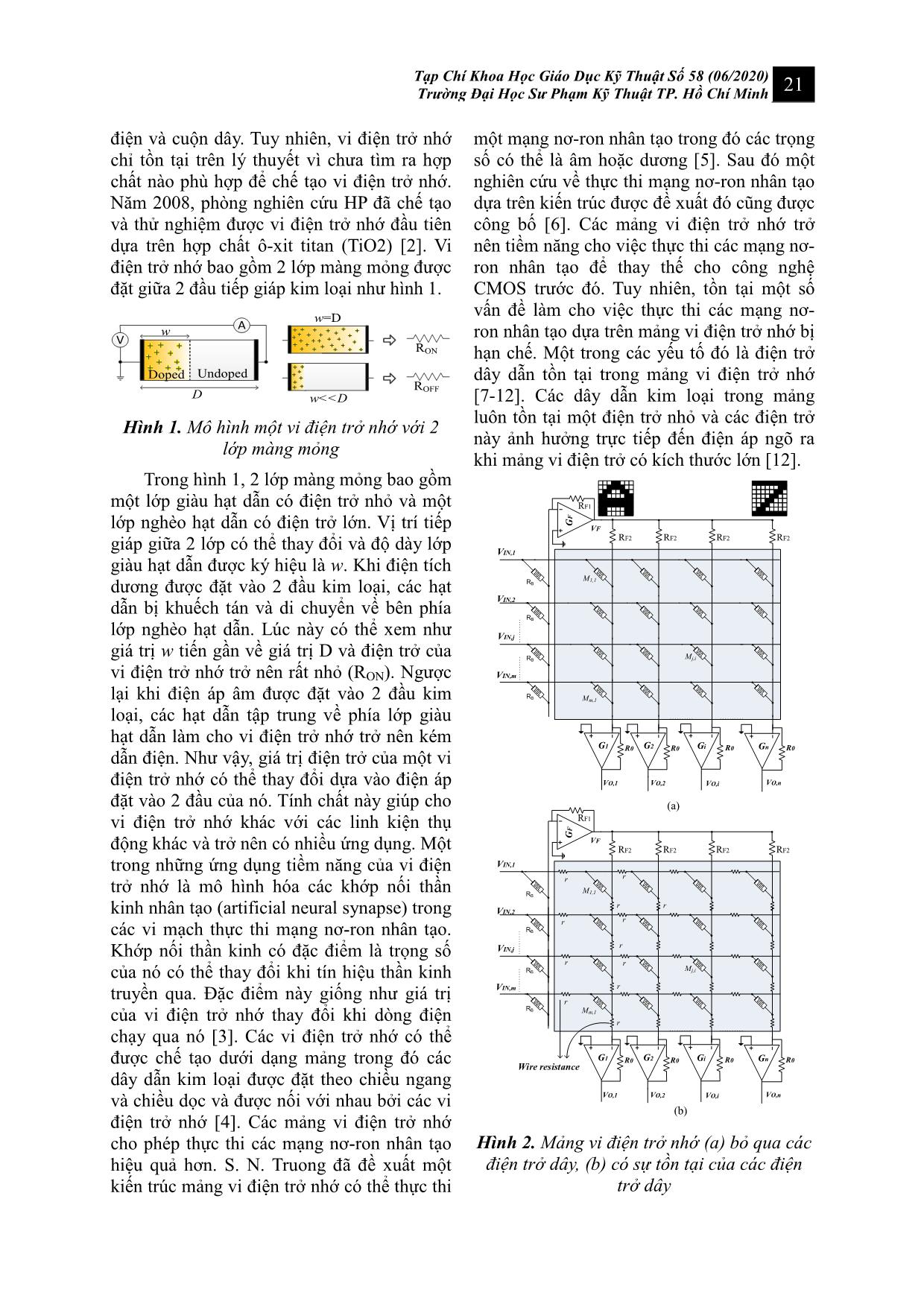

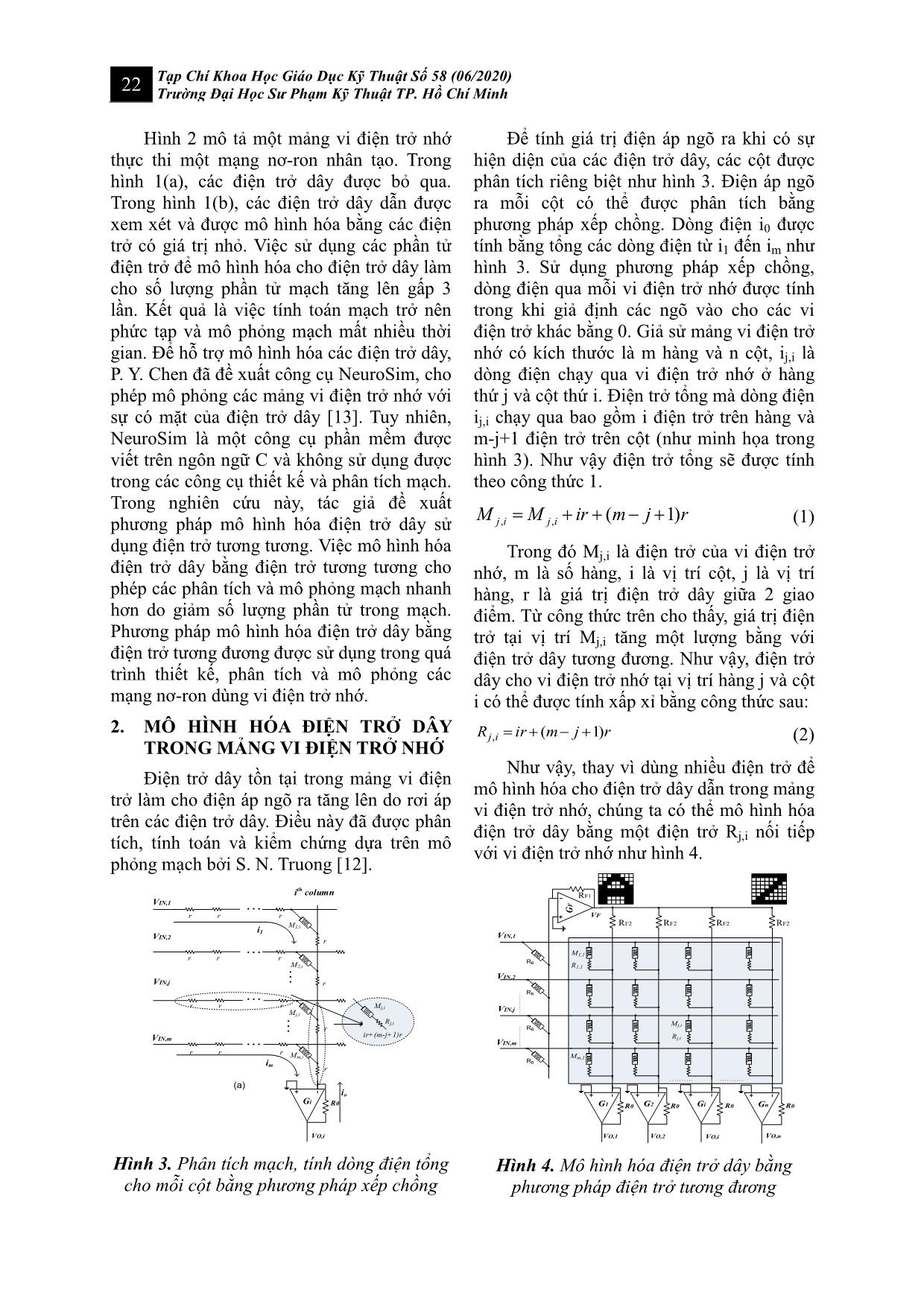

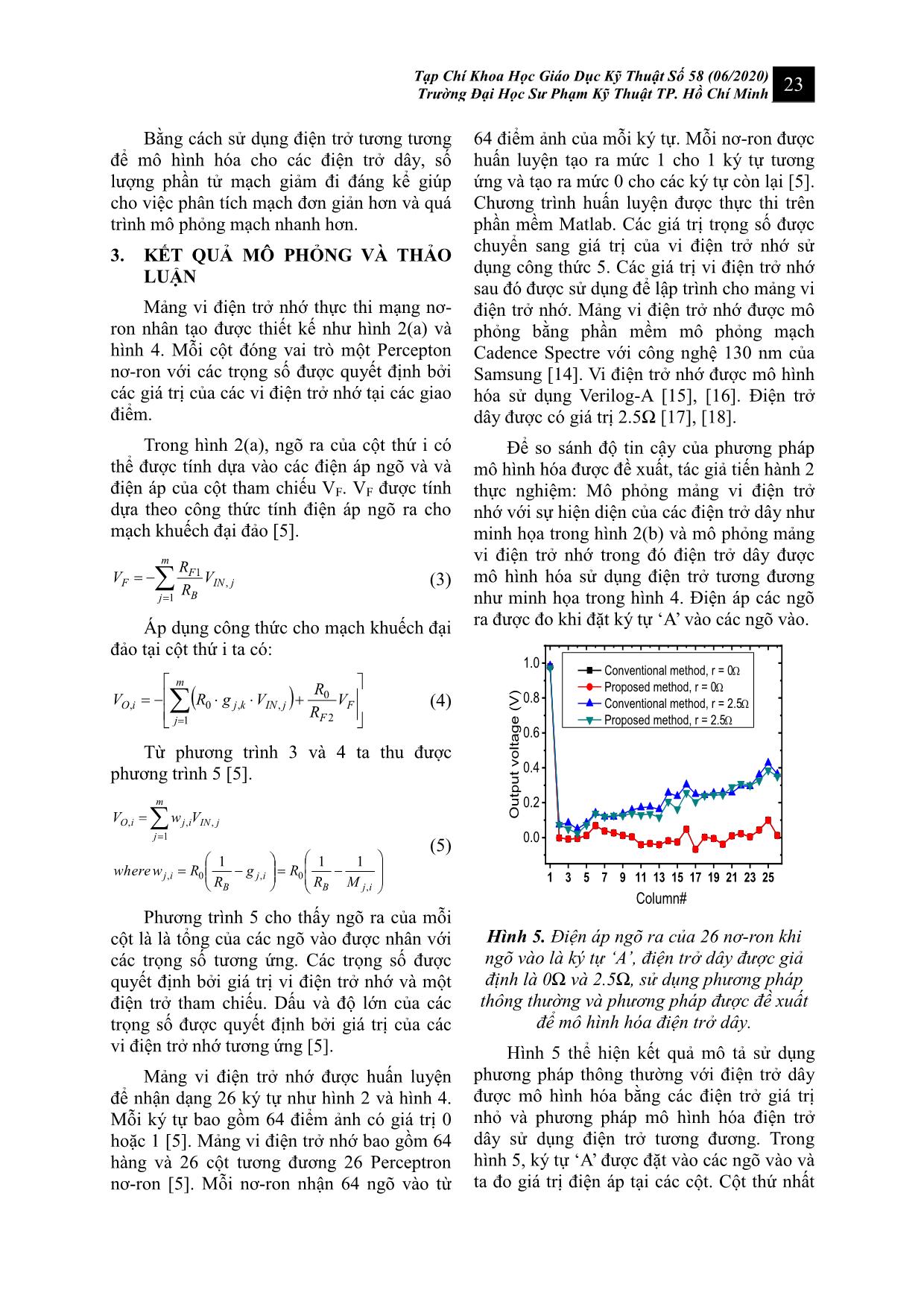

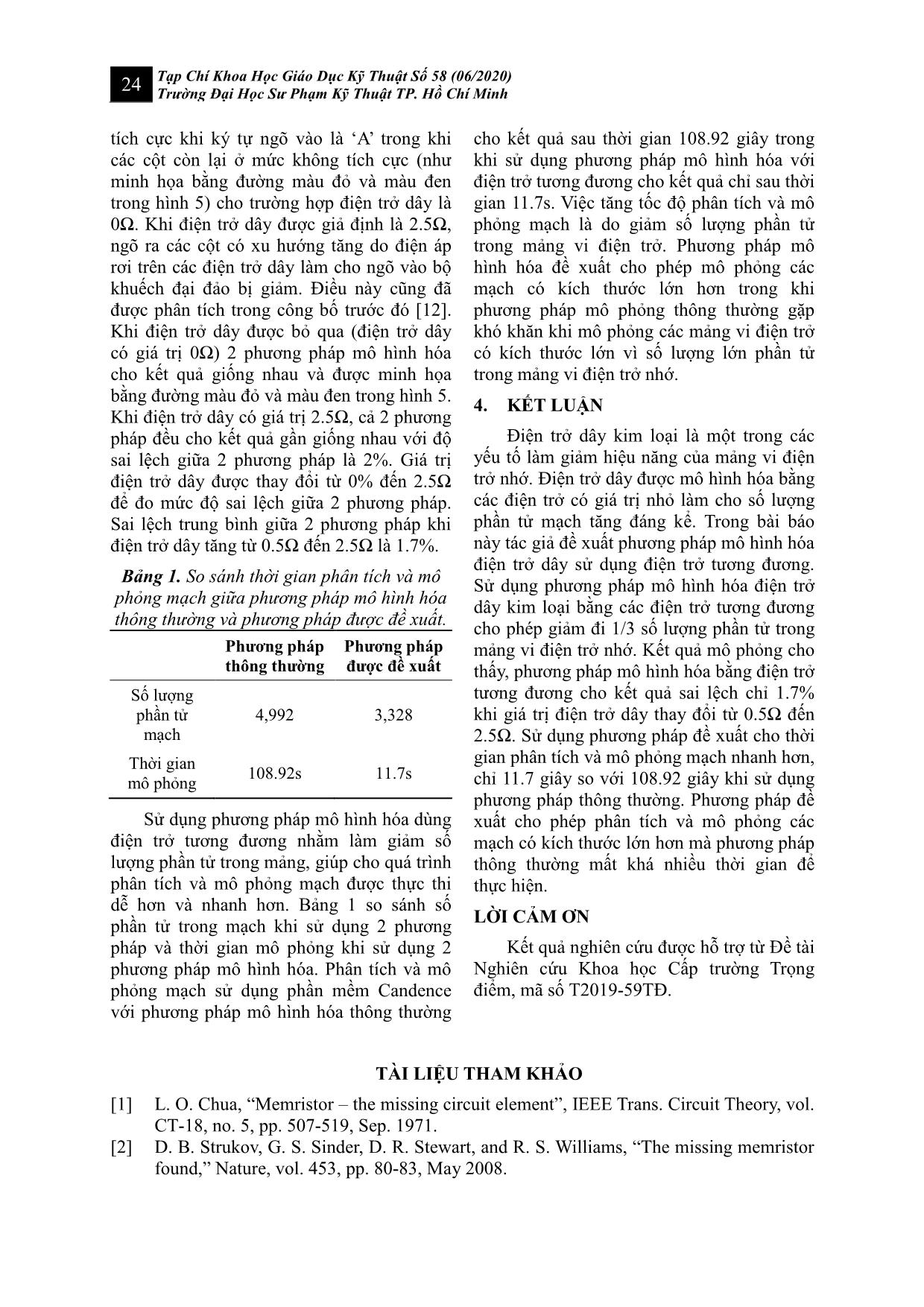

n kiến trúc được đề xuất đó cũng được công bố [6]. Các mảng vi điện trở nhớ trở nên tiềm năng cho việc thực thi các mạng nơ- ron nhân tạo để thay thế cho công nghệ CMOS trước đó. Tuy nhiên, tồn tại một số vấn đề làm cho việc thực thi các mạng nơ- ron nhân tạo dựa trên mảng vi điện trở nhớ bị hạn chế. Một trong các yếu tố đó là điện trở dây dẫn tồn tại trong mảng vi điện trở nhớ [7-12]. Các dây dẫn kim loại trong mảng luôn tồn tại một điện trở nhỏ và các điện trở này ảnh hưởng trực tiếp đến điện áp ngõ ra khi mảng vi điện trở có kích thước lớn [12]. Hình 2. Mảng vi điện trở nhớ (a) bỏ qua các điện trở dây, (b) có sự tồn tại của các điện trở dây RON ROFF Doped Undoped D w V A w=D w<<D Mm,1 M1,1 r VIN,m VIN,j VIN,2 VIN,1 R0 R0 R0 R0 VF RF1 VO,1 VO,2 VO,i VO,n G F G1 G2 Gi Gn r r r r r r r r r r r RB RB RB RB Mj,i Wire resistance RF2 RF2 RF2 RF2 Mm,1 M1,1 VIN,m VIN,j VIN,2 VIN,1 R0 R0 R0 R0 VF RF1 VO,1 VO,2 VO,i VO,n G F G1 G2 Gi Gn RB RB RB RB Mj,i RF2 RF2 RF2 RF2 (a) (b) 22 Tạp Chí Khoa Học Giáo Dục Kỹ Thuật Số 58 (06/2020) Trường Đại Học Sư Phạm Kỹ Thuật TP. Hồ Chí Minh Hình 2 mô tả một mảng vi điện trở nhớ thực thi một mạng nơ-ron nhân tạo. Trong hình 1(a), các điện trở dây được bỏ qua. Trong hình 1(b), các điện trở dây dẫn được xem xét và được mô hình hóa bằng các điện trở có giá trị nhỏ. Việc sử dụng các phần tử điện trở để mô hình hóa cho điện trở dây làm cho số lượng phần tử mạch tăng lên gấp 3 lần. Kết quả là việc tính toán mạch trở nên phức tạp và mô phỏng mạch mất nhiều thời gian. Để hỗ trợ mô hình hóa các điện trở dây, P. Y. Chen đã đề xuất công cụ NeuroSim, cho phép mô phỏng các mảng vi điện trở nhớ với sự có mặt của điện trở dây [13]. Tuy nhiên, NeuroSim là một công cụ phần mềm được viết trên ngôn ngữ C và không sử dụng được trong các công cụ thiết kế và phân tích mạch. Trong nghiên cứu này, tác giả đề xuất phương pháp mô hình hóa điện trở dây sử dụng điện trở tương tương. Việc mô hình hóa điện trở dây bằng điện trở tương tương cho phép các phân tích và mô phỏng mạch nhanh hơn do giảm số lượng phần tử trong mạch. Phương pháp mô hình hóa điện trở dây bằng điện trở tương đương được sử dụng trong quá trình thiết kế, phân tích và mô phỏng các mạng nơ-ron dùng vi điện trở nhớ. 2. MÔ HÌNH HÓA ĐIỆN TRỞ DÂY TRONG MẢNG VI ĐIỆN TRỞ NHỚ Điện trở dây tồn tại trong mảng vi điện trở làm cho điện áp ngõ ra tăng lên do rơi áp trên các điện trở dây. Điều này đã được phân tích, tính toán và kiểm chứng dựa trên mô phỏng mạch bởi S. N. Truong [12]. Hình 3. Phân tích mạch, tính dòng điện tổng cho mỗi cột bằng phương pháp xếp chồng Để tính giá trị điện áp ngõ ra khi có sự hiện diện của các điện trở dây, các cột được phân tích riêng biệt như hình 3. Điện áp ngõ ra mỗi cột có thể được phân tích bằng phương pháp xếp chồng. Dòng điện i0 được tính bằng tổng các dòng điện từ i1 đến im như hình 3. Sử dụng phương pháp xếp chồng, dòng điện qua mỗi vi điện trở nhớ được tính trong khi giả định các ngõ vào cho các vi điện trở khác bằng 0. Giả sử mảng vi điện trở nhớ có kích thước là m hàng và n cột, ij,i là dòng điện chạy qua vi điện trở nhớ ở hàng thứ j và cột thứ i. Điện trở tổng mà dòng điện ij,i chạy qua bao gồm i điện trở trên hàng và m-j+1 điện trở trên cột (như minh họa trong hình 3). Như vậy điện trở tổng sẽ được tính theo công thức 1. rjmirMM ijij )1(,, (1) Trong đó Mj,i là điện trở của vi điện trở nhớ, m là số hàng, i là vị trí cột, j là vị trí hàng, r là giá trị điện trở dây giữa 2 giao điểm. Từ công thức trên cho thấy, giá trị điện trở tại vị trí Mj,i tăng một lượng bằng với điện trở dây tương đương. Như vậy, điện trở dây cho vi điện trở nhớ tại vị trí hàng j và cột i có thể được tính xấp xỉ bằng công thức sau: rjmirR ij )1(, (2) Như vậy, thay vì dùng nhiều điện trở để mô hình hóa cho điện trở dây dẫn trong mảng vi điện trở nhớ, chúng ta có thể mô hình hóa điện trở dây bằng một điện trở Rj,i nối tiếp với vi điện trở nhớ như hình 4. Hình 4. Mô hình hóa điện trở dây bằng phương pháp điện trở tương đương r VIN,m VIN,j VIN,2 VIN,1 R0 VO,i Gi r r r i th column r r r r r r r r r r r r i1 im io M1,i M2,i Mj,i Mm,i (a) ir+(m-j+1)r Mj,i Rj,i Mm,1 M1,1 VIN,m VIN,j VIN,2 VIN,1 R0 R0 R0 R0 VF RF1 VO,1 VO,2 VO,i VO,n G F G1 G2 Gi Gn RB RB RB RB Mj,i RF2 RF2 RF2 RF2 Rj,i R1,1 Tạp Chí Khoa Học Giáo Dục Kỹ Thuật Số 58 (06/2020) Trường Đại Học Sư Phạm Kỹ Thuật TP. Hồ Chí Minh 23 Bằng cách sử dụng điện trở tương tương để mô hình hóa cho các điện trở dây, số lượng phần tử mạch giảm đi đáng kể giúp cho việc phân tích mạch đơn giản hơn và quá trình mô phỏng mạch nhanh hơn. 3. KẾT QUẢ MÔ PHỎNG VÀ THẢO LUẬN Mảng vi điện trở nhớ thực thi mạng nơ- ron nhân tạo được thiết kế như hình 2(a) và hình 4. Mỗi cột đóng vai trò một Percepton nơ-ron với các trọng số được quyết định bởi các giá trị của các vi điện trở nhớ tại các giao điểm. Trong hình 2(a), ngõ ra của cột thứ i có thể được tính dựa vào các điện áp ngõ và và điện áp của cột tham chiếu VF. VF được tính dựa theo công thức tính điện áp ngõ ra cho mạch khuếch đại đảo [5]. m j jIN B F F V R R V 1 , 1 (3) Áp dụng công thức cho mạch khuếch đại đảo tại cột thứ i ta có: F F m j jINkjiO V R R VgRV 2 0 1 ,,0, (4) Từ phương trình 3 và 4 ta thu được phương trình 5 [5]. ijB ij B ij m j jINijiO MR Rg R Rwwhere VwV , 0,0, 1 ,,, 111 (5) Phương trình 5 cho thấy ngõ ra của mỗi cột là là tổng của các ngõ vào được nhân với các trọng số tương ứng. Các trọng số được quyết định bởi giá trị vi điện trở nhớ và một điện trở tham chiếu. Dấu và độ lớn của các trọng số được quyết định bởi giá trị của các vi điện trở nhớ tương ứng [5]. Mảng vi điện trở nhớ được huấn luyện để nhận dạng 26 ký tự như hình 2 và hình 4. Mỗi ký tự bao gồm 64 điểm ảnh có giá trị 0 hoặc 1 [5]. Mảng vi điện trở nhớ bao gồm 64 hàng và 26 cột tương đương 26 Perceptron nơ-ron [5]. Mỗi nơ-ron nhận 64 ngõ vào từ 64 điểm ảnh của mỗi ký tự. Mỗi nơ-ron được huấn luyện tạo ra mức 1 cho 1 ký tự tương ứng và tạo ra mức 0 cho các ký tự còn lại [5]. Chương trình huấn luyện được thực thi trên phần mềm Matlab. Các giá trị trọng số được chuyển sang giá trị của vi điện trở nhớ sử dụng công thức 5. Các giá trị vi điện trở nhớ sau đó được sử dụng để lập trình cho mảng vi điện trở nhớ. Mảng vi điện trở nhớ được mô phỏng bằng phần mềm mô phỏng mạch Cadence Spectre với công nghệ 130 nm của Samsung [14]. Vi điện trở nhớ được mô hình hóa sử dụng Verilog-A [15], [16]. Điện trở dây được có giá trị 2.5Ω [17], [18]. Để so sánh độ tin cậy của phương pháp mô hình hóa được đề xuất, tác giả tiến hành 2 thực nghiệm: Mô phỏng mảng vi điện trở nhớ với sự hiện diện của các điện trở dây như minh họa trong hình 2(b) và mô phỏng mảng vi điện trở nhớ trong đó điện trở dây được mô hình hóa sử dụng điện trở tương đương như minh họa trong hình 4. Điện áp các ngõ ra được đo khi đặt ký tự ‘A’ vào các ngõ vào. Hình 5. Điện áp ngõ ra của 26 nơ-ron khi ngõ vào là ký tự ‘A’, điện trở dây được giả định là 0Ω và 2.5Ω, sử dụng phương pháp thông thường và phương pháp được đề xuất để mô hình hóa điện trở dây. Hình 5 thể hiện kết quả mô tả sử dụng phương pháp thông thường với điện trở dây được mô hình hóa bằng các điện trở giá trị nhỏ và phương pháp mô hình hóa điện trở dây sử dụng điện trở tương đương. Trong hình 5, ký tự ‘A’ được đặt vào các ngõ vào và ta đo giá trị điện áp tại các cột. Cột thứ nhất 1 3 5 7 9 11 13 15 17 19 21 23 25 0.0 0.2 0.4 0.6 0.8 1.0 O u tp u t v o lt a g e ( V ) Column# Conventional method, r = 0W Proposed method, r = 0W Conventional method, r = 2.5W Proposed method, r = 2.5W 24 Tạp Chí Khoa Học Giáo Dục Kỹ Thuật Số 58 (06/2020) Trường Đại Học Sư Phạm Kỹ Thuật TP. Hồ Chí Minh tích cực khi ký tự ngõ vào là ‘A’ trong khi các cột còn lại ở mức không tích cực (như minh họa bằng đường màu đỏ và màu đen trong hình 5) cho trường hợp điện trở dây là 0Ω. Khi điện trở dây được giả định là 2.5Ω, ngõ ra các cột có xu hướng tăng do điện áp rơi trên các điện trở dây làm cho ngõ vào bộ khuếch đại đảo bị giảm. Điều này cũng đã được phân tích trong công bố trước đó [12]. Khi điện trở dây được bỏ qua (điện trở dây có giá trị 0Ω) 2 phương pháp mô hình hóa cho kết quả giống nhau và được minh họa bằng đường màu đỏ và màu đen trong hình 5. Khi điện trở dây có giá trị 2.5Ω, cả 2 phương pháp đều cho kết quả gần giống nhau với độ sai lệch giữa 2 phương pháp là 2%. Giá trị điện trở dây được thay đổi từ 0% đến 2.5Ω để đo mức độ sai lệch giữa 2 phương pháp. Sai lệch trung bình giữa 2 phương pháp khi điện trở dây tăng từ 0.5Ω đến 2.5Ω là 1.7%. Bảng 1. So sánh thời gian phân tích và mô phỏng mạch giữa phương pháp mô hình hóa thông thường và phương pháp được đề xuất. Phương pháp thông thường Phương pháp được đề xuất Số lượng phần tử mạch 4,992 3,328 Thời gian mô phỏng 108.92s 11.7s Sử dụng phương pháp mô hình hóa dùng điện trở tương đương nhằm làm giảm số lượng phần tử trong mảng, giúp cho quá trình phân tích và mô phỏng mạch được thực thi dễ hơn và nhanh hơn. Bảng 1 so sánh số phần tử trong mạch khi sử dụng 2 phương pháp và thời gian mô phỏng khi sử dụng 2 phương pháp mô hình hóa. Phân tích và mô phỏng mạch sử dụng phần mềm Candence với phương pháp mô hình hóa thông thường cho kết quả sau thời gian 108.92 giây trong khi sử dụng phương pháp mô hình hóa với điện trở tương đương cho kết quả chỉ sau thời gian 11.7s. Việc tăng tốc độ phân tích và mô phỏng mạch là do giảm số lượng phần tử trong mảng vi điện trở. Phương pháp mô hình hóa đề xuất cho phép mô phỏng các mạch có kích thước lớn hơn trong khi phương pháp mô phỏng thông thường gặp khó khăn khi mô phỏng các mảng vi điện trở có kích thước lớn vì số lượng lớn phần tử trong mảng vi điện trở nhớ. 4. KẾT LUẬN Điện trở dây kim loại là một trong các yếu tố làm giảm hiệu năng của mảng vi điện trở nhớ. Điện trở dây được mô hình hóa bằng các điện trở có giá trị nhỏ làm cho số lượng phần tử mạch tăng đáng kể. Trong bài báo này tác giả đề xuất phương pháp mô hình hóa điện trở dây sử dụng điện trở tương đương. Sử dụng phương pháp mô hình hóa điện trở dây kim loại bằng các điện trở tương đương cho phép giảm đi 1/3 số lượng phần tử trong mảng vi điện trở nhớ. Kết quả mô phỏng cho thấy, phương pháp mô hình hóa bằng điện trở tương đương cho kết quả sai lệch chỉ 1.7% khi giá trị điện trở dây thay đổi từ 0.5Ω đến 2.5Ω. Sử dụng phương pháp đề xuất cho thời gian phân tích và mô phỏng mạch nhanh hơn, chỉ 11.7 giây so với 108.92 giây khi sử dụng phương pháp thông thường. Phương pháp đề xuất cho phép phân tích và mô phỏng các mạch có kích thước lớn hơn mà phương pháp thông thường mất khá nhiều thời gian để thực hiện. LỜI CẢM ƠN Kết quả nghiên cứu được hỗ trợ từ Đề tài Nghiên cứu Khoa học Cấp trường Trọng điểm, mã số T2019-59TĐ. TÀI LIỆU THAM KHẢO [1] L. O. Chua, “Memristor – the missing circuit element”, IEEE Trans. Circuit Theory, vol. CT-18, no. 5, pp. 507-519, Sep. 1971. [2] D. B. Strukov, G. S. Sinder, D. R. Stewart, and R. S. Williams, “The missing memristor found,” Nature, vol. 453, pp. 80-83, May 2008. Tạp Chí Khoa Học Giáo Dục Kỹ Thuật Số 58 (06/2020) Trường Đại Học Sư Phạm Kỹ Thuật TP. Hồ Chí Minh 25 [3] S. H. Jo, T. Chang, I. Ebong, B. B. Bhadviya, P. Mazumder, and W. Lu, “Nanoscale memristor device as synapse in neuromorphic systems”, Nano Letters, vol. 10, no. 4, pp. 1297-1301, Mar. 2010. [4] R. S. Williams, “How we found the missing memristor”, IEEE Spectrum, vol. 45, iss. 12, pp. 28-35, Dec. 2008. [5] S. N. Truong and K. S. Min “New memristor-based crossbar array architecture with 50- % area reduction and 48-% power saving for matrix-vector multiplication of analog neuromorphic computing”, Journal of Semiconductor Technology and Science, vol. 14, no. 3, pp. 356-363, Jun. 2014 [6] S. Y. Sun, H. Xu, J. Li, Q. Li, and H. Liu, “Cascaded Architecture for Memristor Crossbar Array Based Larger-Scale Neuromorphic Computing”, IEEE Access, vol. 7, pp. 61679-61688, May 2019 [7] J. Liang and H. -. P. Wong, “Cross-Point Memory Array Without Cell Selectors— Device Characteristics and Data Storage Pattern Dependencies”, in IEEE Transactions on Electron Devices, vol. 57, no. 10, pp. 2531-2538, Oct. 2010. [8] E. Linn, R. Rosezin, C. Kügeler, and R. Waser, “Complementary resistive switches for passive nanocrossbar memories”, Nature Materials, vol. 9, pp. 403-406, 2010. [9] S. H. Shin, S. D. Byeon, J. S. Song, S. N. Truong, H. S. Mo, D. J. Kim, and K. S. Min, “Dynamic reference scheme with improved read voltage margin for compensating cell- position and back ground-pattern dependencies in pure memristor array”, Journal of Semiconductor Technology and Science, vol.15, No.6, Dec. 2015. [10] A. Adeyemo, A. Jabir, J. Mathew, “Minimising Impact of Wire Resistance in Low-Power Crossbar Array Write Scheme”, Journal of Low Power Electronics, vol. 13, pp. 649-660, 2017 [11] A. Levisse, P. Royer, B. Giraud, J. P. Noel, M. Moreau, J. M. Portal, “Architecture, design and technology guidelines for crosspoint memories”, IEEE/ACM International Symposium on Nanoscale Architectures (NANOARCH), 2017. [12] S. N. Truong, “Compensating Circuit to Reduce the Impact of Wire Resistance in a Memristor Crossbar-Based Perceptron Neural Network”, Micromachines, vol. 10, no. 671, 2019 [13] P. Y. Chen, X. Peng, S. Yu, “NeuroSim: A Circuit-Level Macro Model for Benchmarking Neuro-Inspired Architectures in Online Learning”, IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, vol. 13, pp. 3067-3080, 2018 [14] Virtuoso Spectre Circuit Simulator User Guide, Cadence, San Jose, CA, USA, 2004 [15] S. J. Ham, H. S. Mo, and K. S. Min, “Low-power VDD/3 write scheme with inversion coding circuit for complementary memristor array”, IEEE Trans. Nanotechnology, vol. 12, no. 5, pp. 851-857, Sep. 2013. [16] S. N. Truong, K. V. Pham, W. S. Yang, H. Shin, K. Pedrotti, K. S. Min, “New pulse amplitude modulation for fine tuning of memristor synapses”, Microelectronic Jounal, vol. 55, pp. 162-168, Aug. 2016. [17] J. Liang, H. S. P. Wong, “Cross-point memristor array without cell selector — device characteristics and data storage pattern dependencies”, IEEE Trans. Electron. Device, vol. 57, no. 10, pp. 2531-2538, 2010. [18] ITRS, International Technology Roadmap for Semiconductors, 2007. Tác giả chịu trách nhiệm bài viết: TS. Trương Ngọc Sơn Trường Đại học Sư phạm Kỹ thuật TP.HCM Email: sontn@hcmute.edu.vn

File đính kèm:

phuong_phap_mo_hinh_hoa_dien_tro_day_trong_mang_vi_dien_tro.pdf

phuong_phap_mo_hinh_hoa_dien_tro_day_trong_mang_vi_dien_tro.pdf