Phương pháp điều chế độ rộng xung của biến tần ma trận đa bậc nhằm triệt tiêu điện áp điểm nối chung

Bài báo trình bày phương pháp điều chế độ rộng xung cho bộ biến tần ma trận đa bậc nhằm triệt tiêu điện áp điểm nối

chung. Bộ biến tần ma trận đa bậc được nghiên cứu trong bài báo được xây dựng từ sự kết hợp giữa bộ nghịch lưu ba

bậc dạng T và hai bộ chỉnh lưu nguồn dòng mắc nối tiếp với nhau. Ngoài những ưu điểm của bộ biến tần ma trận truyền

thống như: dòng điện nguồn và tải dạng sin, công suất có thể truyền theo 2 chiều từ nguồn sang tải hoặc tải sang nguồn

thì bộ biến tần ma trận đa bậc có thêm ưu điểm đó là: điện áp trên tài có 3 mức, do đó chất lượng điện áp/dòng điện trên

tải sẽ cao hơn so với bộ biến tần ma trận truyền thống. Điện áp điểm nối chung là nguyên nhân gây ra sự hư hỏng cách

điện của động cơ, gây ra các nhiễu điện từ. Do đó, trong nghiên cứu này, một phương pháp điều chế vector không gian

phù hợp sẽ được đề xuất để triệt tiêu điện áp điểm nối chung. Để xác nhận tính đúng đắn của phương pháp đề xuất, các

kết quả mô phỏng được xây dựng bằng phần mềm Psim, cũng như các kết quả thực nghiệm được xây dựng trong phòng

thí nghiệm sẽ được trình bày.

Trang 1

Trang 2

Trang 3

Trang 4

Trang 5

Trang 6

Tóm tắt nội dung tài liệu: Phương pháp điều chế độ rộng xung của biến tần ma trận đa bậc nhằm triệt tiêu điện áp điểm nối chung

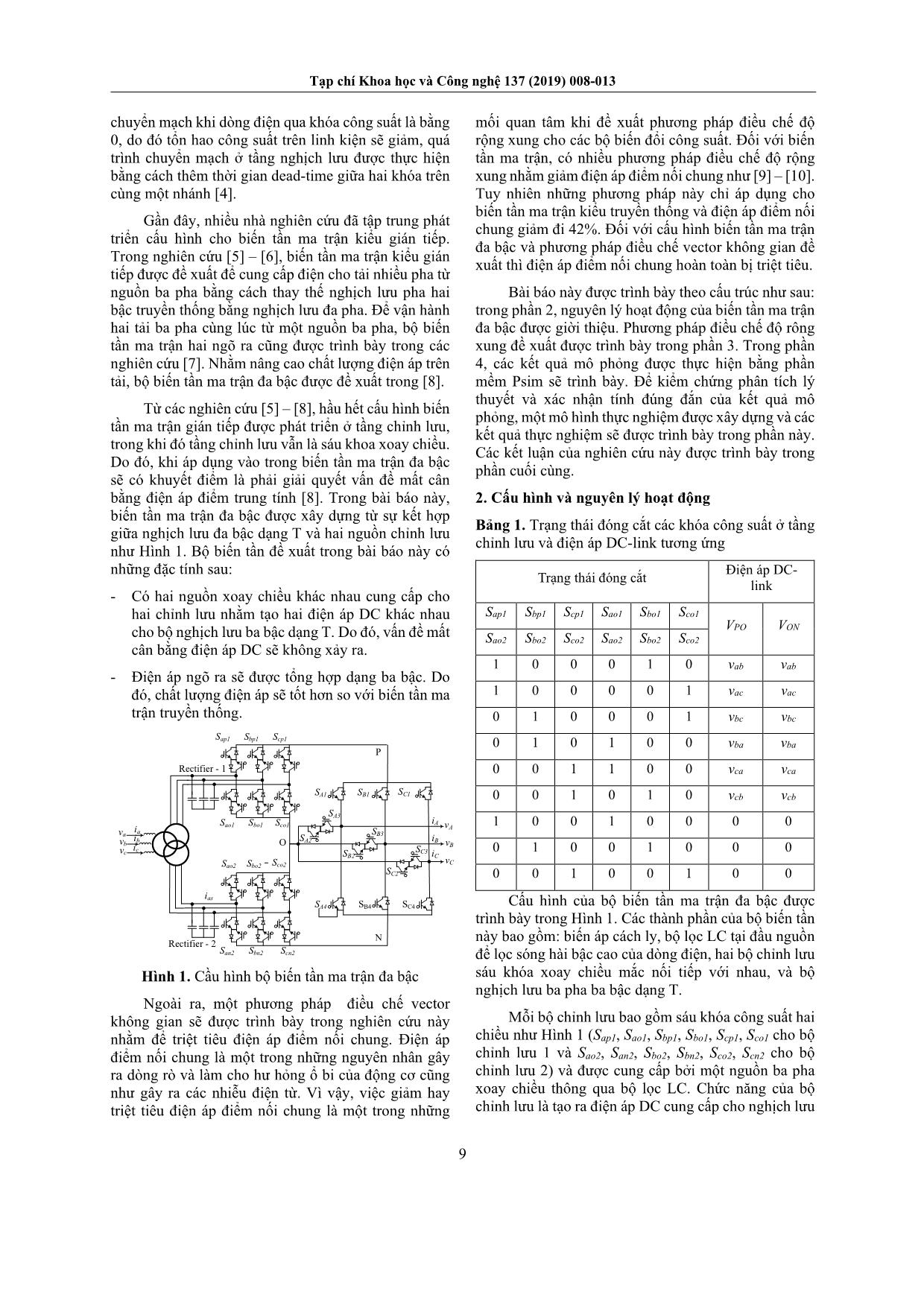

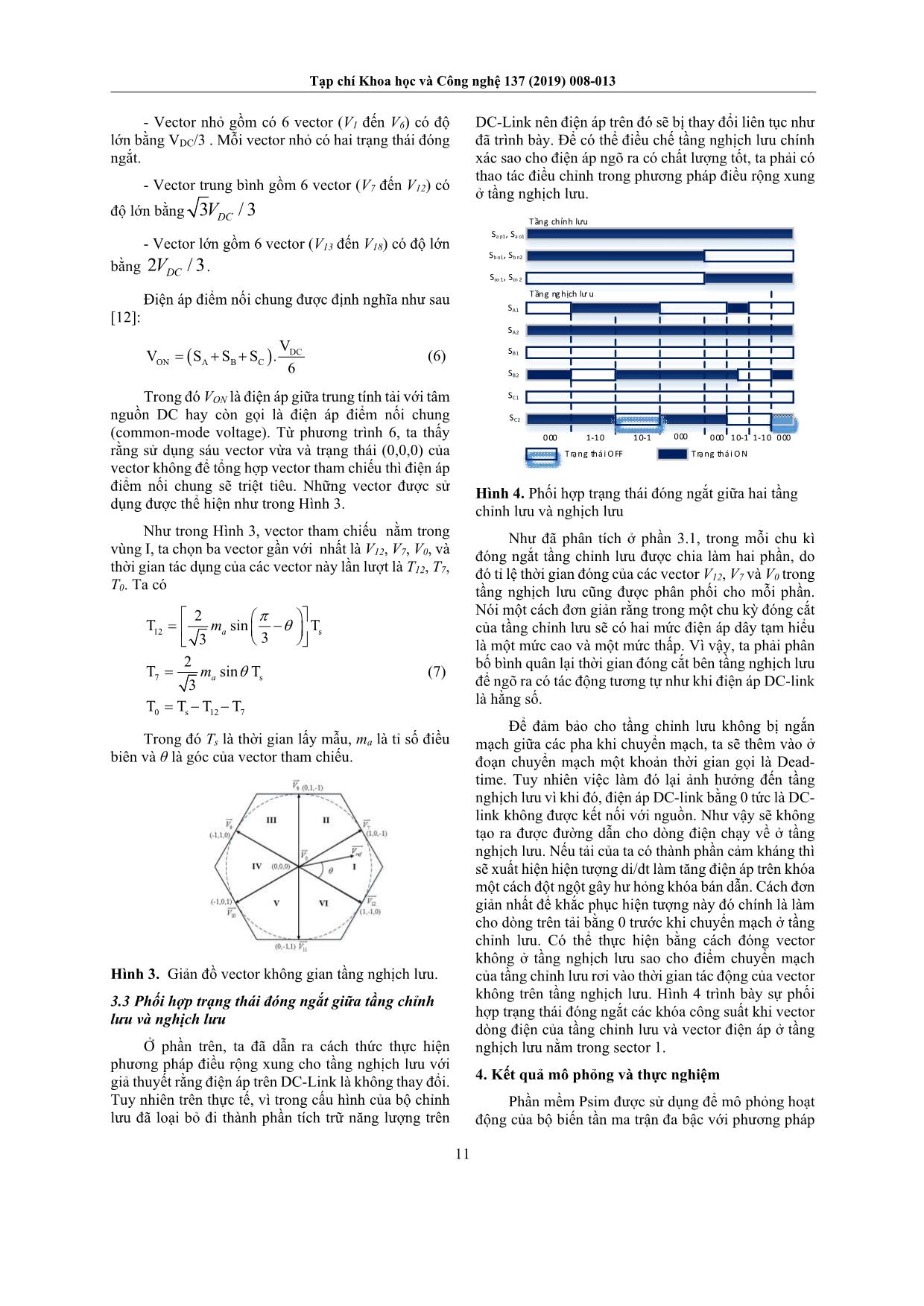

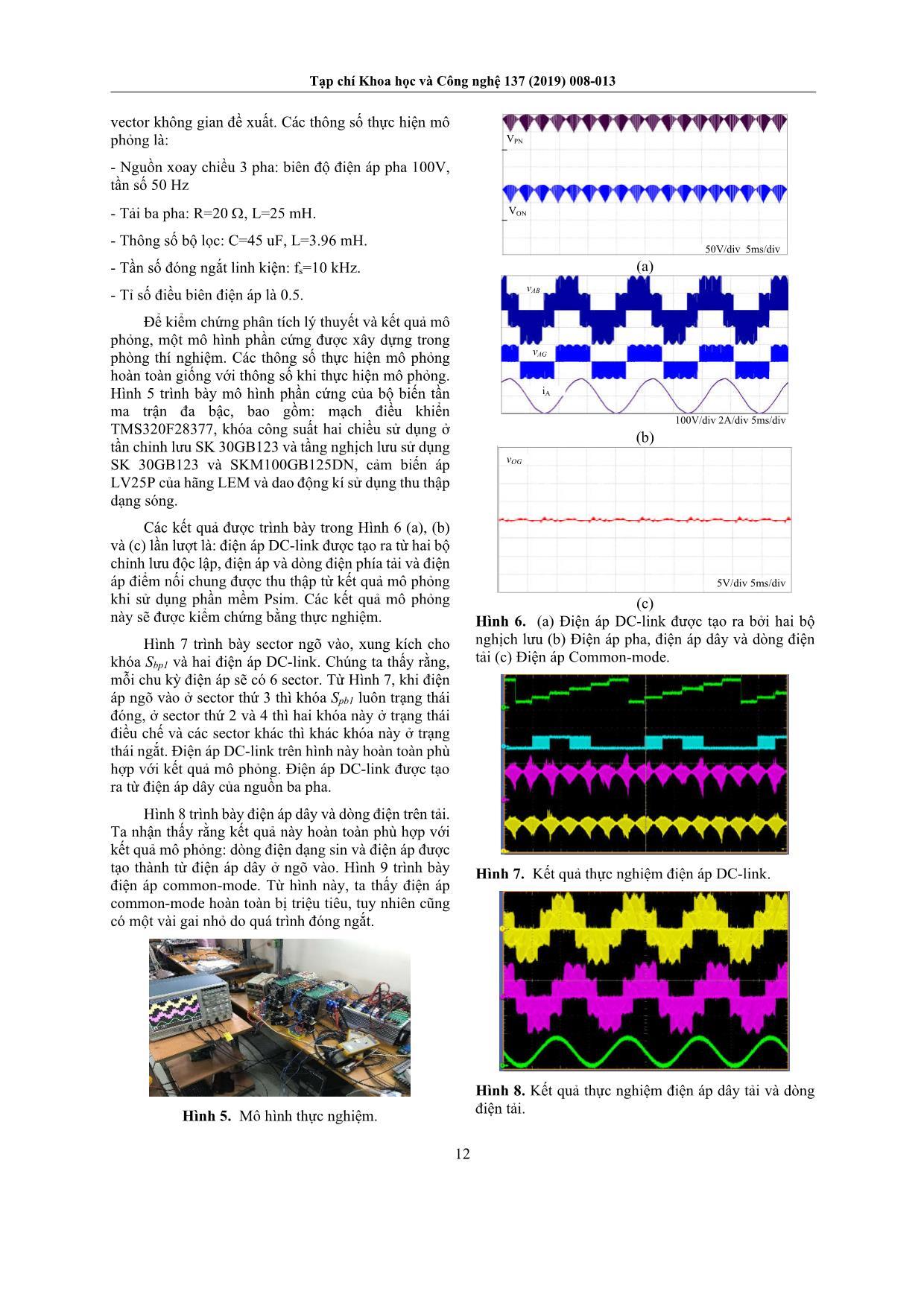

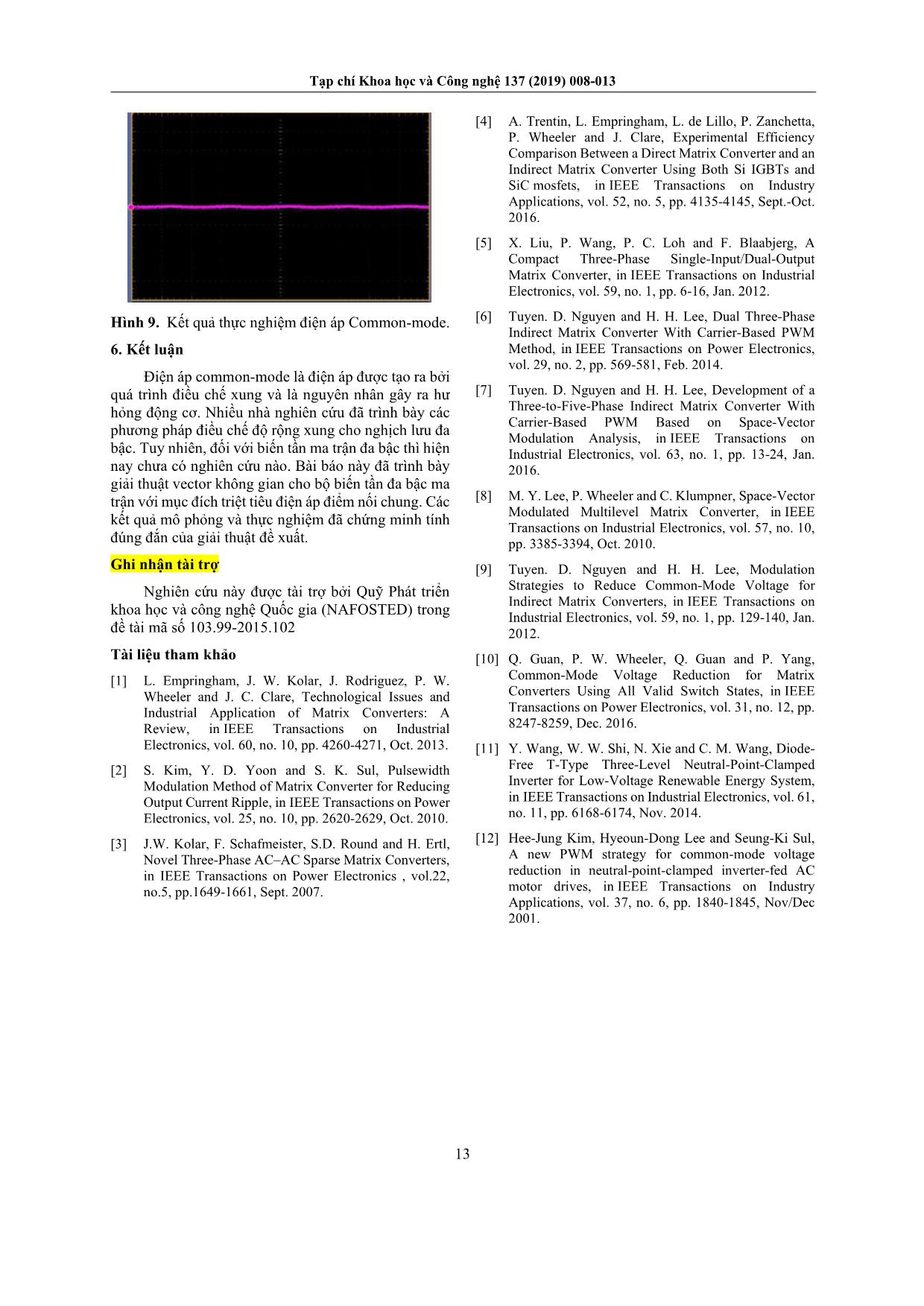

n 4, các kết quả mô phỏng được thực hiện bằng phần mềm Psim sẽ trình bày. Để kiểm chứng phân tích lý thuyết và xác nhận tính đúng đắn của kết quả mô phỏng, một mô hình thực nghiệm được xây dựng và các kết quả thực nghiệm sẽ được trình bày trong phần này. Các kết luận của nghiên cứu này được trình bày trong phần cuối cùng. 2. Cấu hình và nguyên lý hoạt động Bảng 1. Trạng thái đóng cắt các khóa công suất ở tầng chỉnh lưu và điện áp DC-link tương ứng Trạng thái đóng cắt Điện áp DC- link Sap1 Sbp1 Scp1 Sao1 Sbo1 Sco1 VPO VON Sao2 Sbo2 Sco2 Sao2 Sbo2 Sco2 1 0 0 0 1 0 vab vab 1 0 0 0 0 1 vac vac 0 1 0 0 0 1 vbc vbc 0 1 0 1 0 0 vba vba 0 0 1 1 0 0 vca vca 0 0 1 0 1 0 vcb vcb 1 0 0 1 0 0 0 0 0 1 0 0 1 0 0 0 0 0 1 0 0 1 0 0 Cấu hình của bộ biến tần ma trận đa bậc được trình bày trong Hình 1. Các thành phần của bộ biến tần này bao gồm: biến áp cách ly, bộ lọc LC tại đầu nguồn để lọc sóng hài bậc cao của dòng điện, hai bộ chỉnh lưu sáu khóa xoay chiều mắc nối tiếp với nhau, và bộ nghịch lưu ba pha ba bậc dạng T. Mỗi bộ chỉnh lưu bao gồm sáu khóa công suất hai chiều như Hình 1 (Sap1, Sao1, Sbp1, Sbo1, Scp1, Sco1 cho bộ chỉnh lưu 1 và Sao2, San2, Sbo2, Sbn2, Sco2, Scn2 cho bộ chỉnh lưu 2) và được cung cấp bởi một nguồn ba pha xoay chiều thông qua bộ lọc LC. Chức năng của bộ chỉnh lưu là tạo ra điện áp DC cung cấp cho nghịch lưu Tạp chí Khoa học và Công nghệ 137 (2019) 008-013 10 đa bậc và đảm bảo dòng điện ở nguồn AC dạng sin. Bộ chỉnh lưu thứ nhất tạo ra điện áp VPO và bộ chỉnh lưu thứ 2 tạo ra điện VNO. Bảng 1 trình bày trạng thái đóng cắt các khóa công suất bán dẫn và điện áp DC-link. Bộ nghịch lưu ba bậc dạng T là cấu hình mở rộng của bộ nghịch lưu hai bậc ba pha truyền thống, bằng cách thêm ba khóa công suất xoay chiều nối ba ngõ ra của tải vào điểm trung tính O. So sánh với bộ nghịch lưu ba pha NPC truyền thống thì bộ nghịch lưu ba pha dạng T có nhiều ưu điểm hơn: tổn hao ít hơn, số lượng linh kiện bán dẫn ít hơn do không sử dụng các diode kẹp [11]. Từ Hình 1, trạng thái đóng cắt và điện áp pha tải của bộ nghịch lưu ba pha được cho ở Bảng 2: Bảng 2. Trạng thái đóng cắt các khóa công suất ở tầng chỉnh lưu và điện áp pha tải – trung tính tương ứng. Trạng thái nhánh SX Trạng thái đóng ngắt các khóa công suất trong một nhánh X = (A, B, C) Điện áp pha tải – trung tính VXO SX1 SX2 SX3 SX4 1 1 1 0 0 VPO 0 0 1 1 0 0 -1 0 0 1 1 -VON Bộ nghịch lưu ba bậc dạng T được cấp nguồn DC tạo ra từ hai bộ chỉnh lưu là VPO và VON. Chức năng của bộ nghịch lưu là tạo ra điện áp trên tải với tần số và biên độ thay đổi được bằng cách phối hợp các trạng thái đóng ngắt của các khóa bán dẫn. 3. Phương pháp điều chế độ rộng xung triệt tiêu điện áp điểm nối chung. 3.1 Điều khiển tầng chỉnh lưu Hai bộ chỉnh lưu 1 và 2 được điều khiển làm sao cho hai điện áp DC tạo ra là VPO và VON giống nhau. Như trình bày ở Hình 1, thì hai bộ chỉnh lưu này được cung cấp bằng hai nguồn xoay chiều ba pha giống nhau. Do đó, trạng thái đóng ngắt của ba khóa xoay chiều phía trên/phía dưới của bộ chỉnh lưu 1 hoàn toàn tương tự như trạng thái đóng ngắt của ba khóa xoay chiều phía trên/phía dưới của bộ chỉnh lưu 2. Để tránh diễn giải trùng lặp, trong phần này chỉ trình bày phương pháp điều khiển bộ chỉnh lưu 1, bộ chỉnh lưu 2 hoạt động tương tự. Giả sử điện áp cung cấp cho bộ chỉnh lưu này là cân bằng và được biểu diễn bằng các phương trình sau: in in in sin( ) sin( 2 3) sin( 2 3) a in b in c in v V t v V t v V t (1) Biểu đồ vector không gian của tầng chỉnh lưu được trình bày trên Hình 2 gồm sáu vector dòng điện tích cực và ba vector không. Mỗi vector dòng điện thể hiện sự kết hợp của điện áp pha ngõ vào cho điện áp một chiều DC. Ví dụ, vector Iab thể hiện sự kết hợp của điện áp vào pha a (cực dương P của DC-link) và pha b (điểm trung tính O của DC-link). Nếu ta giả sử rằng vector dòng điện ở ngõ vào Iin nằm trong sector 1, ta có thể tổng hợp vector từ hai vector liền kề là: in ab acI d I d Ig d (2) trong đó abI , acI là hai vector dòng điện liền kề và dg , dd là tỷ số đóng của hai vector tương ứng. ain Iab Ibc Ibc Iba Ica Icb iin 1 23 4 5 6 IaaIbb Icc dd dg Hình 2. Giản đồ vector không gian tầng chỉnh lưu Tuy nhiên, để đảm bảo điện áp ở DC-link có giá trị lớn nhất thì vector không Iaa, Ibb, Icc không được sử dụng. Do đó, tỷ số đóng của hai vector tích cực sẽ được tính lại như sau [6] – [7]: b ab a d v d d d v g g d (3) c ac a d v d d d v d g d (4) Điện áp trung bình trong một chu kỳ lấy mẫu của điện áp VPO và VON là: 23 2 in dc ab a b ac a c a V V d v v d v v v (5) 3.2 Điều khiển tầng nghịch lưu Với bộ nghịch lưu NPC ba bậc dạng T sẽ có 27 trạng thái đóng ngắt khác nhau. Mỗi một trạng thái đóng ngắt được mô tả qua tổ hợp trạng thái SX = -1, 0, 1 (X=A,B,C) như trình bày ở Bảng 2. Dựa vào độ lớn điện áp của vector không gian, ta chia làm bốn nhóm: - Vector không (V0) đại diện cho ba trạng thái (1,1,1), (0,0,0) và (-1,-1,-1), độ lớn của vector này bằng 0. Tạp chí Khoa học và Công nghệ 137 (2019) 008-013 11 - Vector nhỏ gồm có 6 vector (V1 đến V6) có độ lớn bằng VDC/3 . Mỗi vector nhỏ có hai trạng thái đóng ngắt. - Vector trung bình gồm 6 vector (V7 đến V12) có độ lớn bằng 3 / 3DCV - Vector lớn gồm 6 vector (V13 đến V18) có độ lớn bằng 2 / 3DCV . Điện áp điểm nối chung được định nghĩa như sau [12]: DCON A B C V V S S S . 6 (6) Trong đó VON là điện áp giữa trung tính tải với tâm nguồn DC hay còn gọi là điện áp điểm nối chung (common-mode voltage). Từ phương trình 6, ta thấy rằng sử dụng sáu vector vừa và trạng thái (0,0,0) của vector không để tổng hợp vector tham chiếu thì điện áp điểm nối chung sẽ triệt tiêu. Những vector được sử dụng được thể hiện như trong Hình 3. Như trong Hình 3, vector tham chiếu nằm trong vùng I, ta chọn ba vector gần với nhất là V12, V7, V0, và thời gian tác dụng của các vector này lần lượt là T12, T7, T0. Ta có 12 s 7 s 0 s 12 7 2 T sin T 33 2 T sin T 3 T T T T a a m m (7) Trong đó Ts là thời gian lấy mẫu, ma là tỉ số điều biên và θ là góc của vector tham chiếu. Hình 3. Giản đồ vector không gian tầng nghịch lưu. 3.3 Phối hợp trạng thái đóng ngắt giữa tầng chỉnh lưu và nghịch lưu Ở phần trên, ta đã dẫn ra cách thức thực hiện phương pháp điều rộng xung cho tầng nghịch lưu với giả thuyết rằng điện áp trên DC-Link là không thay đổi. Tuy nhiên trên thực tế, vì trong cấu hình của bộ chỉnh lưu đã loại bỏ đi thành phần tích trữ năng lượng trên DC-Link nên điện áp trên đó sẽ bị thay đổi liên tục như đã trình bày. Để có thể điều chế tầng nghịch lưu chính xác sao cho điện áp ngõ ra có chất lượng tốt, ta phải có thao tác điều chỉnh trong phương pháp điều rộng xung ở tầng nghịch lưu. T rạng thá i O FF T rạ ng thá i O N 1-10 T ầng chỉnh lưu T ầng ng hịch lư u Sa p1, Sa o1 Sb o1, Sb n2 Sco 1, Scn 2 SA1 SA2 SB1 SB2 SC1 SC2 000 10-1 000 000 10-1 1-10 000 Hình 4. Phối hợp trạng thái đóng ngắt giữa hai tầng chỉnh lưu và nghịch lưu Như đã phân tích ở phần 3.1, trong mỗi chu kì đóng ngắt tầng chỉnh lưu được chia làm hai phần, do đó tỉ lệ thời gian đóng của các vector V12, V7 và V0 trong tầng nghịch lưu cũng được phân phối cho mỗi phần. Nói một cách đơn giản rằng trong một chu kỳ đóng cắt của tầng chỉnh lưu sẽ có hai mức điện áp dây tạm hiểu là một mức cao và một mức thấp. Vì vậy, ta phải phân bố bình quân lại thời gian đóng cắt bên tầng nghịch lưu để ngõ ra có tác động tương tự như khi điện áp DC-link là hằng số. Để đảm bảo cho tầng chỉnh lưu không bị ngắn mạch giữa các pha khi chuyển mạch, ta sẽ thêm vào ở đoạn chuyển mạch một khoản thời gian gọi là Dead- time. Tuy nhiên việc làm đó lại ảnh hưởng đến tầng nghịch lưu vì khi đó, điện áp DC-link bằng 0 tức là DC- link không được kết nối với nguồn. Như vậy sẽ không tạo ra được đường dẫn cho dòng điện chạy về ở tầng nghịch lưu. Nếu tải của ta có thành phần cảm kháng thì sẽ xuất hiện hiện tượng di/dt làm tăng điện áp trên khóa một cách đột ngột gây hư hỏng khóa bán dẫn. Cách đơn giản nhất để khắc phục hiện tượng này đó chính là làm cho dòng trên tải bằng 0 trước khi chuyển mạch ở tầng chỉnh lưu. Có thể thực hiện bằng cách đóng vector không ở tầng nghịch lưu sao cho điểm chuyển mạch của tầng chỉnh lưu rơi vào thời gian tác động của vector không trên tầng nghịch lưu. Hình 4 trình bày sự phối hợp trạng thái đóng ngắt các khóa công suất khi vector dòng điện của tầng chỉnh lưu và vector điện áp ở tầng nghịch lưu nằm trong sector 1. 4. Kết quả mô phỏng và thực nghiệm Phần mềm Psim được sử dụng để mô phỏng hoạt động của bộ biến tần ma trận đa bậc với phương pháp Tạp chí Khoa học và Công nghệ 137 (2019) 008-013 12 vector không gian đề xuất. Các thông số thực hiện mô phỏng là: - Nguồn xoay chiều 3 pha: biên độ điện áp pha 100V, tần số 50 Hz - Tải ba pha: R=20 , L=25 mH. - Thông số bộ lọc: C=45 uF, L=3.96 mH. - Tần số đóng ngắt linh kiện: fs=10 kHz. - Tỉ số điều biên điện áp là 0.5. Để kiểm chứng phân tích lý thuyết và kết quả mô phỏng, một mô hình phần cứng được xây dựng trong phòng thí nghiệm. Các thông số thực hiện mô phỏng hoàn toàn giống với thông số khi thực hiện mô phỏng. Hình 5 trình bày mô hình phần cứng của bộ biến tần ma trận đa bậc, bao gồm: mạch điều khiển TMS320F28377, khóa công suất hai chiều sử dụng ở tần chỉnh lưu SK 30GB123 và tầng nghịch lưu sử dụng SK 30GB123 và SKM100GB125DN, cảm biến áp LV25P của hãng LEM và dao động kí sử dụng thu thập dạng sóng. Các kết quả được trình bày trong Hình 6 (a), (b) và (c) lần lượt là: điện áp DC-link được tạo ra từ hai bộ chỉnh lưu độc lập, điện áp và dòng điện phía tải và điện áp điểm nối chung được thu thập từ kết quả mô phỏng khi sử dụng phần mềm Psim. Các kết quả mô phỏng này sẽ được kiểm chứng bằng thực nghiệm. Hình 7 trình bày sector ngõ vào, xung kích cho khóa Sbp1 và hai điện áp DC-link. Chúng ta thấy rằng, mỗi chu kỳ điện áp sẽ có 6 sector. Từ Hình 7, khi điện áp ngõ vào ở sector thứ 3 thì khóa Spb1 luôn trạng thái đóng, ở sector thứ 2 và 4 thì hai khóa này ở trạng thái điều chế và các sector khác thì khác khóa này ở trạng thái ngắt. Điện áp DC-link trên hình này hoàn toàn phù hợp với kết quả mô phỏng. Điện áp DC-link được tạo ra từ điện áp dây của nguồn ba pha. Hình 8 trình bày điện áp dây và dòng điện trên tải. Ta nhận thấy rằng kết quả này hoàn toàn phù hợp với kết quả mô phỏng: dòng điện dạng sin và điện áp được tạo thành từ điện áp dây ở ngõ vào. Hình 9 trình bày điện áp common-mode. Từ hình này, ta thấy điện áp common-mode hoàn toàn bị triệu tiêu, tuy nhiên cũng có một vài gai nhỏ do quá trình đóng ngắt. Hình 5. Mô hình thực nghiệm. 50V/div 5ms/div VPN VON (a) vAB vAG iA 100V/div 2A/div 5ms/div (b) vOG 5V/div 5ms/div (c) Hình 6. (a) Điện áp DC-link được tạo ra bởi hai bộ nghịch lưu (b) Điện áp pha, điện áp dây và dòng điện tải (c) Điện áp Common-mode. Hình 7. Kết quả thực nghiệm điện áp DC-link. Hình 8. Kết quả thực nghiệm điện áp dây tải và dòng điện tải. Tạp chí Khoa học và Công nghệ 137 (2019) 008-013 13 Hình 9. Kết quả thực nghiệm điện áp Common-mode. 6. Kết luận Điện áp common-mode là điện áp được tạo ra bởi quá trình điều chế xung và là nguyên nhân gây ra hư hỏng động cơ. Nhiều nhà nghiên cứu đã trình bày các phương pháp điều chế độ rộng xung cho nghịch lưu đa bậc. Tuy nhiên, đối với biến tần ma trận đa bậc thì hiện nay chưa có nghiên cứu nào. Bài báo này đã trình bày giải thuật vector không gian cho bộ biến tần đa bậc ma trận với mục đích triệt tiêu điện áp điểm nối chung. Các kết quả mô phỏng và thực nghiệm đã chứng minh tính đúng đắn của giải thuật đề xuất. Ghi nhận tài trợ Nghiên cứu này được tài trợ bởi Quỹ Phát triển khoa học và công nghệ Quốc gia (NAFOSTED) trong đề tài mã số 103.99-2015.102 Tài liệu tham khảo [1] L. Empringham, J. W. Kolar, J. Rodriguez, P. W. Wheeler and J. C. Clare, Technological Issues and Industrial Application of Matrix Converters: A Review, in IEEE Transactions on Industrial Electronics, vol. 60, no. 10, pp. 4260-4271, Oct. 2013. [2] S. Kim, Y. D. Yoon and S. K. Sul, Pulsewidth Modulation Method of Matrix Converter for Reducing Output Current Ripple, in IEEE Transactions on Power Electronics, vol. 25, no. 10, pp. 2620-2629, Oct. 2010. [3] J.W. Kolar, F. Schafmeister, S.D. Round and H. Ertl, Novel Three-Phase AC–AC Sparse Matrix Converters, in IEEE Transactions on Power Electronics , vol.22, no.5, pp.1649-1661, Sept. 2007. [4] A. Trentin, L. Empringham, L. de Lillo, P. Zanchetta, P. Wheeler and J. Clare, Experimental Efficiency Comparison Between a Direct Matrix Converter and an Indirect Matrix Converter Using Both Si IGBTs and SiC mosfets, in IEEE Transactions on Industry Applications, vol. 52, no. 5, pp. 4135-4145, Sept.-Oct. 2016. [5] X. Liu, P. Wang, P. C. Loh and F. Blaabjerg, A Compact Three-Phase Single-Input/Dual-Output Matrix Converter, in IEEE Transactions on Industrial Electronics, vol. 59, no. 1, pp. 6-16, Jan. 2012. [6] Tuyen. D. Nguyen and H. H. Lee, Dual Three-Phase Indirect Matrix Converter With Carrier-Based PWM Method, in IEEE Transactions on Power Electronics, vol. 29, no. 2, pp. 569-581, Feb. 2014. [7] Tuyen. D. Nguyen and H. H. Lee, Development of a Three-to-Five-Phase Indirect Matrix Converter With Carrier-Based PWM Based on Space-Vector Modulation Analysis, in IEEE Transactions on Industrial Electronics, vol. 63, no. 1, pp. 13-24, Jan. 2016. [8] M. Y. Lee, P. Wheeler and C. Klumpner, Space-Vector Modulated Multilevel Matrix Converter, in IEEE Transactions on Industrial Electronics, vol. 57, no. 10, pp. 3385-3394, Oct. 2010. [9] Tuyen. D. Nguyen and H. H. Lee, Modulation Strategies to Reduce Common-Mode Voltage for Indirect Matrix Converters, in IEEE Transactions on Industrial Electronics, vol. 59, no. 1, pp. 129-140, Jan. 2012. [10] Q. Guan, P. W. Wheeler, Q. Guan and P. Yang, Common-Mode Voltage Reduction for Matrix Converters Using All Valid Switch States, in IEEE Transactions on Power Electronics, vol. 31, no. 12, pp. 8247-8259, Dec. 2016. [11] Y. Wang, W. W. Shi, N. Xie and C. M. Wang, Diode- Free T-Type Three-Level Neutral-Point-Clamped Inverter for Low-Voltage Renewable Energy System, in IEEE Transactions on Industrial Electronics, vol. 61, no. 11, pp. 6168-6174, Nov. 2014. [12] Hee-Jung Kim, Hyeoun-Dong Lee and Seung-Ki Sul, A new PWM strategy for common-mode voltage reduction in neutral-point-clamped inverter-fed AC motor drives, in IEEE Transactions on Industry Applications, vol. 37, no. 6, pp. 1840-1845, Nov/Dec 2001.

File đính kèm:

phuong_phap_dieu_che_do_rong_xung_cua_bien_tan_ma_tran_da_ba.pdf

phuong_phap_dieu_che_do_rong_xung_cua_bien_tan_ma_tran_da_ba.pdf