Phân tích, đánh giá hiệu quả các phương pháp mặt nạ chống tấn công DPA cho AES trên Smart Card

Tấn công phân tích năng lượng vi sai

(Difference Power Analysis attack - DPA

attack) là loại tấn công khai thác năng lượng của

thiết bị mật mã dựa vào kết quả sai khác giữa dữ

liệu giả định và giá trị năng lượng thực tế đo

được để tìm khóa bí mật [1], [7]. Với ưu điểm

hiệu quả cao, không xâm lấn, giá thành rẻ, tấn

công DPA là nguy cơ tiềm tàng ảnh hưởng đến

sự an toàn của các thiết bị mật mã [1], [2], [9].

Khi tìm được khóa mật, kẻ tấn công có thể truy

cập trái phép, giải mã, tạo chữ ký giả, giả mạo

thông báo, nhân bản thiết bị

Để chống tấn công DPA thì phải làm cho

năng lượng tiêu thụ của thiết bị độc lập với giá trị

trung gian thực của thiết bị. Kỹ thuật mặt nạ thực

hiện che các giá trị trung gian của thuật toán bằng

các giá trị ngẫu nhiên là giải pháp hiệu quả chống

được tấn công DPA [3], [4]. Theo cách che giá

trị trung gian, có thể chia kỹ thuật mặt nạ thành 4

loại: mặt nạ cố định, mặt nạ đầy đủ, mặt nạ nhân,

mặt nạ biến đổi số học [14]. Bài báo phân tích,

đánh giá phương pháp mặt nạ (Phần II), đề xuất

thuật toán AES chống tấn công DPA dựa trên kỹ

thuật mặt nạ nhúng (Phần III), xây dựng thực

nghiệm đánh giá các phương pháp chống tấn

công DPA lên AES trên Smart Card (Phần IV).

Trang 1

Trang 2

Trang 3

Trang 4

Trang 5

Trang 6

Trang 7

Tóm tắt nội dung tài liệu: Phân tích, đánh giá hiệu quả các phương pháp mặt nạ chống tấn công DPA cho AES trên Smart Card

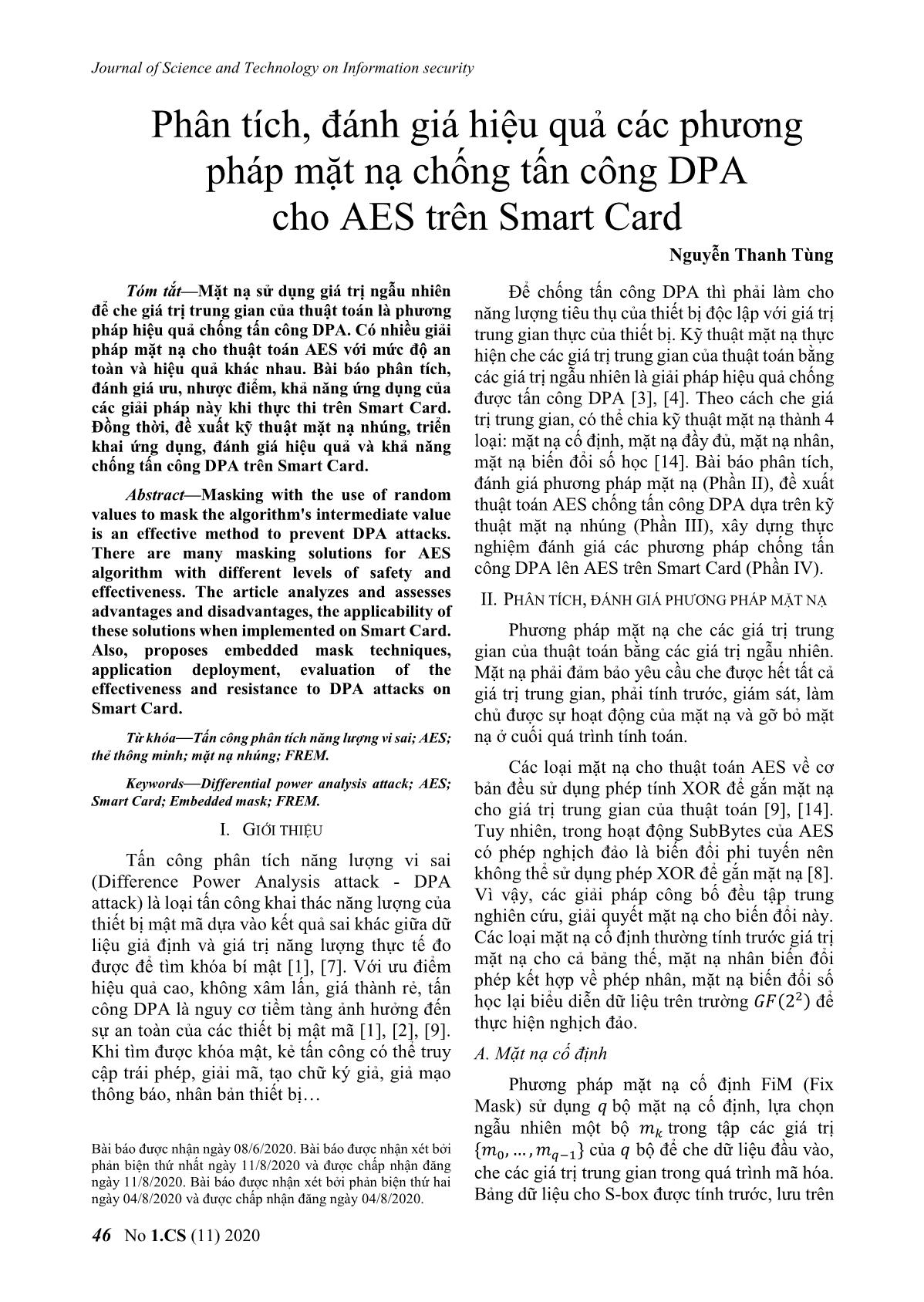

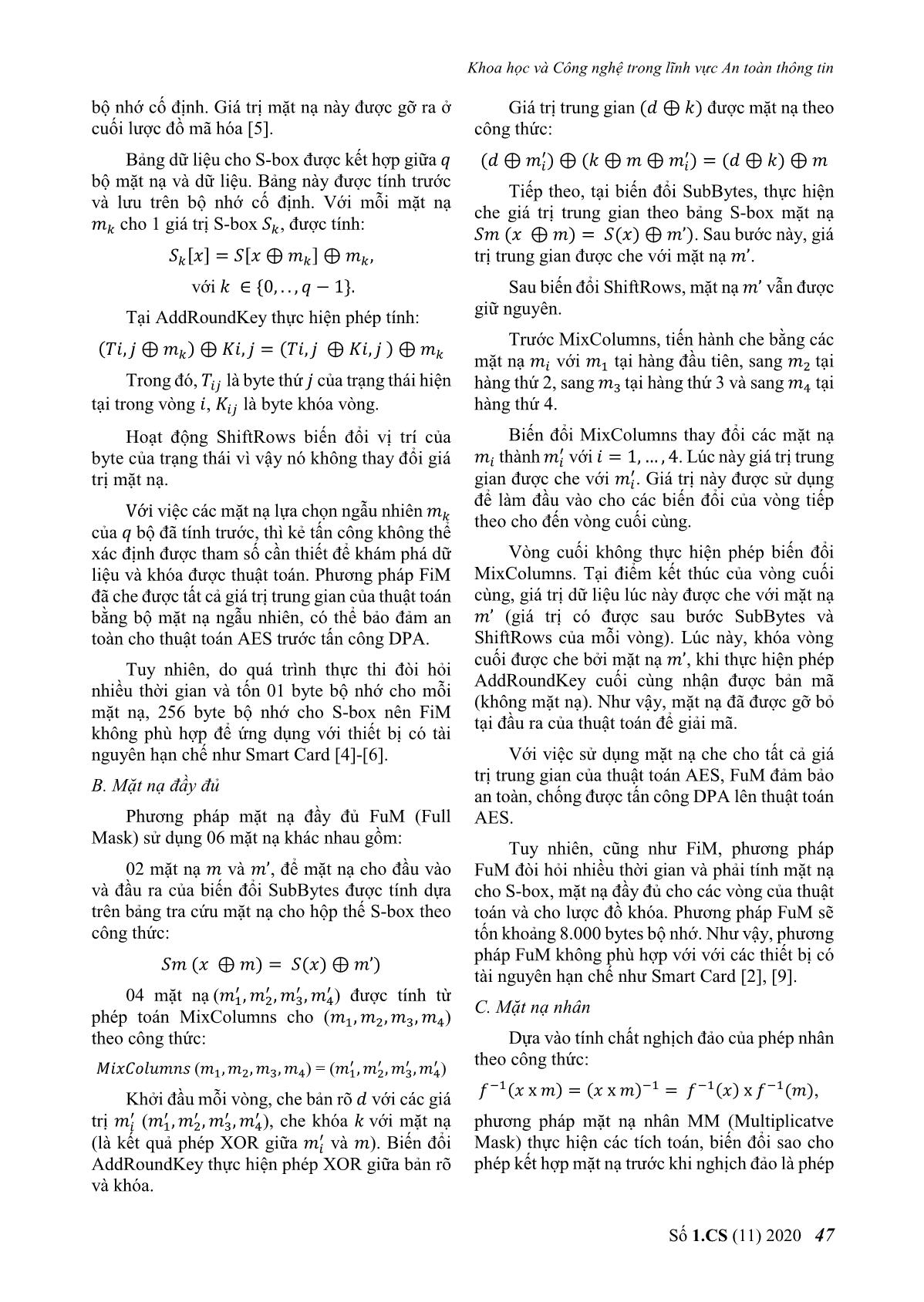

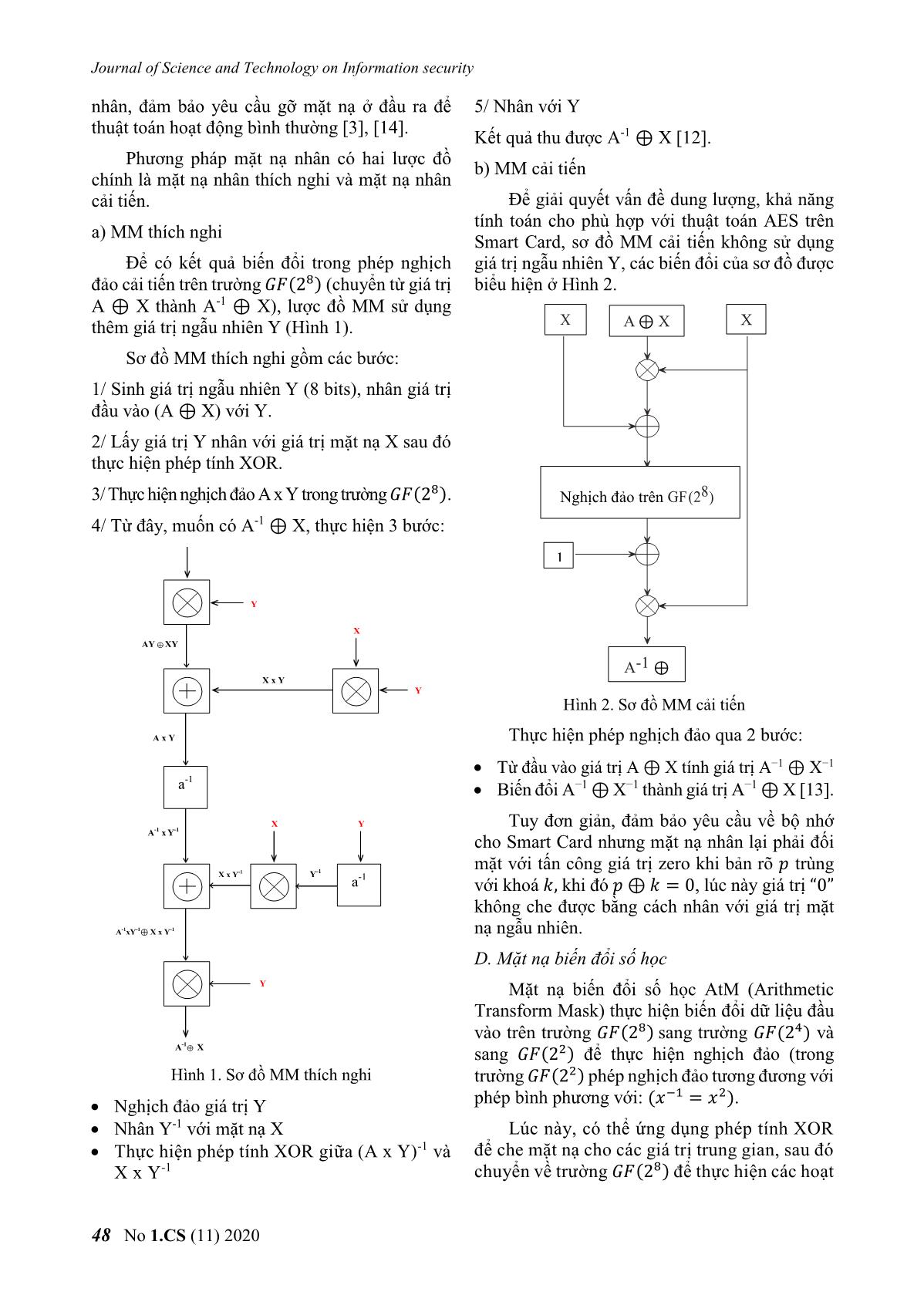

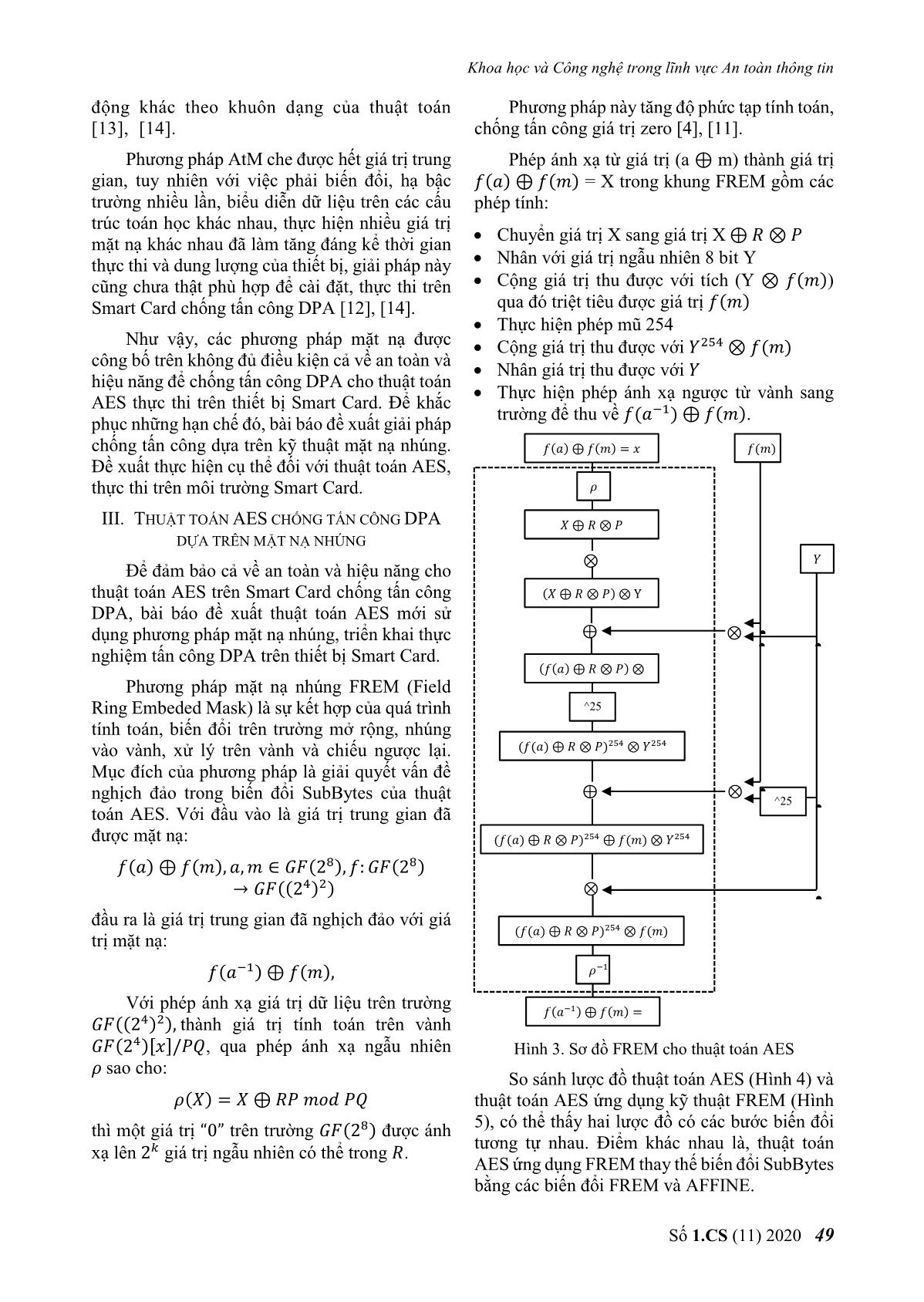

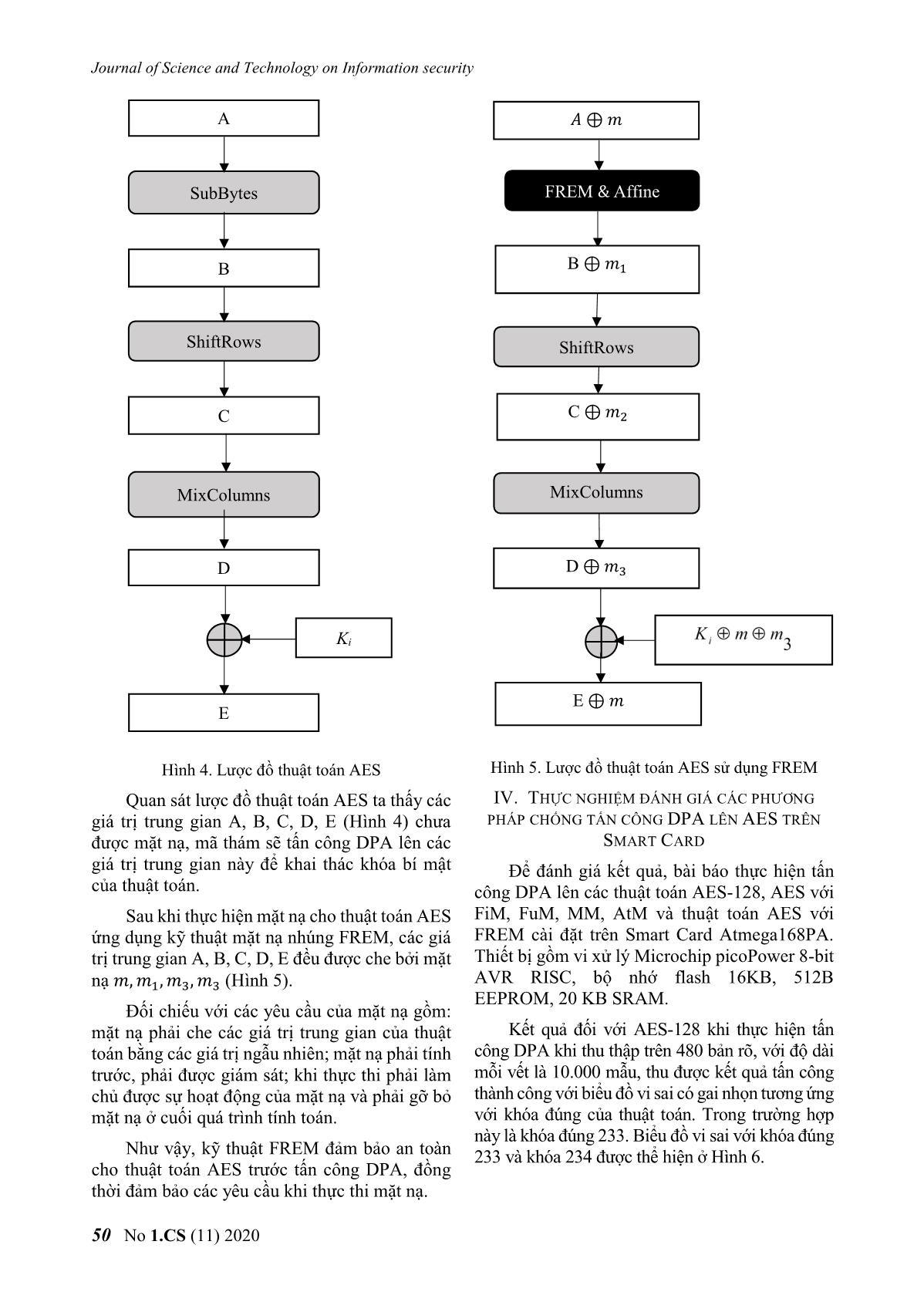

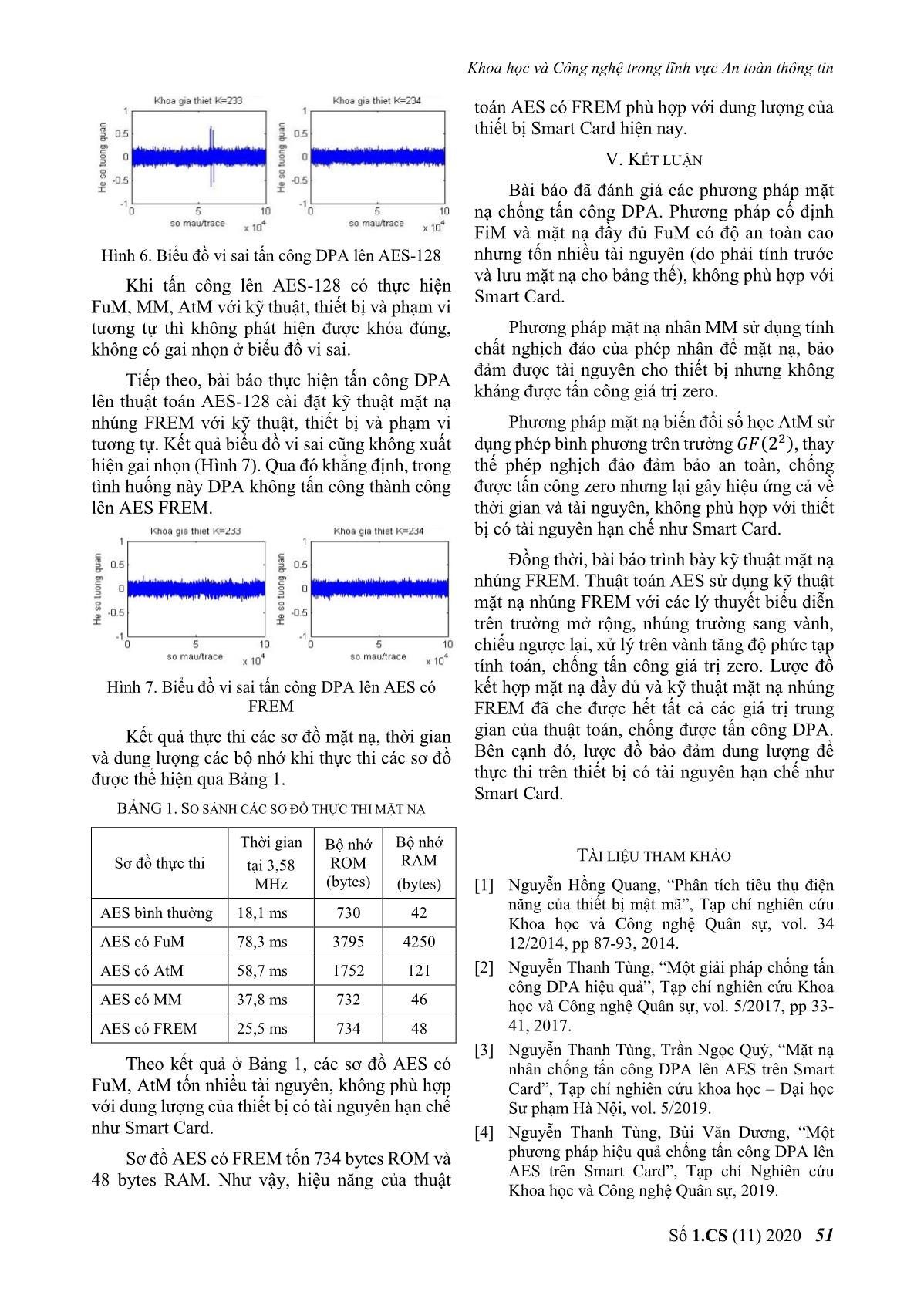

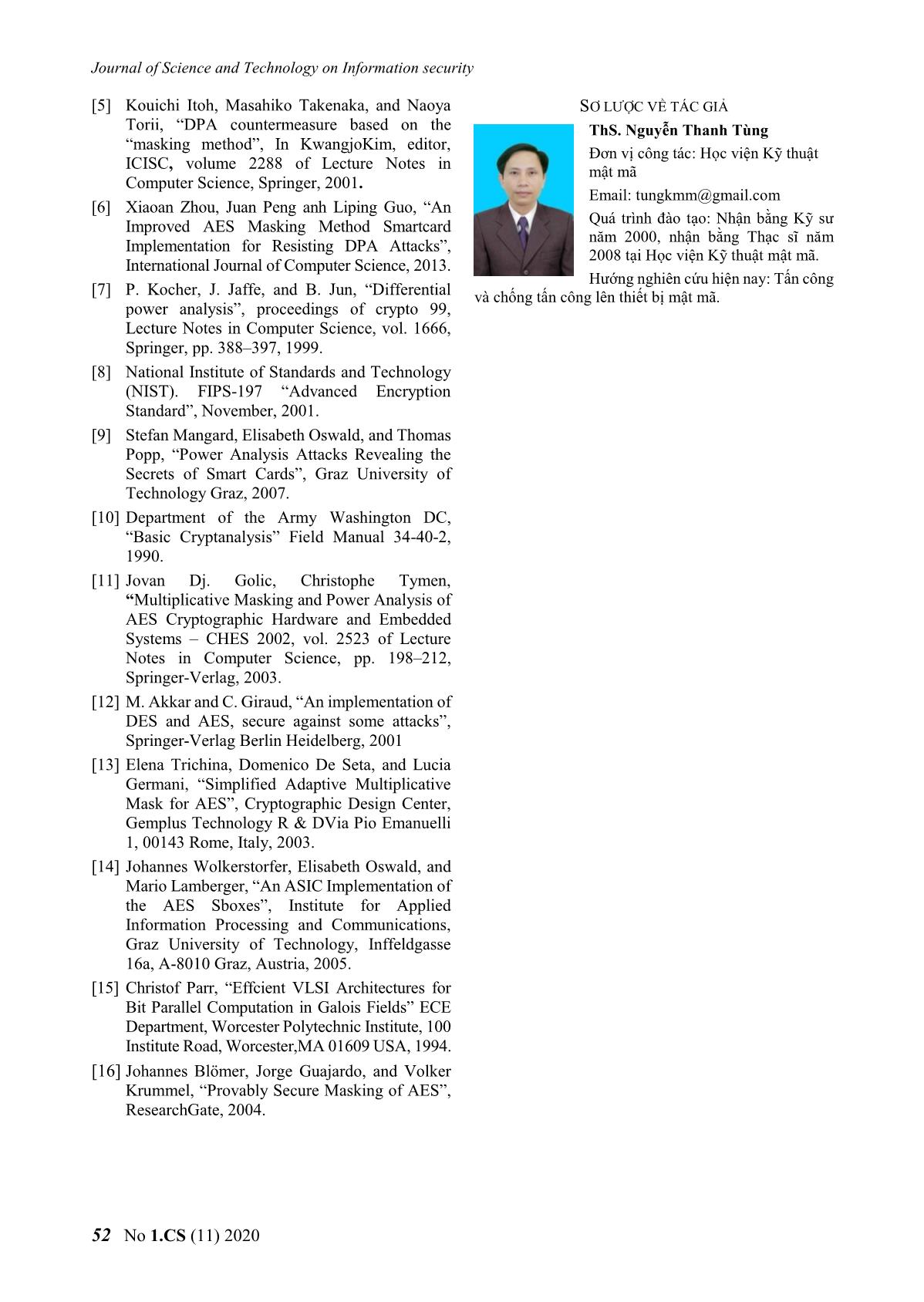

t toán. Phương pháp FiM MixColumns. Tại điểm kết thúc của vòng cuối đã che được tất cả giá trị trung gian của thuật toán cùng, giá trị dữ liệu lúc này được che với mặt nạ bằng bộ mặt nạ ngẫu nhiên, có thể bảo đảm an ’ (giá trị có được sau bước SubBytes và toàn cho thuật toán AES trước tấn công DPA. ShiftRows của mỗi vòng). Lúc này, khóa vòng cuối được che bởi mặt nạ ’, khi thực hiện phép Tuy nhiên, do quá trình thực thi đòi hỏi AddRoundKey cuối cùng nhận được bản mã nhiều thời gian và tốn 01 byte bộ nhớ cho mỗi (không mặt nạ). Như vậy, mặt nạ đã được gỡ bỏ mặt nạ, 256 byte bộ nhớ cho S-box nên FiM tại đầu ra của thuật toán để giải mã. không phù hợp để ứng dụng với thiết bị có tài nguyên hạn chế như Smart Card [4]-[6]. Với việc sử dụng mặt nạ che cho tất cả giá trị trung gian của thuật toán AES, FuM đảm bảo B. Mặt nạ đầy đủ an toàn, chống được tấn công DPA lên thuật toán Phương pháp mặt nạ đầy đủ FuM (Full AES. Mask) sử dụng 06 mặt nạ khác nhau gồm: Tuy nhiên, cũng như FiM, phương pháp 02 mặt nạ và ’, để mặt nạ cho đầu vào FuM đòi hỏi nhiều thời gian và phải tính mặt nạ và đầu ra của biến đổi SubBytes được tính dựa cho S-box, mặt nạ đầy đủ cho các vòng của thuật trên bảng tra cứu mặt nạ cho hộp thế S-box theo toán và cho lược đồ khóa. Phương pháp FuM sẽ công thức: tốn khoảng 8.000 bytes bộ nhớ. Như vậy, phương pháp FuM không phù hợp với với các thiết bị có 푆 ( ⊕ ) = 푆( ) ⊕ ’) tài nguyên hạn chế như Smart Card [2], [9]. 04 mặt nạ ( ′ , ′ , ′ , ′ ) được tính từ 1 2 3 4 C. Mặt nạ nhân phép toán MixColumns cho ( 1, 2, 3, 4) theo công thức: Dựa vào tính chất nghịch đảo của phép nhân ′ ′ ′ ′ theo công thức: 푖 표푙 푛푠 ( 1, 2, 3, 4) = ( 1, 2, 3, 4) −1( ) ( )−1 −1( ) −1 Khởi đầu mỗi vòng, che bản rõ với các giá x = x = x ( ), ′ ′ ′ ′ ′ trị 푖 ( 1, 2, 3, 4), che khóa với mặt nạ phương pháp mặt nạ nhân MM (Multiplicatve ′ (là kết quả phép XOR giữa 푖 và ). Biến đổi Mask) thực hiện các tích toán, biến đổi sao cho AddRoundKey thực hiện phép XOR giữa bản rõ phép kết hợp mặt nạ trước khi nghịch đảo là phép và khóa. Số 1.CS (11) 2020 47 Journal of Science and Technology on Information security nhân, đảm bảo yêu cầu gỡ mặt nạ ở đầu ra để 5/ Nhân với Y thuật toán hoạt động bình thường [3], [14]. Kết quả thu được A-1 ⊕ X [12]. Phương pháp mặt nạ nhân có hai lược đồ b) MM cải tiến chính là mặt nạ nhân thích nghi và mặt nạ nhân cải tiến. Để giải quyết vấn đề dung lượng, khả năng tính toán cho phù hợp với thuật toán AES trên a) MM thích nghi Smart Card, sơ đồ MM cải tiến không sử dụng Để có kết quả biến đổi trong phép nghịch giá trị ngẫu nhiên Y, các biến đổi của sơ đồ được đảo cải tiến trên trường 퐹(28) (chuyển từ giá trị biểu hiện ở Hình 2. A ⊕ X thành A-1 ⊕ X), lược đồ MM sử dụng thêm giá trị ngẫu nhiên Y (Hình 1). A ⊕ X X Sơ đồ MM thích nghi gồm các bước: 1/ Sinh giá trị ngẫu nhiên Y (8 bits), nhân giá trị đầu vào (A ⊕ X) với Y. 2/ Lấy giá trị Y nhân với giá trị mặt nạ X sau đó thực hiện phép tính XOR. 3/ Thực hiện nghịch đảo A x Y trong trường 퐹(28). Nghịch đảo trên 4/ Từ đây, muốn có A-1 ⊕ X, thực hiện 3 bước: 1 Y X AY ⊕ XY A-1 ⊕ X x Y Y X Hình 2. Sơ đồ MM cải tiến A x Y Thực hiện phép nghịch đảo qua 2 bước: Từ đầu vào giá trị A ⊕ X tính giá trị A−1 ⊕ X−1 -1 a Biến đổi A−1 ⊕ X−1 thành giá trị A−1 ⊕ X [13]. X Y Tuy đơn giản, đảm bảo yêu cầu về bộ nhớ A-1 x Y-1 cho Smart Card nhưng mặt nạ nhân lại phải đối mặt với tấn công giá trị zero khi bản rõ trùng X x Y-1 Y-1 a-1 với khoá , khi đó ⊕ = 0, lúc này giá trị “0” không che được bằng cách nhân với giá trị mặt A-1xY-1⊕ X x Y-1 nạ ngẫu nhiên. D. Mặt nạ biến đổi số học Y Mặt nạ biến đổi số học AtM (Arithmetic Transform Mask) thực hiện biến đổi dữ liệu đầu vào trên trường 퐹(28) sang trường 퐹(24) và -1 A ⊕ X sang 퐹(22) để thực hiện nghịch đảo (trong Hình 1. Sơ đồ MM thích nghi trường 퐹(22) phép nghịch đảo tương đương với −1 2 Nghịch đảo giá trị Y phép bình phương với: ( = ). Nhân Y-1 với mặt nạ X Lúc này, có thể ứng dụng phép tính XOR Thực hiện phép tính XOR giữa (A x Y)-1 và để che mặt nạ cho các giá trị trung gian, sau đó X x Y-1 chuyển về trường 퐹(28) để thực hiện các hoạt 48 No 1.CS (11) 2020 Khoa học và Công nghệ trong lĩnh vực An toàn thông tin động khác theo khuôn dạng của thuật toán Phương pháp này tăng độ phức tạp tính toán, [13], [14]. chống tấn công giá trị zero [4], [11]. Phương pháp AtM che được hết giá trị trung Phép ánh xạ từ giá trị (a ⊕ m) thành giá trị gian, tuy nhiên với việc phải biến đổi, hạ bậc ( ) ⊕ ( ) = X trong khung FREM gồm các trường nhiều lần, biểu diễn dữ liệu trên các cấu phép tính: trúc toán học khác nhau, thực hiện nhiều giá trị Chuyển giá trị X sang giá trị X ⊕ 푅 ⊗ 푃 mặt nạ khác nhau đã làm tăng đáng kể thời gian thực thi và dung lượng của thiết bị, giải pháp này Nhân với giá trị ngẫu nhiên 8 bit Y cũng chưa thật phù hợp để cài đặt, thực thi trên Cộng giá trị thu được với tích (Y ⊗ ( )) Smart Card chống tấn công DPA [12], [14]. qua đó triệt tiêu được giá trị ( ) Thực hiện phép mũ 254 Như vậy, các phương pháp mặt nạ được Cộng giá trị thu được với 푌254 ⊗ ( ) công bố trên không đủ điều kiện cả về an toàn và Nhân giá trị thu được với 푌 hiệu năng để chống tấn công DPA cho thuật toán Thực hiện phép ánh xạ ngược từ vành sang AES thực thi trên thiết bị Smart Card. Để khắc trường để thu về ( −1) ⊕ ( ). phục những hạn chế đó, bài báo đề xuất giải pháp chống tấn công dựa trên kỹ thuật mặt nạ nhúng. ( ) ⊕ ( ) = ( ) Đề xuất thực hiện cụ thể đối với thuật toán AES, thực thi trên môi trường Smart Card. 휌 III. THUẬT TOÁN AES CHỐNG TẤN CÔNG DPA ⊕ 푅 ⊗ 푃 DỰA TRÊN MẶT NẠ NHÚNG ⊗ 푌 Để đảm bảo cả về an toàn và hiệu năng cho thuật toán AES trên Smart Card chống tấn công ( ⊕ 푅 ⊗ 푃) ⊗ Y DPA, bài báo đề xuất thuật toán AES mới sử dụng phương pháp mặt nạ nhúng, triển khai thực ⊕ ⊗ . nghiệm tấn công DPA trên thiết bị Smart Card. . . ( ( ) ⊕ 푅 ⊗ 푃) ⊗ Phương pháp mặt nạ nhúng FREM (Field Y Ring Embeded Mask) là sự kết hợp của quá trình ^25 tính toán, biến đổi trên trường mở rộng, nhúng 4 vào vành, xử lý trên vành và chiếu ngược lại. ( ( ) ⊕ 푅 ⊗ 푃)254 ⊗ 푌254 Mục đích của phương pháp là giải quyết vấn đề nghịch đảo trong biến đổi SubBytes của thuật ⊕ ⊗ . ^25 toán AES. Với đầu vào là giá trị trung gian đã 4 . được mặt nạ: ( ( ) ⊕ 푅 ⊗ 푃)254 ⊕ ( ) ⊗ 푌254 ( ) ⊕ ( ), , ∈ 퐹(28), : 퐹(28) → 퐹((24)2) ⊗ . đầu ra là giá trị trung gian đã nghịch đảo với giá ( ( ) ⊕ 푅 ⊗ 푃)254 ⊗ ( ) trị mặt nạ: ( −1) ⊕ ( ), 휌−1 Với phép ánh xạ giá trị dữ liệu trên trường ( −1) ⊕ ( ) = 4 2 퐹((2 ) ), thành giá trị tính toán trên vành 퐹(24)[ ]/푃푄, qua phép ánh xạ ngẫu nhiên Hình 3. Sơ đồ FREM cho thuật toán AES 휌 sao cho: So sánh lược đồ thuật toán AES (Hình 4) và 휌( ) = ⊕ 푅푃 표 푃푄 thuật toán AES ứng dụng kỹ thuật FREM (Hình thì một giá trị “0” trên trường 퐹(28) được ánh 5), có thể thấy hai lược đồ có các bước biến đổi tương tự nhau. Điểm khác nhau là, thuật toán xạ lên 2 giá trị ngẫu nhiên có thể trong 푅. AES ứng dụng FREM thay thế biến đổi SubBytes bằng các biến đổi FREM và AFFINE. Số 1.CS (11) 2020 49 Journal of Science and Technology on Information security A ⊕ SubBytes FREM & Affine B B ⊕ 1 ShiftRows ShiftRows C C ⊕ 2 MixColumns MixColumns D D ⊕ 3 Ki E ⊕ E Hình 4. Lược đồ thuật toán AES Hình 5. Lược đồ thuật toán AES sử dụng FREM Quan sát lược đồ thuật toán AES ta thấy các IV. THỰC NGHIỆM ĐÁNH GIÁ CÁC PHƯƠNG giá trị trung gian A, B, C, D, E (Hình 4) chưa PHÁP CHỐNG TẤN CÔNG DPA LÊN AES TRÊN được mặt nạ, mã thám sẽ tấn công DPA lên các SMART CARD giá trị trung gian này để khai thác khóa bí mật Để đánh giá kết quả, bài báo thực hiện tấn của thuật toán. công DPA lên các thuật toán AES-128, AES với Sau khi thực hiện mặt nạ cho thuật toán AES FiM, FuM, MM, AtM và thuật toán AES với ứng dụng kỹ thuật mặt nạ nhúng FREM, các giá FREM cài đặt trên Smart Card Atmega168PA. trị trung gian A, B, C, D, E đều được che bởi mặt Thiết bị gồm vi xử lý Microchip picoPower 8-bit nạ , 1, 3, 3 (Hình 5). AVR RISC, bộ nhớ flash 16KB, 512B EEPROM, 20 KB SRAM. Đối chiếu với các yêu cầu của mặt nạ gồm: mặt nạ phải che các giá trị trung gian của thuật Kết quả đối với AES-128 khi thực hiện tấn toán bằng các giá trị ngẫu nhiên; mặt nạ phải tính công DPA khi thu thập trên 480 bản rõ, với độ dài trước, phải được giám sát; khi thực thi phải làm mỗi vết là 10.000 mẫu, thu được kết quả tấn công chủ được sự hoạt động của mặt nạ và phải gỡ bỏ thành công với biểu đồ vi sai có gai nhọn tương ứng mặt nạ ở cuối quá trình tính toán. với khóa đúng của thuật toán. Trong trường hợp này là khóa đúng 233. Biểu đồ vi sai với khóa đúng Như vậy, kỹ thuật FREM đảm bảo an toàn 233 và khóa 234 được thể hiện ở Hình 6. cho thuật toán AES trước tấn công DPA, đồng thời đảm bảo các yêu cầu khi thực thi mặt nạ. 50 No 1.CS (11) 2020 Khoa học và Công nghệ trong lĩnh vực An toàn thông tin toán AES có FREM phù hợp với dung lượng của thiết bị Smart Card hiện nay. V. KẾT LUẬN Bài báo đã đánh giá các phương pháp mặt nạ chống tấn công DPA. Phương pháp cố định FiM và mặt nạ đầy đủ FuM có độ an toàn cao Hình 6. Biểu đồ vi sai tấn công DPA lên AES-128 nhưng tốn nhiều tài nguyên (do phải tính trước và lưu mặt nạ cho bảng thế), không phù hợp với Khi tấn công lên AES-128 có thực hiện Smart Card. FuM, MM, AtM với kỹ thuật, thiết bị và phạm vi tương tự thì không phát hiện được khóa đúng, Phương pháp mặt nạ nhân MM sử dụng tính không có gai nhọn ở biểu đồ vi sai. chất nghịch đảo của phép nhân để mặt nạ, bảo đảm được tài nguyên cho thiết bị nhưng không Tiếp theo, bài báo thực hiện tấn công DPA kháng được tấn công giá trị zero. lên thuật toán AES-128 cài đặt kỹ thuật mặt nạ nhúng FREM với kỹ thuật, thiết bị và phạm vi Phương pháp mặt nạ biến đổi số học AtM sử tương tự. Kết quả biểu đồ vi sai cũng không xuất dụng phép bình phương trên trường 퐹(22), thay hiện gai nhọn (Hình 7). Qua đó khẳng định, trong thế phép nghịch đảo đảm bảo an toàn, chống tình huống này DPA không tấn công thành công được tấn công zero nhưng lại gây hiệu ứng cả về lên AES FREM. thời gian và tài nguyên, không phù hợp với thiết bị có tài nguyên hạn chế như Smart Card. Đồng thời, bài báo trình bày kỹ thuật mặt nạ nhúng FREM. Thuật toán AES sử dụng kỹ thuật mặt nạ nhúng FREM với các lý thuyết biểu diễn trên trường mở rộng, nhúng trường sang vành, chiếu ngược lại, xử lý trên vành tăng độ phức tạp tính toán, chống tấn công giá trị zero. Lược đồ Hình 7. Biểu đồ vi sai tấn công DPA lên AES có kết hợp mặt nạ đầy đủ và kỹ thuật mặt nạ nhúng FREM FREM đã che được hết tất cả các giá trị trung Kết quả thực thi các sơ đồ mặt nạ, thời gian gian của thuật toán, chống được tấn công DPA. và dung lượng các bộ nhớ khi thực thi các sơ đồ Bên cạnh đó, lược đồ bảo đảm dung lượng để được thể hiện qua Bảng 1. thực thi trên thiết bị có tài nguyên hạn chế như Smart Card. BẢNG 1. SO SÁNH CÁC SƠ ĐỒ THỰC THI MẶT NẠ Thời gian Bộ nhớ Bộ nhớ TÀI LIỆU THAM KHẢO Sơ đồ thực thi tại 3,58 ROM RAM MHz (bytes) (bytes) [1] Nguyễn Hồng Quang, “Phân tích tiêu thụ điện năng của thiết bị mật mã”, Tạp chí nghiên cứu AES bình thường 18,1 ms 730 42 Khoa học và Công nghệ Quân sự, vol. 34 AES có FuM 78,3 ms 3795 4250 12/2014, pp 87-93, 2014. AES có AtM 58,7 ms 1752 121 [2] Nguyễn Thanh Tùng, “Một giải pháp chống tấn công DPA hiệu quả”, Tạp chí nghiên cứu Khoa AES có MM 37,8 ms 732 46 học và Công nghệ Quân sự, vol. 5/2017, pp 33- AES có FREM 25,5 ms 734 48 41, 2017. [3] Nguyễn Thanh Tùng, Trần Ngọc Quý, “Mặt nạ Theo kết quả ở Bảng 1, các sơ đồ AES có nhân chống tấn công DPA lên AES trên Smart FuM, AtM tốn nhiều tài nguyên, không phù hợp Card”, Tạp chí nghiên cứu khoa học – Đại học với dung lượng của thiết bị có tài nguyên hạn chế Sư phạm Hà Nội, vol. 5/2019. như Smart Card. [4] Nguyễn Thanh Tùng, Bùi Văn Dương, “Một Sơ đồ AES có FREM tốn 734 bytes ROM và phương pháp hiệu quả chống tấn công DPA lên 48 bytes RAM. Như vậy, hiệu năng của thuật AES trên Smart Card”, Tạp chí Nghiên cứu Khoa học và Công nghệ Quân sự, 2019. Số 1.CS (11) 2020 51 Journal of Science and Technology on Information security [5] Kouichi Itoh, Masahiko Takenaka, and Naoya SƠ LƯỢC VỀ TÁC GIẢ Torii, “DPA countermeasure based on the ThS. Nguyễn Thanh Tùng “masking method”, In KwangjoKim, editor, Đơn vị công tác: Học viện Kỹ thuật ICISC, volume 2288 of Lecture Notes in mật mã Computer Science, Springer, 2001. Email: tungkmm@gmail.com [6] Xiaoan Zhou, Juan Peng anh Liping Guo, “An Improved AES Masking Method Smartcard Quá trình đào tạo: Nhận bằng Kỹ sư năm 2000, nhận bằng Thạc sĩ năm Implementation for Resisting DPA Attacks”, 2008 tại Học viện Kỹ thuật mật mã. International Journal of Computer Science, 2013. Hướng nghiên cứu hiện nay: Tấn công [7] P. Kocher, J. Jaffe, and B. Jun, “Differential và chống tấn công lên thiết bị mật mã. power analysis”, proceedings of crypto 99, Lecture Notes in Computer Science, vol. 1666, Springer, pp. 388–397, 1999. [8] National Institute of Standards and Technology (NIST). FIPS-197 “Advanced Encryption Standard”, November, 2001. [9] Stefan Mangard, Elisabeth Oswald, and Thomas Popp, “Power Analysis Attacks Revealing the Secrets of Smart Cards”, Graz University of Technology Graz, 2007. [10] Department of the Army Washington DC, “Basic Cryptanalysis” Field Manual 34-40-2, 1990. [11] Jovan Dj. Golic, Christophe Tymen, “Multiplicative Masking and Power Analysis of AES Cryptographic Hardware and Embedded Systems – CHES 2002, vol. 2523 of Lecture Notes in Computer Science, pp. 198–212, Springer-Verlag, 2003. [12] M. Akkar and C. Giraud, “An implementation of DES and AES, secure against some attacks”, Springer-Verlag Berlin Heidelberg, 2001 [13] Elena Trichina, Domenico De Seta, and Lucia Germani, “Simplified Adaptive Multiplicative Mask for AES”, Cryptographic Design Center, Gemplus Technology R & DVia Pio Emanuelli 1, 00143 Rome, Italy, 2003. [14] Johannes Wolkerstorfer, Elisabeth Oswald, and Mario Lamberger, “An ASIC Implementation of the AES Sboxes”, Institute for Applied Information Processing and Communications, Graz University of Technology, Inffeldgasse 16a, A-8010 Graz, Austria, 2005. [15] Christof Parr, “Effcient VLSI Architectures for Bit Parallel Computation in Galois Fields” ECE Department, Worcester Polytechnic Institute, 100 Institute Road, Worcester,MA 01609 USA, 1994. [16] Johannes Blömer, Jorge Guajardo, and Volker Krummel, “Provably Secure Masking of AES”, ResearchGate, 2004. 52 No 1.CS (11) 2020

File đính kèm:

phan_tich_danh_gia_hieu_qua_cac_phuong_phap_mat_na_chong_tan.pdf

phan_tich_danh_gia_hieu_qua_cac_phuong_phap_mat_na_chong_tan.pdf