Phần mềm VIPEX rút trích và tối ưu hóa tham số linh kiện MOSFET tự động

Rút trích tham số linh kiện MOSFET là khâu

quan trọng trong quá trình thiết kế vi mạch. Việc rút trích

tham số góp phần mô phỏng và thiết kế mạch điện ngày

càng chính xác.Đầy là cầu nối giữa công nghệ sản xuất bán

dẫn và các phần mềm thiết kế mô phỏng mạch điện SPICE.

Phần mềm rút trích tham số VIPEX được phát triển và

thiết kế đầu tiên tại Việt Nam có các chức năng rút trích

tự động tham số linh kiện MOSFET, tối ưu hóa, mô hình

hóa linh kiện dựa trên các mô hình MOS Mức 1-2-3, EKV

2.6, BSIM3v3. Các tham số linh kiện rút trích có thể được

đưa vào bộ mô phỏng mạch điện SPICE. Phần mềm có thể

sử dụng trong đào tạo và nghiên cứu ở lĩnh vực thiết kế vi

mạch.

Trang 1

Trang 2

Trang 3

Trang 4

Trang 5

Bạn đang xem tài liệu "Phần mềm VIPEX rút trích và tối ưu hóa tham số linh kiện MOSFET tự động", để tải tài liệu gốc về máy hãy click vào nút Download ở trên

Tóm tắt nội dung tài liệu: Phần mềm VIPEX rút trích và tối ưu hóa tham số linh kiện MOSFET tự động

Phần mềm VIPEX rút trích và tối ƣu hóa tham

số linh kiện MOSFET tự động

Lê Đức Hùng1*, Võ Thanh Trí2, Nguyễn Trần Sơn3, Nguyễn Đăng Nhật Tâm2, Bùi Trọng Tú1*

1Khoa Điện tử - Viễn thông, Trƣờng Đại Học Khoa Học Tự Nhiên –Đại Học Quốc Gia TP.HCM

2

Phòng Thí Nghiệm DESLAB, Trƣờng Đại Học Khoa Học Tự Nhiên –Đại Học Quốc Gia TP.HCM

3Trƣờng Đại Học Công Nghệ Thông Tin – Đại Học Quốc Gia TP.HCM

*

Email:{ldhung, bttu}@hcmus.edu.vn

Tómtắt—Rút trích tham số linh kiện MOSFET là khâu

quan trọng trong quá trình thiết kế vi mạch. Việc rút trích

tham số góp phần mô phỏng và thiết kế mạch điện ngày

càng chính xác.Đầy là cầu nối giữa công nghệ sản xuất bán

dẫn và các phần mềm thiết kế mô phỏng mạch điện SPICE.

Phần mềm rút trích tham số VIPEX được phát triển và

thiết kế đầu tiên tại Việt Nam có các chức năng rút trích

tự động tham số linh kiện MOSFET, tối ưu hóa, mô hình

hóa linh kiện dựa trên các mô hình MOS Mức 1-2-3, EKV

2.6, BSIM3v3. Các tham số linh kiện rút trích có thể được

đưa vào bộ mô phỏng mạch điện SPICE. Phần mềm có thể

sử dụng trong đào tạo và nghiên cứu ở lĩnh vực thiết kế vi

mạch.

Từ khóa—trích tham số; MOSFET; EKV2.6; BSIM3v3;

MOS Mức 1-2-3; Lavenberg-Marquardt; Genetic Algorithm

I. TỔNG QUAN

Ngày nay công nghệ CMOS (Complementary Metal-

Oxide-Semiconductor) là một công nghệ đƣợc sử dụng

phổ biến trong thiết kế vi mạch. Mà công nghệ CMOS

có nền tảng dựa trên linh kiện MOSFET (Metal-Oxide

Semiconductor Field Effect Transistor). Vì vậy để có

thiết kế tốt và mô phỏng mạch điện chính xác thì ta cần

phải hiểu rõ hoạt động của linh kiện MOSFET và các

ảnh hƣởng vật lý tác động lên nó. Vì vậy các linh kiện

MOSFET đƣợc mô hình hóa để mô tả chi tiết hoạt động

của MOSFET.

Mô hình MOSFET là một tập hợp các công thức toán

học phức tạp mô tả hoạt động của MOSFET. Các mô

hình đơn giản thì số lƣợng công thức còn ít, nhƣng khi

MOSFET đƣợc chế tạo với kích thƣớc ngày càng nhỏ

hơn thì các hiệu ứng phụ bắt đầu phát sinh và chúng ta

cần những mô hình phức tạp hơn để có thể bao quát hết

đƣợc các hiệu ứng vật lý đó. Kết quả là số lƣợng công

thức ở các mô hình mới này cũng bắt đầu nhiều hơn. Khi

đƣa mô hình MOSFET vào chƣơng trình mô phỏng

mạch điện, chúng sẽ dựa vào các công thức của mô hình

để tính ra các kết quả thiết kế mạch điện. Trong các công

thức toán của mô hình chứa rất nhiều các tham số, gọi là

tham số mô hình. Các tham số này chỉ có thể rút trích

đƣợc từ các giá trị đo đạc thực nghiệm I-V và dùng các

phƣơng pháp toán số phức tạp.

II. PHƢƠNG PHÁP TRÍCH THAM SỐ

A. Giới thiệu

Phần mềm với mục đích chính là rút trích và tối ƣu

các tham số của mô hình MOSFET một cách tự động.

Nhƣ đã trình bày ở phần trên, việc trích tham số mô hình

là công việc quan trọng.Trên thế giới cũng đã có nhiều

công cụ phần mềm rút trích tham số điển hình là IC-

CAP của hãng Agilent và UTMOST của hãng Silvaco.

Tuy nhiên, chi phí mua bản quyền là rất đắt.

Trong phần mềm này, nhóm tác giả tập trung vào

việc rút trích và tối ƣu hóa tập tham số của các mô hình

MOSFET điển hình, cụ thể làmô hình MOS Mức 1,

MOS Mức 2, MOS Mức 3; mô hình BSIM3; mô hình

EKV v2.6.

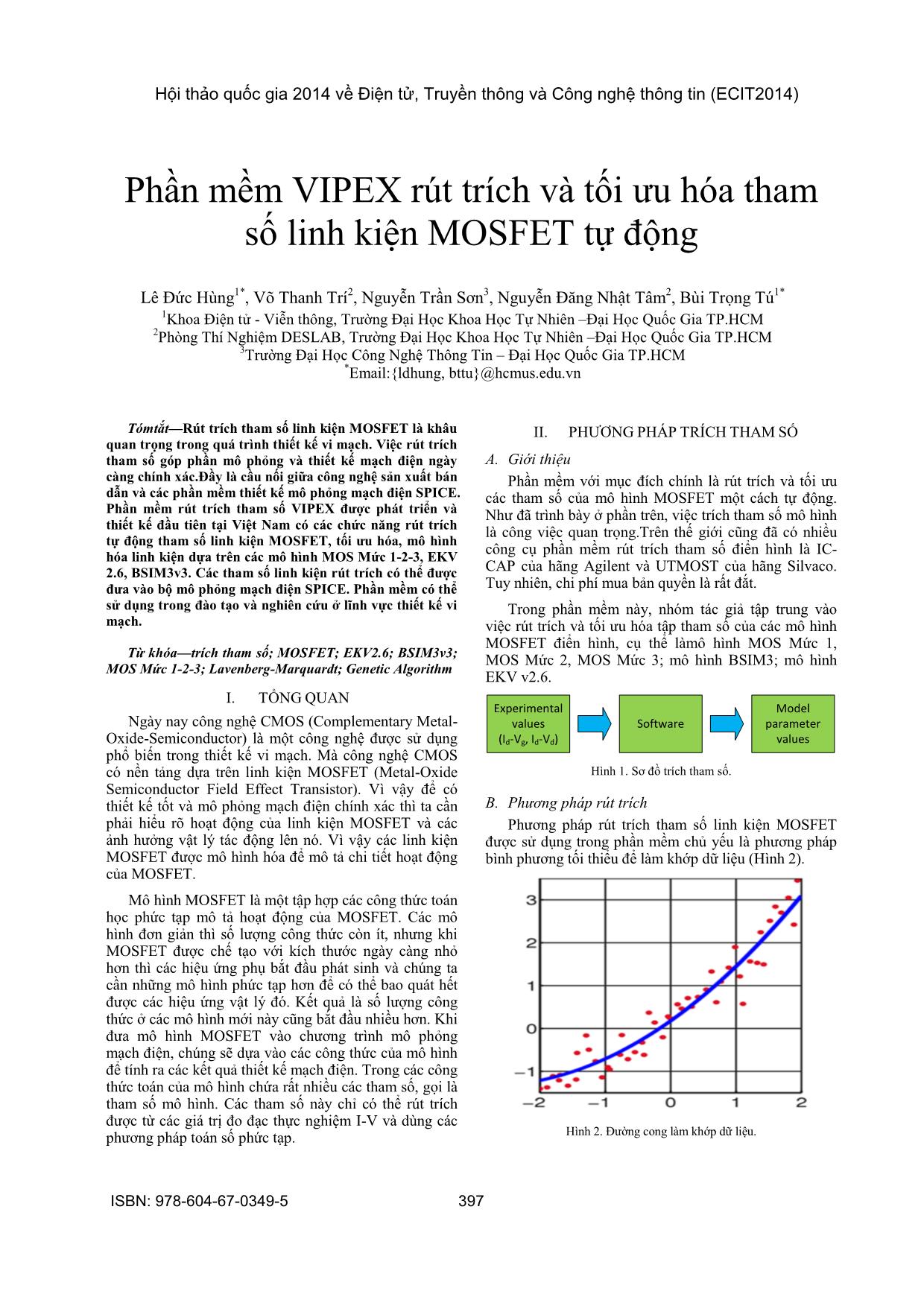

Experimental

values

(Id-Vg, Id-Vd)

Software

Model

parameter

values

Hình 1. Sơ đồ trích tham số.

B. Phương pháp rút trích

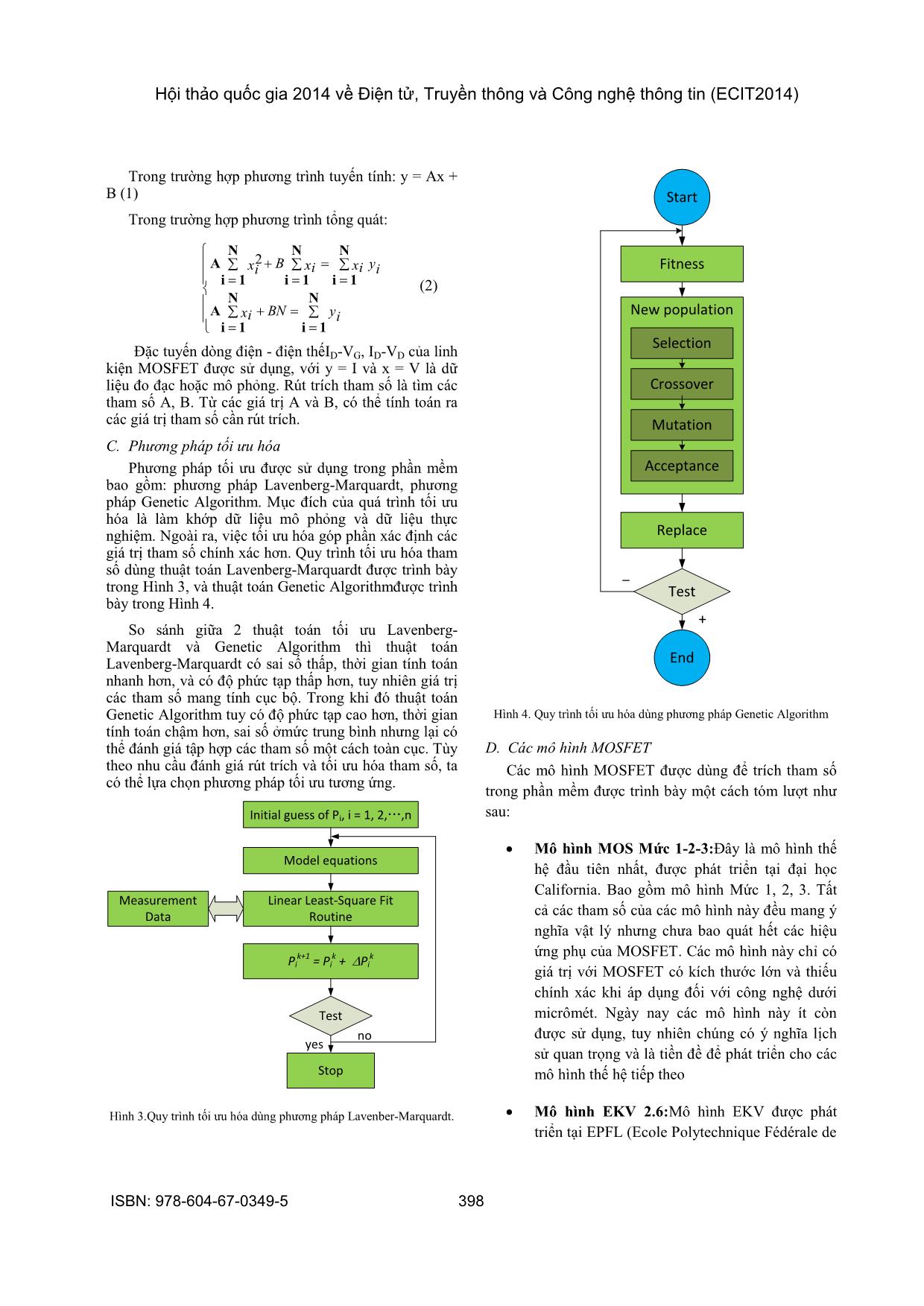

Phƣơng pháp rút trích tham số linh kiện MOSFET

đƣợc sử dụng trong phần mềm chủ yếu là phƣơng pháp

bình phƣơng tối thiểu để làm khớp dữ liệu (Hình 2).

Hình 2. Đƣờng cong làm khớp dữ liệu.

Hội thảo quốc gia 2014 về Điện tử, Truyền thông và Công nghệ thông tin (ECIT2014)

ISBN: 978-604-67-0349-5 397

Trong trƣờng hợp phƣơng trình tuyến tính: y = Ax +

B (1)

Trong trƣờng hợp phƣơng trình tổng quát:

N

1i

N

1i

A

N

1i

N

1i

N

1i

A

yiBNxi

yixixiBxi

2

Đặc tuyến dòng điện - điện thếID-VG, ID-VD của linh

kiện MOSFET đƣợc sử dụng, với y = I và x = V là dữ

liệu đo đạc hoặc mô phỏng. Rút trích tham số là tìm các

tham số A, B. Từ các giá trị A và B, có thể tính toán ra

các giá trị tham số cần rút trích.

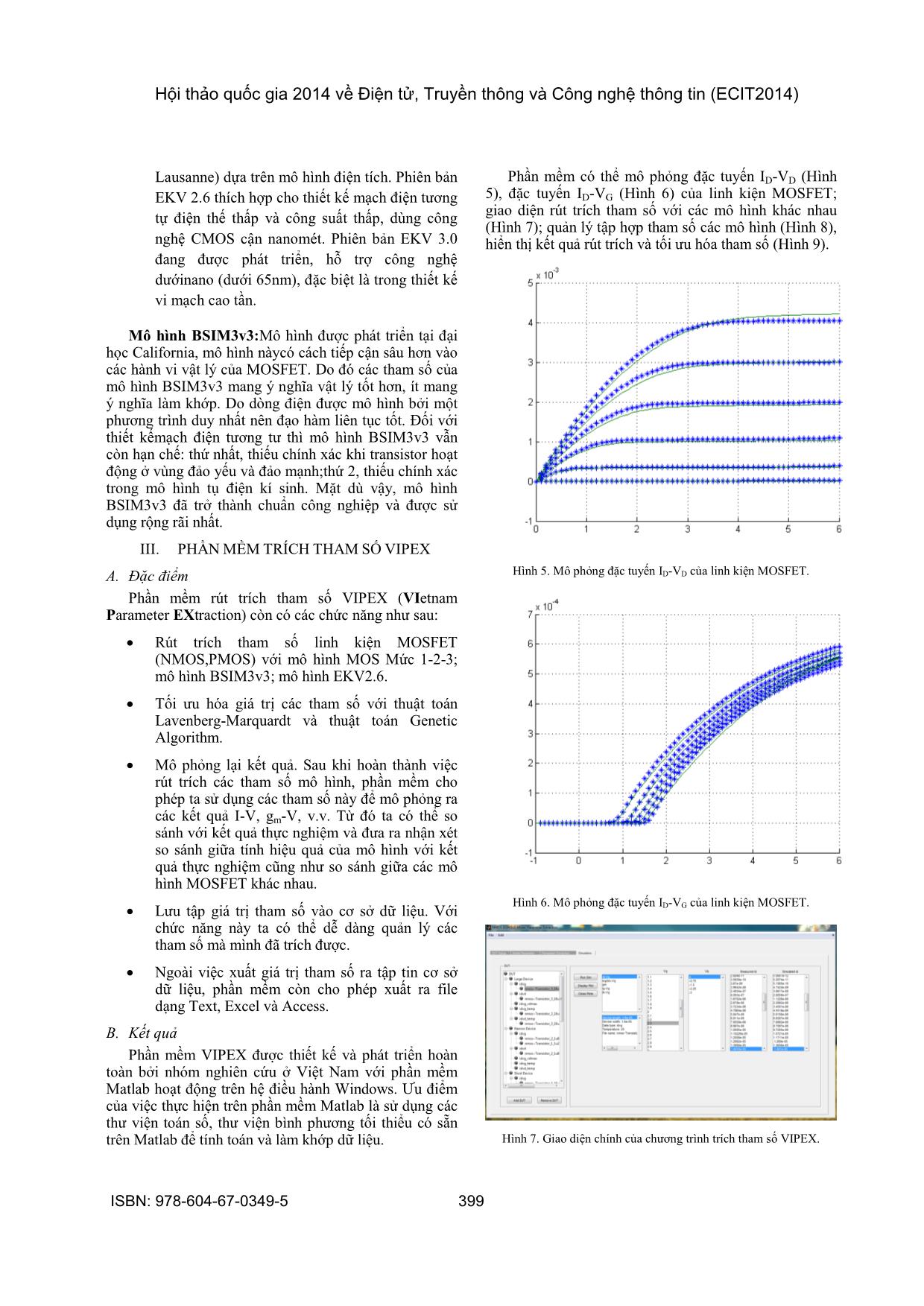

C. Phương pháp tối ưu hóa

Phƣơng pháp tối ƣu đƣợc sử dụng trong phần mềm

bao gồm: phƣơng pháp Lavenberg-Marquardt, phƣơng

pháp Genetic Algorithm. Mục đích của quá trình tối ƣu

hóa là làm khớp dữ liệu mô phỏng và dữ liệu thực

nghiệm. Ngoài ra, việc tối ƣu hóa góp phần xác định các

giá trị tham số chính xác hơn. Quy trình tối ƣu hóa tham

số dùng thuật toán Lavenberg-Marquardt đƣợc trình bày

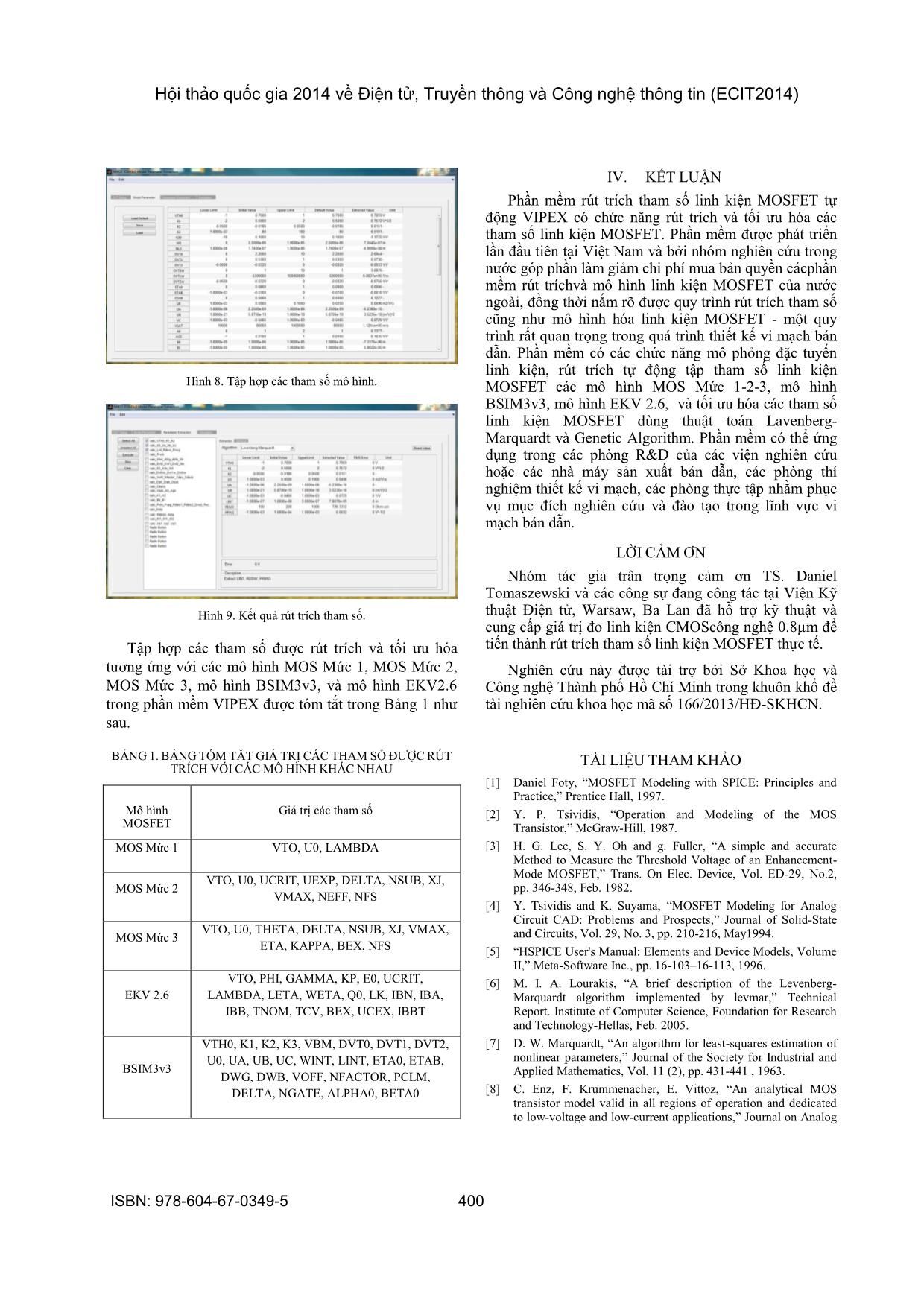

trong Hình 3, và thuật toán Genetic Algorithmđƣợc trình

bày trong Hình 4.

So sánh giữa 2 thuật toán tối ƣu Lavenberg-

Marquardt và Genetic Algorithm thì thuật toán

Lavenberg-Marquardt có sai số thấp, thời gian tính toán

nhanh hơn, và có độ phức tạp thấp hơn, tuy nhiên giá trị

các tham số mang tính cục bộ. Trong khi đó thuật toán

Genetic Algorithm tuy có độ phức tạp cao hơn, thời gian

tính toán chậm hơn, sai số ởmức trung bình nhƣng lại có

thể đánh giá tập hợp các tham số một cách toàn cục. Tùy

theo nhu cầu đánh giá rút trích và tối ƣu hóa tham số, ta

có thể lựa chọn phƣơng pháp tối ƣu tƣơng ứng.

Initial guess of Pi, i = 1, 2,,n

Model equations

Linear Least-Square Fit

Routine

Measurement

Data

Pi

k+1 = Pi

k + DPi

k

Test

Stop

no

yes

Hình 3.Quy trình tối ƣu hóa dùng phƣơng pháp Lavenber-Marquardt.

Fitness

New population

Start

Selection

Crossover

Mutation

Acceptance

Replace

Test

End

–

+

Hình 4. Quy trình tối ƣu hóa dùng phƣơng pháp Genetic Algorithm

D. Các mô hình MOSFET

Các mô hình MOSFET đƣợc dùng để trích tham số

trong phần mềm đƣợc trình bày một cách tóm lƣợt nhƣ

sau:

Mô hình MOS Mức 1-2-3:Đây là mô hình thế

hệ đầu tiên nhất, đƣợc phát triển tại đại học

California. Bao gồm mô hình Mức 1, 2, 3. Tất

cả các tham số của các mô hình này đều mang ý

nghĩa vật lý nhƣng chƣa bao quát hết các hiệu

ứng phụ của MOSFET. Các mô hình này chỉ có

giá trị với MOSFET có kích thƣớc lớn và thiếu

chính xác khi áp dụng đối với công nghệ dƣới

micrômét. Ngày nay các mô hình này ít còn

đƣợc sử dụng, tuy nhiên chúng có ý nghĩa lịch

sử quan trọng và là tiền đề để phát triển cho các

mô hình thế hệ tiếp theo

Mô hình EKV 2.6:Mô hình EKV đƣợc phát

triển tại EPFL (Ecole Polytechnique Fédérale de

(2)

Hội thảo quốc gia 2014 về Điện tử, Truyền thông và Công nghệ thông tin (ECIT2014)

ISBN: 978-604-67-0349-5 398

Lausanne) dựa trên mô hình điện tích. Phiên bản

EKV 2.6 thích hợp cho thiết kế mạch điện tƣơng

tự điện thế thấp và công suất thấp, dùng công

nghệ CMOS cận nanomét. Phiên bản EKV 3.0

đang đƣợc phát triển, hỗ trợ công nghệ

dƣớinano (dƣới 65nm), đặc biệt là trong thiết kế

vi mạch cao tần.

Mô hình BSIM3v3:Mô hình đƣợc phát triển tại đại

học California, mô hình nàycó cách tiếp cận sâu hơn vào

các hành vi vật lý của MOSFET. Do đó các tham số của

mô hình BSIM3v3 mang ý nghĩa vật lý tốt hơn, ít mang

ý nghĩa làm khớp. Do dòng điện đƣợc mô hình bởi một

phƣơng trình duy nhất nên đạo hàm liên tục tốt. Đối với

thiết kếmạch điện tƣơng tƣ thì mô hình BSIM3v3 vẫn

còn hạn chế: thứ nhất, thiếu chính xác khi transistor hoạt

động ở vùng đảo yếu và đảo mạnh;thứ 2, thiếu chính xác

trong mô hình tụ điện kí sinh. Mặt dù vậy, mô hình

BSIM3v3 đã trở thành chuẩn công nghiệp và đƣợc sử

dụng rộng rãi nhất.

III. PHẦN MỀM TRÍCH THAM SỐ VIPEX

A. Đặc điểm

Phần mềm rút trích tham số VIPEX (VIetnam

Parameter EXtraction) còn có các chức năng nhƣ sau:

Rút trích tham số linh kiện MOSFET

(NMOS,PMOS) với mô hình MOS Mức 1-2-3;

mô hình BSIM3v3; mô hình EKV2.6.

Tối ƣu hóa giá trị các tham số với thuật toán

Lavenberg-Marquardt và thuật toán Genetic

Algorithm.

Mô phỏng lại kết quả. Sau khi hoàn thành việc

rút trích các tham số mô hình, phần mềm cho

phép ta sử dụng các tham số này để mô phỏng ra

các kết quả I-V, gm-V, v.v. Từ đó ta có thể so

sánh với kết quả thực nghiệm và đƣa ra nhận xét

so sánh giữa tính hiệu quả của mô hình với kết

quả thực nghiệm cũng nhƣ so sánh giữa các mô

hình MOSFET khác nhau.

Lƣu tập giá trị tham số vào cơ sở dữ liệu. Với

chức năng này ta có thể dễ dàng quản lý các

tham số mà mình đã trích đƣợc.

Ngoài việc xuất giá trị tham số ra tập tin cơ sở

dữ liệu, phần mềm còn cho phép xuất ra file

dạng Text, Excel và Access.

B. Kết quả

Phần mềm VIPEX đƣợc thiết kế và phát triển hoàn

toàn bởi nhóm nghiên cứu ở Việt Nam với phần mềm

Matlab hoạt động trên hệ điều hành Windows. Ƣu điểm

của việc thực hiện trên phần mềm Matlab là sử dụng các

thƣ viện toán số, thƣ viện bình phƣơng tối thiểu có sẵn

trên Matlab để tính toán và làm khớp dữ liệu.

Phần mềm có thể mô phỏng đặc tuyến ID-VD (Hình

5), đặc tuyến ID-VG (Hình 6) của linh kiện MOSFET;

giao diện rút trích tham số với các mô hình khác nhau

(Hình 7); quản lý tập hợp tham số các mô hình (Hình 8),

hiển thị kết quả rút trích và tối ƣu hóa tham số (Hình 9).

Hình 5. Mô phỏng đặc tuyến ID-VD của linh kiện MOSFET.

Hình 6. Mô phỏng đặc tuyến ID-VG của linh kiện MOSFET.

Hình 7. Giao diện chính của chƣơng trình trích tham số VIPEX.

Hội thảo quốc gia 2014 về Điện tử, Truyền thông và Công nghệ thông tin (ECIT2014)

ISBN: 978-604-67-0349-5 399

Hình 8. Tập hợp các tham số mô hình.

Hình 9. Kết quả rút trích tham số.

Tập hợp các tham số đƣợc rút trích và tối ƣu hóa

tƣơng ứng với các mô hình MOS Mức 1, MOS Mức 2,

MOS Mức 3, mô hình BSIM3v3, và mô hình EKV2.6

trong phần mềm VIPEX đƣợc tóm tắt trong Bảng 1 nhƣ

sau.

BẢNG 1. BẢNG TÓM TẮT GIÁ TRỊ CÁC THAM SỐ ĐƢỢC RÚT

TRÍCH VỚI CÁC MÔ HÌNH KHÁC NHAU

Mô hình

MOSFET

Giá trị các tham số

MOS Mức 1 VTO, U0, LAMBDA

MOS Mức 2

VTO, U0, UCRIT, UEXP, DELTA, NSUB, XJ,

VMAX, NEFF, NFS

MOS Mức 3

VTO, U0, THETA, DELTA, NSUB, XJ, VMAX,

ETA, KAPPA, BEX, NFS

EKV 2.6

VTO, PHI, GAMMA, KP, E0, UCRIT,

LAMBDA, LETA, WETA, Q0, LK, IBN, IBA,

IBB, TNOM, TCV, BEX, UCEX, IBBT

BSIM3v3

VTH0, K1, K2, K3, VBM, DVT0, DVT1, DVT2,

U0, UA, UB, UC, WINT, LINT, ETA0, ETAB,

DWG, DWB, VOFF, NFACTOR, PCLM,

DELTA, NGATE, ALPHA0, BETA0

IV. KẾT LUẬN

Phần mềm rút trích tham số linh kiện MOSFET tự

động VIPEX có chức năng rút trích và tối ƣu hóa các

tham số linh kiện MOSFET. Phần mềm đƣợc phát triển

lần đầu tiên tại Việt Nam và bởi nhóm nghiên cứu trong

nƣớc góp phần làm giảm chi phí mua bản quyền cácphần

mềm rút tríchvà mô hình linh kiện MOSFET của nƣớc

ngoài, đồng thời nắm rõ đƣợc quy trình rút trích tham số

cũng nhƣ mô hình hóa linh kiện MOSFET - một quy

trình rất quan trọng trong quá trình thiết kế vi mạch bán

dẫn. Phần mềm có các chức năng mô phỏng đặc tuyến

linh kiện, rút trích tự động tập tham số linh kiện

MOSFET các mô hình MOS Mức 1-2-3, mô hình

BSIM3v3, mô hình EKV 2.6, và tối ƣu hóa các tham số

linh kiện MOSFET dùng thuật toán Lavenberg-

Marquardt và Genetic Algorithm. Phần mềm có thể ứng

dụng trong các phòng R&D của các viện nghiên cứu

hoặc các nhà máy sản xuất bán dẫn, các phòng thí

nghiệm thiết kế vi mạch, các phòng thực tập nhằm phục

vụ mục đích nghiên cứu và đào tạo trong lĩnh vực vi

mạch bán dẫn.

LỜI CẢM ƠN

Nhóm tác giả trân trọng cảm ơn TS. Daniel

Tomaszewski và các công sự đang công tác tại Viện Kỹ

thuật Điện tử, Warsaw, Ba Lan đã hỗ trợ kỹ thuật và

cung cấp giá trị đo linh kiện CMOScông nghệ 0.8µm để

tiến thành rút trích tham số linh kiện MOSFET thực tế.

Nghiên cứu này đƣợc tài trợ bởi Sở Khoa học và

Công nghệ Thành phố Hồ Chí Minh trong khuôn khổ đề

tài nghiên cứu khoa học mã số 166/2013/HĐ-SKHCN.

TÀI LIỆU THAM KHẢO

[1] Daniel Foty, “MOSFET Modeling with SPICE: Principles and

Practice,” Prentice Hall, 1997.

[2] Y. P. Tsividis, “Operation and Modeling of the MOS

Transistor,” McGraw-Hill, 1987.

[3] H. G. Lee, S. Y. Oh and g. Fuller, “A simple and accurate

Method to Measure the Threshold Voltage of an Enhancement-

Mode MOSFET,” Trans. On Elec. Device, Vol. ED-29, No.2,

pp. 346-348, Feb. 1982.

[4] Y. Tsividis and K. Suyama, “MOSFET Modeling for Analog

Circuit CAD: Problems and Prospects,” Journal of Solid-State

and Circuits, Vol. 29, No. 3, pp. 210-216, May1994.

[5] “HSPICE User's Manual: Elements and Device Models, Volume

II,” Meta-Software Inc., pp. 16-103–16-113, 1996.

[6] M. I. A. Lourakis, “A brief description of the Levenberg-

Marquardt algorithm implemented by levmar,” Technical

Report. Institute of Computer Science, Foundation for Research

and Technology-Hellas, Feb. 2005.

[7] D. W. Marquardt, “An algorithm for least-squares estimation of

nonlinear parameters,” Journal of the Society for Industrial and

Applied Mathematics, Vol. 11 (2), pp. 431-441 , 1963.

[8] C. Enz, F. Krummenacher, E. Vittoz, “An analytical MOS

transistor model valid in all regions of operation and dedicated

to low-voltage and low-current applications,” Journal on Analog

Hội thảo quốc gia 2014 về Điện tử, Truyền thông và Công nghệ thông tin (ECIT2014)

ISBN: 978-604-67-0349-5 400

Integrated Circuits and Signal Processsing, Kluwer Academic

Publishers, pp. 83-114, July 1995.

[9] H.J. Oguey and S. Cserveny, “MOS modelling at low current

density,” Summer Course on Process and Device Modelling,

ESAT Leuven-Heverlee, Belgium, June 1983.

[10] D. Goldberg, “Genetic Algorithms in Search, Optimization, and

Machine Learning,” Addison Wesley, 1989.

[11] M. Mitchell, “An Introduction to Genetic Algorithms,” MIT

Press, 1996.

[12] M. Keser and K. Joardar, “Genetic algorithm based MOSFET

model parameter extraction,” Technical Proceedings of the

International Conference on Modeling and Simulation of

Microsystems, pp. 341-344, 2000.

Hội thảo quốc gia 2014 về Điện tử, Truyền thông và Công nghệ thông tin (ECIT2014)

ISBN: 978-604-67-0349-5 401

File đính kèm:

phan_mem_vipex_rut_trich_va_toi_uu_hoa_tham_so_linh_kien_mos.pdf

phan_mem_vipex_rut_trich_va_toi_uu_hoa_tham_so_linh_kien_mos.pdf