Nghiên cứu hiệu năng kiến trúc chuyển mạch gói quang cho mạng trung tâm dữ liệu

Xu hướng gần đây cho thấy các ứng dụng mạng chuyển

từ các trung tâm dữ liệu đám mây riêng sang các trung tâm

dữ liệu đám mây công cộng. Như được chỉ ra trong chỉ số

đám mây toàn cầu của Cisco năm 2016, số lượng IP đám

mây toàn cầu hàng năm sẽ đạt 14,1ZB vào cuối năm 2020,

tăng từ 8,6ZB vào năm 2018 [1, 2]. Trong các mạng trung

tâm dữ liệu hiện nay, các thiết bị chuyển mạch điện tử chưa

đáp ứng được các nhu cầu về băng thông nhiều hơn, mức

tiêu thụ điện năng thấp và độ trễ nhỏ [3]. Các thiết bị

chuyển mạch kênh quang (OCS) có thể tăng băng thông

đáng kể nhưng không phù hợp với lưu lượng thay đổi. Các

DCN được đề xuất mới nhất sử dụng công nghệ chuyển

mạch gói quang (OPS) có khả năng đạt được thông lượng

cao, mềm dẻo phù hợp với các dịch vụ có tính bùng nổ.

Đặc biệt, giải quyết được hiện tượng thắt nút cổ chai, gia

tăng được thông lượng chuyển mạch. Tuy nhiên trong các

công trình này đã đưa ra các mô hình kiến trúc chuyển

mạch gói quang sử dụng các bộ xử lý mào đầu điện tử, do

đó làm tăng thời gian xử lý gói tại các nút chuyển mạch.

Trong bài báo này, tác giả đề xuất một mô hình kiến

trúc chuyển mạch gói toàn quang sử dụng kỹ thuật xử lý

mào đầu gói quang (OHP) có khả năng làm giảm thời gian

xử lý mào đầu hiệu quả hơn so với kỹ thuật xử lý mào đầu

điện tử, do đó làm giảm đáng kể thời gian trễ truyền các

gói dịch vụ đồng thời làm tăng thông lượng chuyển mạch.

Thông qua mô hình giải tích và mô phỏng đã tiến hành

khảo sát và đưa ra các kết quả liên quan tới các tham số

hiệu năng thời gian trễ hệ thống trung bình và thông lượng

chuyển mạch.

Bài báo được cấu trúc như sau: Phần một là phần giới

thiệu; Tiếp theo kiến trúc chuyển mạch gói quang, phân

tích hiệu năng chuyển mạch gói quang, các kết quả tính

toán số và mô phỏng hiệu năng chuyển mạch gói quang

được khảo sát và thảo luận cũng như kiến trúc chuyển

mạch gói toàn quang đề xuất được trình bày trong phần

thứ hai; Cuối cùng, phần thứ ba là phần kết luận.

Trang 1

Trang 2

Trang 3

Trang 4

Trang 5

Tóm tắt nội dung tài liệu: Nghiên cứu hiệu năng kiến trúc chuyển mạch gói quang cho mạng trung tâm dữ liệu

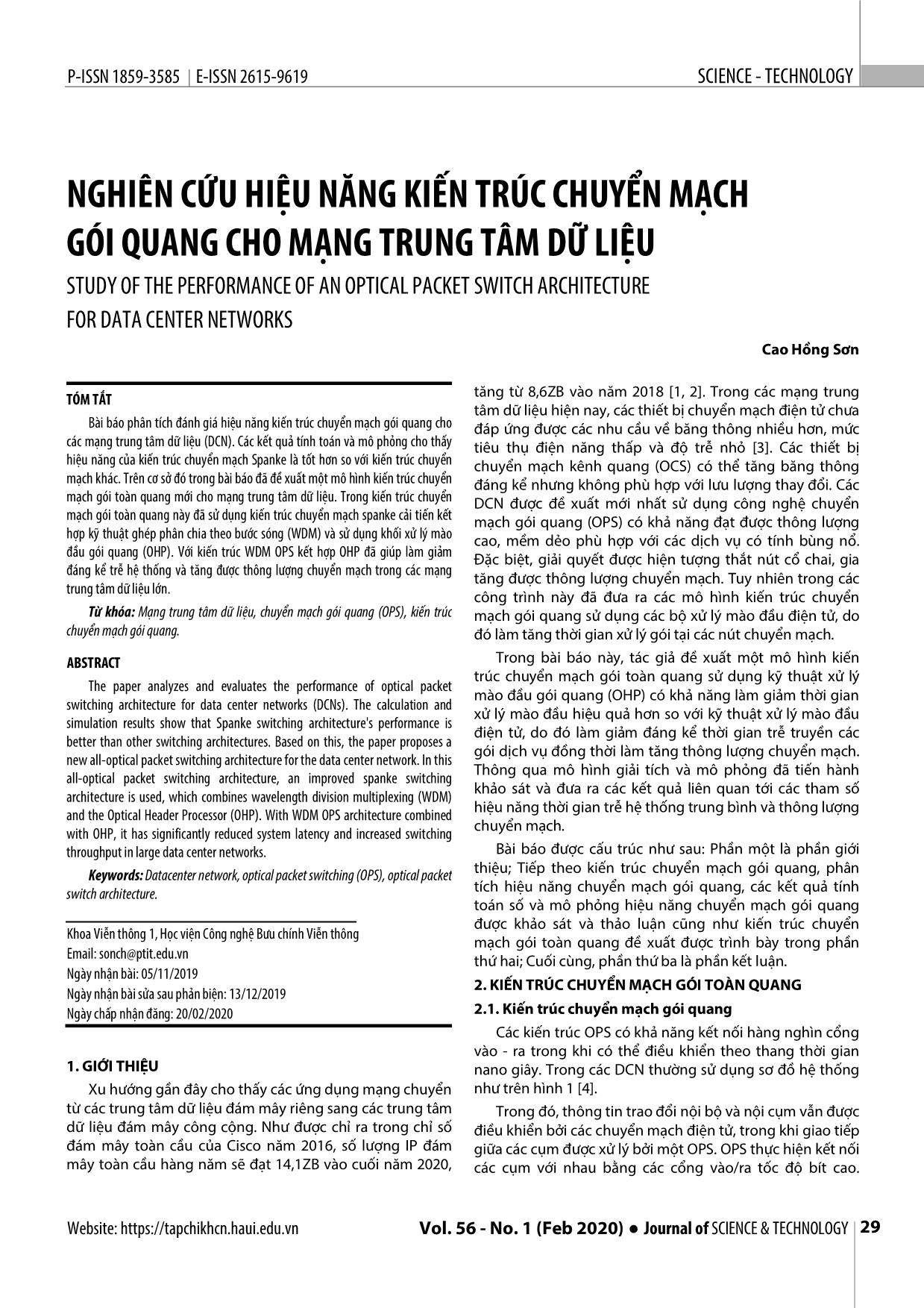

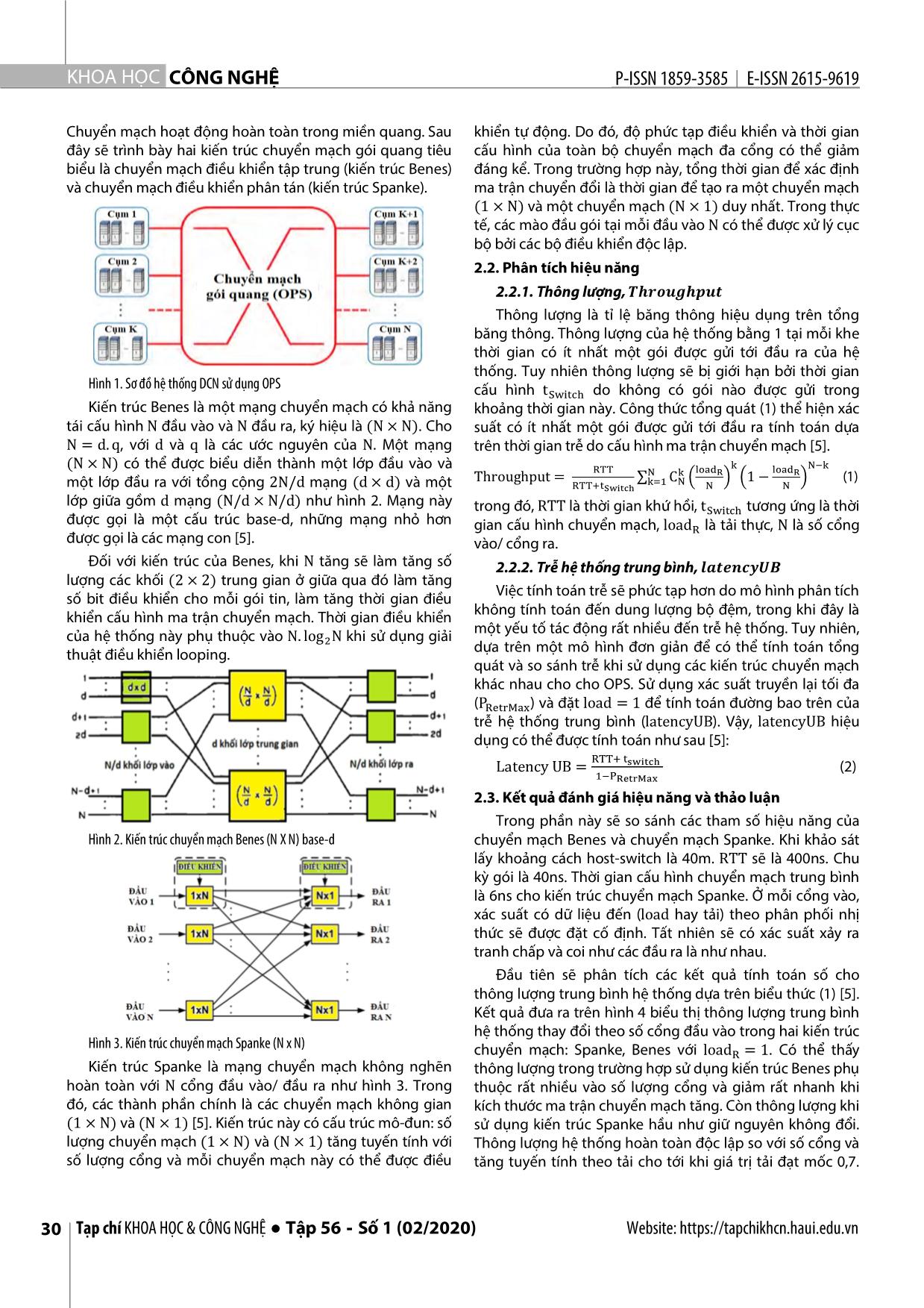

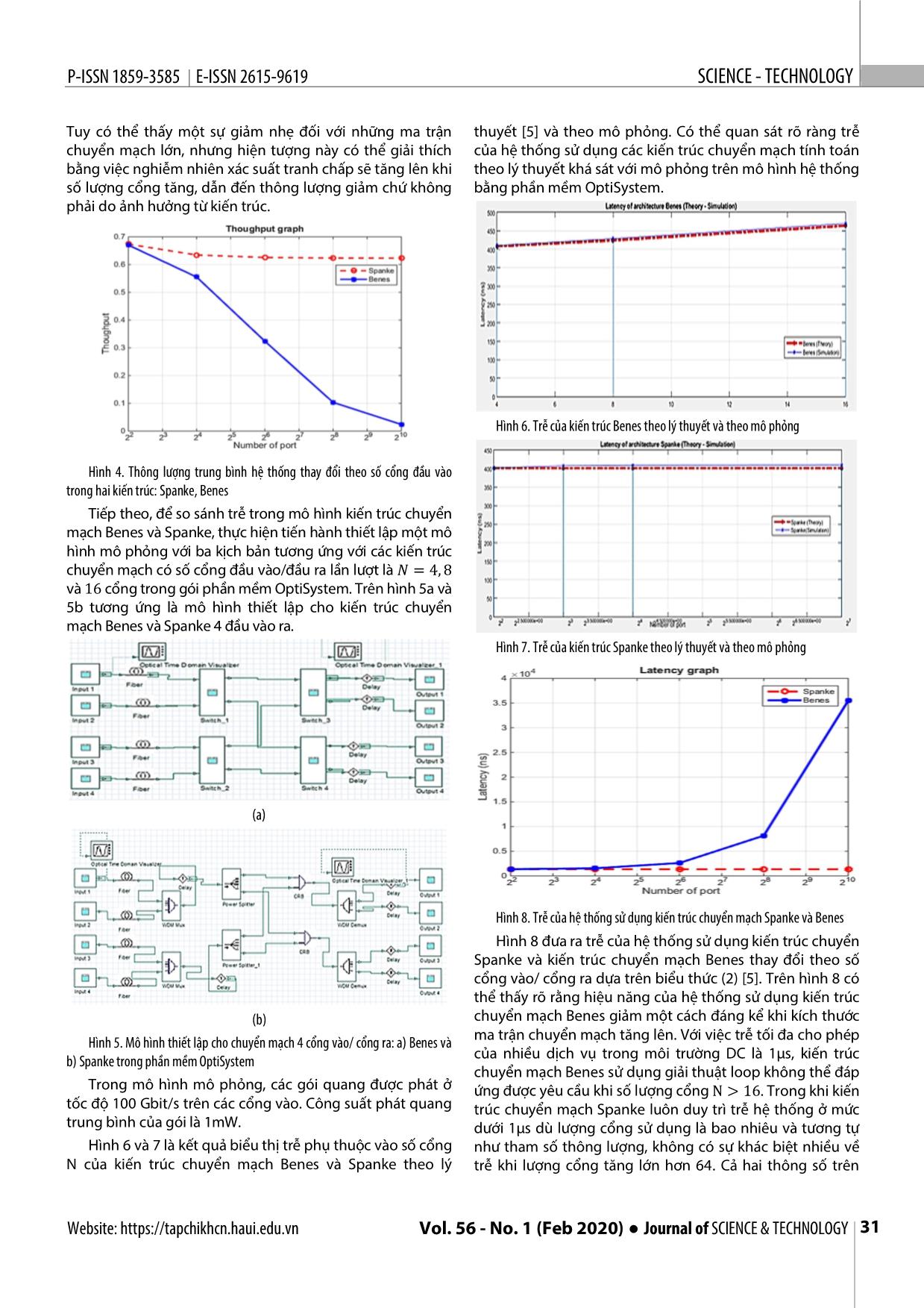

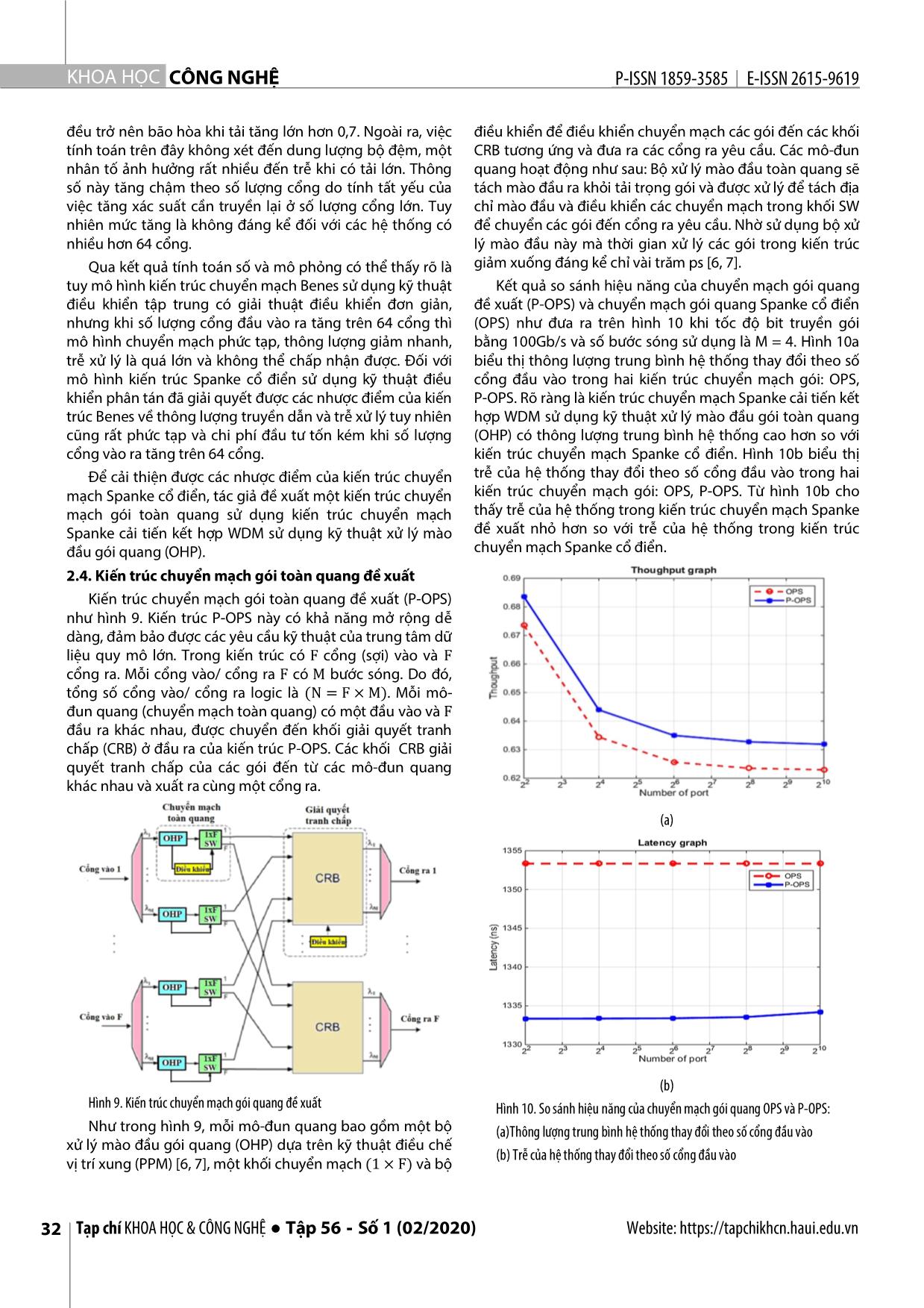

hing throughput in large data center networks. Bài báo được cấu trúc như sau: Phần một là phần giới Keywords: Datacenter network, optical packet switching (OPS), optical packet thiệu; Tiếp theo kiến trúc chuyển mạch gói quang, phân switch architecture. tích hiệu năng chuyển mạch gói quang, các kết quả tính toán số và mô phỏng hiệu năng chuyển mạch gói quang được khảo sát và thảo luận cũng như kiến trúc chuyển Khoa Viễn thông 1, Học viện Công nghệ Bưu chính Viễn thông mạch gói toàn quang đề xuất được trình bày trong phần Email: sonch@ptit.edu.vn thứ hai; Cuối cùng, phần thứ ba là phần kết luận. Ngày nhận bài: 05/11/2019 2. KIẾN TRÚC CHUYỂN MẠCH GÓI TOÀN QUANG Ngày nhận bài sửa sau phản biện: 13/12/2019 Ngày chấp nhận đăng: 20/02/2020 2.1. Kiến trúc chuyển mạch gói quang Các kiến trúc OPS có khả năng kết nối hàng nghìn cổng vào - ra trong khi có thể điều khiển theo thang thời gian 1. GIỚI THIỆU nano giây. Trong các DCN thường sử dụng sơ đồ hệ thống Xu hướng gần đây cho thấy các ứng dụng mạng chuyển như trên hình 1 [4]. từ các trung tâm dữ liệu đám mây riêng sang các trung tâm Trong đó, thông tin trao đổi nội bộ và nội cụm vẫn được dữ liệu đám mây công cộng. Như được chỉ ra trong chỉ số điều khiển bởi các chuyển mạch điện tử, trong khi giao tiếp đám mây toàn cầu của Cisco năm 2016, số lượng IP đám giữa các cụm được xử lý bởi một OPS. OPS thực hiện kết nối mây toàn cầu hàng năm sẽ đạt 14,1ZB vào cuối năm 2020, các cụm với nhau bằng các cổng vào/ra tốc độ bít cao. Website: https://tapchikhcn.haui.edu.vn Vol. 56 - No. 1 (Feb 2020) ● Journal of SCIENCE & TECHNOLOGY 29 KHOA H ỌC CÔNG NGHỆ P - ISSN 1859 - 3585 E - ISSN 2615 - 961 9 Chuyển mạch hoạt động hoàn toàn trong miền quang. Sau khiển tự động. Do đó, độ phức tạp điều khiển và thời gian đây sẽ trình bày hai kiến trúc chuyển mạch gói quang tiêu cấu hình của toàn bộ chuyển mạch đa cổng có thể giảm biểu là chuyển mạch điều khiển tập trung (kiến trúc Benes) đáng kể. Trong trường hợp này, tổng thời gian để xác định và chuyển mạch điều khiển phân tán (kiến trúc Spanke). ma trận chuyển đổi là thời gian để tạo ra một chuyển mạch (1 × N) và một chuyển mạch (N × 1) duy nhất. Trong thực tế, các mào đầu gói tại mỗi đầu vào N có thể được xử lý cục bộ bởi các bộ điều khiển độc lập. 2.2. Phân tích hiệu năng 2.2.1. Thông lượng, ���������� Thông lượng là tỉ lệ băng thông hiệu dụng trên tổng băng thông. Thông lượng của hệ thống bằng 1 tại mỗi khe thời gian có ít nhất một gói được gửi tới đầu ra của hệ thống. Tuy nhiên thông lượng sẽ bị giới hạn bởi thời gian Hình 1. Sơ đồ hệ thống DCN sử dụng OPS cấu hình t������ do không có gói nào được gửi trong Kiến trúc Benes là một mạng chuyển mạch có khả năng khoảng thời gian này. Công thức tổng quát (1) thể hiện xác tái cấu hình N đầu vào và N đầu ra, ký hiệu là (N × N). Cho suất có ít nhất một gói được gửi tới đầu ra tính toán dựa N = d. q, với d và q là các ước nguyên của N. Một mạng trên thời gian trễ do cấu hình ma trận chuyển mạch [5]. (N × N) có thể được biểu diễn thành một lớp đầu vào và � ��� ��� � � ����� ����� Throughput = ∑��� C� � � �1 − � (1) một lớp đầu ra với tổng cộng 2N/d mạng (d × d) và một ����������� � � lớp giữa gồm d mạng (N/d × N/d) như hình 2. Mạng này trong đó, RTT là thời gian khứ hồi, t������ tương ứng là thời được gọi là một cấu trúc base-d, những mạng nhỏ hơn gian cấu hình chuyển mạch, load� là tải thực, N là số cổng được gọi là các mạng con [5]. vào/ cổng ra. Đối với kiến trúc của Benes, khi N tăng sẽ làm tăng số 2.2.2. Trễ hệ thống trung bình, ��������� lượng các khối (2 × 2) trung gian ở giữa qua đó làm tăng Việc tính toán trễ sẽ phức tạp hơn do mô hình phân tích số bit điều khiển cho mỗi gói tin, làm tăng thời gian điều không tính toán đến dung lượng bộ đệm, trong khi đây là khiển cấu hình ma trận chuyển mạch. Thời gian điều khiển một yếu tố tác động rất nhiều đến trễ hệ thống. Tuy nhiên, của hệ thống này phụ thuộc vào N. log N khi sử dụng giải � dựa trên một mô hình đơn giản để có thể tính toán tổng thuật điều khiển looping. quát và so sánh trễ khi sử dụng các kiến trúc chuyển mạch khác nhau cho cho OPS. Sử dụng xác suất truyền lại tối đa (P�������) và đặt load = 1 để tính toán đường bao trên của trễ hệ thống trung bình (latencyUB). Vậy, latencyUB hiệu dụng có thể được tính toán như sau [5]: ���� � Latency UB = ������ (2) ���������� 2.3. Kết quả đánh giá hiệu năng và thảo luận Trong phần này sẽ so sánh các tham số hiệu năng của Hình 2. Kiến trúc chuyển mạch Benes (N X N) base-d chuyển mạch Benes và chuyển mạch Spanke. Khi khảo sát lấy khoảng cách host-switch là 40m. RTT sẽ là 400ns. Chu kỳ gói là 40ns. Thời gian cấu hình chuyển mạch trung bình là 6ns cho kiến trúc chuyển mạch Spanke. Ở mỗi cổng vào, xác suất có dữ liệu đến (load hay tải) theo phân phối nhị thức sẽ được đặt cố định. Tất nhiên sẽ có xác suất xảy ra tranh chấp và coi như các đầu ra là như nhau. Đầu tiên sẽ phân tích các kết quả tính toán số cho thông lượng trung bình hệ thống dựa trên biểu thức (1) [5]. Kết quả đưa ra trên hình 4 biểu thị thông lượng trung bình hệ thống thay đổi theo số cổng đầu vào trong hai kiến trúc Hình 3. Kiến trúc chuyển mạch Spanke (N x N) chuyển mạch: Spanke, Benes với load� = 1. Có thể thấy Kiến trúc Spanke là mạng chuyển mạch không nghẽn thông lượng trong trường hợp sử dụng kiến trúc Benes phụ hoàn toàn với N cổng đầu vào/ đầu ra như hình 3. Trong thuộc rất nhiều vào số lượng cổng và giảm rất nhanh khi đó, các thành phần chính là các chuyển mạch không gian kích thước ma trận chuyển mạch tăng. Còn thông lượng khi (1 × N) và (N × 1) [5]. Kiến trúc này có cấu trúc mô-đun: số sử dụng kiến trúc Spanke hầu như giữ nguyên không đổi. lượng chuyển mạch (1 × N) và (N × 1) tăng tuyến tính với Thông lượng hệ thống hoàn toàn độc lập so với số cổng và số lượng cổng và mỗi chuyển mạch này có thể được điều tăng tuyến tính theo tải cho tới khi giá trị tải đạt mốc 0,7. 30 Tạp chí KHOA HỌC & CÔNG NGHỆ ● Tập 56 - Số 1 (02/2020) Website: https://tapchikhcn.haui.edu.vn P-ISSN 1859-3585 E-ISSN 2615-9619 SCIENCE - TECHNOLOGY Tuy có thể thấy một sự giảm nhẹ đối với những ma trận thuyết [5] và theo mô phỏng. Có thể quan sát rõ ràng trễ chuyển mạch lớn, nhưng hiện tượng này có thể giải thích của hệ thống sử dụng các kiến trúc chuyển mạch tính toán bằng việc nghiễm nhiên xác suất tranh chấp sẽ tăng lên khi theo lý thuyết khá sát với mô phỏng trên mô hình hệ thống số lượng cổng tăng, dẫn đến thông lượng giảm chứ không bằng phần mềm OptiSystem. phải do ảnh hưởng từ kiến trúc. Hình 6. Trễ của kiến trúc Benes theo lý thuyết và theo mô phỏng Hình 4. Thông lượng trung bình hệ thống thay đổi theo số cổng đầu vào trong hai kiến trúc: Spanke, Benes Tiếp theo, để so sánh trễ trong mô hình kiến trúc chuyển mạch Benes và Spanke, thực hiện tiến hành thiết lập một mô hình mô phỏng với ba kịch bản tương ứng với các kiến trúc chuyển mạch có số cổng đầu vào/đầu ra lần lượt là � = 4, 8 và 16 cổng trong gói phần mềm OptiSystem. Trên hình 5a và 5b tương ứng là mô hình thiết lập cho kiến trúc chuyển mạch Benes và Spanke 4 đầu vào ra. Hình 7. Trễ của kiến trúc Spanke theo lý thuyết và theo mô phỏng (a) Hình 8. Trễ của hệ thống sử dụng kiến trúc chuyển mạch Spanke và Benes Hình 8 đưa ra trễ của hệ thống sử dụng kiến trúc chuyển Spanke và kiến trúc chuyển mạch Benes thay đổi theo số cổng vào/ cổng ra dựa trên biểu thức (2) [5]. Trên hình 8 có thể thấy rõ rằng hiệu năng của hệ thống sử dụng kiến trúc (b) chuyển mạch Benes giảm một cách đáng kể khi kích thước ma trận chuyển mạch tăng lên. Với việc trễ tối đa cho phép Hình 5. Mô hình thiết lập cho chuyển mạch 4 cổng vào/ cổng ra: a) Benes và của nhiều dịch vụ trong môi trường DC là 1µs, kiến trúc b) Spanke trong phần mềm OptiSystem chuyển mạch Benes sử dụng giải thuật loop không thể đáp Trong mô hình mô phỏng, các gói quang được phát ở ứng được yêu cầu khi số lượng cổng N > 16. Trong khi kiến tốc độ 100 Gbit/s trên các cổng vào. Công suất phát quang trúc chuyển mạch Spanke luôn duy trì trễ hệ thống ở mức trung bình của gói là 1mW. dưới 1µs dù lượng cổng sử dụng là bao nhiêu và tương tự Hình 6 và 7 là kết quả biểu thị trễ phụ thuộc vào số cổng như tham số thông lượng, không có sự khác biệt nhiều về N của kiến trúc chuyển mạch Benes và Spanke theo lý trễ khi lượng cổng tăng lớn hơn 64. Cả hai thông số trên Website: https://tapchikhcn.haui.edu.vn Vol. 56 - No. 1 (Feb 2020) ● Journal of SCIENCE & TECHNOLOGY 31 KHOA H ỌC CÔNG NGHỆ P - ISSN 1859 - 3585 E - ISSN 2615 - 961 9 đều trở nên bão hòa khi tải tăng lớn hơn 0,7. Ngoài ra, việc điều khiển để điều khiển chuyển mạch các gói đến các khối tính toán trên đây không xét đến dung lượng bộ đệm, một CRB tương ứng và đưa ra các cổng ra yêu cầu. Các mô-đun nhân tố ảnh hưởng rất nhiều đến trễ khi có tải lớn. Thông quang hoạt động như sau: Bộ xử lý mào đầu toàn quang sẽ số này tăng chậm theo số lượng cổng do tính tất yếu của tách mào đầu ra khỏi tải trọng gói và được xử lý để tách địa việc tăng xác suất cần truyền lại ở số lượng cổng lớn. Tuy chỉ mào đầu và điều khiển các chuyển mạch trong khối SW nhiên mức tăng là không đáng kể đối với các hệ thống có để chuyển các gói đến cổng ra yêu cầu. Nhờ sử dụng bộ xử nhiều hơn 64 cổng. lý mào đầu này mà thời gian xử lý các gói trong kiến trúc Qua kết quả tính toán số và mô phỏng có thể thấy rõ là giảm xuống đáng kể chỉ vài trăm ps [6, 7]. tuy mô hình kiến trúc chuyển mạch Benes sử dụng kỹ thuật Kết quả so sánh hiệu năng của chuyển mạch gói quang điều khiển tập trung có giải thuật điều khiển đơn giản, đề xuất (P-OPS) và chuyển mạch gói quang Spanke cổ điển nhưng khi số lượng cổng đầu vào ra tăng trên 64 cổng thì (OPS) như đưa ra trên hình 10 khi tốc độ bit truyền gói mô hình chuyển mạch phức tạp, thông lượng giảm nhanh, bằng 100Gb/s và số bước sóng sử dụng là M = 4. Hình 10a trễ xử lý là quá lớn và không thể chấp nhận được. Đối với biểu thị thông lượng trung bình hệ thống thay đổi theo số mô hình kiến trúc Spanke cổ điển sử dụng kỹ thuật điều cổng đầu vào trong hai kiến trúc chuyển mạch gói: OPS, khiển phân tán đã giải quyết được các nhược điểm của kiến P-OPS. Rõ ràng là kiến trúc chuyển mạch Spanke cải tiến kết trúc Benes về thông lượng truyền dẫn và trễ xử lý tuy nhiên hợp WDM sử dụng kỹ thuật xử lý mào đầu gói toàn quang cũng rất phức tạp và chi phí đầu tư tốn kém khi số lượng (OHP) có thông lượng trung bình hệ thống cao hơn so với cổng vào ra tăng trên 64 cổng. kiến trúc chuyển mạch Spanke cổ điển. Hình 10b biểu thị Để cải thiện được các nhược điểm của kiến trúc chuyển trễ của hệ thống thay đổi theo số cổng đầu vào trong hai mạch Spanke cổ điển, tác giả đề xuất một kiến trúc chuyển kiến trúc chuyển mạch gói: OPS, P-OPS. Từ hình 10b cho mạch gói toàn quang sử dụng kiến trúc chuyển mạch thấy trễ của hệ thống trong kiến trúc chuyển mạch Spanke Spanke cải tiến kết hợp WDM sử dụng kỹ thuật xử lý mào đề xuất nhỏ hơn so với trễ của hệ thống trong kiến trúc đầu gói quang (OHP). chuyển mạch Spanke cổ điển. 2.4. Kiến trúc chuyển mạch gói toàn quang đề xuất Kiến trúc chuyển mạch gói toàn quang đề xuất (P-OPS) như hình 9. Kiến trúc P-OPS này có khả năng mở rộng dễ dàng, đảm bảo được các yêu cầu kỹ thuật của trung tâm dữ liệu quy mô lớn. Trong kiến trúc có F cổng (sợi) vào và F cổng ra. Mỗi cổng vào/ cổng ra F có M bước sóng. Do đó, tổng số cổng vào/ cổng ra logic là (N = F × M). Mỗi mô- đun quang (chuyển mạch toàn quang) có một đầu vào và F đầu ra khác nhau, được chuyển đến khối giải quyết tranh chấp (CRB) ở đầu ra của kiến trúc P-OPS. Các khối CRB giải quyết tranh chấp của các gói đến từ các mô-đun quang khác nhau và xuất ra cùng một cổng ra. (a) (b) Hình 9. Kiến trúc chuyển mạch gói quang đề xuất Hình 10. So sánh hiệu năng của chuyển mạch gói quang OPS và P-OPS: Như trong hình 9, mỗi mô-đun quang bao gồm một bộ (a)Thông lượng trung bình hệ thống thay đổi theo số cổng đầu vào xử lý mào đầu gói quang (OHP) dựa trên kỹ thuật điều chế (b) Trễ của hệ thống thay đổi theo số cổng đầu vào vị trí xung (PPM) [6, 7], một khối chuyển mạch (1 × F) và bộ 32 Tạp chí KHOA HỌC & CÔNG NGHỆ ● Tập 56 - Số 1 (02/2020) Website: https://tapchikhcn.haui.edu.vn P-ISSN 1859-3585 E-ISSN 2615-9619 SCIENCE - TECHNOLOGY 3. KẾT LUẬN Trong bài báo, trên cơ sở phân tích đánh giá hiệu năng của kiến trúc chuyển mạch Benes và kiến trúc chuyển mạch Spanke, tác giả đã đề xuất một kiến trúc chuyển mạch gói toàn quang mới nhờ kết hợp kiến trúc Spanke cải tiến và kỹ thuật ghép phân chia theo bước sóng (WDM), đồng thời trong kiến trúc chuyển mạch sử dụng bộ xử lý mào đầu gói quang (OHP). Kiến trúc OPS đề xuất này có khả năng tăng dung lượng các cổng mà vẫn đáp ứng được các yêu cầu đặt ra cho các trung tâm dữ liệu lớn. Bên cạnh đó, với việc sử dụng bộ xử lý mào đầu gói toàn quang đã giảm được đáng kể thời gian xử lý các gói tại kiến trúc chuyển mạch và đã góp phần cải thiện được hiệu năng của hệ thống. Cụ thể làm giảm trễ hệ thống trung bình và cải thiện thông lượng chuyển mạch. TÀI LIỆU THAM KHẢO [1]. Shu, Y., et al., 2018. Programmable OPS/OCS hybrid data centre network. Optical Fiber Technology, 44, 102–114. [2]. Toru Segawa, et al., 2016. High-speed Optical Packet Switching for Photonic Datacenter Networks. NTT Technical Review, Vol. 14, No. 1. [3]. C. Chaintoutis, A. Bogris and D. Syvridis, 2018. P-Torus: Torus-based Optical Packet Switching Architecture for intra-Data Centre Networks. Photonics in Switching and Computing (PSC), pp. 1-3. [4]. N. Calabretta, R. P. Centelles, S. Di Lucente and H. J. S. Dorren, 2013. On the performance of a large-scale optical packet switch under realistic data center traffic. in IEEE/OSA Journal of Optical Communications and Networking, vol. 5, no. 6, pp. 565-573. [5]. S.Di Lucente, 2013. Optical packet switching with distributed control for high performance data center networks. Diss. Technische Universiteit Eindhoven. [6]. Son H.Cao, Hong M.Nguyen, and Quy Q.Ho 2015. Improving Performance of All-Optical Packet Switching Network with a Modified Pulse Position Modulation Routing Table. International Journal of Electronics and Data Communications, Vol.3, No.3, pp.90-99, 11-2015. [7]. Son H.Cao, 2017. Multi-wavelength All-Optical Packet Switching Node Using Modified Pulse Position Modulation Header Processing. Tạp chí Khoa học và công nghệ, Trường Đại học Công nghiệp Hà Nội số 43, trang 3-7. AUTHOR INFORMATION Cao Hong Son Facuty of Telecommunication 1, Posts and Telecommunications Institute of Technology Website: https://tapchikhcn.haui.edu.vn Vol. 56 - No. 1 (Feb 2020) ● Journal of SCIENCE & TECHNOLOGY 33

File đính kèm:

nghien_cuu_hieu_nang_kien_truc_chuyen_mach_goi_quang_cho_man.pdf

nghien_cuu_hieu_nang_kien_truc_chuyen_mach_goi_quang_cho_man.pdf