Nghịch lưu ghép tầng cầu H với độ lợi điện áp cao

Trong bài báo này, nghịch lưu một pha ghép tầng cầu H với độ lợi điện áp cao (CHBqSBI-HG) được trình bày. Cấu hình này được biết đến như một bộ chuyển đổi công suất một

chặng mà nó hoạt động ở hai chế độ: chế độ ngắn mạch (ST) và chế độ không ngắn mạch

(NST). Do đó, trạng thái ngắn mạch (hai khóa trên một nhánh cùng dẫn trong một thời gian)

được khắc phục, vì thế chất lượng của điện áp và dòng điện ngõ ra được cải thiện. Ngoài ra,

một phương pháp điều chế độ rộng xung (PWM) được cải tiến và kết hợp với cấu hình CHBqSBI-HG để đạt được sự vượt trội về độ lợi điện áp cũng như giảm điện áp trên các linh kiện

công suất. Một mô hình mô phỏng được xây dựng để kiểm chứng nguyên lý hoạt động theo

phân tích lý thuyết của CHB-qSBI-HG.

Trang 1

Trang 2

Trang 3

Trang 4

Trang 5

Trang 6

Trang 7

Tóm tắt nội dung tài liệu: Nghịch lưu ghép tầng cầu H với độ lợi điện áp cao

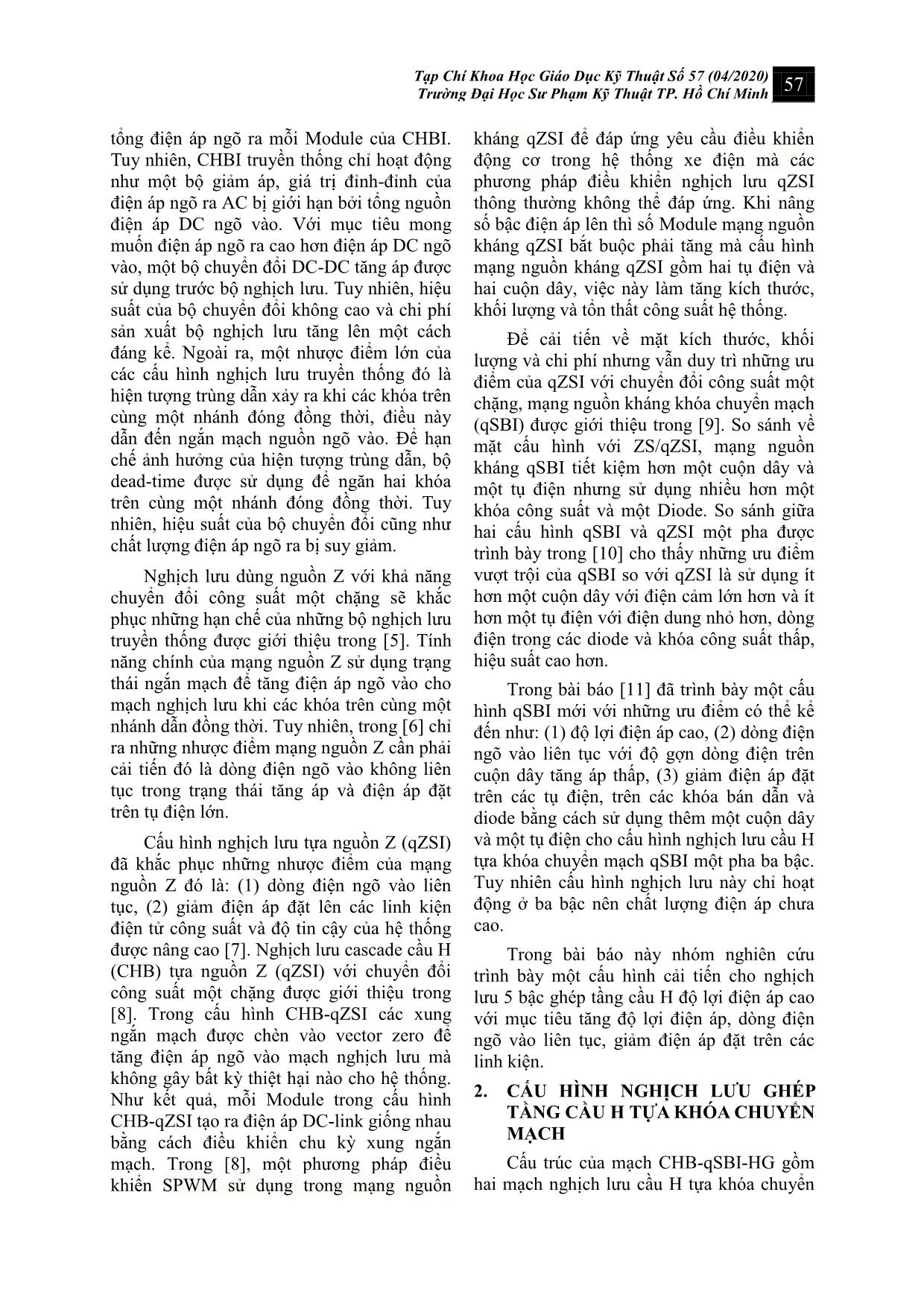

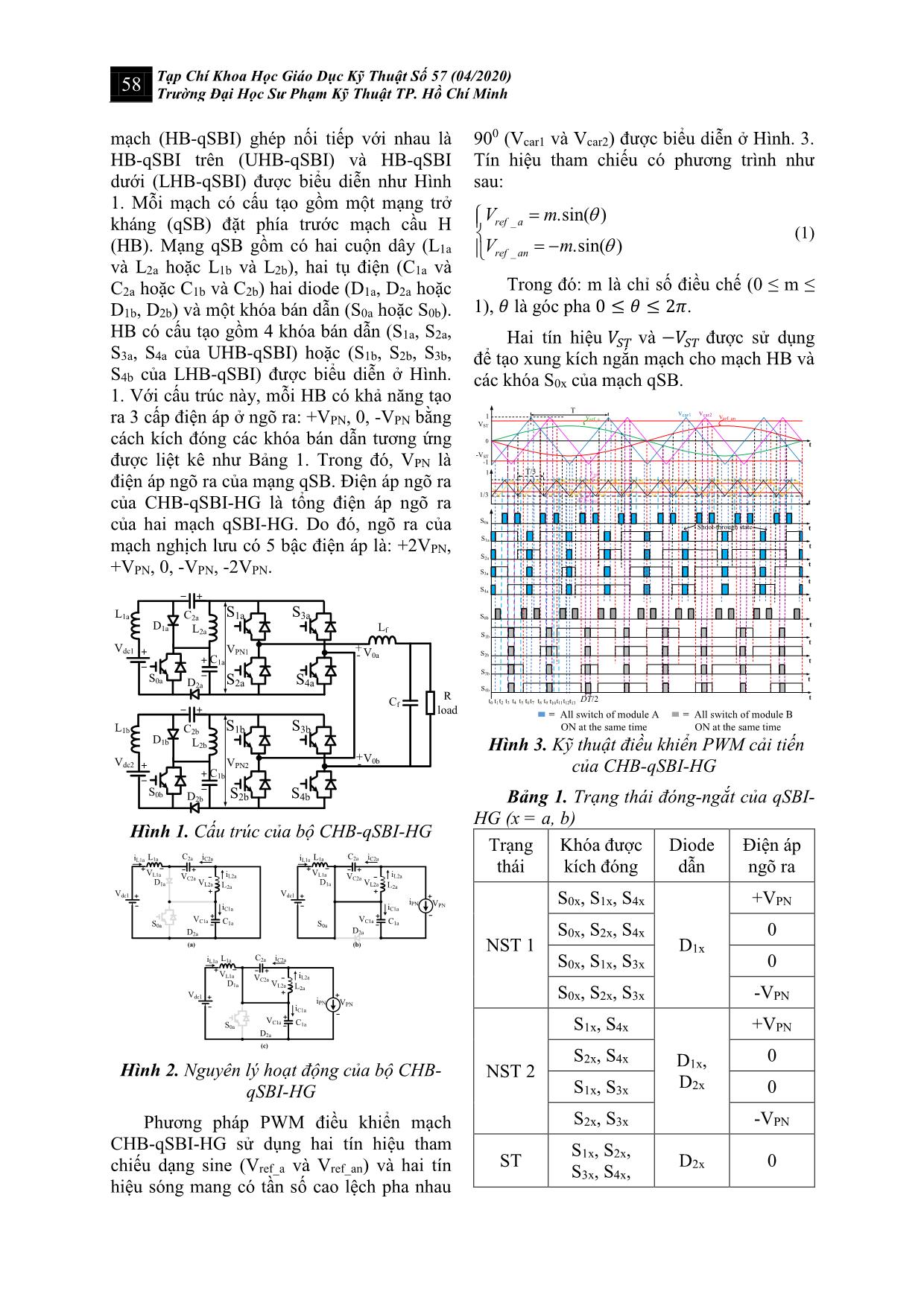

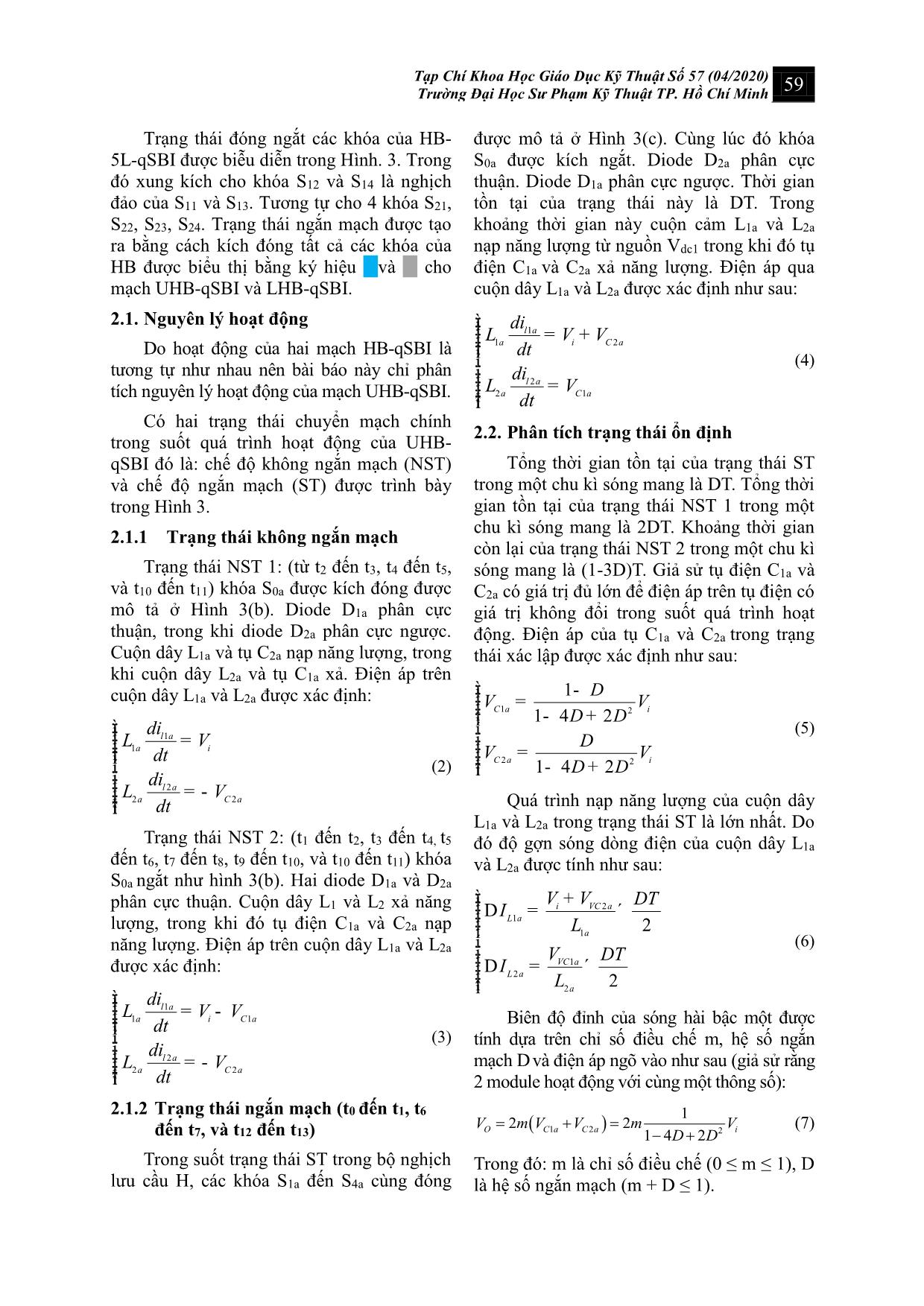

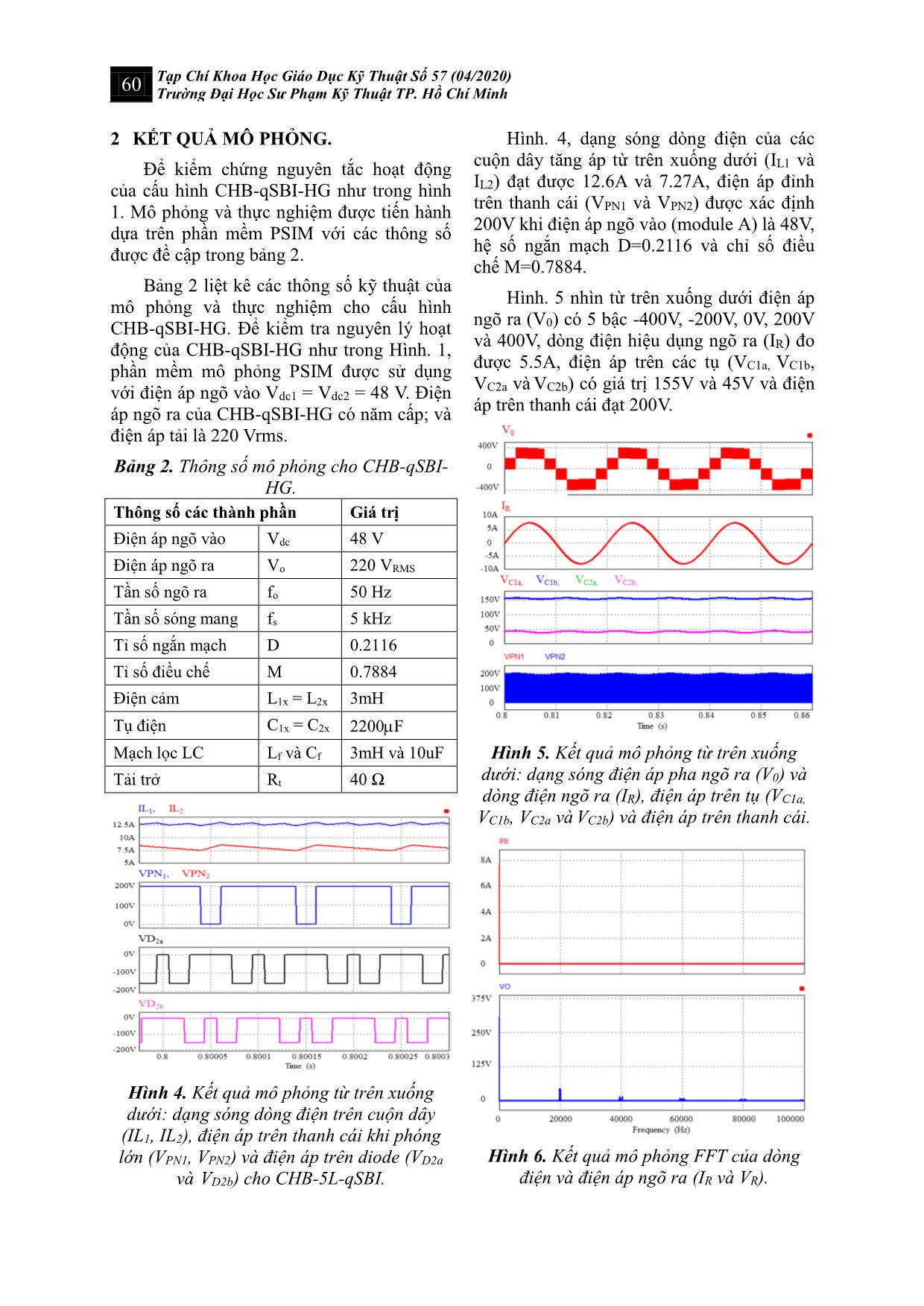

gõ vào liên tục, (2) giảm điện áp đặt lên các linh kiện điện tử công suất và độ tin cậy của hệ thống được nâng cao [7]. Nghịch lưu cascade cầu H (CHB) tựa nguồn Z (qZSI) với chuyển đổi công suất một chặng được giới thiệu trong [8]. Trong cấu hình CHB-qZSI các xung ngắn mạch được chèn vào vector zero để tăng điện áp ngõ vào mạch nghịch lưu mà không gây bất kỳ thiệt hại nào cho hệ thống. Như kết quả, mỗi Module trong cấu hình CHB-qZSI tạo ra điện áp DC-link giống nhau bằng cách điều khiển chu kỳ xung ngắn mạch. Trong [8], một phương pháp điều khiển SPWM sử dụng trong mạng nguồn kháng qZSI để đáp ứng yêu cầu điều khiển động cơ trong hệ thống xe điện mà các phương pháp điều khiển nghịch lưu qZSI thông thường không thể đáp ứng. Khi nâng số bậc điện áp lên thì số Module mạng nguồn kháng qZSI bắt buộc phải tăng mà cấu hình mạng nguồn kháng qZSI gồm hai tụ điện và hai cuộn dây, việc này làm tăng kích thước, khối lượng và tổn thất công suất hệ thống. Để cải tiến về mặt kích thước, khối lượng và chi phí nhưng vẫn duy trì những ưu điểm của qZSI với chuyển đổi công suất một chặng, mạng nguồn kháng khóa chuyển mạch (qSBI) được giới thiệu trong [9]. So sánh về mặt cấu hình với ZS/qZSI, mạng nguồn kháng qSBI tiết kiệm hơn một cuộn dây và một tụ điện nhưng sử dụng nhiều hơn một khóa công suất và một Diode. So sánh giữa hai cấu hình qSBI và qZSI một pha được trình bày trong [10] cho thấy những ưu điểm vượt trội của qSBI so với qZSI là sử dụng ít hơn một cuộn dây với điện cảm lớn hơn và ít hơn một tụ điện với điện dung nhỏ hơn, dòng điện trong các diode và khóa công suất thấp, hiệu suất cao hơn. Trong bài báo [11] đã trình bày một cấu hình qSBI mới với những ưu điểm có thể kể đến như: (1) độ lợi điện áp cao, (2) dòng điện ngõ vào liên tục với độ gợn dòng điện trên cuộn dây tăng áp thấp, (3) giảm điện áp đặt trên các tụ điện, trên các khóa bán dẫn và diode bằng cách sử dụng thêm một cuộn dây và một tụ điện cho cấu hình nghịch lưu cầu H tựa khóa chuyển mạch qSBI một pha ba bậc. Tuy nhiên cấu hình nghịch lưu này chỉ hoạt động ở ba bậc nên chất lượng điện áp chưa cao. Trong bài báo này nhóm nghiên cứu trình bày một cấu hình cải tiến cho nghịch lưu 5 bậc ghép tầng cầu H độ lợi điện áp cao với mục tiêu tăng độ lợi điện áp, dòng điện ngõ vào liên tục, giảm điện áp đặt trên các linh kiện. 2. CẤU HÌNH NGHỊCH LƯU GHÉP TẦNG CẦU H TỰA KHÓA CHUYỂN MẠCH Cấu trúc của mạch CHB-qSBI-HG gồm hai mạch nghịch lưu cầu H tựa khóa chuyển 58 Tạp Chí Khoa Học Giáo Dục Kỹ Thuật Số 57 (04/2020) Trường Đại Học Sư Phạm Kỹ Thuật TP. Hồ Chí Minh mạch (HB-qSBI) ghép nối tiếp với nhau là HB-qSBI trên (UHB-qSBI) và HB-qSBI dưới (LHB-qSBI) được biểu diễn như Hình 1. Mỗi mạch có cấu tạo gồm một mạng trở kháng (qSB) đặt phía trước mạch cầu H (HB). Mạng qSB gồm có hai cuộn dây (L1a và L2a hoặc L1b và L2b), hai tụ điện (C1a và C2a hoặc C1b và C2b) hai diode (D1a, D2a hoặc D1b, D2b) và một khóa bán dẫn (S0a hoặc S0b). HB có cấu tạo gồm 4 khóa bán dẫn (S1a, S2a, S3a, S4a của UHB-qSBI) hoặc (S1b, S2b, S3b, S4b của LHB-qSBI) được biểu diễn ở Hình. 1. Với cấu trúc này, mỗi HB có khả năng tạo ra 3 cấp điện áp ở ngõ ra: +VPN, 0, -VPN bằng cách kích đóng các khóa bán dẫn tương ứng được liệt kê như Bảng 1. Trong đó, VPN là điện áp ngõ ra của mạng qSB. Điện áp ngõ ra của CHB-qSBI-HG là tổng điện áp ngõ ra của hai mạch qSBI-HG. Do đó, ngõ ra của mạch nghịch lưu có 5 bậc điện áp là: +2VPN, +VPN, 0, -VPN, -2VPN. L1a D2a Vdc1 C1a D1a R load S1a S2a S3a S4aS0a Cf Lf - +V0a - +V0b L2a C2a L1b D2b Vdc2 C1b D1b S1b S2b S3b S4bS0b L2b C2b VPN1 VPN2 Hình 1. Cấu trúc của bộ CHB-qSBI-HG (a) C1a C2a VC2a VC1a D1a S0a VL1a VL2a iC1a iL1a Vdc1 iC2a iL2a L1a L2a D2a (b) C1a C2a VC2a VC1a D1a S0a VL1a VL2a iC1a iL1a Vdc1 iC2a iL2a L1a L2a D2a VPNiPN (c) C1a C2a VC2a VC1a D1a S0a VL1a VL2a iC1a iL1a Vdc1 iC2a iL2a L1a L2a D2a VPNiPN Hình 2. Nguyên lý hoạt động của bộ CHB- qSBI-HG Phương pháp PWM điều khiển mạch CHB-qSBI-HG sử dụng hai tín hiệu tham chiếu dạng sine (Vref_a và Vref_an) và hai tín hiệu sóng mang có tần số cao lệch pha nhau 900 (Vcar1 và Vcar2) được biểu diễn ở Hình. 3. Tín hiệu tham chiếu có phương trình như sau: _ _ .sin( ) .sin( ) ref a ref an V m V m (1) Trong đó: m là chỉ số điều chế (0 ≤ m ≤ 1), 𝜃 là góc pha 0 ≤ 𝜃 ≤ 2𝜋. Hai tín hiệu 𝑉𝑆𝑇 và −𝑉𝑆𝑇 được sử dụng để tạo xung kích ngắn mạch cho mạch HB và các khóa S0x của mạch qSB. vref S0a S1a S2a t t t Shoot-through state DT/2 S3a S4a S0b t t = All switch of module A ON at the same time = All switch of module B ON at the same time t1t2 t3 t4 t5 t7 t8t0 1/3 T/3 4/3-vref t vcar1 VST 1 t -1 0 T vref_anvref_a -VST vcar2 1 S1b S2b S3b S4b t t t t t t6 t9 t10t11t12t13 Hình 3. Kỹ thuật điều khiển PWM cải tiến của CHB-qSBI-HG Bảng 1. Trạng thái đóng-ngắt của qSBI- HG (x = a, b) Trạng thái Khóa được kích đóng Diode dẫn Điện áp ngõ ra NST 1 S0x, S1x, S4x D1x +VPN S0x, S2x, S4x 0 S0x, S1x, S3x 0 S0x, S2x, S3x -VPN NST 2 S1x, S4x D1x, D2x +VPN S2x, S4x 0 S1x, S3x 0 S2x, S3x -VPN ST S1x, S2x, S3x, S4x, D2x 0 Tạp Chí Khoa Học Giáo Dục Kỹ Thuật Số 57 (04/2020) Trường Đại Học Sư Phạm Kỹ Thuật TP. Hồ Chí Minh 59 Trạng thái đóng ngắt các khóa của HB- 5L-qSBI được biễu diễn trong Hình. 3. Trong đó xung kích cho khóa S12 và S14 là nghịch đảo của S11 và S13. Tương tự cho 4 khóa S21, S22, S23, S24. Trạng thái ngắn mạch được tạo ra bằng cách kích đóng tất cả các khóa của HB được biểu thị bằng ký hiệu và cho mạch UHB-qSBI và LHB-qSBI. 2.1. Nguyên lý hoạt động Do hoạt động của hai mạch HB-qSBI là tương tự như nhau nên bài báo này chỉ phân tích nguyên lý hoạt động của mạch UHB-qSBI. Có hai trạng thái chuyển mạch chính trong suốt quá trình hoạt động của UHB- qSBI đó là: chế độ không ngắn mạch (NST) và chế độ ngắn mạch (ST) được trình bày trong Hình 3. 2.1.1 Trạng thái không ngắn mạch Trạng thái NST 1: (từ t2 đến t3, t4 đến t5, và t10 đến t11) khóa S0a được kích đóng được mô tả ở Hình 3(b). Diode D1a phân cực thuận, trong khi diode D2a phân cực ngược. Cuộn dây L1a và tụ C2a nạp năng lượng, trong khi cuộn dây L2a và tụ C1a xả. Điện áp trên cuộn dây L1a và L2a được xác định: 1 1 2 2 2 l a a i l a a C a di L V dt di L V dt ìïï =ïïï í ïï = -ïïïî (2) Trạng thái NST 2: (t1 đến t2, t3 đến t4, t5 đến t6, t7 đến t8, t9 đến t10, và t10 đến t11) khóa S0a ngắt như hình 3(b). Hai diode D1a và D2a phân cực thuận. Cuộn dây L1 và L2 xả năng lượng, trong khi đó tụ điện C1a và C2a nạp năng lượng. Điện áp trên cuộn dây L1a và L2a được xác định: 1 1 1 2 2 2 l a a i C a l a a C a di L V V dt di L V dt ìïï = -ïïï í ïï = -ïïïî (3) 2.1.2 Trạng thái ngắn mạch (t0 đến t1, t6 đến t7, và t12 đến t13) Trong suốt trạng thái ST trong bộ nghịch lưu cầu H, các khóa S1a đến S4a cùng đóng được mô tả ở Hình 3(c). Cùng lúc đó khóa S0a được kích ngắt. Diode D2a phân cực thuận. Diode D1a phân cực ngược. Thời gian tồn tại của trạng thái này là DT. Trong khoảng thời gian này cuộn cảm L1a và L2a nạp năng lượng từ nguồn Vdc1 trong khi đó tụ điện C1a và C2a xả năng lượng. Điện áp qua cuộn dây L1a và L2a được xác định như sau: 1 1 2 2 2 1 l a a i C a l a a C a di L V V dt di L V dt ìïï = +ïïï í ïï =ïïïî (4) 2.2. Phân tích trạng thái ổn định Tổng thời gian tồn tại của trạng thái ST trong một chu kì sóng mang là DT. Tổng thời gian tồn tại của trạng thái NST 1 trong một chu kì sóng mang là 2DT. Khoảng thời gian còn lại của trạng thái NST 2 trong một chu kì sóng mang là (1-3D)T. Giả sử tụ điện C1a và C2a có giá trị đủ lớn để điện áp trên tụ điện có giá trị không đổi trong suốt quá trình hoạt động. Điện áp của tụ C1a và C2a trong trạng thái xác lập được xác định như sau: 1 2 2 2 1 1 4 2 1 4 2 C a i C a i D V V D D D V V D D ì -ïï =ïï - +ï í ïï =ïï - +ïî (5) Quá trình nạp năng lượng của cuộn dây L1a và L2a trong trạng thái ST là lớn nhất. Do đó độ gợn sóng dòng điện của cuộn dây L1a và L2a được tính như sau: 2 1 1 1 2 2 2 2 i VC a L a a VC a L a a V V DT I L V DT I L ì +ïï D = ´ïïï í ïï D = ´ïïïî (6) Biên độ đỉnh của sóng hài bậc một được tính dựa trên chỉ số điều chế m, hệ số ngắn mạch D và điện áp ngõ vào như sau (giả sử rằng 2 module hoạt động với cùng một thông số): 1 2 2 1 2 2 1 4 2 O C a C a iV m V V m V D D (7) Trong đó: m là chỉ số điều chế (0 ≤ m ≤ 1), D là hệ số ngắn mạch (m + D ≤ 1). 60 Tạp Chí Khoa Học Giáo Dục Kỹ Thuật Số 57 (04/2020) Trường Đại Học Sư Phạm Kỹ Thuật TP. Hồ Chí Minh 2 KẾT QUẢ MÔ PHỎNG. Để kiểm chứng nguyên tắc hoạt động của cấu hình CHB-qSBI-HG như trong hình 1. Mô phỏng và thực nghiệm được tiến hành dựa trên phần mềm PSIM với các thông số được đề cập trong bảng 2. Bảng 2 liệt kê các thông số kỹ thuật của mô phỏng và thực nghiệm cho cấu hình CHB-qSBI-HG. Để kiểm tra nguyên lý hoạt động của CHB-qSBI-HG như trong Hình. 1, phần mềm mô phỏng PSIM được sử dụng với điện áp ngõ vào Vdc1 = Vdc2 = 48 V. Điện áp ngõ ra của CHB-qSBI-HG có năm cấp; và điện áp tải là 220 Vrms. Bảng 2. Thông số mô phỏng cho CHB-qSBI- HG. Thông số các thành phần Giá trị Điện áp ngõ vào Vdc 48 V Điện áp ngõ ra Vo 220 VRMS Tần số ngõ ra fo 50 Hz Tần số sóng mang fs 5 kHz Tỉ số ngắn mạch D 0.2116 Tỉ số điều chế M 0.7884 Điện cảm L1x = L2x 3mH Tụ điện C1x = C2x 2200F Mạch lọc LC Lf và Cf 3mH và 10uF Tải trở Rt 40 Ω Hình 4. Kết quả mô phỏng từ trên xuống dưới: dạng sóng dòng điện trên cuộn dây (IL1, IL2), điện áp trên thanh cái khi phóng lớn (VPN1, VPN2) và điện áp trên diode (VD2a và VD2b) cho CHB-5L-qSBI. Hình. 4, dạng sóng dòng điện của các cuộn dây tăng áp từ trên xuống dưới (IL1 và IL2) đạt được 12.6A và 7.27A, điện áp đỉnh trên thanh cái (VPN1 và VPN2) được xác định 200V khi điện áp ngõ vào (module A) là 48V, hệ số ngắn mạch D=0.2116 và chỉ số điều chế M=0.7884. Hình. 5 nhìn từ trên xuống dưới điện áp ngõ ra (V0) có 5 bậc -400V, -200V, 0V, 200V và 400V, dòng điện hiệu dụng ngõ ra (IR) đo được 5.5A, điện áp trên các tụ (VC1a, VC1b, VC2a và VC2b) có giá trị 155V và 45V và điện áp trên thanh cái đạt 200V. Hình 5. Kết quả mô phỏng từ trên xuống dưới: dạng sóng điện áp pha ngõ ra (V0) và dòng điện ngõ ra (IR), điện áp trên tụ (VC1a, VC1b, VC2a và VC2b) và điện áp trên thanh cái. Hình 6. Kết quả mô phỏng FFT của dòng điện và điện áp ngõ ra (IR và VR). Tạp Chí Khoa Học Giáo Dục Kỹ Thuật Số 57 (04/2020) Trường Đại Học Sư Phạm Kỹ Thuật TP. Hồ Chí Minh 61 Hình. 6 từ trên xuống dưới, phổ hài của tín hiệu dòng điện và điện áp ngõ ra (IR và VR). Từ hình 6 có thể thấy rằng biên độ hài bậc một của dòng điện và điện áp ngõ ra là 7.65A và 300V. Độ méo dạng dòng điện và điện áp ngõ ra (THDi và THDu) đạt được 1.27%, 38.9% tại trị hiệu dụng dòng điện ngõ ra 5.5A và trị hiệu dụng điện áp ngõ ra 220V. Với kết quả THDi này đã thỏa mãn tiêu chí nhỏ hơn 5% của tiêu chuẩn IEC61000-4-30 Edition 2 Class A. 3 KẾT LUẬN Bài báo này đã trình bày một mạng nguồn kháng qSB được kết nối với nghịch lưu cascade cầu H 1 pha năm bậc. Bên cạnh các tính năng tăng, giảm áp (Buck-Boost), cấu hình này còn chịu đựng ngắn mạch và đa bậc. Nguyên lý hoạt động và kết quả mô phỏng cho cấu hình CHB-qSBI-HG đã được phân tích phù hợp với cơ sở lý thuyết. Cấu hình và giải thuật cho CHB-qSBI-HG phù hợp với các ứng dụng như: hệ thống PV, pin nhiên liệu và động cơ, hòa lưới, UPS. LỜI CẢM ƠN Bài báo này được thực hiện tại phòng thí nghiệm điện tử công suất nâng cao D405. DANH MỤC TỪ VIẾT TẮT THD Total Harmonic Distortion qSBI Quasi Switch Boost Inverter CHB-FL Cascaded H-Bridge Five-Level CHB-qSBI-HG Cascaded H-Bridge quasi switch bosst inverter high gain qZS Quasi-Z-Source CHB Cascaded H-Bridge PWM Pulse Width Modulation IGBT Insulated Gate Bipolar Transistor SPWM Sine Pulse Width Modulation TÀI LIỆU THAM KHẢO [1] Rodríguez, J., Lai, J. S., Peng, F. Z.: ‘Multilevel inverters: a survey of topologies, controls, and applications’, IEEE Trans. Ind. Electron., 2002, vol 49, no. 4, pp. 724–738. [2] Pereda, J., Dixon, J.: ‘Cascaded multilevel converters: optimal asymmetries and floating capacitor control’, IEEE Trans. Ind. Electron., 2013, vol 60, no. 11, pp. 4784–4793. [3] Mohammad Ahmad, Anil Kumar Jha, Sitaram Jana and, Kishore Kumar, “Simulation and Performance Analysis of a Grid Connected Multilevel Inverter Considering Either Battery or Solar PV as DC Input Sources”, 2017 3rd International Conference on Computational Intelligence & Communication Technology (CICT), Feb. 2017. [4] Ngô Văn Quang Bình, Nguyễn Văn Liễn, “Ứng dụng nghịch lưu áp đa mức trong hệ truyền động”, Tạp chí Khoa Học và Công Nghệ, đại học Đà Nẵng, số 1(36), xuất bản năm 2010. [5] A.Shanmuga priyaa, Dr.R.Seyezhai, Dr.B.L.Mathur, “Design and Implementation of Cascaded Z-Source Multilevel Inverter”, IEEE Industrial Electronics Magazine, vol. 10, no. 1, pp. 6 - 24 March 2016. [6] R. Miceli, G. Schettino, F. Viola, F. Blaabjerg, Y. Yang, “Modified Modulation Techniques for Quasi-Z-Source Cascaded H-Bridge Inverters”, IECON 2018 - 44th Annual Conference of the IEEE Industrial Electronics Society, 31 December 2018. 62 Tạp Chí Khoa Học Giáo Dục Kỹ Thuật Số 57 (04/2020) Trường Đại Học Sư Phạm Kỹ Thuật TP. Hồ Chí Minh [7] Katharina Beer and Bernhard Piepenbreier, " Properties and Advantages of the Quasi-Z- Source Inverter for DC-AC Conversion for Electric Vehicle Applications", Emobility- Electrical power, pp.l-6, 2010. [8] Dongsen Sun, Baoming Ge, Fang Zheng Peng, Abu Rub Haitham, Daqiang Bi, Yushan Liu,“A New Grid-Connected PV System Based on Cascaded H-bridge Quasi-Z Source Inverter”, 2012 IEEE International Symposium on Industrial Electronics, 12 July 2012. [9] Adda Ravindranath, Santanu K. Mishra, Avinash Joshi, “Analysis and PWM Control of Switched Boost Inverter”, IEEE Transactions on Industrial Electronics, vol. 60, no. 12, pp. 5593 – 5602, November 2012. [10] M. K. Nguyen, Y. C. Lim and S. J. Park, “A comparison between singlephase quasi-Z- source and quasi-switched boost inverters,” IEEE Trans. Ind. Electron., vol. 62, no. 10, pp. 6336 - 6344, Oct. 2015. [11] Minh-Khai Nguyen, Truong-Duy Duong, Young-Cheol Lim, Joon-Ho Choi, “High Voltage Gain Quasi-Switched Boost Inverters With Low Input Current Ripple”, IEEE Trans. Ind. Electron, Vol. 15, no, 9, pp. 4857 – 4866, Sept. 2019. Tác giả chịu trách nhiệm bài viết: Đỗ Đức Trí Trường Đại học Sư phạm Kỹ thuật Tp. HCM Email: tridd@hcmute.edu.vn

File đính kèm:

nghich_luu_ghep_tang_cau_h_voi_do_loi_dien_ap_cao.pdf

nghich_luu_ghep_tang_cau_h_voi_do_loi_dien_ap_cao.pdf