Nghịch lưu 3 bậc hình T với khả năng chịu lỗi

Bài báo này trình bày hoạt động của bộ nghịch lưu quasi Z Source (qZS) hình T 3 bậc với

điều kiện hoạt động bình thường và lỗi khóa đóng ngắt hở mạch. Cấu hình này được kết hợp

bởi hai thành phần chính: mạng nguồn kháng (qZS) và nghịch lưu ba bậc hình T. Bên cạnh

những ưu điểm của nghịch lưu đa bậc nguồn áp, cấu hình này còn có khả năng khắc phục

hiện tượng trùng dẫn trong nghịch lưu đa bậc truyền thống. Ngoài ra, cấu hình này đảm bảo

duy trì tính ổn định cho hệ thống khi bất kỳ khóa đóng ngắt phía nghịch lưu hình T bị lỗi hở

mạch. Trong các phương pháp sửa lỗi hở mạch cho cấu hình nghịch lưu truyền thống, công

suất ngõ ra sẽ bị giảm. Tuy nhiên, nhược điểm này sẽ được khắc phục nhờ đặc tính tăng áp

của mạng qSZ. Các kết quả mô phỏng và thực nghiệm được trình bày để kiểm chứng giải

thuật điều khiển.

Trang 1

Trang 2

Trang 3

Trang 4

Trang 5

Trang 6

Trang 7

Trang 8

Tóm tắt nội dung tài liệu: Nghịch lưu 3 bậc hình T với khả năng chịu lỗi

c

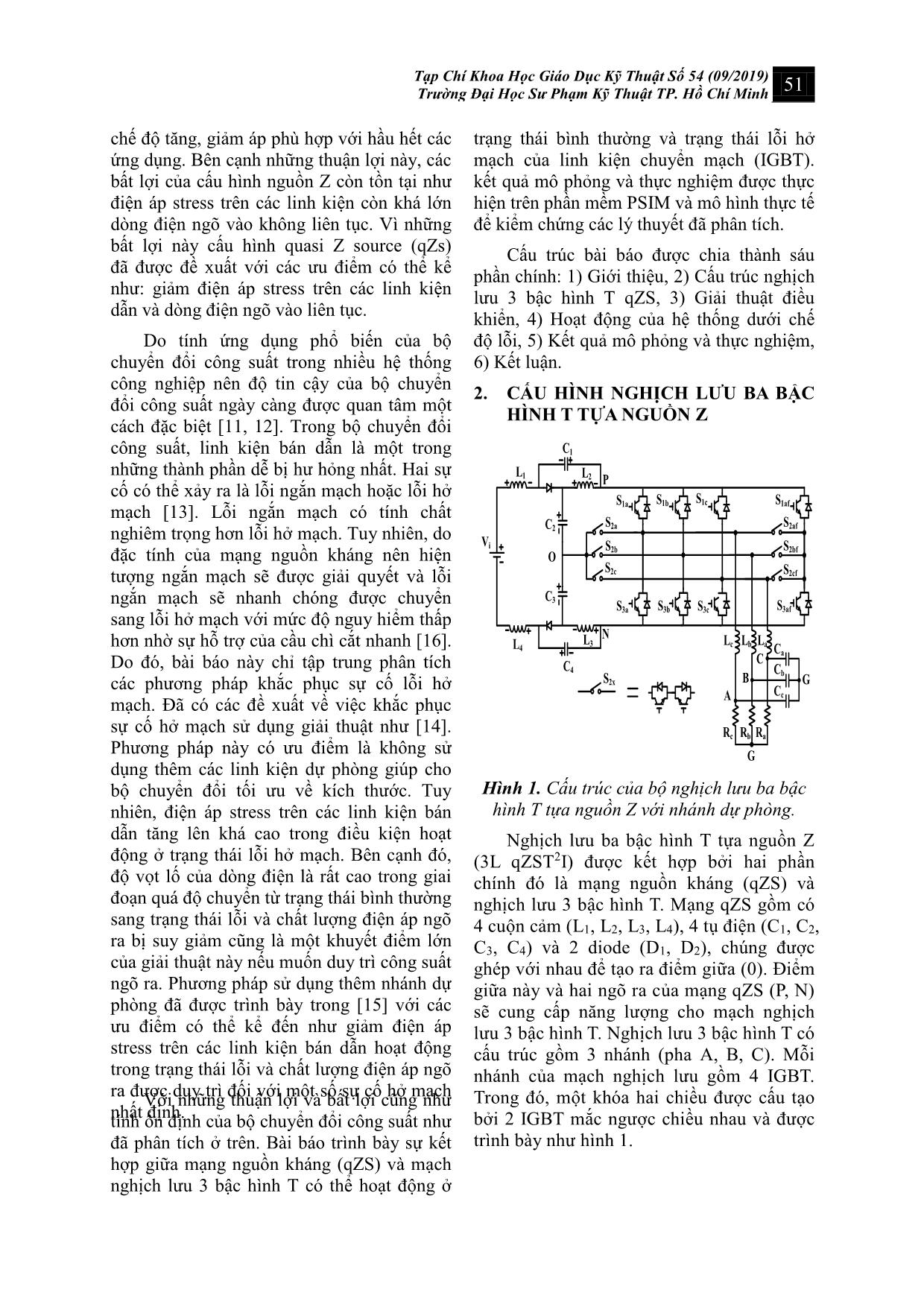

ghép với nhau để tạo ra điểm giữa (0). Điểm

giữa này và hai ngõ ra của mạng qZS (P, N)

sẽ cung cấp năng lượng cho mạch nghịch

lưu 3 bậc hình T. Nghịch lưu 3 bậc hình T có

cấu trúc gồm 3 nhánh (pha A, B, C). Mỗi

nhánh của mạch nghịch lưu gồm 4 IGBT.

Trong đó, một khóa hai chiều được cấu tạo

bởi 2 IGBT mắc ngược chiều nhau và được

trình bày như hình 1.

52

Tạp Chí Khoa Học Giáo Dục Kỹ Thuật Số 54 (09/2019)

Trường Đại Học Sư Phạm Kỹ Thuật TP. Hồ Chí Minh

Với cấu trúc 3 bậc, nghịch lưu hình T có

khả năng tạo ra 3 cấp điện áp trên ngõ ra

bằng cách kích đóng khóa S1x (x = a, b, c)

điện áp VXO sẽ đạt được giá trị +VPN/2. Điện

áp VXO sẽ đạt giá trị 0 khi khóa S2x được kích

đóng. Tương tự, điện áp VXO sẽ đạt giá trị –

VPN/2 bằng cách kích đóng S3x.

Giá trị điện áp VPN là kết quả của quá

trình hoạt động của mạng nguồn kháng qZS

và có thể phân tích bởi hai chế độ hoạt động

chính của mạch đó là: chế độ ngắn mạch và

không ngắn mạch như trình bày ở bảng 1 và

hình 2.

Gọi hệ số boost (độ lợi) của nghịch lưu 3

bậc là B. Để xác định B, chúng ta dựa vào

hai trạng thái hoạt động của bộ nghịch lưu:

Trạng thái ngắn mạch và trạng thái không

ngắn mạch.

Bảng 1. Các trạng thái hoạt động của mạch

nghịch lưu

Trạng

thái

Các khóa

hoạt động

Diode phân

cực thuận

Điện áp

ngõ ra

NST

(hình

2a)

S1x D1, D2 +VPN/2

S2x D1, D2 0

S3x D1, D2 -VPN/2

ST

(hình

2b)

S1x, S2x,

S3x

Không 0

NST: không ngắn mạch; ST ngắn mạch

O

L2L1

L3L4

C1

C4

C2

C3

P

N

D1

D2

O

L2L1

L3L4

C1

C4

C2

C3

P

N

D1

D2

ViVi

(a) (b)

Hình 2. Nguyên lý hoạt động của 3L qZST2I.

a) Trạng thái không ngắn mạch, b) trạng thái

ngắn mạch

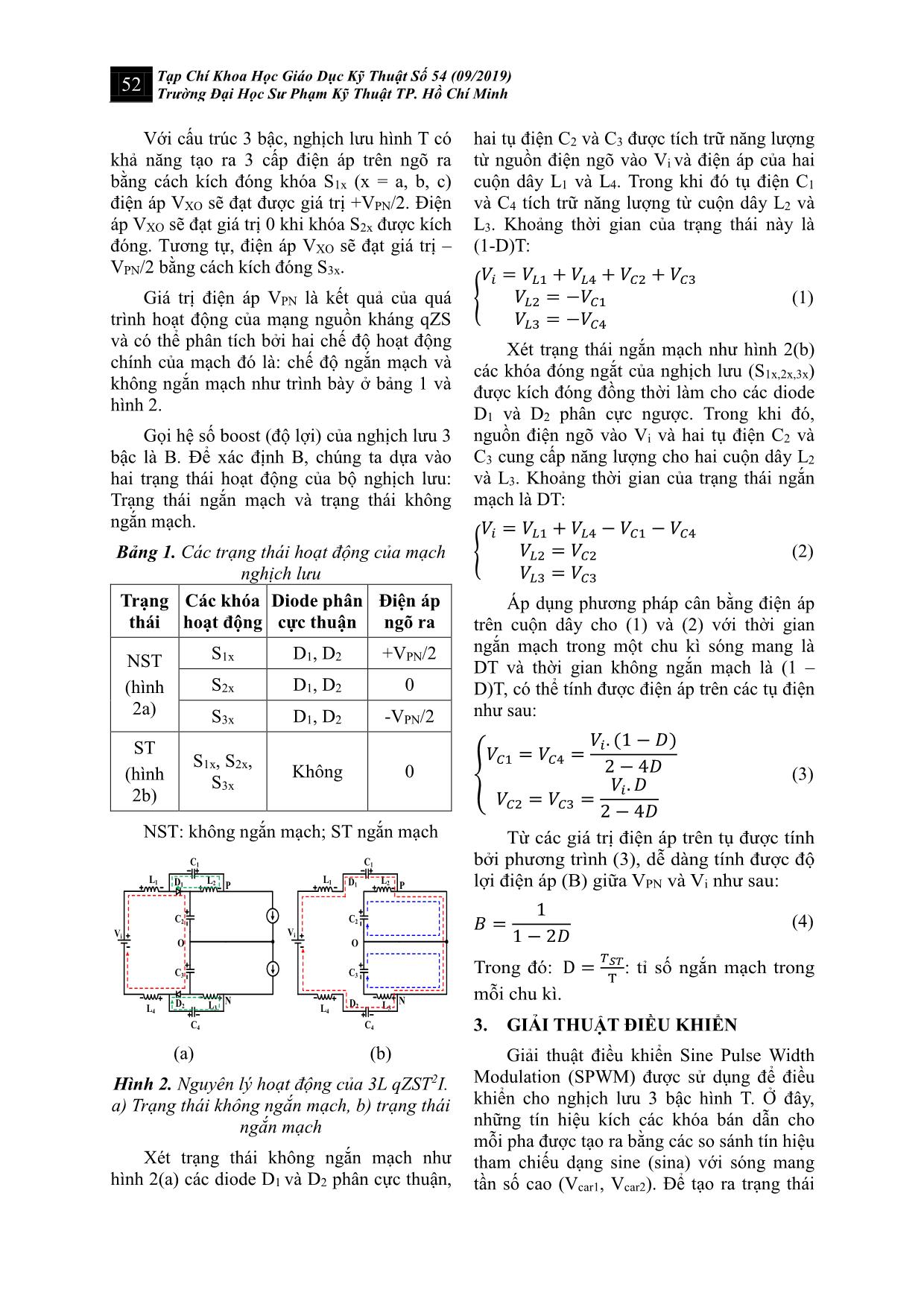

Xét trạng thái không ngắn mạch như

hình 2(a) các diode D1 và D2 phân cực thuận,

hai tụ điện C2 và C3 được tích trữ năng lượng

từ nguồn điện ngõ vào Vi và điện áp của hai

cuộn dây L1 và L4. Trong khi đó tụ điện C1

và C4 tích trữ năng lượng từ cuộn dây L2 và

L3. Khoảng thời gian của trạng thái này là

(1-D)T:

{

𝑉𝑖 = 𝑉𝐿1 + 𝑉𝐿4 + 𝑉𝐶2 + 𝑉𝐶3

𝑉𝐿2 = −𝑉𝐶1

𝑉𝐿3 = −𝑉𝐶4

(1)

Xét trạng thái ngắn mạch như hình 2(b)

các khóa đóng ngắt của nghịch lưu (S1x,2x,3x)

được kích đóng đồng thời làm cho các diode

D1 và D2 phân cực ngược. Trong khi đó,

nguồn điện ngõ vào Vi và hai tụ điện C2 và

C3 cung cấp năng lượng cho hai cuộn dây L2

và L3. Khoảng thời gian của trạng thái ngắn

mạch là DT:

{

𝑉𝑖 = 𝑉𝐿1 + 𝑉𝐿4 − 𝑉𝐶1 − 𝑉𝐶4

𝑉𝐿2 = 𝑉𝐶2

𝑉𝐿3 = 𝑉𝐶3

(2)

Áp dụng phương pháp cân bằng điện áp

trên cuộn dây cho (1) và (2) với thời gian

ngắn mạch trong một chu kì sóng mang là

DT và thời gian không ngắn mạch là (1 –

D)T, có thể tính được điện áp trên các tụ điện

như sau:

{

𝑉𝐶1 = 𝑉𝐶4 =

𝑉𝑖. (1 − 𝐷)

2 − 4𝐷

𝑉𝐶2 = 𝑉𝐶3 =

𝑉𝑖. 𝐷

2 − 4𝐷

(3)

Từ các giá trị điện áp trên tụ được tính

bởi phương trình (3), dễ dàng tính được độ

lợi điện áp (B) giữa VPN và Vi như sau:

𝐵 =

1

1 − 2𝐷

(4)

Trong đó: D =

𝑇𝑆𝑇

T

: tỉ số ngắn mạch trong

mỗi chu kì.

3. GIẢI THUẬT ĐIỀU KHIỂN

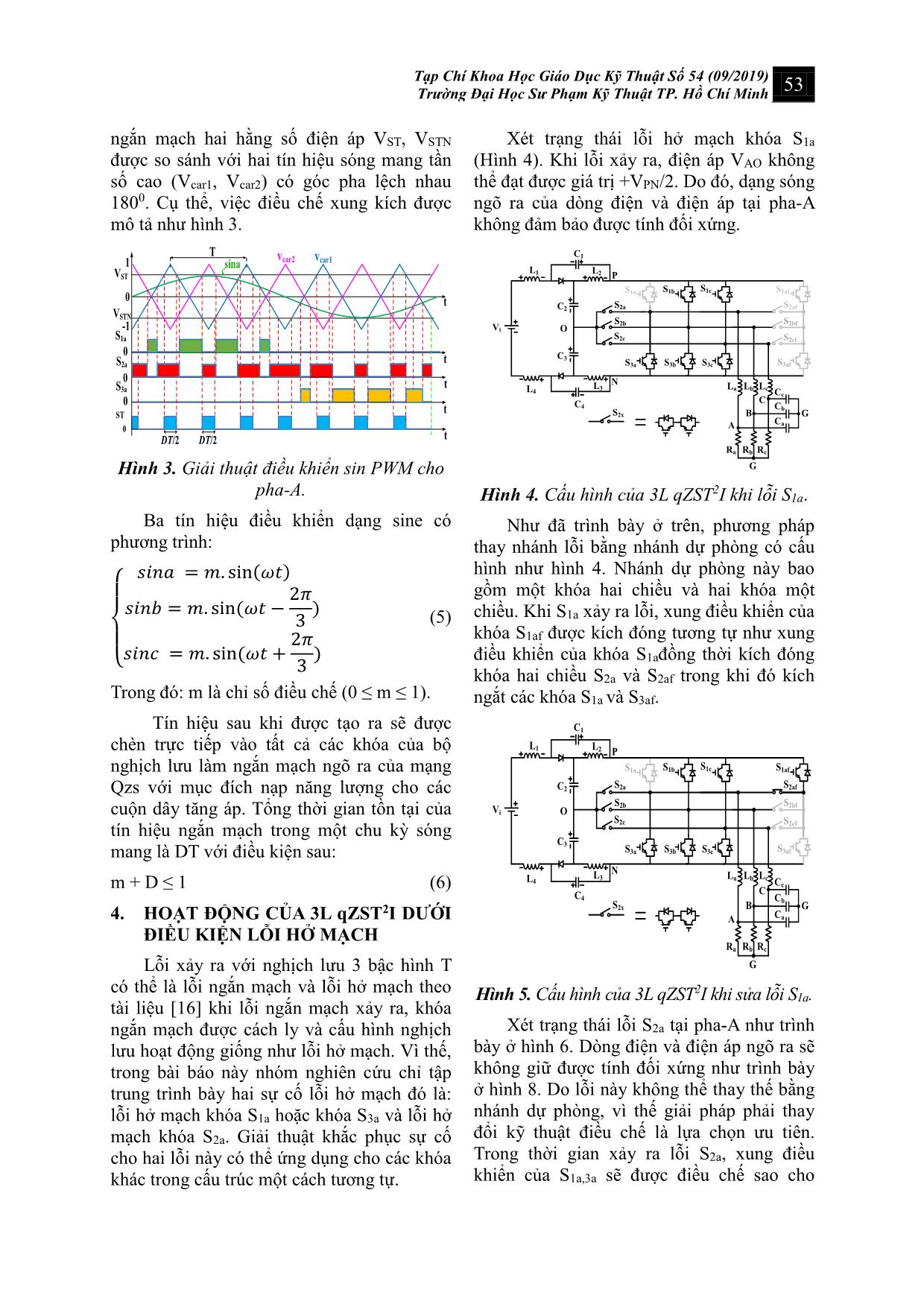

Giải thuật điều khiển Sine Pulse Width

Modulation (SPWM) được sử dụng để điều

khiển cho nghịch lưu 3 bậc hình T. Ở đây,

những tín hiệu kích các khóa bán dẫn cho

mỗi pha được tạo ra bằng các so sánh tín hiệu

tham chiếu dạng sine (sina) với sóng mang

tần số cao (Vcar1, Vcar2). Để tạo ra trạng thái

Tạp Chí Khoa Học Giáo Dục Kỹ Thuật Số 54 (09/2019)

Trường Đại Học Sư Phạm Kỹ Thuật TP. Hồ Chí Minh

53

ngắn mạch hai hằng số điện áp VST, VSTN

được so sánh với hai tín hiệu sóng mang tần

số cao (Vcar1, Vcar2) có góc pha lệch nhau

1800. Cụ thể, việc điều chế xung kích được

mô tả như hình 3.

vcar1

VST

S1a

S2a

S3a

ST

0

t

1

0

0

0

t

t

t

t

-1

0

T

sina

VSTN

DT/2 DT/2

vcar2

Hình 3. Giải thuật điều khiển sin PWM cho

pha-A.

Ba tín hiệu điều khiển dạng sine có

phương trình:

{

𝑠𝑖𝑛𝑎 = 𝑚. sin(𝜔𝑡)

𝑠𝑖𝑛𝑏 = 𝑚. sin (𝜔𝑡 −

2𝜋

3

)

𝑠𝑖𝑛𝑐 = 𝑚. sin (𝜔𝑡 +

2𝜋

3

)

(5)

Trong đó: m là chỉ số điều chế (0 ≤ m ≤ 1).

Tín hiệu sau khi được tạo ra sẽ được

chèn trực tiếp vào tất cả các khóa của bộ

nghịch lưu làm ngắn mạch ngõ ra của mạng

Qzs với mục đích nạp năng lượng cho các

cuộn dây tăng áp. Tổng thời gian tồn tại của

tín hiệu ngắn mạch trong một chu kỳ sóng

mang là DT với điều kiện sau:

m + D ≤ 1 (6)

4. HOẠT ĐỘNG CỦA 3L qZST2I DƯỚI

ĐIỀU KIỆN LỖI HỞ MẠCH

Lỗi xảy ra với nghịch lưu 3 bậc hình T

có thể là lỗi ngắn mạch và lỗi hở mạch theo

tài liệu [16] khi lỗi ngắn mạch xảy ra, khóa

ngắn mạch được cách ly và cấu hình nghịch

lưu hoạt động giống như lỗi hở mạch. Vì thế,

trong bài báo này nhóm nghiên cứu chỉ tập

trung trình bày hai sự cố lỗi hở mạch đó là:

lỗi hở mạch khóa S1a hoặc khóa S3a và lỗi hở

mạch khóa S2a. Giải thuật khắc phục sự cố

cho hai lỗi này có thể ứng dụng cho các khóa

khác trong cấu trúc một cách tương tự.

Xét trạng thái lỗi hở mạch khóa S1a

(Hình 4). Khi lỗi xảy ra, điện áp VAO không

thể đạt được giá trị +VPN/2. Do đó, dạng sóng

ngõ ra của dòng điện và điện áp tại pha-A

không đảm bảo được tính đối xứng.

S1a

S2a

S1b

S2b

S3b

S1c

S2c

S3c

O

L2L1

L3L4

Vi

C1

C4

C2

C3

S3a

P

N

G

LcLbLa

RcRbRa

S1af

S3af

S2af

G

Cc

Cb

Ca

S2bf

S2cf

S2x

A

B

C

Hình 4. Cấu hình của 3L qZST2I khi lỗi S1a.

Như đã trình bày ở trên, phương pháp

thay nhánh lỗi bằng nhánh dự phòng có cấu

hình như hình 4. Nhánh dự phòng này bao

gồm một khóa hai chiều và hai khóa một

chiều. Khi S1a xảy ra lỗi, xung điều khiển của

khóa S1af được kích đóng tương tự như xung

điều khiển của khóa S1ađồng thời kích đóng

khóa hai chiều S2a và S2af trong khi đó kích

ngắt các khóa S1a và S3af.

S1a

S2a

S1b

S2b

S3b

S1c

S2c

S3c

O

L2L1

L3L4

Vi

C1

C4

C2

C3

S3a

P

N

G

LcLbLa

RcRbRa

S1af

S3af

S2af

G

Cc

Cb

Ca

S2bf

S2cf

S2x

A

B

C

Hình 5. Cấu hình của 3L qZST2I khi sửa lỗi S1a.

Xét trạng thái lỗi S2a tại pha-A như trình

bày ở hình 6. Dòng điện và điện áp ngõ ra sẽ

không giữ được tính đối xứng như trình bày

ở hình 8. Do lỗi này không thể thay thế bằng

nhánh dự phòng, vì thế giải pháp phải thay

đổi kỹ thuật điều chế là lựa chọn ưu tiên.

Trong thời gian xảy ra lỗi S2a, xung điều

khiển của S1a,3a sẽ được điều chế sao cho

54

Tạp Chí Khoa Học Giáo Dục Kỹ Thuật Số 54 (09/2019)

Trường Đại Học Sư Phạm Kỹ Thuật TP. Hồ Chí Minh

pha-A hoạt động ở điều kiện 2 bậc trong khi

pha-B và pha-C vẫn hoạt động ở điều kiện 3

bậc, đồng thời kích ngắt khóa S2a.

S1a

S2a

S1b

S2b

S3b

S1c

S2c

S3c

O

L2L1

L3L4

Vi

C1

C4

C2

C3

S3a

P

N

G

LcLbLa

RcRbRa

S1af

S3af

S2af

G

Cc

Cb

Ca

S2bf

S2cf

S2x

A

B

C

Hình 6. Cấu hình của 3L qZST2I khi lỗi S2a.

5. KẾT QUẢ MÔ PHỎNG VÀ THỰC

NGHIỆM

5.1 Kết quả mô phỏng

Nhóm nghiên cứu tiến hành mô phỏng

và thực nghiệm để xem khả năng chịu lỗi của

nghịch lưu 3 pha 3 bậc hình T tải RL dưới sự

hỗ trợ của phần mềm PSIM và mô hình thực

tế với các thông số sau:

Bảng 2. Các thông số mô phỏng và thực

nghiệm của bộ nghịch lưu

Thông số các thành phần Giá trị

Điện áp ngõ vào Vdc 80 V

Điện áp ngõ ra Vo 50 V

Tần số ngõ ra fo 50 Hz

Tần số sóng

mang

fs 5 kHz

Tỉ số ngắn mạch D 0.3

Tỉ số điều chế M 0.7

Điện cảm

L1 = L2 =

L3 = L4

1mH/ 20 A

Tụ điện

C1 = C2 =

C3 = C4

2200 F/400 V

Mạch lọc LC Lf và Cf 3 mH và 10 F

Tải trở Rt 40 Ω

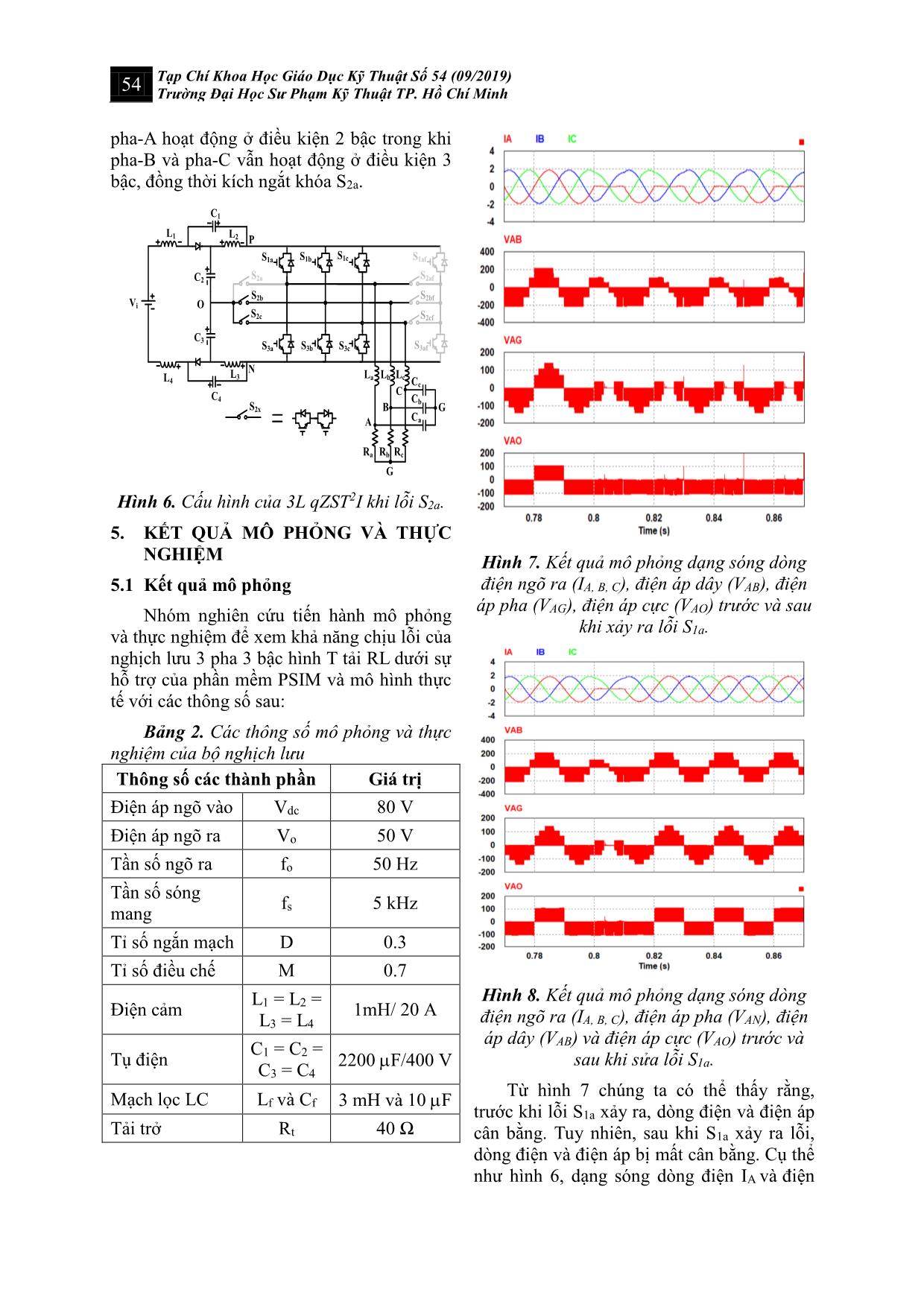

Hình 7. Kết quả mô phỏng dạng sóng dòng

điện ngõ ra (IA, B, C), điện áp dây (VAB), điện

áp pha (VAG), điện áp cực (VAO) trước và sau

khi xảy ra lỗi S1a.

Hình 8. Kết quả mô phỏng dạng sóng dòng

điện ngõ ra (IA, B, C), điện áp pha (VAN), điện

áp dây (VAB) và điện áp cực (VAO) trước và

sau khi sửa lỗi S1a.

Từ hình 7 chúng ta có thể thấy rằng,

trước khi lỗi S1a xảy ra, dòng điện và điện áp

cân bằng. Tuy nhiên, sau khi S1a xảy ra lỗi,

dòng điện và điện áp bị mất cân bằng. Cụ thể

như hình 6, dạng sóng dòng điện IA và điện

Tạp Chí Khoa Học Giáo Dục Kỹ Thuật Số 54 (09/2019)

Trường Đại Học Sư Phạm Kỹ Thuật TP. Hồ Chí Minh

55

áp pha VAG đã mất đi bán kì dương, điện áp

dây mất đi tính đối xứng và điện áp cực VAO

không đạt được giá trị +VPN/2.

Từ hình 8, sau khi sửa lỗi S1a bằng

nhánh dự phòng, dòng tải pha-A (pha lỗi)

phục hồi về trạng thái ban đầu. Biên độ của

các mức điện áp cũng phục hồi sau khi sự cố

xảy ra.

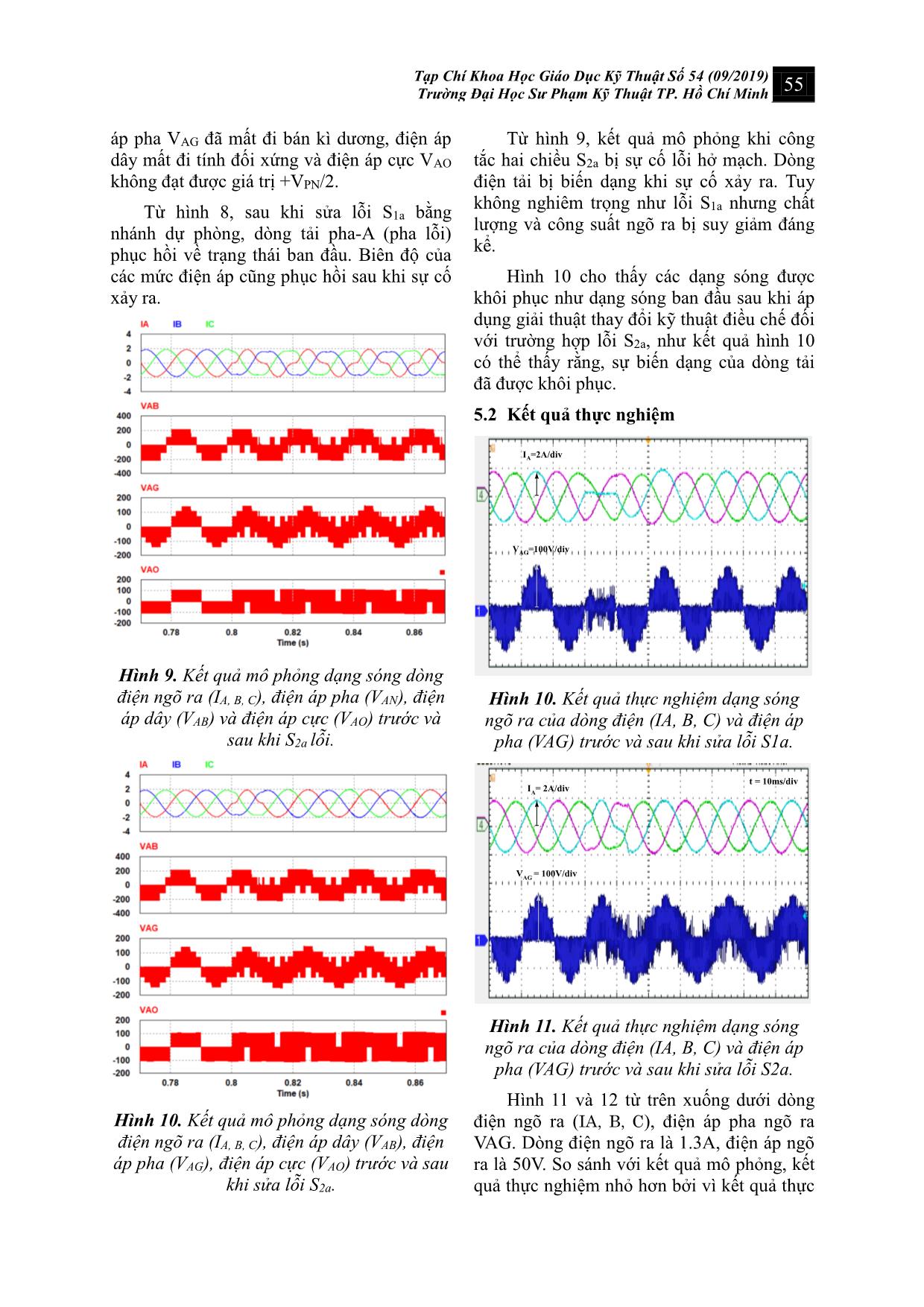

Hình 9. Kết quả mô phỏng dạng sóng dòng

điện ngõ ra (IA, B, C), điện áp pha (VAN), điện

áp dây (VAB) và điện áp cực (VAO) trước và

sau khi S2a lỗi.

Hình 10. Kết quả mô phỏng dạng sóng dòng

điện ngõ ra (IA, B, C), điện áp dây (VAB), điện

áp pha (VAG), điện áp cực (VAO) trước và sau

khi sửa lỗi S2a.

Từ hình 9, kết quả mô phỏng khi công

tắc hai chiều S2a bị sự cố lỗi hở mạch. Dòng

điện tải bị biến dạng khi sự cố xảy ra. Tuy

không nghiêm trọng như lỗi S1a nhưng chất

lượng và công suất ngõ ra bị suy giảm đáng

kể.

Hình 10 cho thấy các dạng sóng được

khôi phục như dạng sóng ban đầu sau khi áp

dụng giải thuật thay đổi kỹ thuật điều chế đối

với trường hợp lỗi S2a, như kết quả hình 10

có thể thấy rằng, sự biến dạng của dòng tải

đã được khôi phục.

5.2 Kết quả thực nghiệm

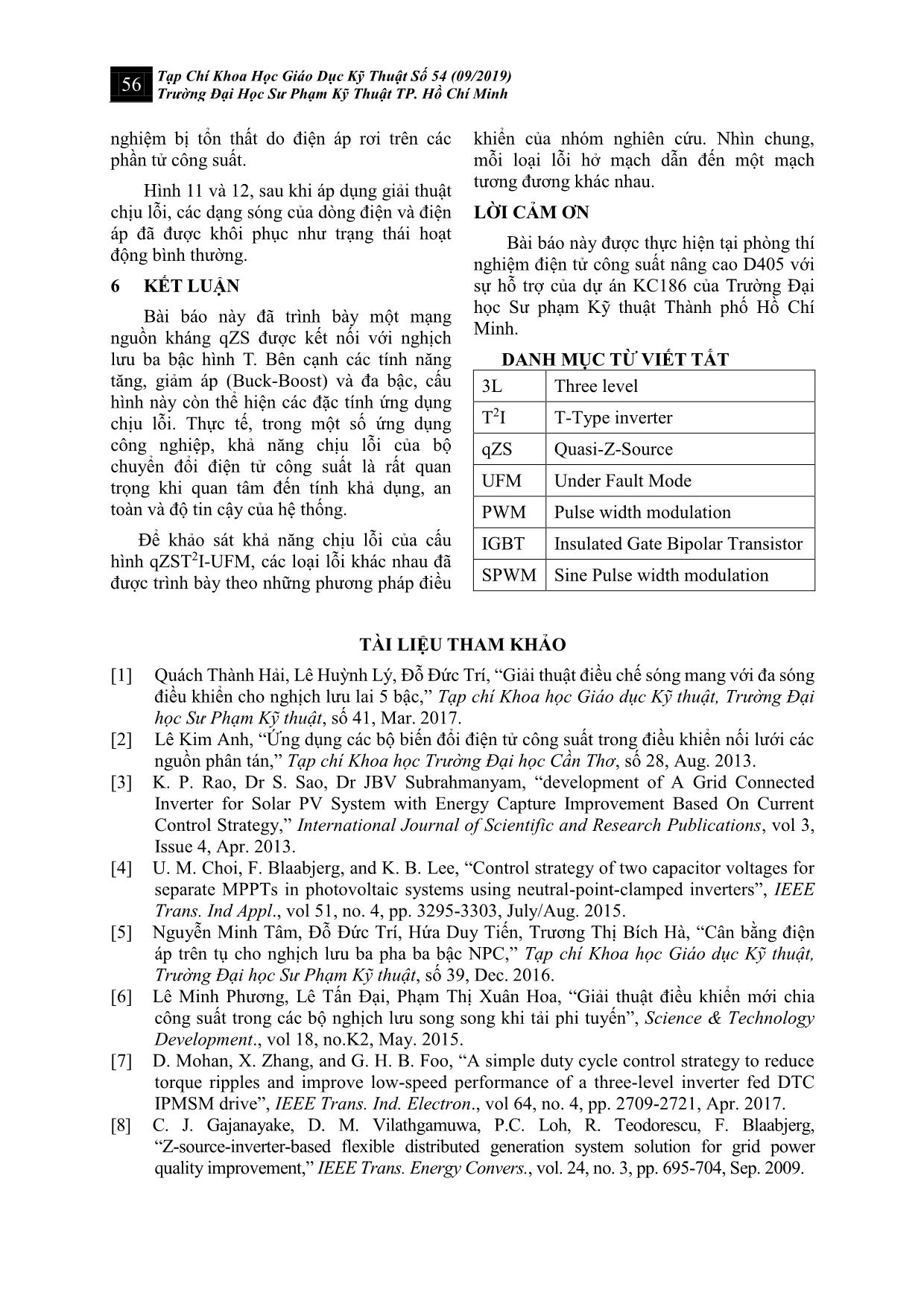

Hình 10. Kết quả thực nghiệm dạng sóng

ngõ ra của dòng điện (IA, B, C) và điện áp

pha (VAG) trước và sau khi sửa lỗi S1a.

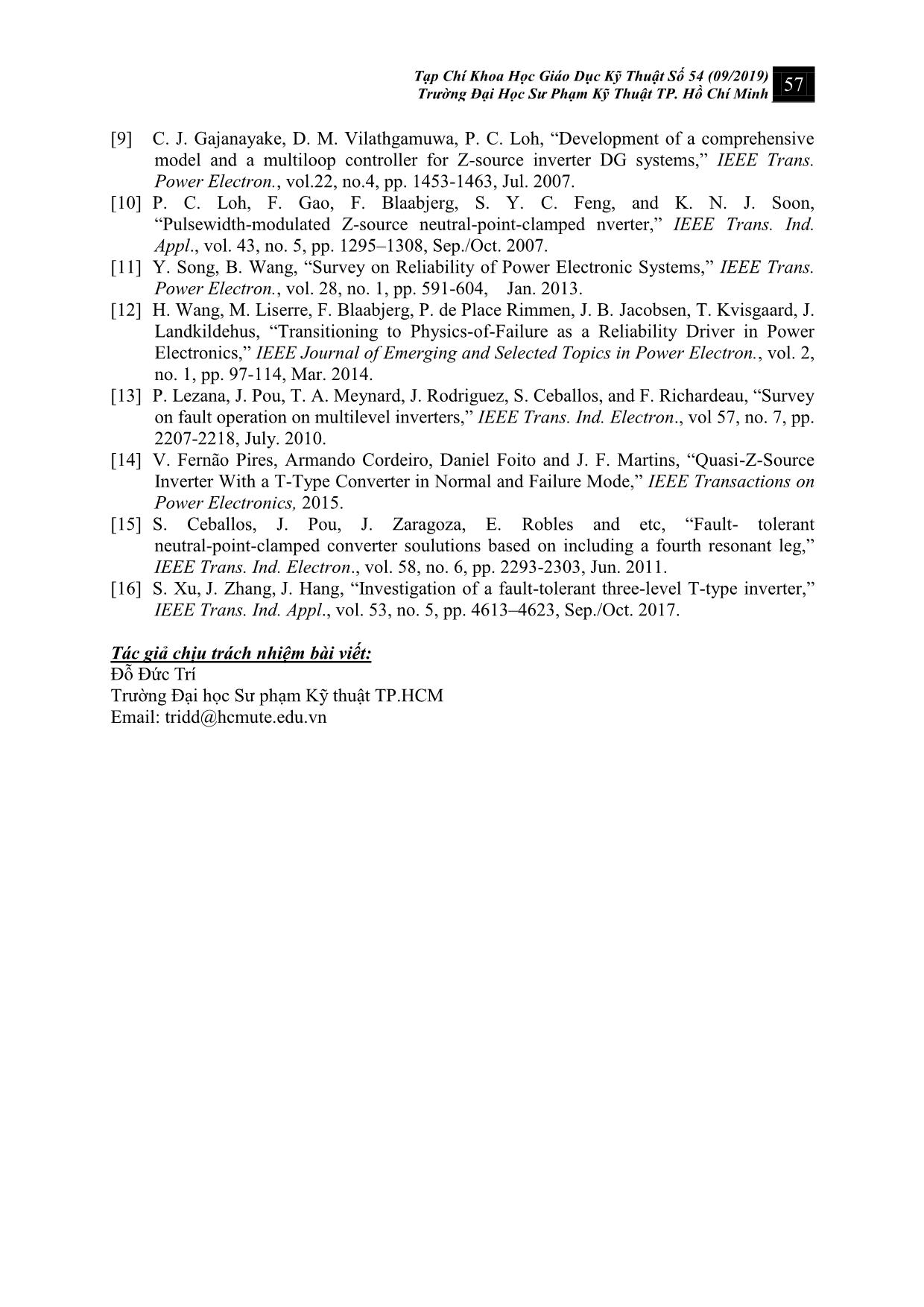

Hình 11. Kết quả thực nghiệm dạng sóng

ngõ ra của dòng điện (IA, B, C) và điện áp

pha (VAG) trước và sau khi sửa lỗi S2a.

Hình 11 và 12 từ trên xuống dưới dòng

điện ngõ ra (IA, B, C), điện áp pha ngõ ra

VAG. Dòng điện ngõ ra là 1.3A, điện áp ngõ

ra là 50V. So sánh với kết quả mô phỏng, kết

quả thực nghiệm nhỏ hơn bởi vì kết quả thực

IA=2A/div

VAG=100V/div

I

A

= 2A/div

V

AG

= 100V/div

t = 10ms/div

56

Tạp Chí Khoa Học Giáo Dục Kỹ Thuật Số 54 (09/2019)

Trường Đại Học Sư Phạm Kỹ Thuật TP. Hồ Chí Minh

nghiệm bị tổn thất do điện áp rơi trên các

phần tử công suất.

Hình 11 và 12, sau khi áp dụng giải thuật

chịu lỗi, các dạng sóng của dòng điện và điện

áp đã được khôi phục như trạng thái hoạt

động bình thường.

6 KẾT LUẬN

Bài báo này đã trình bày một mạng

nguồn kháng qZS được kết nối với nghịch

lưu ba bậc hình T. Bên cạnh các tính năng

tăng, giảm áp (Buck-Boost) và đa bậc, cấu

hình này còn thể hiện các đặc tính ứng dụng

chịu lỗi. Thực tế, trong một số ứng dụng

công nghiệp, khả năng chịu lỗi của bộ

chuyển đổi điện tử công suất là rất quan

trọng khi quan tâm đến tính khả dụng, an

toàn và độ tin cậy của hệ thống.

Để khảo sát khả năng chịu lỗi của cấu

hình qZST2I-UFM, các loại lỗi khác nhau đã

được trình bày theo những phương pháp điều

khiển của nhóm nghiên cứu. Nhìn chung,

mỗi loại lỗi hở mạch dẫn đến một mạch

tương đương khác nhau.

LỜI CẢM ƠN

Bài báo này được thực hiện tại phòng thí

nghiệm điện tử công suất nâng cao D405 với

sự hỗ trợ của dự án KC186 của Trường Đại

học Sư phạm Kỹ thuật Thành phố Hồ Chí

Minh.

DANH MỤC TỪ VIẾT TẮT

3L Three level

T2I T-Type inverter

qZS Quasi-Z-Source

UFM Under Fault Mode

PWM Pulse width modulation

IGBT Insulated Gate Bipolar Transistor

SPWM Sine Pulse width modulation

TÀI LIỆU THAM KHẢO

[1] Quách Thành Hải, Lê Huỳnh Lý, Đỗ Đức Trí, “Giải thuật điều chế sóng mang với đa sóng

điều khiển cho nghịch lưu lai 5 bậc,” Tạp chí Khoa học Giáo dục Kỹ thuật, Trường Đại

học Sư Phạm Kỹ thuật, số 41, Mar. 2017.

[2] Lê Kim Anh, “Ứng dụng các bộ biến đổi điện tử công suất trong điều khiển nối lưới các

nguồn phân tán,” Tạp chí Khoa học Trường Đại học Cần Thơ, số 28, Aug. 2013.

[3] K. P. Rao, Dr S. Sao, Dr JBV Subrahmanyam, “development of A Grid Connected

Inverter for Solar PV System with Energy Capture Improvement Based On Current

Control Strategy,” International Journal of Scientific and Research Publications, vol 3,

Issue 4, Apr. 2013.

[4] U. M. Choi, F. Blaabjerg, and K. B. Lee, “Control strategy of two capacitor voltages for

separate MPPTs in photovoltaic systems using neutral-point-clamped inverters”, IEEE

Trans. Ind Appl., vol 51, no. 4, pp. 3295-3303, July/Aug. 2015.

[5] Nguyễn Minh Tâm, Đỗ Đức Trí, Hứa Duy Tiến, Trương Thị Bích Hà, “Cân bằng điện

áp trên tụ cho nghịch lưu ba pha ba bậc NPC,” Tạp chí Khoa học Giáo dục Kỹ thuật,

Trường Đại học Sư Phạm Kỹ thuật, số 39, Dec. 2016.

[6] Lê Minh Phương, Lê Tấn Đại, Phạm Thị Xuân Hoa, “Giải thuật điều khiển mới chia

công suất trong các bộ nghịch lưu song song khi tải phi tuyến”, Science & Technology

Development., vol 18, no.K2, May. 2015.

[7] D. Mohan, X. Zhang, and G. H. B. Foo, “A simple duty cycle control strategy to reduce

torque ripples and improve low-speed performance of a three-level inverter fed DTC

IPMSM drive”, IEEE Trans. Ind. Electron., vol 64, no. 4, pp. 2709-2721, Apr. 2017.

[8] C. J. Gajanayake, D. M. Vilathgamuwa, P.C. Loh, R. Teodorescu, F. Blaabjerg,

“Z-source-inverter-based flexible distributed generation system solution for grid power

quality improvement,” IEEE Trans. Energy Convers., vol. 24, no. 3, pp. 695-704, Sep. 2009.

Tạp Chí Khoa Học Giáo Dục Kỹ Thuật Số 54 (09/2019)

Trường Đại Học Sư Phạm Kỹ Thuật TP. Hồ Chí Minh

57

[9] C. J. Gajanayake, D. M. Vilathgamuwa, P. C. Loh, “Development of a comprehensive

model and a multiloop controller for Z-source inverter DG systems,” IEEE Trans.

Power Electron., vol.22, no.4, pp. 1453-1463, Jul. 2007.

[10] P. C. Loh, F. Gao, F. Blaabjerg, S. Y. C. Feng, and K. N. J. Soon,

“Pulsewidth-modulated Z-source neutral-point-clamped nverter,” IEEE Trans. Ind.

Appl., vol. 43, no. 5, pp. 1295–1308, Sep./Oct. 2007.

[11] Y. Song, B. Wang, “Survey on Reliability of Power Electronic Systems,” IEEE Trans.

Power Electron., vol. 28, no. 1, pp. 591-604, Jan. 2013.

[12] H. Wang, M. Liserre, F. Blaabjerg, P. de Place Rimmen, J. B. Jacobsen, T. Kvisgaard, J.

Landkildehus, “Transitioning to Physics-of-Failure as a Reliability Driver in Power

Electronics,” IEEE Journal of Emerging and Selected Topics in Power Electron., vol. 2,

no. 1, pp. 97-114, Mar. 2014.

[13] P. Lezana, J. Pou, T. A. Meynard, J. Rodriguez, S. Ceballos, and F. Richardeau, “Survey

on fault operation on multilevel inverters,” IEEE Trans. Ind. Electron., vol 57, no. 7, pp.

2207-2218, July. 2010.

[14] V. Fernão Pires, Armando Cordeiro, Daniel Foito and J. F. Martins, “Quasi-Z-Source

Inverter With a T-Type Converter in Normal and Failure Mode,” IEEE Transactions on

Power Electronics, 2015.

[15] S. Ceballos, J. Pou, J. Zaragoza, E. Robles and etc, “Fault- tolerant

neutral-point-clamped converter soulutions based on including a fourth resonant leg,”

IEEE Trans. Ind. Electron., vol. 58, no. 6, pp. 2293-2303, Jun. 2011.

[16] S. Xu, J. Zhang, J. Hang, “Investigation of a fault-tolerant three-level T-type inverter,”

IEEE Trans. Ind. Appl., vol. 53, no. 5, pp. 4613–4623, Sep./Oct. 2017.

Tác giả chịu trách nhiệm bài viết:

Đỗ Đức Trí

Trường Đại học Sư phạm Kỹ thuật TP.HCM

Email: tridd@hcmute.edu.vn

File đính kèm:

nghich_luu_3_bac_hinh_t_voi_kha_nang_chiu_loi.pdf

nghich_luu_3_bac_hinh_t_voi_kha_nang_chiu_loi.pdf