Giáo trình môn Điện tử số (Phần 2)

MẠCH CHỐT (LATCH) VÀ FLIP-FLOP (FF)

Latch (chốt): là mạch tuần tự mà nó liên tục xem xét các ngõ vào và làm thay đổi các ngõ ra

bất cứ thời điểm nào không phụ thuộc vào xung clock.

Flip-Flop: là mạch tuần tự mà nó thường lấy mẫu các ngõ vào và làm thay đổi các ngõ ra tại

những thời điểm xác định bởi xung clock.

Flip Flop (FF)

Trạng thái kế tiếp của ngõ ra FF sẽ thay đổi theo ngõ vào và trạng thái trước đó của ngõ ra tại

thời điểm thay đổi của xung clock (cạnh lên hoặc cạnh xuống)

- Bảng đặc tính và phương trình đặc tính: Biểu diễn mối quan hệ của ngõ ra kế tiếp Q+

phụ thuộc vào các ngõ vào và trạng thái ngõ ra hiện tại Q.

- Bảng kích thích: biểu diễn giá trị của các ngõ vào cần phải có khi ta cần ngõ ra chuyển

từ trạng thái hiện tại Q sang trạng thái kế tiếp Q+

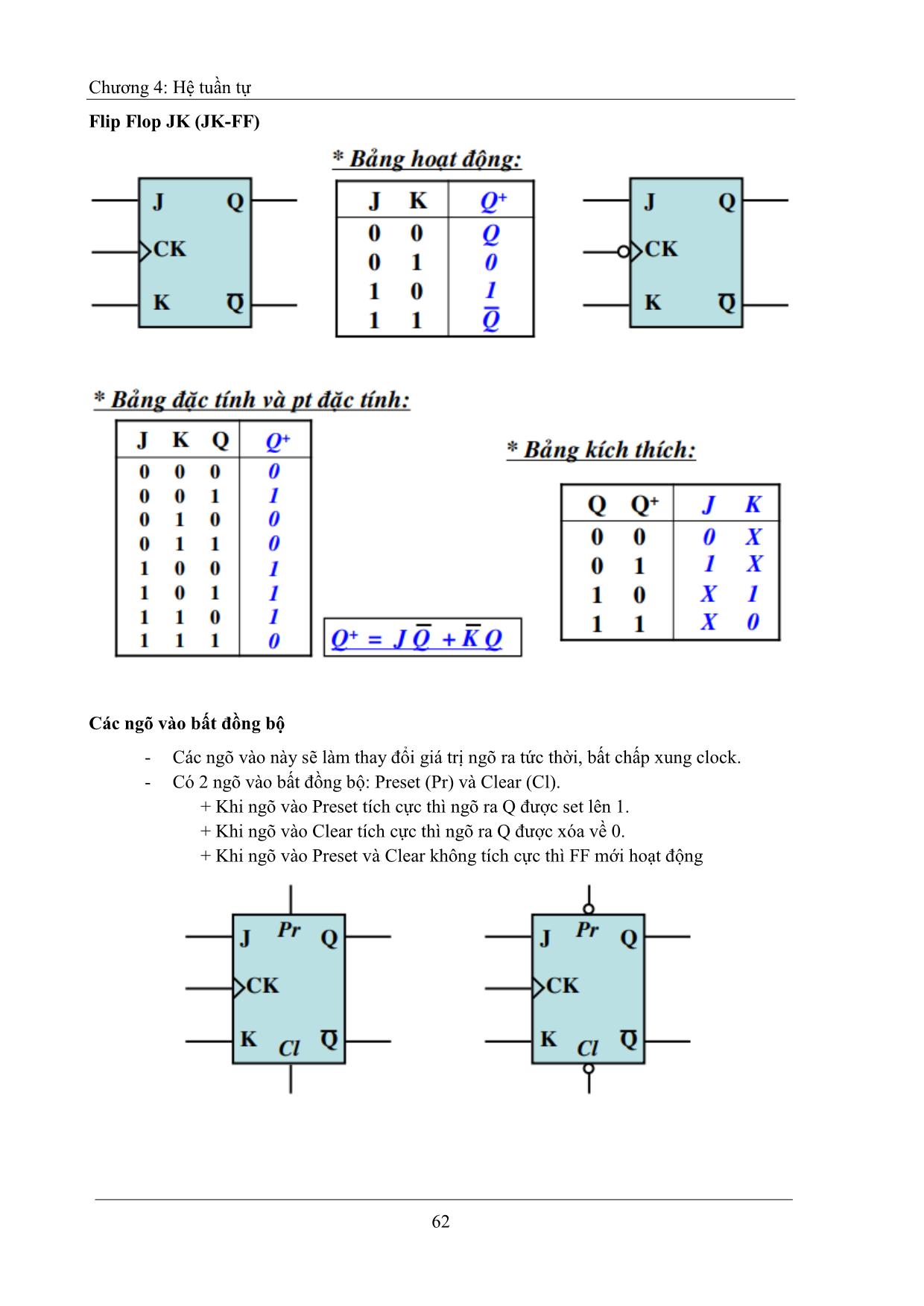

Các ngõ vào bất đồng bộ

- Các ngõ vào này sẽ làm thay đổi giá trị ngõ ra tức thời, bất chấp xung clock.

- Có 2 ngõ vào bất đồng bộ: Preset (Pr) và Clear (Cl).

+ Khi ngõ vào Preset tích cực thì ngõ ra Q được set lên 1.

+ Khi ngõ vào Clear tích cực thì ngõ ra Q được xóa về 0.

+ Khi ngõ vào Preset và Clear không tích cực thì FF mới hoạt động

Trang 1

Trang 2

Trang 3

Trang 4

Trang 5

Trang 6

Trang 7

Trang 8

Trang 9

Trang 10

Tải về để xem bản đầy đủ

Tóm tắt nội dung tài liệu: Giáo trình môn Điện tử số (Phần 2)

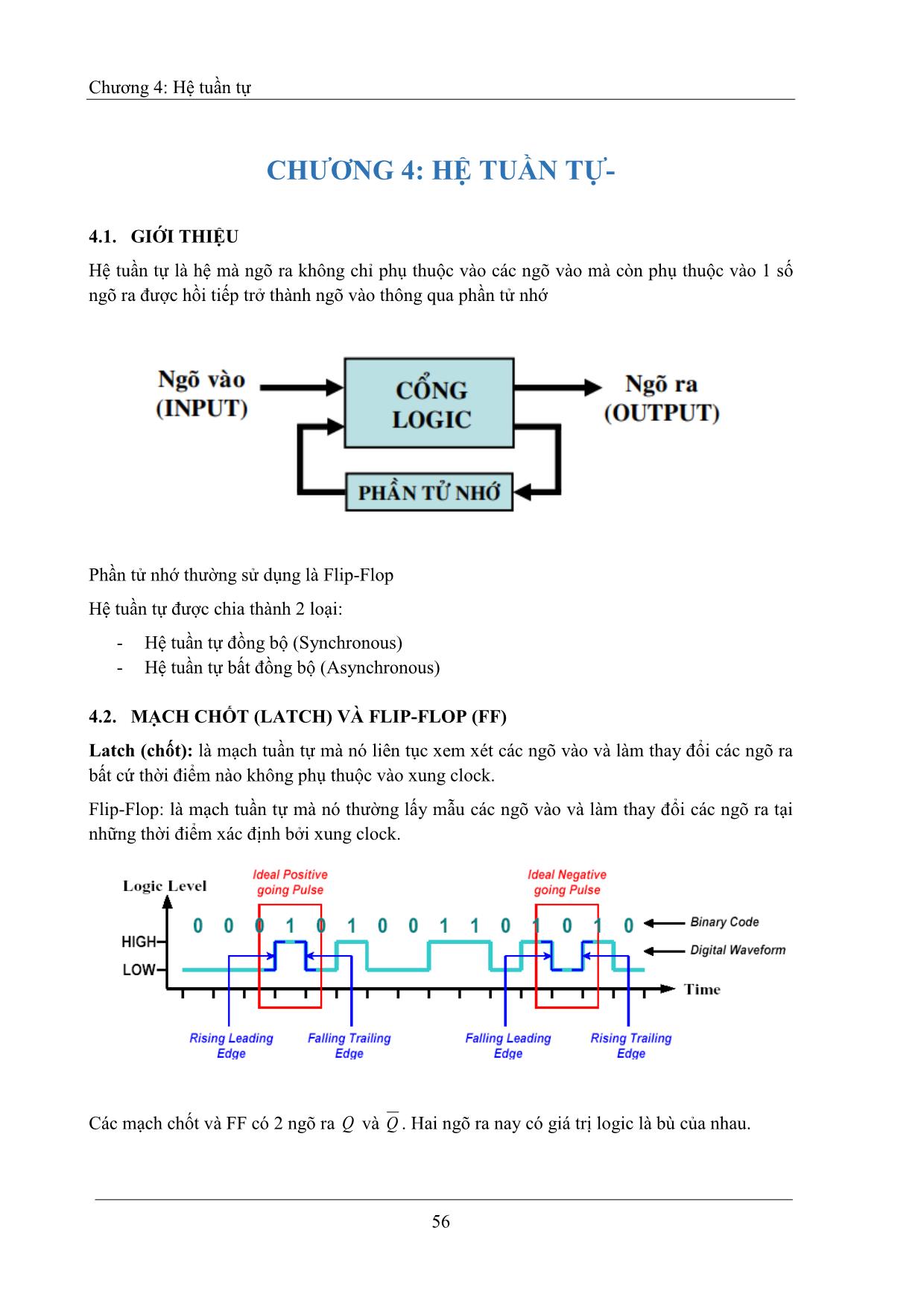

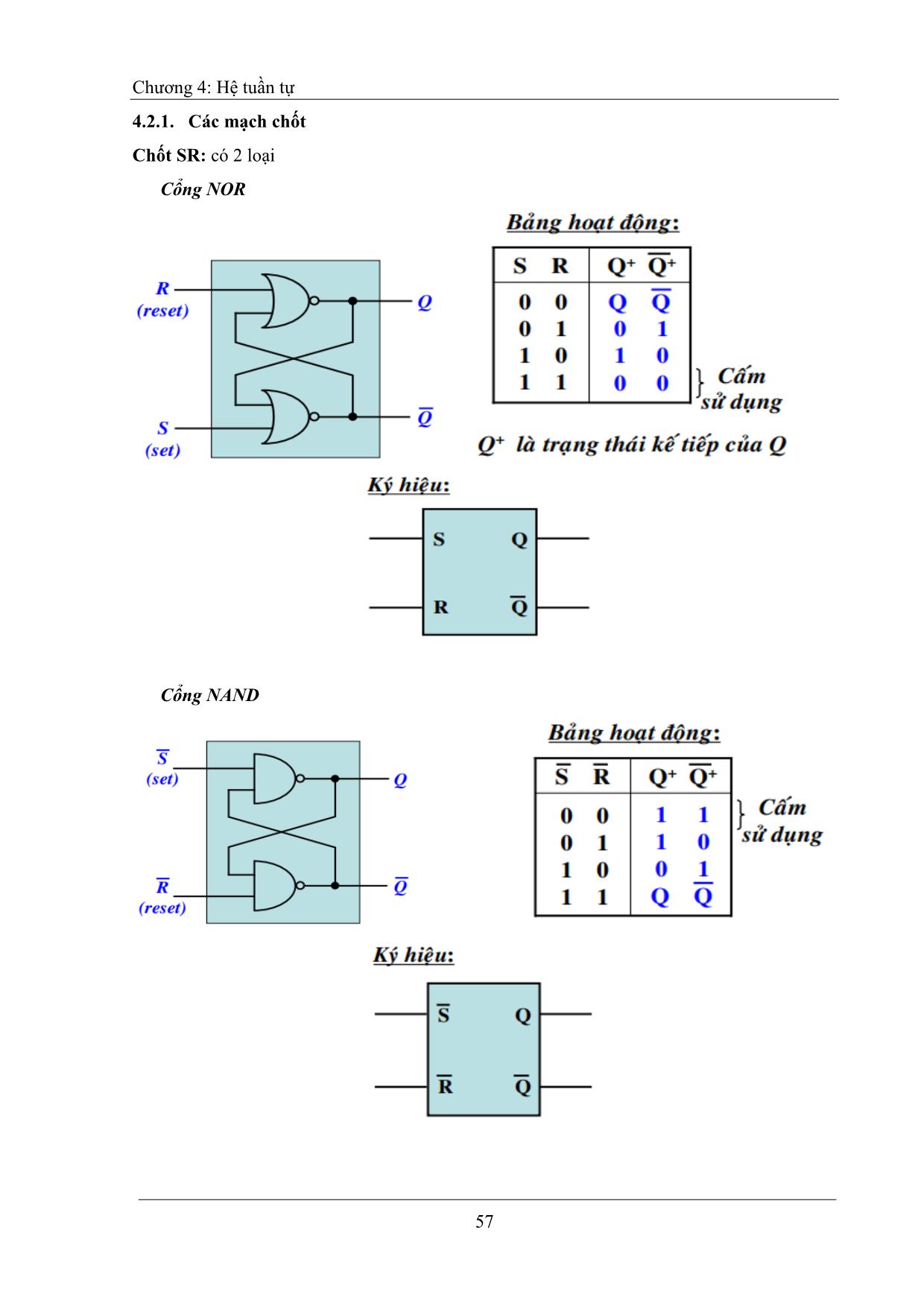

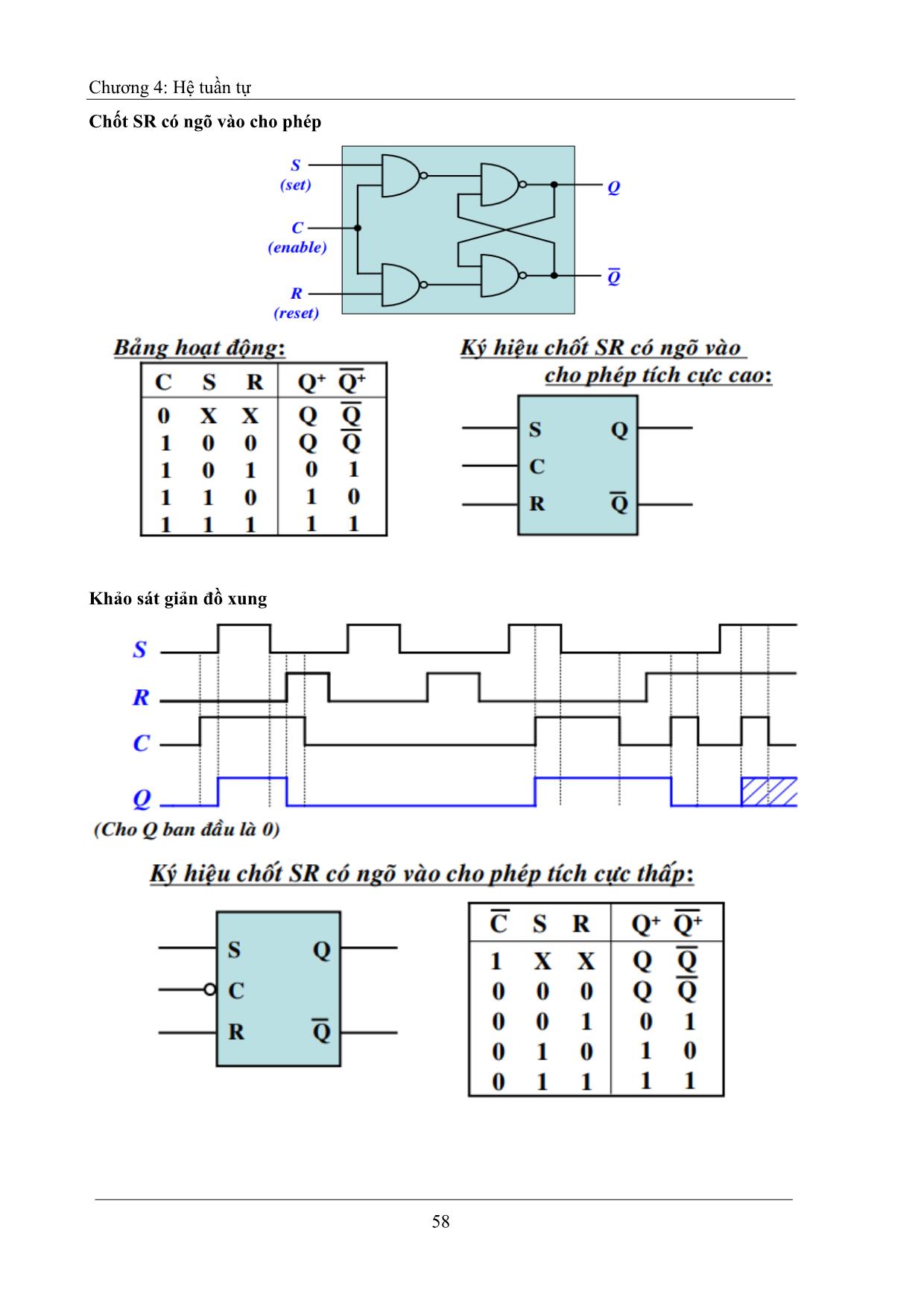

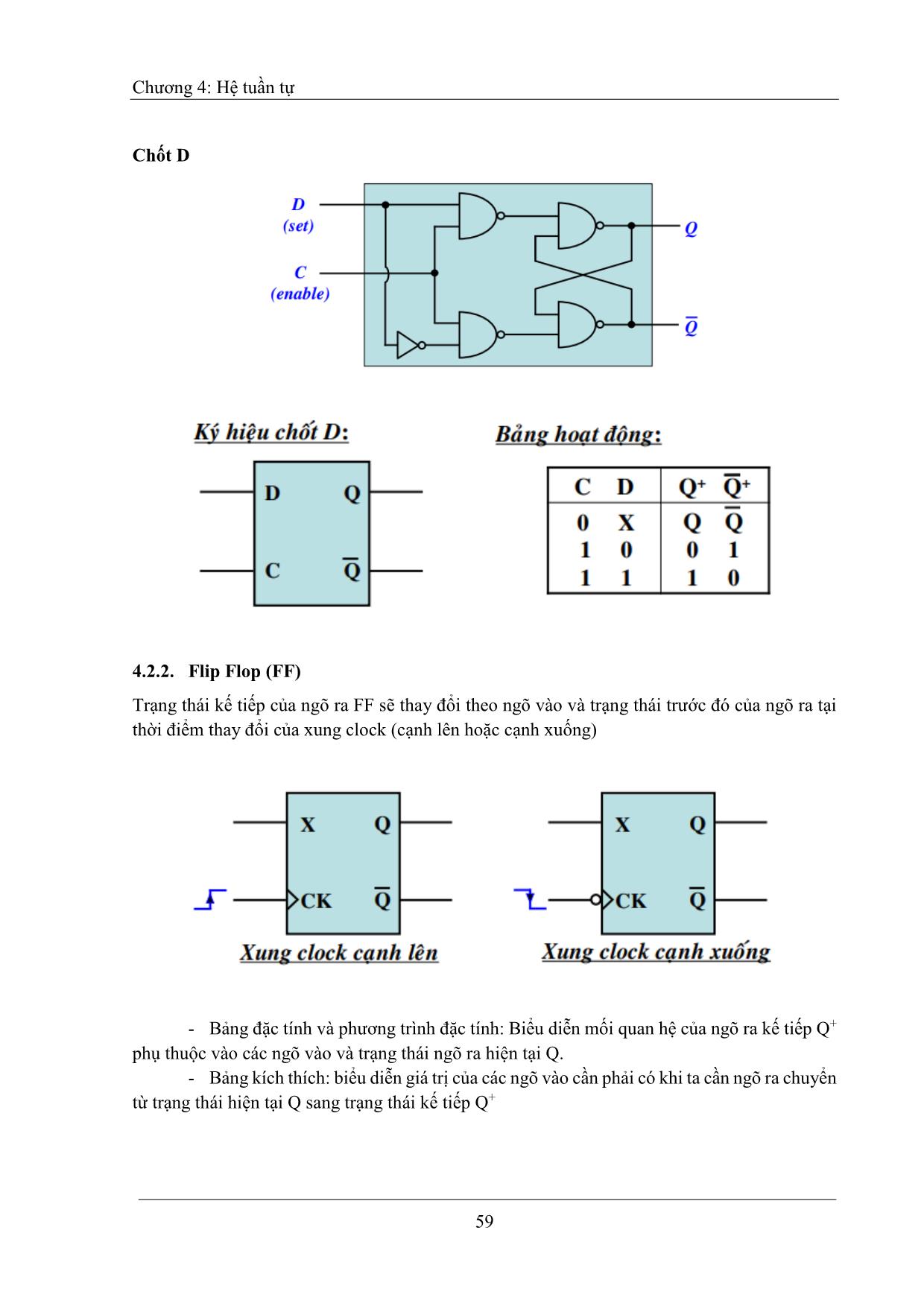

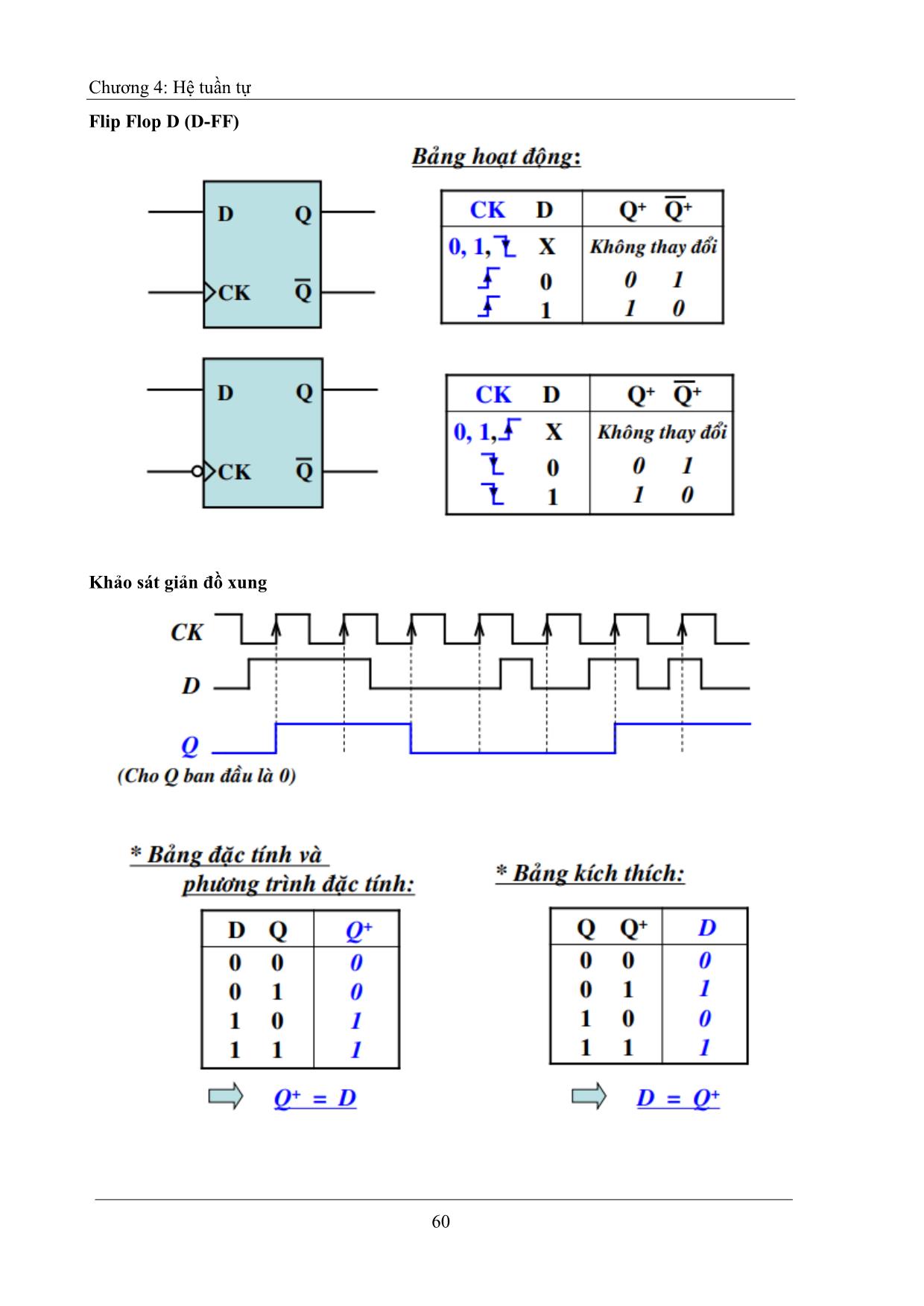

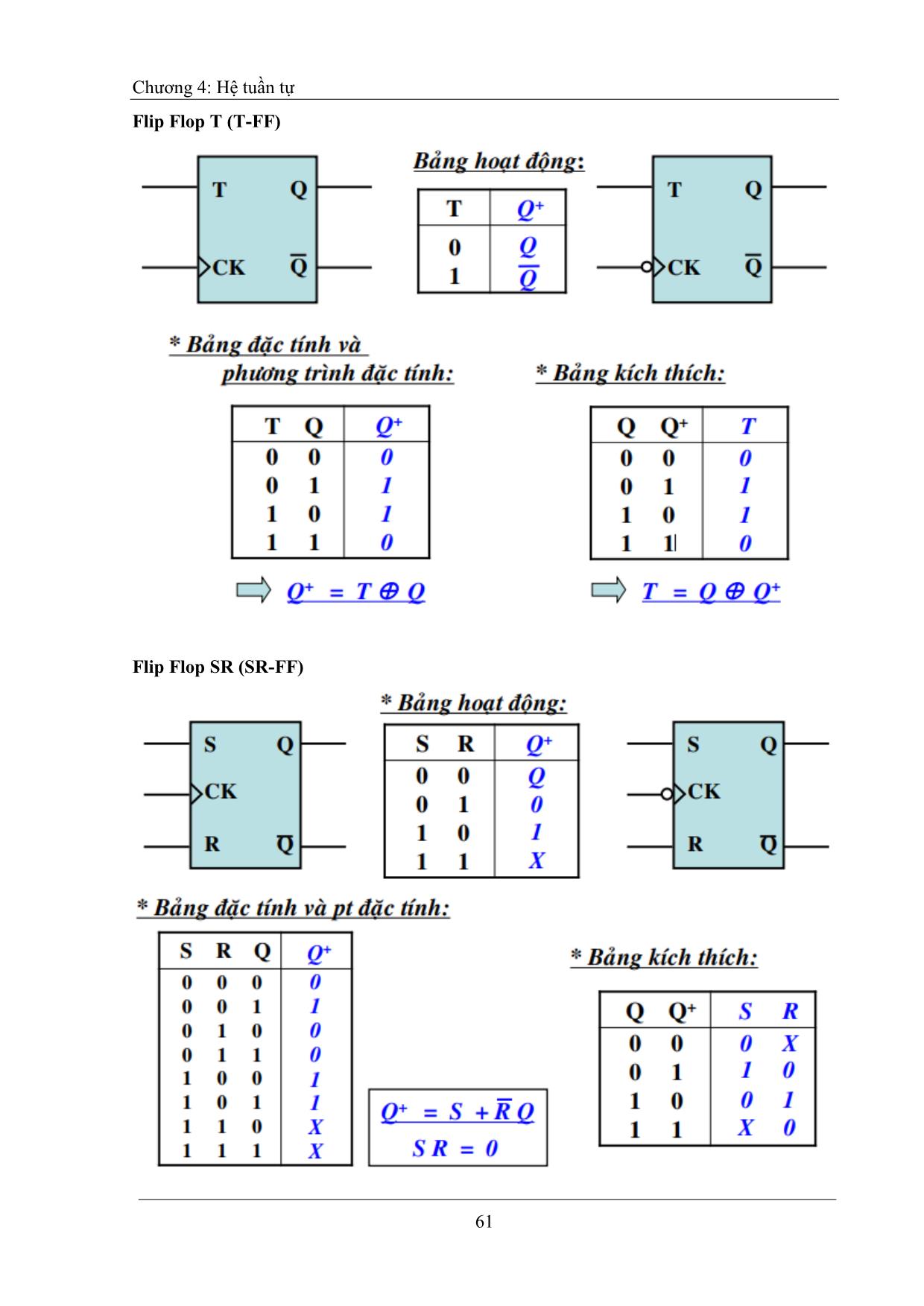

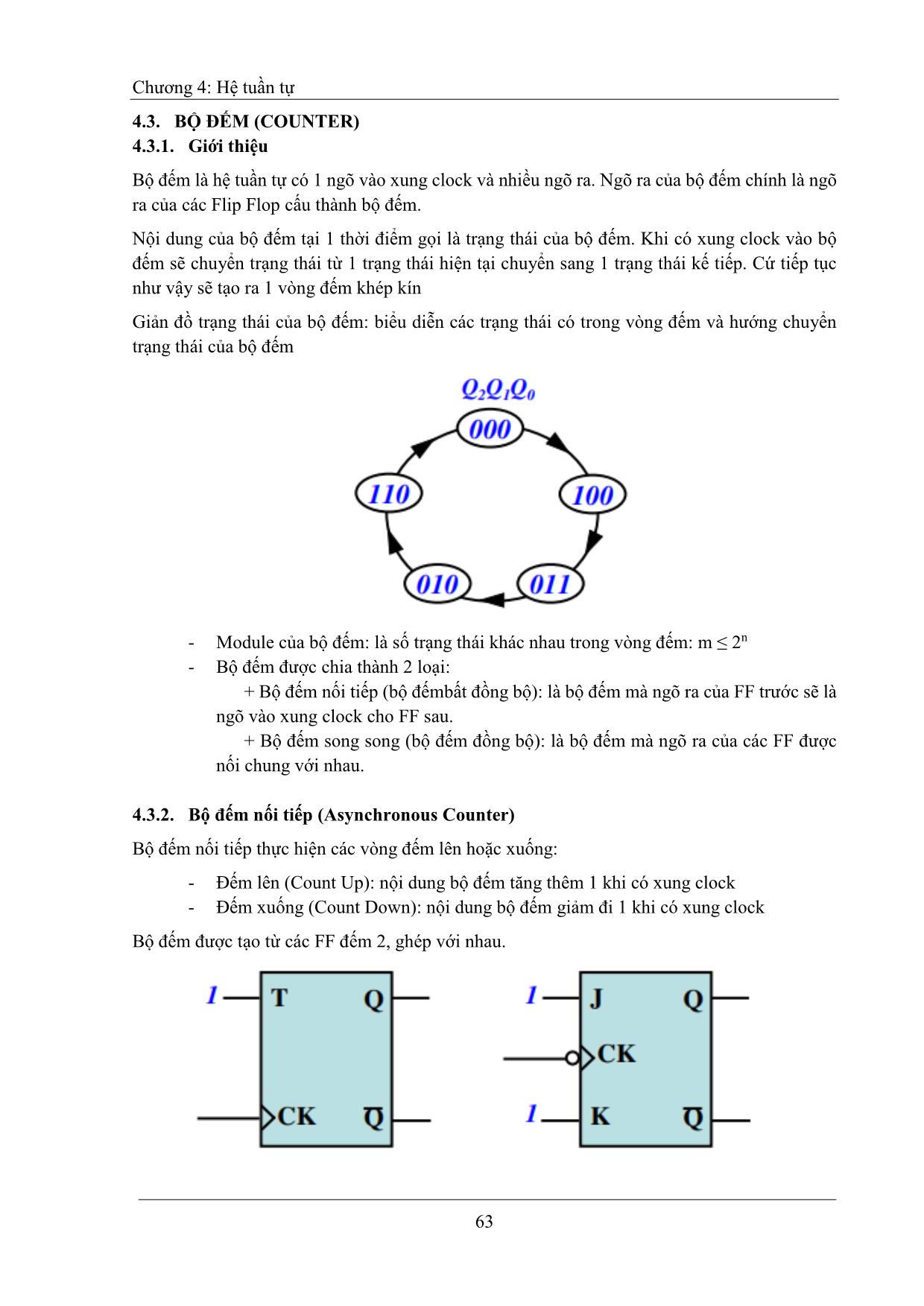

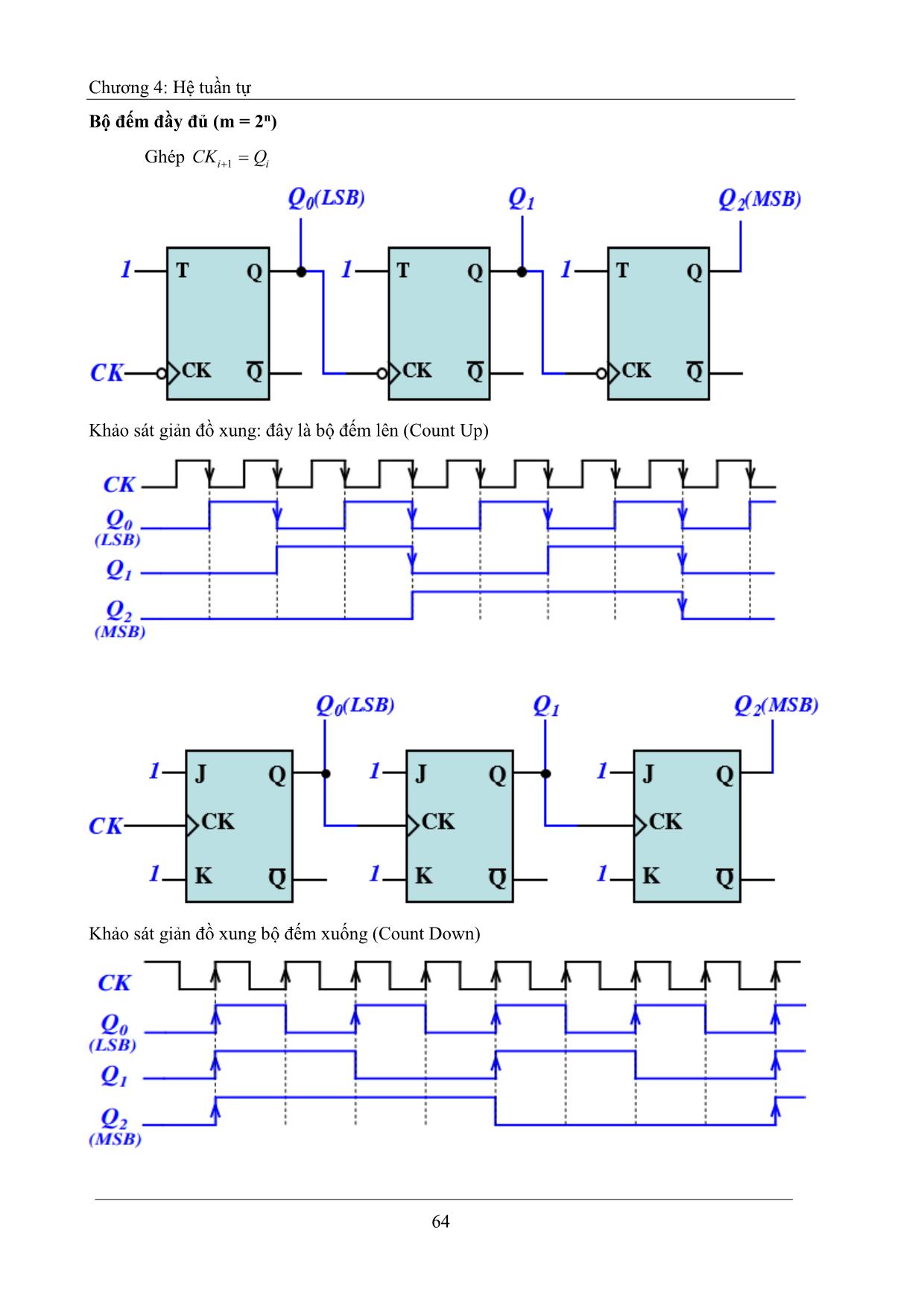

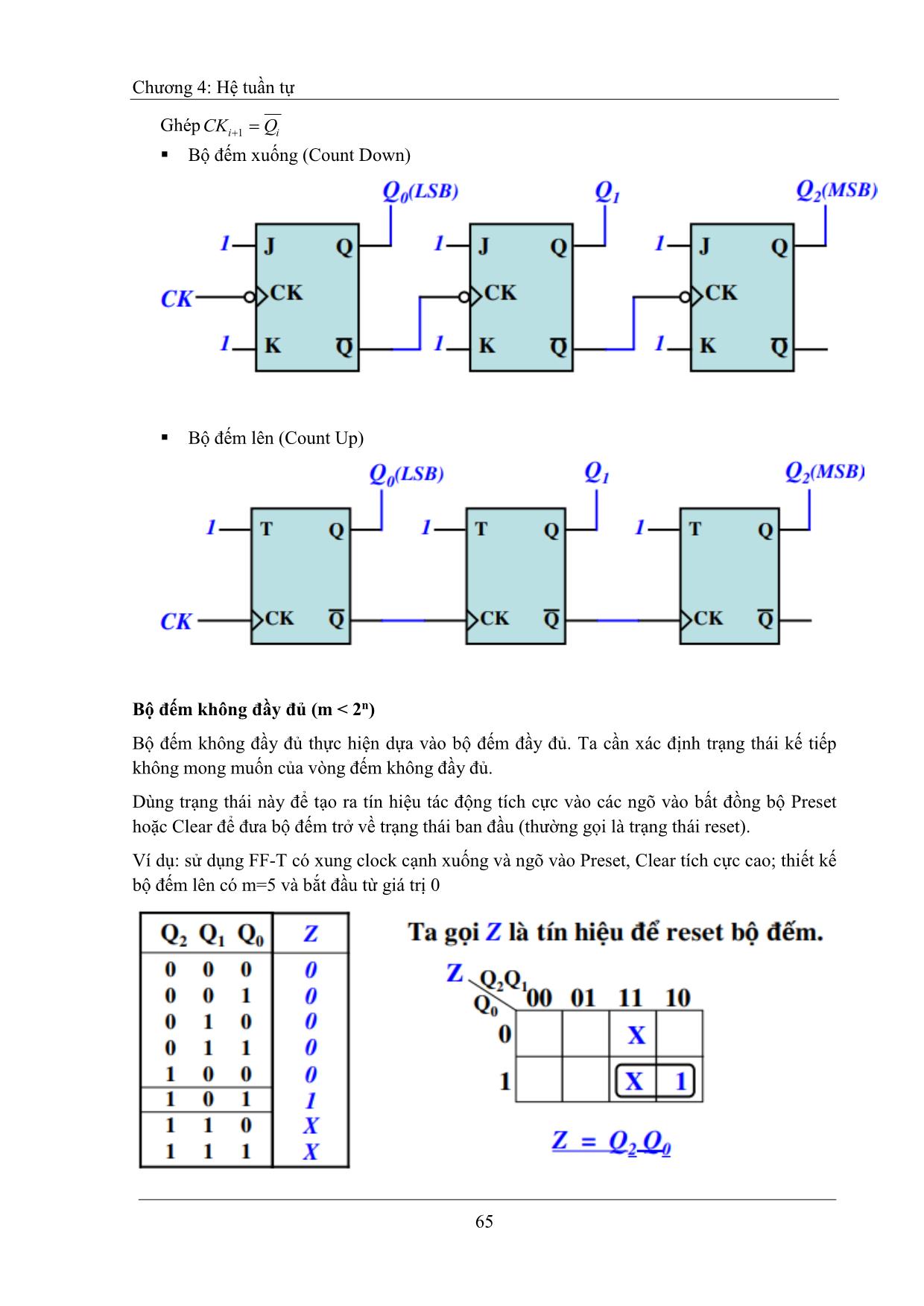

Chương 4: Hệ tuần tự 56 CHƯƠNG 4: HỆ TUẦN TỰ- 4.1. GIỚI THIỆU Hệ tuần tự là hệ mà ngõ ra không chỉ phụ thuộc vào các ngõ vào mà còn phụ thuộc vào 1 số ngõ ra được hồi tiếp trở thành ngõ vào thông qua phần tử nhớ Phần tử nhớ thường sử dụng là Flip-Flop Hệ tuần tự được chia thành 2 loại: - Hệ tuần tự đồng bộ (Synchronous) - Hệ tuần tự bất đồng bộ (Asynchronous) 4.2. MẠCH CHỐT (LATCH) VÀ FLIP-FLOP (FF) Latch (chốt): là mạch tuần tự mà nó liên tục xem xét các ngõ vào và làm thay đổi các ngõ ra bất cứ thời điểm nào không phụ thuộc vào xung clock. Flip-Flop: là mạch tuần tự mà nó thường lấy mẫu các ngõ vào và làm thay đổi các ngõ ra tại những thời điểm xác định bởi xung clock. Các mạch chốt và FF có 2 ngõ ra Q và Q . Hai ngõ ra nay có giá trị logic là bù của nhau. Chương 4: Hệ tuần tự 57 4.2.1. Các mạch chốt Chốt SR: có 2 loại Cổng NOR Cổng NAND Chương 4: Hệ tuần tự 58 Chốt SR có ngõ vào cho phép Khảo sát giản đồ xung Chương 4: Hệ tuần tự 59 Chốt D 4.2.2. Flip Flop (FF) Trạng thái kế tiếp của ngõ ra FF sẽ thay đổi theo ngõ vào và trạng thái trước đó của ngõ ra tại thời điểm thay đổi của xung clock (cạnh lên hoặc cạnh xuống) - Bảng đặc tính và phương trình đặc tính: Biểu diễn mối quan hệ của ngõ ra kế tiếp Q+ phụ thuộc vào các ngõ vào và trạng thái ngõ ra hiện tại Q. - Bảng kích thích: biểu diễn giá trị của các ngõ vào cần phải có khi ta cần ngõ ra chuyển từ trạng thái hiện tại Q sang trạng thái kế tiếp Q+ Chương 4: Hệ tuần tự 60 Flip Flop D (D-FF) Khảo sát giản đồ xung Chương 4: Hệ tuần tự 61 Flip Flop T (T-FF) Flip Flop SR (SR-FF) Chương 4: Hệ tuần tự 62 Flip Flop JK (JK-FF) Các ngõ vào bất đồng bộ - Các ngõ vào này sẽ làm thay đổi giá trị ngõ ra tức thời, bất chấp xung clock. - Có 2 ngõ vào bất đồng bộ: Preset (Pr) và Clear (Cl). + Khi ngõ vào Preset tích cực thì ngõ ra Q được set lên 1. + Khi ngõ vào Clear tích cực thì ngõ ra Q được xóa về 0. + Khi ngõ vào Preset và Clear không tích cực thì FF mới hoạt động Chương 4: Hệ tuần tự 63 4.3. BỘ ĐẾM (COUNTER) 4.3.1. Giới thiệu Bộ đếm là hệ tuần tự có 1 ngõ vào xung clock và nhiều ngõ ra. Ngõ ra của bộ đếm chính là ngõ ra của các Flip Flop cấu thành bộ đếm. Nội dung của bộ đếm tại 1 thời điểm gọi là trạng thái của bộ đếm. Khi có xung clock vào bộ đếm sẽ chuyển trạng thái từ 1 trạng thái hiện tại chuyển sang 1 trạng thái kế tiếp. Cứ tiếp tục như vậy sẽ tạo ra 1 vòng đếm khép kín Giản đồ trạng thái của bộ đếm: biểu diễn các trạng thái có trong vòng đếm và hướng chuyển trạng thái của bộ đếm - Module của bộ đếm: là số trạng thái khác nhau trong vòng đếm: m ≤ 2n - Bộ đếm được chia thành 2 loại: + Bộ đếm nối tiếp (bộ đếmbất đồng bộ): là bộ đếm mà ngõ ra của FF trước sẽ là ngõ vào xung clock cho FF sau. + Bộ đếm song song (bộ đếm đồng bộ): là bộ đếm mà ngõ ra của các FF được nối chung với nhau. 4.3.2. Bộ đếm nối tiếp (Asynchronous Counter) Bộ đếm nối tiếp thực hiện các vòng đếm lên hoặc xuống: - Đếm lên (Count Up): nội dung bộ đếm tăng thêm 1 khi có xung clock - Đếm xuống (Count Down): nội dung bộ đếm giảm đi 1 khi có xung clock Bộ đếm được tạo từ các FF đếm 2, ghép với nhau. Chương 4: Hệ tuần tự 64 Bộ đếm đầy đủ (m = 2n) Ghép 1i iCK Q+ = Khảo sát giản đồ xung: đây là bộ đếm lên (Count Up) Khảo sát giản đồ xung bộ đếm xuống (Count Down) Chương 4: Hệ tuần tự 65 Ghép 1i iCK Q+ = ▪ Bộ đếm xuống (Count Down) ▪ Bộ đếm lên (Count Up) Bộ đếm không đầy đủ (m < 2n) Bộ đếm không đầy đủ thực hiện dựa vào bộ đếm đầy đủ. Ta cần xác định trạng thái kế tiếp không mong muốn của vòng đếm không đầy đủ. Dùng trạng thái này để tạo ra tín hiệu tác động tích cực vào các ngõ vào bất đồng bộ Preset hoặc Clear để đưa bộ đếm trở về trạng thái ban đầu (thường gọi là trạng thái reset). Ví dụ: sử dụng FF-T có xung clock cạnh xuống và ngõ vào Preset, Clear tích cực cao; thiết kế bộ đếm lên có m=5 và bắt đầu từ giá trị 0 Chương 4: Hệ tuần tự 66 Khảo sát giản đồ xung Ví dụ: Sử dụng JK-FF có xung clock cạnh xuống và ngõ vào Pr, Cl tích cực thấp; thiết kế bộ đếm xuống có m=5 và bắt đầu từ giá trị 2. Tín hiệu reset: 2 1Z Q Q= (tích cực thấp) Chương 4: Hệ tuần tự 67 IC 74393: 2 bộ đếm lên đầy đủ 4 bit Chương 4: Hệ tuần tự 68 IC 7490: gồm 2 bộ đếm – bộ đếm 2 và bộ đếm 5 (đếm lên) 4.3.3. Bộ đếm song song (Synchronous Counter) ˗ Là bộ đếm mà các FF đều sử dụng chung nguồn xung clock; khi có xung clock vào thì tất cả các ngõ ra FF đều thay đổi ˗ Khi thiết kế bộ đếm, chỉ quan tâm đến trạng thái hiện tại và trạng thái kế tiếp của FF mà không quan tâm đến dạng xung clock (cạnh lên hoặc cạnh xuống) ˗ Có thể thiết kế bộ đếm có vòng đếm bất kỳ Bảng hàm kích thích Chương 4: Hệ tuần tự 69 Các bước thiết kế: ˗ Từ phát biểu bài toán xác định số FF sử dụng và dãy đếm. ˗ Lập bảng chuyển trạng thái chỉ rõ mối quan hệ giữa trạng thái hiện tại và trạng thái kế tiếp (dựa vào dãy đếm). ˗ Tìm các giá trị ngõ vào FF cần phải có từ giá trị hiện tại Qi và kế tiếp iQ + của từng FF (dựa vào bảng kích thích của FF). ˗ Tìm biểu thức rút gọn của mỗi ngõ vào FF phụ thuộc vào các biến trạng thái hiện tại. ˗ Thực hiện sơ đồ logic. Bộ đếm đầy đủ (m = 2n) Ví dụ: Sử dụng T-FF kích theo cạnh lên, thiết kế bộ đếm có dãy đếm sau: Q2Q1Q0: 010, 101, 110, 001, 000, 111, 100, 011, 010, Chương 4: Hệ tuần tự 70 Bộ đếm không đầy đủ (m < 2n) Các trạng thái có trong vòng đếm sẽ thiết kế như bộ đếm đầy đủ; còn các trạng thái dư không có trong vòng đếm sẽ giải quyết theo 2 cách sau: Cách 1: Các trạng thái dư có trạng thái kế tiếp là tùy định. Khi thiết kế cần khởi động giá trị ban đầu cho bộ đếm; giá trị này phải là 1 trong những trạng thái có trong vòng đếm. Ví dụ: Thiết kế bộ đếm dùng D-FF cạnh lên, có ngõ vào Pr và Cl tích cực cao, có giản đồ trạng thái như sau: Chương 4: Hệ tuần tự 71 Cách 2: Cho các trạng thái dư không có vòng đếm có trạng thái kế tiếp là 1 trong những trạng thái có trong vòng đếm Chương 4: Hệ tuần tự 72 Phân tích bộ đếm song song: - Từ sơ đồ logic của bộ đếm xác định hàm kích thích (biểu thức của các ngõ vào của từng FF phụ thuộc vào các ngõ ra Qi). - Lập bảng trạng thái: từ trạng thái hiện tại Qi và giá trị ngõ vào ta xác định được trạng thái kế tiếp của FF iQ + - Từ bảng chuyển trạng thái xác định được giản đồ trạng thái hoặc khảo sát giản đồ xung của bộ đếm. Chương 4: Hệ tuần tự 73 IC 74193: bộ đếm lên / xuống đồng bộ 4 bit Chương 4: Hệ tuần tự 74 4.4. THANH GHI DỊCH (SHIFT REGISTER) Thanh ghi dịch là hệ tuần tự có khả năng lưu trữ và dịch chuyển dữ liệu 4.4.1. Thanh ghi dịch nhập nối tiếp – xuất nối tiếp (SISO) Chương 4: Hệ tuần tự 75 4.4.2. Thanh ghi dịch nhập nối tiếp – xuất song song (SIPO) 4.4.3. Thanh ghi dịch nhập song song – xuất nối tiếp (PISO) Chương 4: Hệ tuần tự 76 4.4.4. Thanh ghi dịch nhập song song – xuất song song (PIPO) IC 74164: SIPO – Thanh ghi dịch nối tiếp thành song song Chương 4: Hệ tuần tự 77 Chương 4: Hệ tuần tự 78 IC 74165: PISO – Thanh ghi dịch song song thành nối tiếp Chương 4: Hệ tuần tự 79 4.5. BỘ ĐẾM THANH GHI DỊCH (SHIFT REGISTER COUNTER) 4.5.1. Bộ đếm vòng (Ring Counter) 4.5.2. Bộ đếm vòng xoắn (Twisted-ring Counter): bộ đếm Johnson Chương 4: Hệ tuần tự 80 4.6. PHÂN TÍCH HỆ TUẦN TỰ Hệ tuần tự được chia thành 2 loại tùy thuộc vào tính chất của ngõ ra. 4.6.1. Kiểu MEALY Trạng thái kế tiếp = F (trạng thái hiện tại Qi và các ngõ vào Xj) Giá trị ngõ ra = G (trạng thái hiện tại Qi và các ngõ vào Xj) Chương 4: Hệ tuần tự 81 Giản đồ trạng thái (state graph) Chương 4: Hệ tuần tự 82 4.6.2. Kiểu MOORE Trạng thái kế tiếp = F (trạng thái hiện tại Qi và các ngõ vào Xj) Giá trị ngõ ra = G (trạng thái hiện tại Qi và các ngõ vào Xj) Chương 4: Hệ tuần tự 83 4.7. THIẾT KẾ HỆ TUẦN TỰ Các bước thiết kê: - Từ phát biểu bài toán thành lập graph trạng thái hoặc bảng trạng thái - Rút gọn trạng thái - Gán trạng thái - Chọn FF (D-FF, T-FF, JK-FF) và thiết kế phần tổ hợp để tạo ra ngõ ra và trạng thái kế (cổng logic, ROM, PLA, PAL). 4.7.1. Thành lập graph trạng thái hoặc bảng chuyển trạng thái Ví dụ: Một hệ tuần tự có 1 ngõ vào X và 1 ngõ ra Z. Ngõ ra sẽ là 1 nếu ngõ vào nhận được chuỗi vào liên tiếp 101. Kiểu MEALY Chương 4: Hệ tuần tự 84 Kiểu MOORE 4.7.2. Rút gọn trạng thái - Với m trạng thái ta sử dụng n FF: 2n-1 < m ≤ 2n - Trạng thái tương đương Hai trạng thái tương đương là 2 trạng thái mà khi cùng giá trị vào mà chúng có các giá trị ra giống nhau và các trạng thái kế tiếp mà chúng chuyển tới tương đương nhau. Ví dụ: Rút gọn bảng trạng thái sau Bảng rút gọn Chương 4: Hệ tuần tự 85 Phương pháp rút gọn bằng bảng kéo theo (Implicaiton Table) - Thành lập bảng kéo theo của bảng có n trạng thái: có n-1 cột và n-1 hàng. Mỗi ô vuông là cặp trạng thái cần xét tương đương. - Từ bảng trạng thái tìm các trạng thái có ngõ ra giống nhau lập thành nhóm có thể tương đương. - Tại mỗi ô vuông của 2 trạng thái không cùng nhóm thì sẽ không tương đương => gạch chéo ô vuông. - Tại mỗi ô vuông của 2 trạng thái cùng nhóm thì ta ghi điều kiện trạng thái kế tiếp cần xét tương đương. - Kiểm tra các điều kiện trong các ô vuông: gạch chéo các ô không thỏa điều kiện. Các ô còn lại không bị gạch chéo là kết quả tương đương. Chương 4: Hệ tuần tự 86 4.7.3. Gán trạng thái Mỗi trạng thái được gán bằng 1 tổ hợp các biến trạng thái Ví dụ: Hệ có 3 trạng thái A, B, C Ta cần 2 biến trạng thái Q1 và Q2 để gán cho 3 trạng thái 4.7.4. Chọn FF và thiết kế phần tổ hợp - Lập bảng trạng thái - Chọn FF (D-FF, T-FF, JK-FF) và mạch tổ hợp (cổng logic, ROM, PLA, ) Ví dụ: Thực hiện hệ tuần tự sau Chương 4: Hệ tuần tự 87 Thực hiện bằng ROM và T-FF kích cạnh lên Chương 4: Hệ tuần tự 88 Thực hiên bằng cổng logic và JK-FF kích cạnh xuống Từ bảng trạng thái, rút gọn Thực hiện bằng PLA và JK-FF kích cạnh lên Chương 4: Hệ tuần tự 89 Ví dụ: thiết kế bộ (chuyển) đổi mã từ BCD sang BCD quá 3. Ngõ vào và ra là nối tiếp với LSB đi trước. Chương 4: Hệ tuần tự 90 Bảng trạng thái rút gọn của bộ chuyển đổi mã Chương 4: Hệ tuần tự 91 Chương 4: Hệ tuần tự 92 4.8. LƯU ĐỒ MÁY TRẠNG THÁI - Hệ tuần tự còn được gọi là máy trạng thái thuật toán (ASM – algorithmic state machine) hay đơn giản hơn là máy trạng thái (SM- state machine), gọi tắt là SM. - Lưu đồ SM được tạo bởi các khối SM; mỗi khối SM mô tả hoạt động của hệ trong 1 trạng thái. - Một khối SM bao gồm 1 hộp trạng thái (state box), các hộp quyết định (decision box) và các hộp xuất theo điều kiện (condition box) - Chương 4: Hệ tuần tự 93 Một khối SM có chính xác 1 đường vào và 1 hoặc nhiều đường ra - Một đường dẫn đi qua khối SM từ ngõ vào đến ngõ ra được gọi là đường dẫn liên kết (link path). Chương 4: Hệ tuần tự 94 - Khối SM có thể được biểu diễn bằng nhiều dạng khác nhau - Một lưu đồ SM có thể biểu diễn một hệ tổ hợp khi chỉ có 1 trạng thái và không có sự thay đổi trạng thái xảy ra Chương 4: Hệ tuần tự 95 - Ta phải tuân theo một số qui tắc khi xây dựng 1 khối SM ▪ Với mọi kết hợp các biến vào hợp lệ phải có chính xác 1 đường ra được định nghĩa. Điều này là cần thiết vì mỗi tổ hợp vào được cho phép phải dẫn đến 1 trạng thái kế duy nhất. ▪ Không cho phép có đường hồi tiếp nội trong 1 khối SM Chương 4: Hệ tuần tự 96 Cài đặt lưu đồ máy trạng thái - Việc cài đặt lưu đồ SM là tìm được phương trình của các biến ra và biến trạng thái kế tiếp. - Các bước thực hiện như sau: Chương 4: Hệ tuần tự 97 ▪ Thực hiện gán trạng thái cho các hộp trạng thái ▪ Xác định phương trình của biến ra Zi • Tìm các trạng thái có xuất hiện biến ra (Zi=1) • Nếu là biến MOORE thì ta được tích số (AND) của các biến trạng thái; còn nếu là biến MEALY thì ta có tích số của các biến trạng thái và biến điều kiện vào. • Phương trình của biến ra bằng tổng (OR) các tích số đã tìm thấy ở các bước trên lại với nhau. Gán trạng thái ▪ Xác định phương trình các biến trạng thái kế tiếp iQ + • Tìm tất cả các trạng thái trong đó Qj = 1 • Tại mỗi trạng thái này, tìm tất cả các đường dẫn liên kết (link path) mà dẫn vào trạng thái đó • Với mỗi đường dẫn liên kết này, tìm ra một số hạng là 1 khi đi theo đường dẫn liên kết này. Nghĩa là, với đường dẫn liên kết từ Sa đến Sb, số hạng sẽ là 1 tích số của các biến trạng thái ở trạng thái Sa và các biến điều kiện để có thể dẫn đến Sb. • Biểu thức iQ + được tạo thành bằng cách lấy tổng (OR) các tích số được tìm thấy ở bước trên lại với nhau. Chương 4: Hệ tuần tự 98 BÀI TẬP CHƯƠNG 4

File đính kèm:

giao_trinh_mon_dien_tu_so_phan_2.pdf

giao_trinh_mon_dien_tu_so_phan_2.pdf