Giáo trình môn Điện tử số (Phần 1)

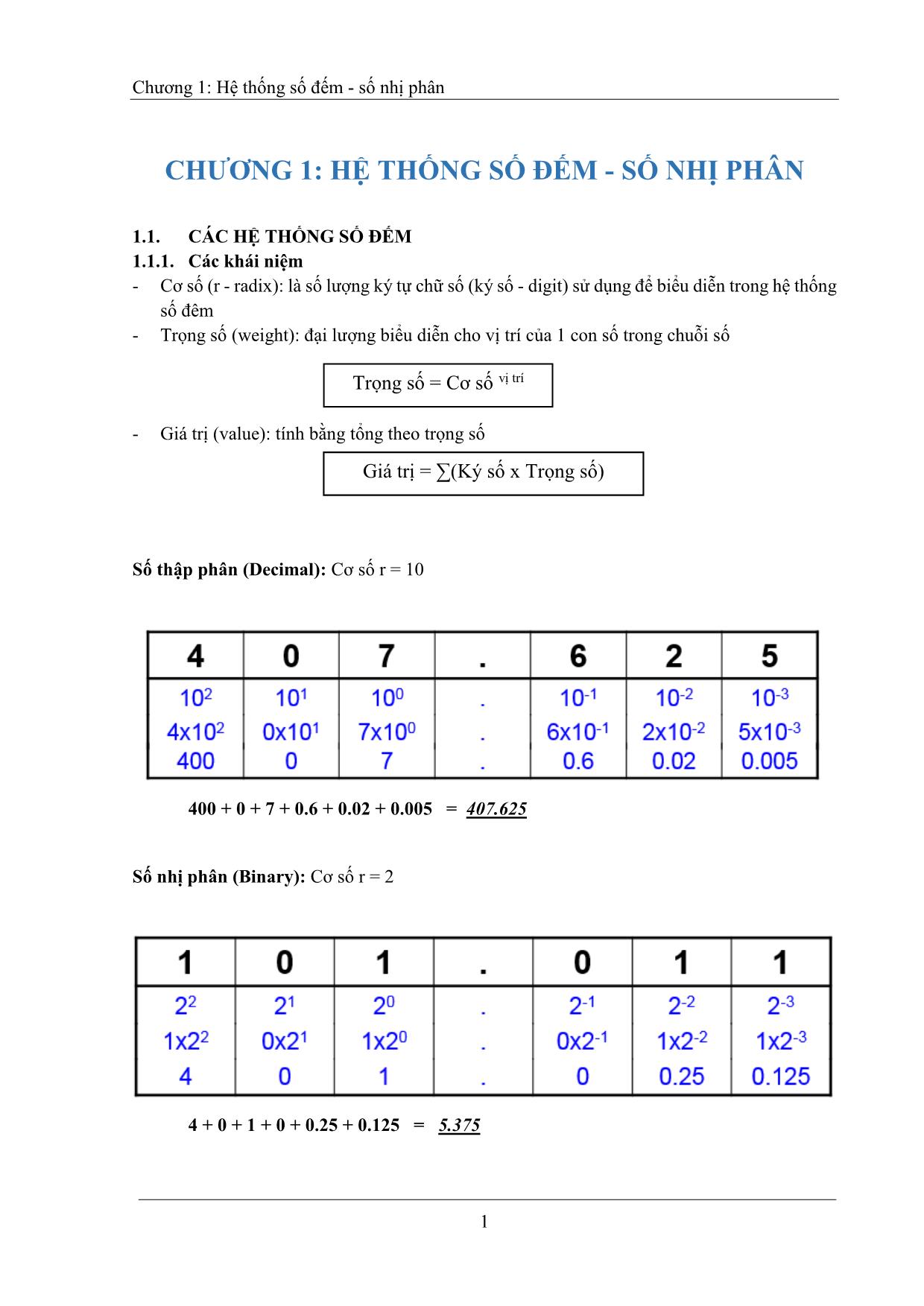

SỐ NHỊ PHÂN (BINARY)

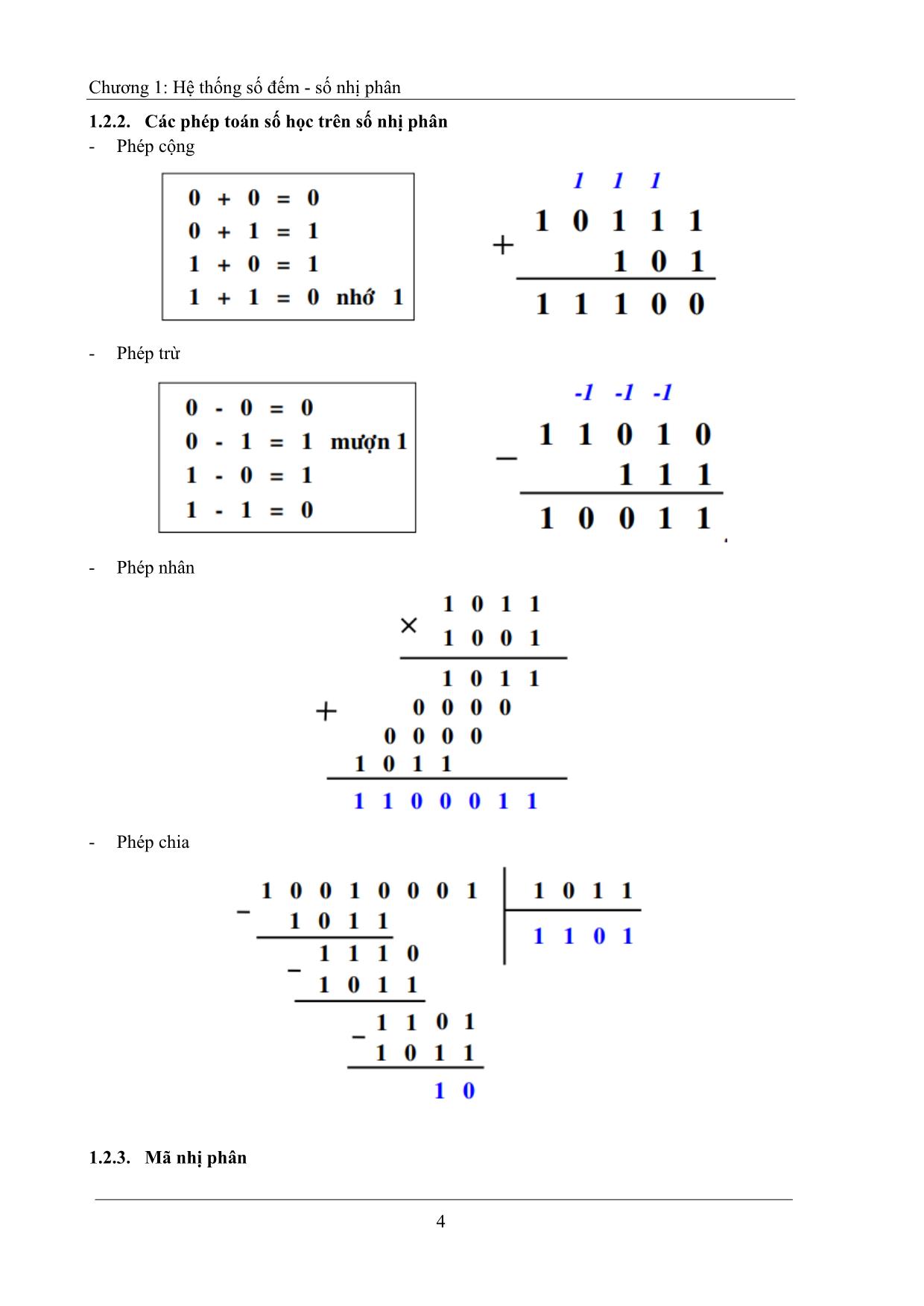

1.2.1. Các tính chất của số nhị phân

- Số nhị phân n bit có 2n giá trị từ 0 đến 2n – 1

- Số nhị phân có giá trị 2n – 1: 1 1(n bit 1)

và giá trị 2n: 10 0(n bit 0)

- Số nhị phân có giá trị lẻ là số có LSB =1; ngược lại giá trị chẵn là số có LSB = 0

- Các bội số của bit:

1B (Byte) = 8 bit

1 KB = 210 B = 1024 B

1 MB = 210 KB = 220 B

1 GB = 210 MB

Trang 1

Trang 2

Trang 3

Trang 4

Trang 5

Trang 6

Trang 7

Trang 8

Trang 9

Trang 10

Tải về để xem bản đầy đủ

Bạn đang xem 10 trang mẫu của tài liệu "Giáo trình môn Điện tử số (Phần 1)", để tải tài liệu gốc về máy hãy click vào nút Download ở trên

Tóm tắt nội dung tài liệu: Giáo trình môn Điện tử số (Phần 1)

được định nghĩa là:

rn – N với N ≠ 0

0 với N = 0

Ví dụ:

˗ Bù 10 của 321D là 103 – 321D = 1000D – 321D = 679D.

˗ Bù 2 của 10101B là 25 – 10101B = 100000B – 10101B =01011B.

˗ Bù 16 của 2CH là 162 – 2CH = 100H – 2CH = D4H

Nhận xét

Bù cơ số của một số được suy ra từ bù cơ số trừ 1 bằng cách cộng thêm 1.

Chương 1: Hệ thống số đếm - số nhị phân

11

1.4. CỘNG TRỪ SỐ BCD

Cn là bit nhớ tạo ra từ decade cao nhất, Ci là số nhớ tạo ra từ decade thứ i

Chương 1: Hệ thống số đếm - số nhị phân

12

Chương 1: Hệ thống số đếm - số nhị phân

13

Trạng thái logic của tín hiệu số (digital signal):

Giản đồ xung (Waveform) của tín hiệu số:

BÀI TẬP CHƯƠNG 1

Chương 2: Đại số Boole - cổng logic

14

CHƯƠNG 2: ĐẠI SỐ BOOLE - CỔNG LOGIC

2.1. CẤU TRÚC ĐẠI SỐ BOOLE

Là cấu trúc đại số được định nghĩa trên 1 tập phần tử nhị phân B = {0,1} và các phép toán nhị

phân: AND (.), OR (+), NOT (’).

Thứ tự phép toán: theo thứ tự dấu ngoặc (), NOT, AND, OR

2.1.1. Các tiên đề (Axioms)

- Tính kín (Closure Property)

- Phần tử đồng nhất (Identity Element)

- Tính giao hoán (Commutative Property)

- Tính phân bố (Distributive Property)

- Phần tử bù (Complement Element)

Chương 2: Đại số Boole - cổng logic

15

2.1.2. Các định lý cơ bản (Basic Theorems)

- Định lý 1:

- Định lý 2:

- Định lý 3:

- Định lý 4: định lý hấp thu (Absorption)

- Định lý 5: định lý kết hợp (Associative)

- Định lý 6: định lý De Morgan

Mở rộng

2.2. HÀM BOOLE (BOOLEAN FUNCTION)

2.2.1. Định nghĩa

- Hàm Boole là 1 biểu thức được tạo bởi các biến nhị phân và các phép toán nhị phân NOT,

AND, OR.

- Với giá trị cho trước của các biến, hàm Boole sẽ có giá trị là 0 hoặc 1

- Bảng giá trị

Chương 2: Đại số Boole - cổng logic

16

2.2.2. Bù của 1 hàm

- Sử dụng định lý De Morgan

- Lấy biểu thức đối ngẫu và lấy bù các biến

Tính đối ngẫu (Duality): Hai biểu thức được gọi là đối ngẫu của nhau khi ta thay phép toán

AND bằng OR, phép toán OR bằng AND, 0 thành 1 và 1 thành 0

Lấy đối ngẫu

Bù các biến

2.3. DẠNG CHÍNH TẮC VÀ DẠNG CHUẨN CỦA HÀM BOOLE

2.3.1. Các tích chuẩn (minterm) và tổng chuẩn (Maxterm)

- Tích chuẩn (minterm): mi (0 ≤ i ≤ 2n – 1) là các số hạng tích (AND) của n biến mà hàm

Boole phụ thuộc với quy ước biến đó có bù nếu nó là 0 và không bù nếu là 1

- Tổng chuẩn (Maxterm): Mi (0 ≤ i ≤ 2n – 1) là các số hạng tổng (OR) của n biến mà hàm

Boole phụ thuộc với quy ước biến đó có bù nếu nó là 1 và không bù nếu là 0

Chương 2: Đại số Boole - cổng logic

17

2.3.2. Dạng chính tắc (Canonical Form)

- Dạng chính tắc 1: là dạng tổng của các tích chuẩn (minterm) làm cho hàm Boole có giá trị

1

- Dạng chính tắc 2: là dạng tích của các tổng chuẩn (Maxterm) làm cho hàm Boole có giá

trị 0.

Chương 2: Đại số Boole - cổng logic

18

Trường hợp hàm Boole tùy định (don’t care): Hàm Boole n biến có thể không được định

nghĩa hết tất cả 2n tổ hợp của n biến phụ thuộc. Khi đó tại các tổ hợp không sử dụng này, hàm

Boole sẽ nhận giá trị tùy định (don’t care), nghĩa là hàm Boole có thể nhận giá trị 0 hoặc 1.

2.3.3. Dạng chuẩn (Standard Form)

- Dạng chuẩn 1: là dạng tổng các tích (S.O.P – Sum of Product)

Chương 2: Đại số Boole - cổng logic

19

- Dạng chuẩn 2: là dạng tích các tổng (P.O.S – Product of Sum)

2.4. CỔNG LOGIC

2.4.1. Cổng NOT

2.4.2. Cổng AND

Với cổng AND có nhiều ngõ vào, ngõ ra sẽ là 1 nếu tất cả các ngõ vào đều là 1.

Chương 2: Đại số Boole - cổng logic

20

2.4.3. Cổng OR

Với cổng OR có nhiều ngõ vào, ngõ ra sẽ là 0 nếu tất cả các ngõ vào đều là 0.

2.4.4. Cổng NAND

Với cổng NAND có nhiều ngõ vào, ngõ ra sẽ là 0 nếu tất cả các ngõ vào đều là 1

2.4.5. Cổng NOR

Với cổng NOR có nhiều ngõ vào, ngõ ra sẽ là 1 nếu tất cả các ngõ vào đều là 0

Chương 2: Đại số Boole - cổng logic

21

2.4.6. Cổng EXOR

Với cổng XOR có nhiều ngõ vào, ngõ ra sẽ là 1 nếu tổng số bit 1 ở các ngõ vào đều là số lẻ.

2.4.7. Cổng ENOR

Với cổng XNOR có nhiều ngõ vào, ngõ ra sẽ là 1 nếu tổng số bit 1 ở các ngõ vào đều là số

chẵn.

2.5. RÚT GỌN HÀM BOOLE

Rút gọn (tối thiểu hóa) hàm Boole nghĩa là đưa hàm Boole về dạng biểu diễn đơn giản nhất,

sao cho:

- Biểu thức có chứa ít nhất các thừa số và mỗi thừa số chứa ít nhất các biến

- Mạch logic thực hiện có chứa ít nhất các vi mạch số

2.5.1. Phương pháp đại số

Dùng các định lý và tiên đề để rút gọn hàm

Chương 2: Đại số Boole - cổng logic

22

2.5.2. Phương pháp bìa KARNAUGH

Cách biểu diễn

- Bìa K gồm các ô vuông, mỗi ô vuông biểu diễn cho tổ hợp n biến. Như vậy bìa K cho n

biến sẽ có 2n ô.

- Hai ô được gọi là kề cận nhau khi tổ hợp biến mà chúng biểu diễn chỉ khác nhau 1 biến.

- Trong ô sẽ ghi giá trị tương ứng của hàm Boole tại tổ hợp đó. Ở dạng chính tắc 1 thì đưa

các giá trị 1 và X lên các ô, không đưa các giá trị 0. Ngược lại, dạng chính tắc 2 thì đưa giá

trị 0 và X

Bìa 2 biến

Bìa 3 biến

Chương 2: Đại số Boole - cổng logic

23

Bìa 4 biến

Bìa 5 biến

Rút gọn bìa Karnaugh

Nguyên tắc

- Liên kết đôi: Khi liên kết (OR) hai ô có giá trị 1 (Ô_1) kề cận với nhau trên bìa K, ta sẽ

được 1 số hạng tích mất đi 1 biến so với tích chuẩn (biến mất đi là biến khác nhau giữa 2

ô). Hoặc khi liên kết (AND) hai ô có giá trị 0 (Ô_0) kề cận với nhau trên bìa K, ta sẽ được

1 số hạng tổng mất đi 1 biến so với tổng chuẩn (biến mất đi là biến khác nhau giữa 2 ô).

Chương 2: Đại số Boole - cổng logic

24

- Liên kết 4: Tương tự như liên kết đôi khi liên kết 4 Ô_1 hoặc 4 Ô_0 kề cận với nhau, ta sẽ

loại đi được 2 biến (2 biến khác nhau giữa 4 ô)

- Liên kết 8: liên kết 8 ô kề cận với nhau, ta sẽ loại đi được 3 biến (3 biến khác nhau giữa 8

ô)

Liên kết 2k: khi ta liên kết 2k Ô_1 hoặc 2k Ô_0 kề cận với nhau, ta sẽ loại đi được k biến (k biến

khác nhau giữa 2k ô)

Chương 2: Đại số Boole - cổng logic

25

Các ví dụ về 2 ô kế cận

Các ví dụ về 4 ô kế cận

Chương 2: Đại số Boole - cổng logic

26

Chương 2: Đại số Boole - cổng logic

27

Các ví dụ về 8 ô kế cận

Chương 2: Đại số Boole - cổng logic

28

Các bước thực hiện rút gọn theo dạng S.O.P:

- Biểu diễn các Ô_1 lên bìa K

- Thực hiện các liên kết có thể có sao cho các Ô_1 được liến kết ít nhất 1 lần; mỗi lần liên

kết cho ta 1 số hạng tích. (Nếu Ô_1 không có kề cận với các Ô_1 khác thì ta có liên kết 1:

số hạng tích chính bằng minterm của ô đó).

- Biểu thức rút gọn có được bằng cách lấy tổng (OR) của các số hạng tích liên kết trên.

Các bước thực hiện rút gọn theo dạng P.O.S:

- Biểu diễn các Ô_0 lên bìa K

- Thực hiện các liên kết có thể có sao cho các Ô_0 được liến kết ít nhất 1 lần; mỗi lần liên

kết cho ta 1 số hạng tổng.

- Biểu thức rút gọn có được bằng cách lấy tích (AND) của các số hạng tổng liên kết trên.

-

Ví dụ: Rút gọn hàm sau

Chương 2: Đại số Boole - cổng logic

29

Trường hợp rút gọn hàm Boole có tùy định: thì ta có thể coi các Ô tùy định này là Ô_1 hoặc

Ô_0 sao cho có lợi khi liên kết (nghĩa là có được liên kết nhiều Ô kề cận nhất)

Chương 2: Đại số Boole - cổng logic

30

Chú ý:

- Ưu tiên liên kết cho các ô chỉ có 1 kiểu liên kết (phải là liên kết có nhiều ô nhất).

- Khi liên kết phải đảm bảo có chứa ít nhất 1 ô chưa được liên kết lần nào.

- Có thể có nhiều cách liên kết có kết quả tương đương nhau.

- Ta coi các tùy định như là những ô đã liên kết rồi

Ví dụ: Rút gọn các hàm

2.6. THỰC HIỆN HÀM BOOLE BẰNG CỔNG LOGIC

2.6.1. Cấu trúc cổng AND_OR

Cấu trúc AND_OR là sơ đồ logic thực hiện cho hàm Boole biểu diễn theo dạng tổng các tích

(S.O.P)

Chương 2: Đại số Boole - cổng logic

31

2.6.2. Cấu trúc cổng OR _ AND

Cấu trúc OR _ AND là sơ đồ logic thực hiện cho hàm Boole biểu diễn theo dạng tích các tổng

(P.O.S)

2.6.3. Cấu trúc cổng AND_OR_INVERTER (AOI)

Cấu trúc AOI là sơ đồ logic thực hiện cho hàm Boole biểu diễn theo dạng bù (INVERTER =

NOT) của tổng các tích

2.6.4. Cấu trúc cổng OR _ AND _INVERTER (OAI)

Cấu trúc OAI là sơ đồ logic thực hiện cho hàm Boole biểu diễn theo dạng bù của tích các tổng.

Chương 2: Đại số Boole - cổng logic

32

Các IC logic thực tế

Chương 2: Đại số Boole - cổng logic

33

2.6.5. Cấu trúc toàn cổng NAND

Cấu trúc NAND là sơ đồ logic thực hiện cho hàm Boole có biểu thức là dạng bù của 1 số hạng

tích

- Dùng định lý De Morgan để biến đổi số hạng tổng thành tích

- Cổng NOT cũng được thay thế bằng cổng NAND

-

Chương 2: Đại số Boole - cổng logic

34

Trong thực tế người ta chỉ sử dụng 1 loại cổng NAND 2 ngõ vào khi đó ta phải biến đổi biểu

thức sao cho chỉ có dạng bù trên 1 số hạng tích chỉ có 2 biến

2.6.6. Cấu trúc toàn cổng NOR

Cấu trúc NOR là sơ đồ logic thực hiện cho hàm Boole có biểu thức là dạng bù của 1 số hạng

tổng.

- Dùng định lý De Morgan để biến đổi số hạng tích thành tổng

- Cổng NOT cũng được thay thế bằng cổng NOR

Chương 2: Đại số Boole - cổng logic

35

BÀI TẬP CHƯƠNG 2

Chương 3: Hệ tổ hợp

36

CHƯƠNG 3: HỆ TỔ HỢP

3.1. GIỚI THIỆU - CÁCH THIẾT LẬP HỆ TỔ HỢP

Mạch logic được chia làm 2 loại:

- Hệ tổ hợp (Combinational Circuit)

- Hệ tuần tự (Sequential Circuit)

Hệ tổ hợp là mạch mà các ngõ ra chỉ phụ thuộc vào các giá trị của các ngõ vào. Mọi sự thay đổi

của ngõ vào sẽ làm ngõ rat hay đổi theo

❖ Các bước thiết kế:

- Phát biểu bài toán

- Xác định số biến ngõ vào và số biến ngõ ra

- Thành lập bảng giá trị chỉ rõ mối quan hệ giữa ngõ vào và ngõ ra

- Tìm biểu thức rút gọn của từng ngõ ra phụ thuộc vào các biến ngõ vào

- Thực hiện sơ đồ logic

Ví dụ: Thiết kế hệ tổ hợp có 3 ngõ vào X, Y, Z; và 2 ngõ ra F, G

- Ngõ ra F là 1 nếu như 3 ngõ vào có số bit 1 nhiều hơn số bit 0; ngược lại F = 0.

- Ngõ ra G là 1 nếu như giá trị nhi phân của 3 ngõ vào lớn hơn 1 và nhỏ hơn 6; ngược lại

G = 0

Chương 3: Hệ tổ hợp

37

Trường hợp hệ tổ hợp không sử dụng tất cả 2n tổ hợp của ngõ vào, thì tại các tổ hợp không sử

dụng đó ngõ ra có giá trị tùy định

Ví dụ: Thiết kế hệ tổ hợp có ngõ vào biểu diễn cho 1 số mã BCD. Nếu giá trị ngõ vào nhỏ hơn

3 thì ngõ ra có giá trị bằng bình phương giá trị ngõ vào; ngược lại giá trị ngõ ra bằng giá trị ngõ

vào trừ đi 3.

Chương 3: Hệ tổ hợp

38

3.2. BỘ CỘNG - TRỪ NHỊ PHÂN

3.2.1. Bộ cộng (Adder)

Bộ cộng bán phần (Half Adder – H.A)

Bộ cộng bán phần là hệ tổ hợp có nhiệm vụ thực hiện phép cộng số học x+y (x,y là 2 bit nhị

phân ngõ vào); hệ có 2 ngõ ra; bit tổng S (Sum) và bit nhớ C (Carry)

Chương 3: Hệ tổ hợp

39

Bộ cộng toàn phần (Full Adder – F.A)

Bộ cộng toàn phần thực hiện phép cộng số học 3 bit x + y + z (z biểu diễn cho bit nhớ từ vị trí

có trọng số nhỏ hơn gởi tới)

Chương 3: Hệ tổ hợp

40

3.2.2. Bộ trừ (Subtractor)

Bộ trừ bán phần (Half Subtractor – H.S)

Bộ trừ bán phần có nhiệm vụ thực hiện phép trừ số học x - y (x,y là 2 bit nhị phân ngõ vào); hệ

có 2 ngõ ra; bit tổng D (Difference) và bit mượn B (Borrow)

Bộ trừ toàn phần (Full Subtractor – F.S)

Bộ trừ toàn phần thực hiện phép trừ số học 3 bit x - y - z (z biểu diễn cho bit muọn từ vị trí có

trọng số nhỏ hơn gởi tới)

Chương 3: Hệ tổ hợp

41

3.2.3. Bộ cộng / trừ nhị phân song song

Bộ cộng nhị phân

Bộ trừ nhị phân

- Sử dụng các bộ trừ toàn phần F.S

- Thực hiện bằng phép cộng với bù 2 của số trừ

Kết quả: - C4 = 1 kết quả là số dương

- C4 = 0 kết quả là số âm

Chương 3: Hệ tổ hợp

42

Bộ cộng / trừ nhị phân

3.3. Hệ chuyển mã (Code Conversion)

- Hệ chuyển mã là hệ tổ hợp có nhiệm vụ làm cho 2 hệ thống tương thích với nhau, mặc dù

mỗi hệ thống dùng mã nhị phân khác nhau.

-

- Hệ chuyển mã có ngõ vào cung cấp các tổ hợp mã nhị phân A và các ngõ ra tạo ra cá tổ hợp

mã nhị phân B. Như vậy, ngõ vào và ngõ ra phải có số lượng từ mã bằng nhau.

Ví dụ: Thiết kế hệ chuyển mã từ mã BCD thành mã BCD quá 3

Chương 3: Hệ tổ hợp

43

3.4. BỘ GIẢI MÃ (DECODER)

3.4.1. Giới thiệu

- Bộ giải mã là hệ chuyển mã có nhiệm vụ chuyển từ mã nhị phân cơ bản n bit ở ngõ vào

thành mã nhị phân 1 trong m ở ngõ ra

- Với giá trị i của tổ hợp nhị phân ở ngõ vào, thì ngõ ra Yi sẽ tích cực và các ngõ ra còn lại

sẽ không tích cực.

- Có 2 dạng: ngõ ra tích cực cao (mức 1) và ngõ ra tích cực thấp (mức 0)

Chương 3: Hệ tổ hợp

44

Bộ giải mã ngõ ra tích cực cao

Bộ giải mã ngõ ra tích cực thấp

Chương 3: Hệ tổ hợp

45

Bộ giải mã có ngõ vào cho phép

- Ngoài các ngõ vào dữ liệu, bộ giải mã có thể có 1 hay nhiều ngõ vào cho phép

- Khi các ngõ vào cho phép ở trạng thái tích cực thì mạch giải mã mới được hoạt động. Ngược

lại, mạch giải mã sẽ không hoạt động; khi đó các ngõ ra đều ở trạng thái không tích cực.

3.4.2. IC giải mã

IC 74139: gồm 2 bộ giải mã 2 sang 4 ngõ ra tích cực thấp

Chương 3: Hệ tổ hợp

46

IC 74138: bộ giải mã 3 sang 8 ngõ ra tích cực thấp

3.4.3. Sử dụng bộ giải mã thực hiện hàm Boole

Ngõ ra của bộ giải mã là minterm (ngõ ra tích cực cao) hoặc maxterm (ngõ ra tích cực thấp)

của n biến ngõ vào. Do đó, ta có thể sử dụng bộ giải mã thực hiện hàm Boole theo dạng chính

tắc

3.5. BỘ MÃ HÓA (ENCODER)

3.5.1. Giới thiệu

- Encoder là hệ chuyển mã thực hiện hoạt động ngược lại với decoder. Nghĩa là encoder có

m ngõ vào theo mã nhị phân 1 trong m và n ngõ ra theo mã nhị phân cơ bản (với m ≤ 2n)

- Với ngõ vào Ii được tích cực thì ngõ ra chính là tổ hợp giá trị nhị phân i tương ứng

Chương 3: Hệ tổ hợp

47

Bộ mã hóa có ưu tiên (Priority Encoder): là mạch mã hóa sao cho nếu có nhiều hơn 1 ngõ vào

cùng tích cực thì ngõ ra sẽ là giá trị nhị phân của ngõ vào có ưu tiên cao nhất.

Chương 3: Hệ tổ hợp

48

3.5.2. IC mã hóa ưu tiên 8 sang 3 (74148)

3.6. BỘ DỒN KÊNH (MULTIPLEXER – MUX)

3.6.1. Giới thiệu

- Bộ MUX 2n→1 là hệ tổ hợp có nhiều ngõ vào nhưng chỉ có 1 ngõ ra. Ngõ vào gồm 2 nhóm:

m ngõ vào dữ liệu (data input) và n ngõ vào lựa chọn (select input)

- Với 1 giá trị i của tổ hợp nhị phân các ngõ vào lựa chọn, ngõ vào dữ liệu Di sẽ được chọn

đưa đến ngõ ra. (m = 2n)

Chương 3: Hệ tổ hợp

49

Bộ MUX 4→1

Chương 3: Hệ tổ hợp

50

3.6.2. IC dồn kênh

74LS153: gồm 2 bộ MUX 4→1

74LS151: bộ MUX 8→1

Chương 3: Hệ tổ hợp

51

3.6.3. Sử dụng bộ MUX thực hiện hàm Boole

Bộ MUX 2n thực hiện hàm Boole n biến

Bộ MUX 2n thực hiện hàm Boole n+1 biến

Chương 3: Hệ tổ hợp

52

3.7. BỘ PHÂN KÊNH (DEMUX)

3.7.1. Giới thiệu

- Bộ DEMUX 1→2n có chức năng thực hiện hoạt động ngược lại với bộ MUX. Mạch có 1

ngõ vào dữ liệu, n ngõ vào lựa chọn và 2n ngõ ra

- Với 1 giá trị i của tổ hợp nhị phân các ngõ vào lựa chọn, ngõ vào dữ liệu D sẽ được chọn

đưa đến ngõ ra Yi.

Bộ DEMUX 1→4

Chương 3: Hệ tổ hợp

53

3.7.2. IC phân kênh 74LS155

Gồm 2 bộ phân kênh 1→4

3.8. BỘ SO SÁNH ĐỘ LỚN (COMPARATOR)

3.8.1. Giới thiệu

- Bộ so sánh là hệ tổ hợp có nhiệm vụ so sánh 2 số nhị phân không dấu A và B(mỗi số n bit)

- Bộ so sánh có 3 ngõ ra(A>B), (A=B) và (A<B); chỉ có 1 ngõ ra tích cực theo kết quả so

sánh.

Bộ so sánh 3 bit

Sử dụng biến trung gian:

Chương 3: Hệ tổ hợp

54

Chương 3: Hệ tổ hợp

55

3.8.2. IC so sánh 74LS85

BÀI TẬP CHƯƠNG 3

File đính kèm:

giao_trinh_mon_dien_tu_so_phan_1.pdf

giao_trinh_mon_dien_tu_so_phan_1.pdf