Giáo trình Kỹ thuật số - Nguyễn Thị Thanh Hằng

Hệ thống số nhị phân(Binary System)

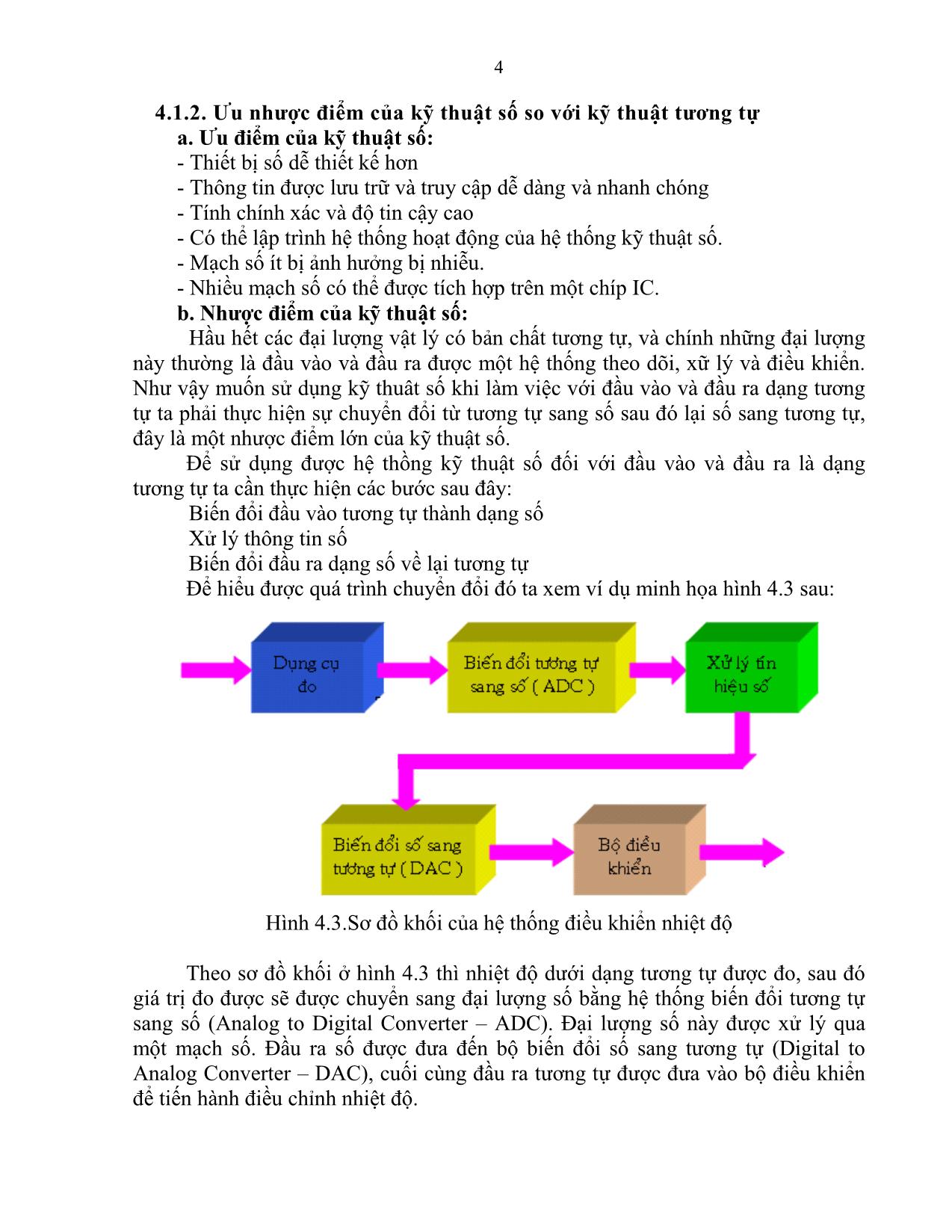

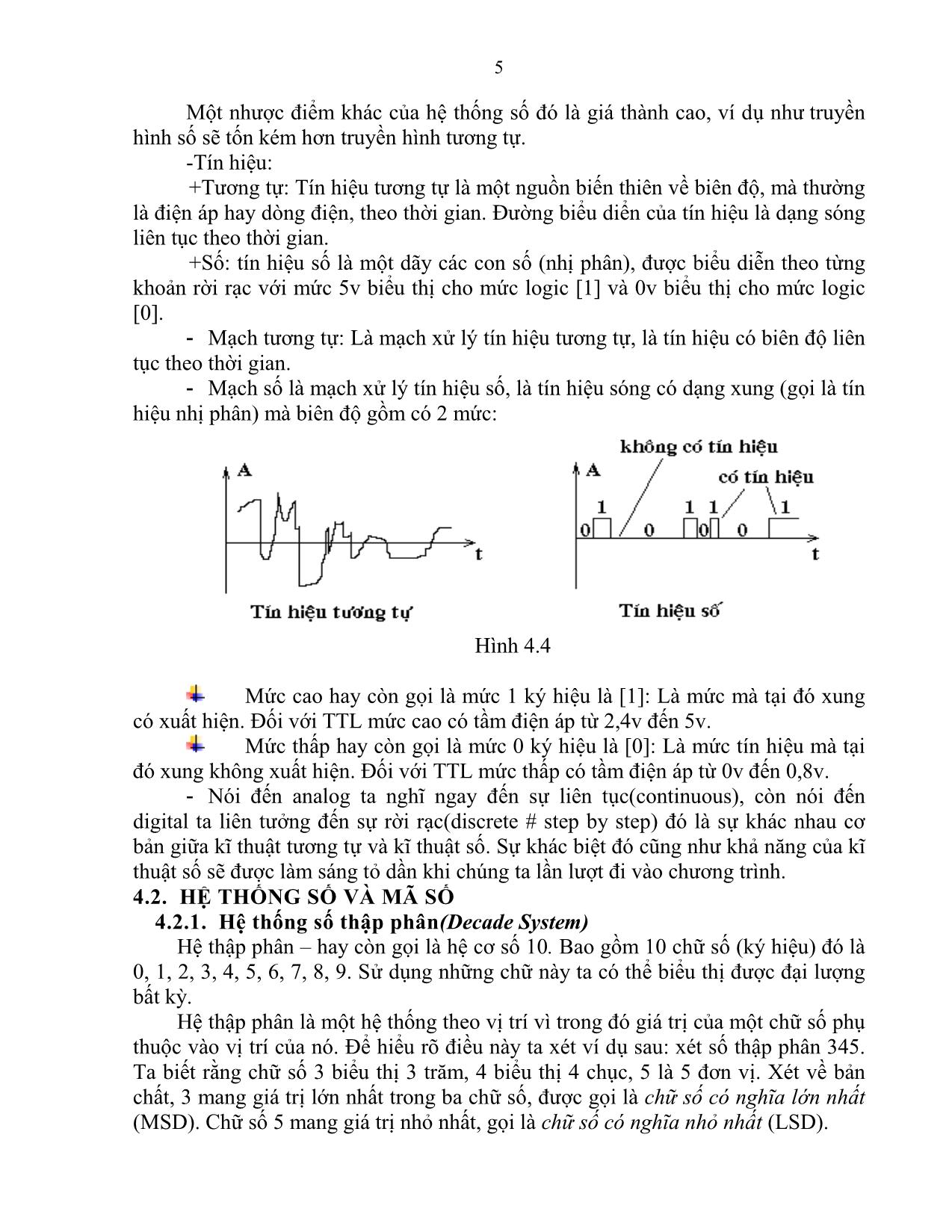

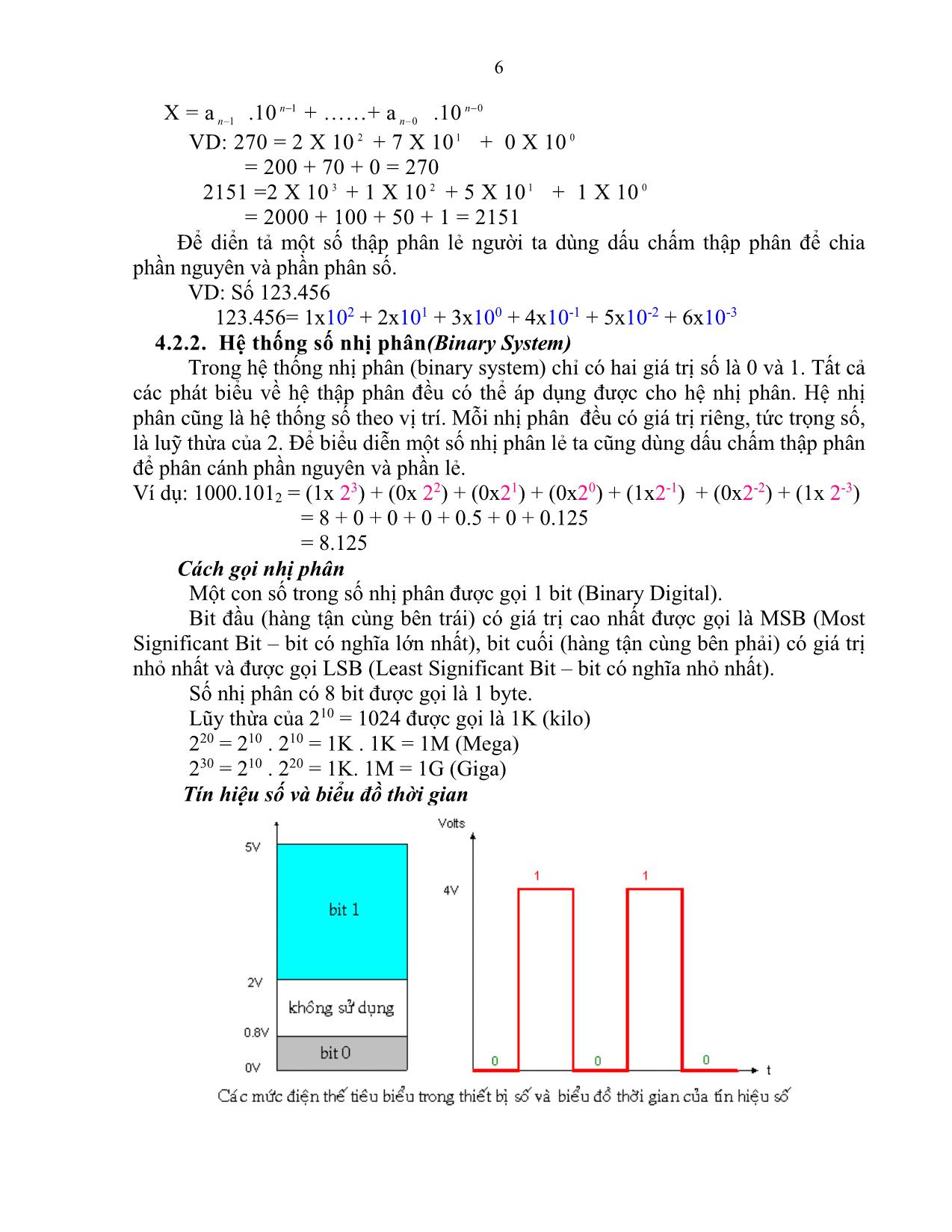

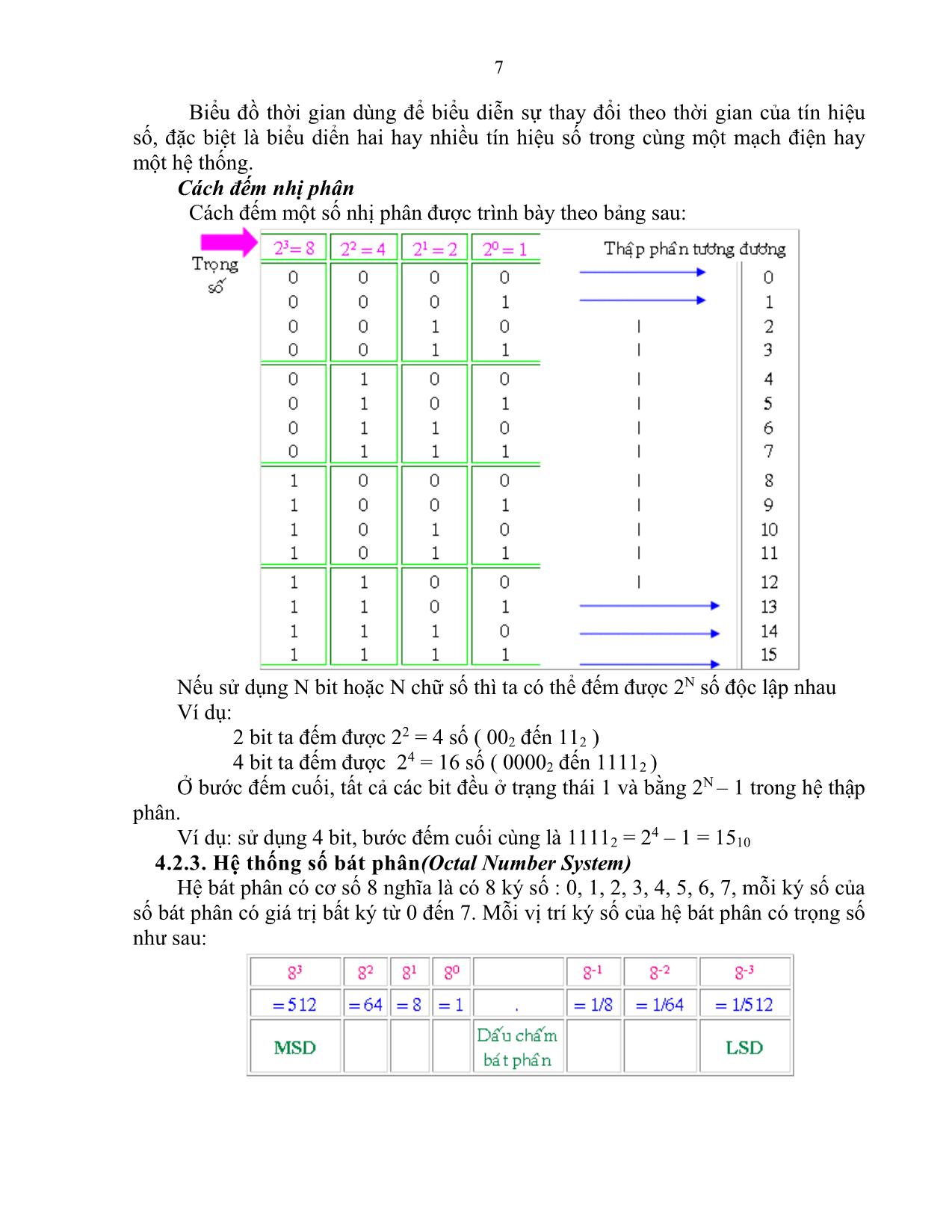

Trong hệ thống nhị phân (binary system) chỉ có hai giá trị số là 0 và 1. Tất cả

các phát biểu về hệ thập phân đều có thể áp dụng được cho hệ nhị phân. Hệ nhị

phân cũng là hệ thống số theo vị trí. Mỗi nhị phân đều có giá trị riêng, tức trọng số,

là luỹ thừa của 2. Để biểu diễn một số nhị phân lẻ ta cũng dùng dấu chấm thập phân

để phân cánh phần nguyên và phần lẻ.

Ví dụ: 1000.1012 = (1x 23) + (0x 22) + (0x21) + (0x20) + (1x2-1) + (0x2-2) + (1x 2-3)

= 8 + 0 + 0 + 0 + 0.5 + 0 + 0.125

= 8.125

Cách gọi nhị phân

Một con số trong số nhị phân được gọi 1 bit (Binary Digital).

Bit đầu (hàng tận cùng bên trái) có giá trị cao nhất được gọi là MSB (Most

Significant Bit – bit có nghĩa lớn nhất), bit cuối (hàng tận cùng bên phải) có giá trị

nhỏ nhất và được gọi LSB (Least Significant Bit – bit có nghĩa nhỏ nhất).

Số nhị phân có 8 bit được gọi là 1 byte.

Lũy thừa của 210 = 1024 được gọi là 1K (kilo)

220 = 210 . 210 = 1K . 1K = 1M (Mega)

230 = 210 . 220 = 1K. 1M = 1G (Giga)

Trang 1

Trang 2

Trang 3

Trang 4

Trang 5

Trang 6

Trang 7

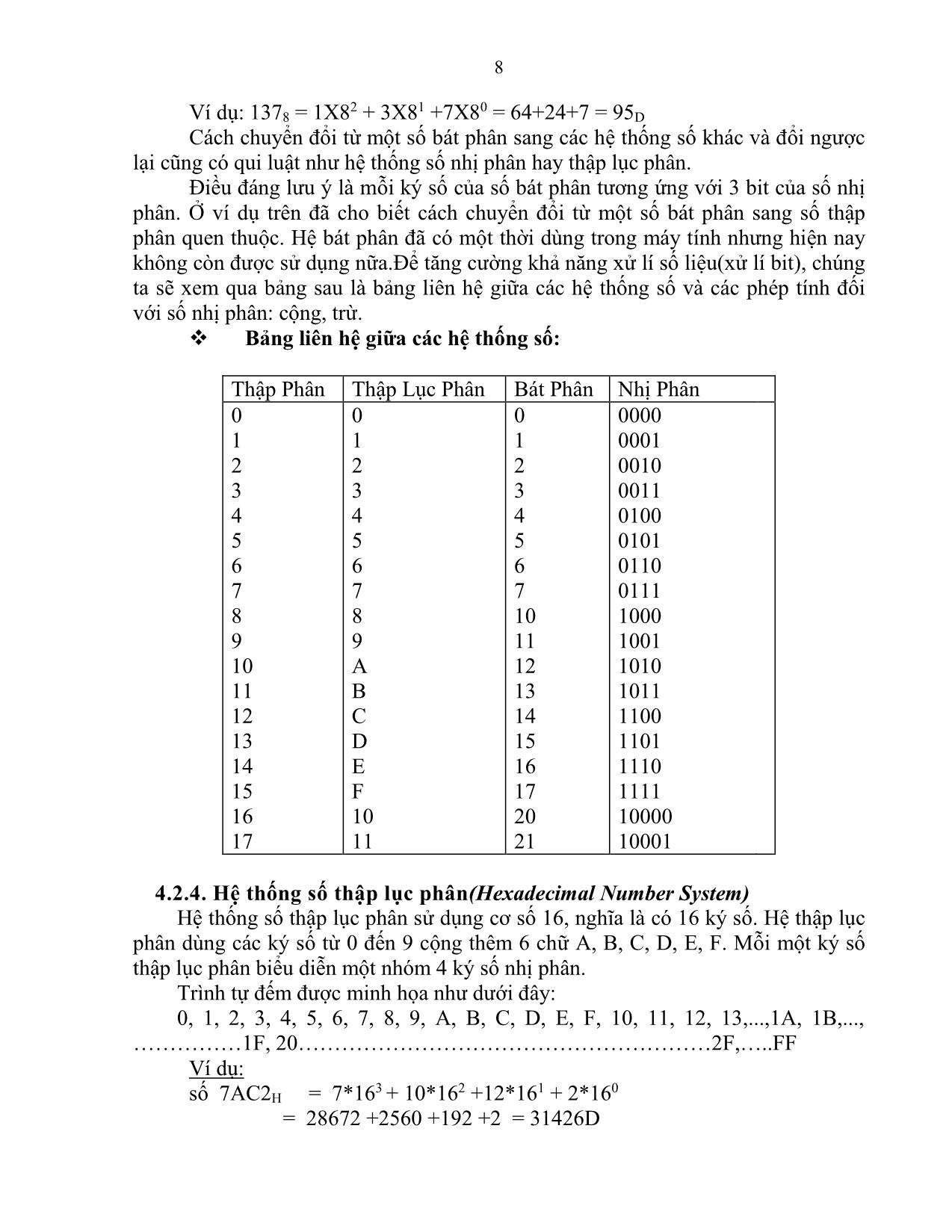

Trang 8

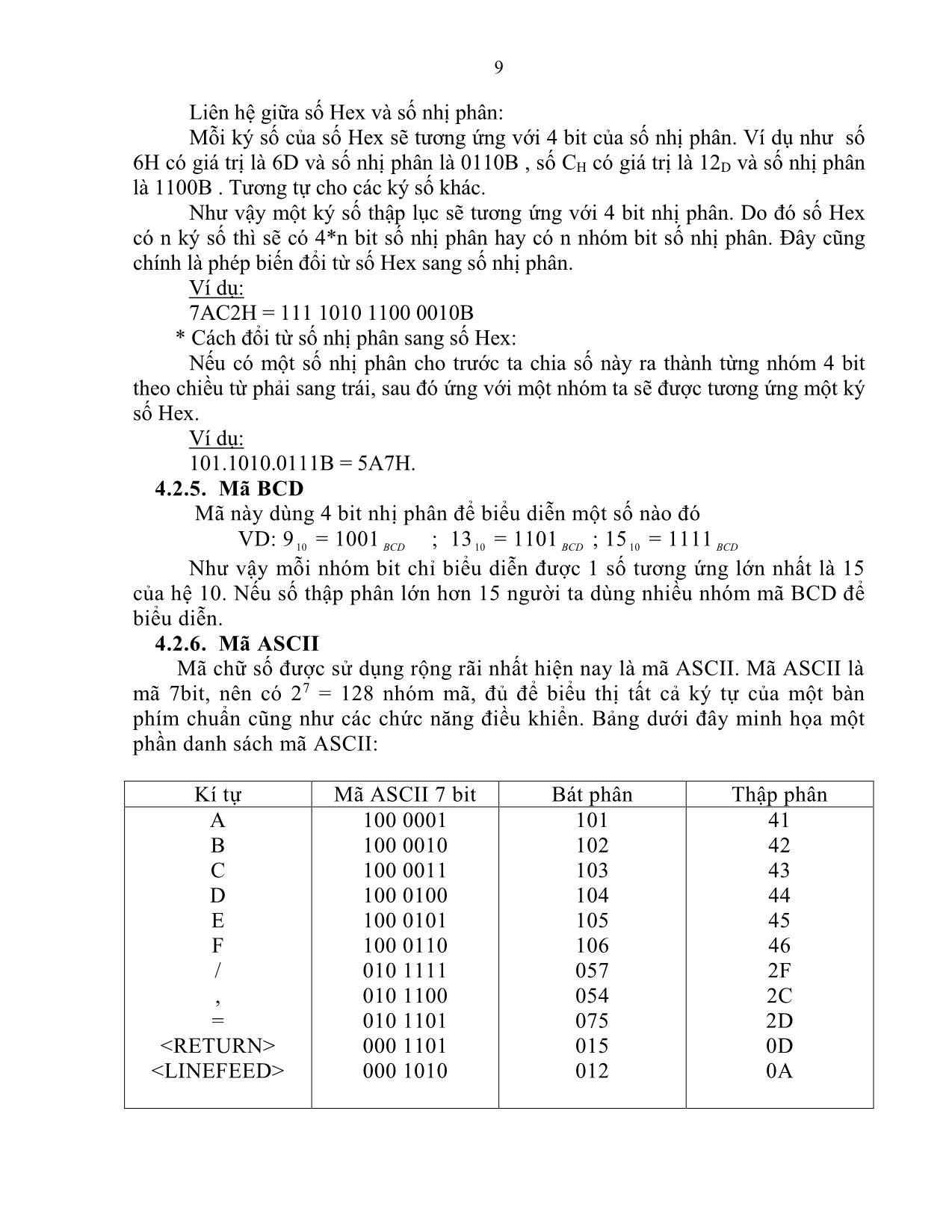

Trang 9

Trang 10

Tải về để xem bản đầy đủ

Tóm tắt nội dung tài liệu: Giáo trình Kỹ thuật số - Nguyễn Thị Thanh Hằng

thông dụng nhất. SAC có sơ đồ phức tạp hơn nhiều so với ADC dạng sóng bậc thang. Ngoài ra SAC còn có giá trị tC cố định, không phụ thuộc vào giá trị của đầu vào tương tự. Hình 10.13 là một cấu hình cơ bản của SAC, tương tự cấu hình của ADC dạng sóng bậc thang. Tuy nhiên SAC không sử dụng bộ đếm cung cấp đầu vào cho DAC mà thay vào đó là thanh ghi. Logic điều khiển sửa đổi nội dung lưu trên thanh ghi theo từng bit một cho đến khi dử liệu ở thanh ghi biến thành giá trị số tương đương với đầu vào tương tự VA trong phạm vi độ phân giải của bộ chuyển đổi. 132 Hình 10.13. Sơ đồ khối ADC liên tiếp xấp xỉ 10.2.5. Mạch ADC chuyển đổi song song Bộ chuyển đổi nhanh (flash converter) là ADC tốc độ cao nhất hiện nay có mặt trên thị trường, nhưng sơ đồ mạch phức tạp hơn các loại khác. Ví dụ một ADC nhanh 6 bit đòi hỏi 63 bộ so sánh tương tự, còn ADC nhanh 8 bit thì con số này lên đến 255, 10 bit thì lên đến 1023. Như vậy số lượng bộ so sánh quá lớn đã giới hạn kích cỡ của ADC nhanh. Hình 10.14 là sơ đồ của một ADC nhanh 133 ADC nhanh ở hình 10.14 có độ phân giải 3 bit. Kích thước bậc thang là 1V. Bộ chia điện thế thiết lập mức quy chiếu cho từng bộ so sánh để có được 7 mức ứng với 1V ( trọng số của LSB ), 2V, 3V, 7V (đầy thang). Đầu vào tương tự VA được nối đến đầu vào còn lại của từng bộ so sánh. Với VA 1V thì từ một đầu ra trở lên sẽ xuống mức thấp. Đầu ra của bộ so sánh được đưa vào bộ mã hoá ưu tiên tích cực ở mức thấp, sinh đầu ra ứng với đầu ra có số thứ tự cao nhất ở mức thấp của bộ so sánh. Lý luận tương tự ta sẽ có được bảng giá trị như bảng 10.1 Bảng 10.1 Bảng sự thật của ADC nhanh 3 bit hình 10.14 ADC nhanh hình 10.14 có độ phân giải 1V vì đầu vào tương tự phải thay đổi mỗi lần 1V mới có thể đưa đầu ra số lên bậc kế tiếp. Muốn có độ phân giải tinh hơn thì phải tăng tổng số mức điện thế vào (nghĩa là sử dụng nhiều điện trở chia thế hơn) và tổng số bộ so sánh. Nói chung ADC nhanh N bit thì cần 2N – 1 bộ so sánh, 2N điện trở, và logic mã hoá cần thiết. Thời gian chuyển đổi Bộ chuyển đổi nhanh không cần thiết tín hiệu xung nhịp vì tiến trình này xảy ra liên tục. Khi giá trị đầu vào thay đổi thì đầu ra của bộ so sánh sẽ thay đổi làm cho ngõ ra của bộ mã hóa thay đổi theo. Như vậy thời gian chuyển đổi là thời gian cần thiết để xuất hiện một đầu ra số mới đáp lại một thay đổi ở VA. Thời gian chuyển đổi chỉ phụ thuộc vào khoảng trể do truyền của bộ so sánh và bộ mã hóa. Vì vậy mà ADC nhanh có thời gian chuyển đổi vô cùng gắn. 10.3. GIỚI THIỆU IC 10.3.1. IC AD7524 IC AD7524 ( IC CMOS) là IC chuyên dụng dùng để chuyển đổi từ số sang tương tự. AD7524 là bộ chuyển đổi D/A 8 bit, dùng mạng R/2R ladder. Có sơ đồ bên trong như hình 10.15. 134 Hình 10.15. Sơ đồ bên trong IC AD7524 AD7524 có đầu vào 8 bit, có thể bị chốt trong dưới sự điều khiển của đầu vào CHỌN CHIP và đầu vào ghi khi cả hai đầu vào điều khiển này đều ở mức thấp, thì 8 đầu vào dữ liệu D7 – D0 sinh ra dòng tương tự OUT1 và OUT2 (thường OUT2 nối đất). Nếu một trong hai đầu vào điều khiển lên cao thì lúc này dữ liệu vào bị chốt lại và đầu ra tương tự duy trì tại mức ứng với dữ liệu số bị chốt đó. Những thay đổi kế tiếp ở đầu vào sẽ không tác động đến ngõ ra tương tự OUT1 ở trạng thái chốt này. Các thông số của IC được liệt kê ở bảng 10.2 Bảng 10.2 Các thông số của IC DA7524 135 Quan hệ ngõ vào và ngõ ra tương ứng được trình bày ở bảng 10.3 Bảng 10.3 Quan hệ ngõ vào và ngõ ra Ứng dụng của IC AD7524 thường dùng giao tiếp với các vi xử lý và vi điều khiển để chuyển đổi tín hiệu số sang tương tự nhằm điều khiển các đối tượng cần điều khiển. Sau đây là một số ứng dụng của IC AD7524 giao tiếp với các IC khác. Hình 10.16. Giao tiếp AD7524 với 6800 136 Hình 10.17. Giao tiếp giữa AD7524 với 8051 Hình 10.18. Giao tiếp giữa AD7524 với Z-80A 10.3.2. IC DAC0830 DAC 0830 là IC thuộc họ CMOS. Là bộ chuyển đổi D/A 8 bit dùng mạng R/2R ladder. Có thể giao tiếp trực tiếp với các vi xử lý để mở rộng hoạt động chuyển đổi D/A. 137 a. Sơ đồ chân và cấu trúc bên trong của DAC0830: Hình 10.19. Cấu trúc bên trong của IC DAC0804 b. Hoạt động của các chân: ( CHIP SELECT) là chân chọn hoạt động ở mức thấp. Được kết hợp với chân ITL để có thể viết dữ liệu. ITL (INPUT LACTH ENABLE) là chân cho phép chốt ngõ vào, hoạt động ở mức cao. ITL kết hợp với để cho phép viết. (WRITE) hoạt động ở mức thấp. Được sử dụng để nạp các bit dữ liệu ngõ vào chốt. Dữ liệu được chốt khi ở mức cao. Để chốt được dữ liệu vào thì và phải ở mức thấp trong khi đó ITL phải ở mức cao. 138 (WRITE) tác động ở mức thấp. Chân này kết hợp với chân cho phép dữ liệu chốt ở ngõ vào mạch chốt được truyền tới thanh nghi DAC trong IC. (TRANSFER CONTROL SIGNAL) tác động ở mức thấp. Cho phép được viết. DI0 – DI7 là các ngõ vào số trong đó DI0 là LSB còn DI7 là MSB. IOUT1 ngõ ra dòng DAC1. Có trị số cực đại khi tất cả các bit vào đều bằng 1, còn bằng 0 khi tất cả các bit vào đều bằng 0. IOUT2 ngõ ra dòng DAC2. Nếu IOUT1 tăng từ 0 cho đến cực đại thì IOUT2 sẽ giảm từ cực đại về 0 để sao cho IOUT1 + IOUT2 = hằng số. Rfb điện trở hồi tiếp nằm trong IC. Luôn được sử dụng để hồi tiếp cho Op Amp mắc ở ngoài. Vref ngõ vào điện áp tham chiếu từ -10 đến +10V. VCC điện áp nguồn cấp cho IC hoạt động từ 5 đến 15V. GND (mass) chung cho IOUT1 và IOUT2. Sau đây là một số ứng dụng của DAC0830 chuyển đổi từ số sang tương tự. Điều khiển volume bằng số Hình 10.20. Ứng dụng DAC0830 để điều khiển Volume 139 Điều khiển máy phát sóng bằng số: Hình 10.21. Ứng dụng DAC0830 để điều khiển máy phát sóng Bộ Điều khiển dòng bằng số: Hình 10.22. Bộ điều khiển dòng bằng số 140 - DAC8030 có thể điều khiển được dòng ra thay đổi theo dữ liệu số vào. Dòng ra thay đổi từ 4mA (khi D = 0) đến 19.9mA (khi D = 255). - Mạch điện trên sử dụng cho các mức điện áp vào khác nhau từ 16V đến 55V. - P2 thay đổi giá trị dòng điện ngõ ra, P1 chỉnh mức 0 của thang toàn phần ngõ ra. - Ngõ vào số có thể cung cấp từ vi xử lý (dùng Opto ở mỗi ngõ vào) và dữ liệu vào có thể đặt bởi các công tắc. 10.4. BÀI TẬP ỨNG DỤNG 10.4.1. Điều chỉnh và ổn định vị trí của một vật Khi yêu cầu mạch điều khiển đòi hỏi khống chế một vật dịch chuyển và cố định ở một mức không đổi có thể thực hiện mạch điều khiển theo sơ đồ trên hình10.23: Hình 10.23 Khi đặt một giá trị số nhị phân vào ngõ vào DAC, điện áp ngõ ra Va tác động mạch Op-Amps điều khiển động cơ servo M đưa vật cần điều khiển đến một vị trí đặt trước (vị trí này được xác lập khi Va = Vp). Như vậy tuỳ vào giá trị của số nhị phân, vật cần điều khiển sẽ dịch chuyển trong chiều dài từ 0 đến 100mm. Vì một lý do nào đó làm cho vật cần điều khiển lệch khỏi vị trí cân bằng (Va ≠ Vp) ví dụ như antenna bị gió thổi lệch khỏi vị trí cân bằng ... sẽ làm thay đổi điện áp Vp so với mass (do biến trở thay đổi vị trí), điều này sẽ tác động vào Op-Amps thay đổi điện áp trên động cơ servo M, tác động dưa vật cần điều khiển về vị trí cân bằng. 10.4.2. Mạch khởi động êm (Ramp-Start) Trong mạch điều khiển hệ truyền động có động cơ sử dụng kỹ thuật số, người ta thường sử dụng các bộ khởi động êm giúp hệ thống tránh được các xung đột biến cơ học giúp động không bị xoắn gãy trục hay hư hỏng các chi tiết cơ khí 141 cũng như điện từ khác. Mạch này có sơ đồ khối về nguyên lý làm việc như hình10.24: Hình 10.24 Khi hệ nhận được tín hiệu "START" từ mạch điều khiển, mạch đếm nhận xung clock và bắt đầu đếm lên, cùng lúc này ngõ ra Op-Amps là tín hiệu EOC (End-Of-Conversion) đang ở mức cao. Theo nhịp đếm lên của mạch đếm, DAC chuyển đổi các số nhị phân theo giá trị lớn dần như dạng sóng điện áp VAX trên hình vẽ. Tín hiệu này điều khiển hệ thống khởi động êm cho đến khi VA = VAX thì tín hiệu ngõ ra Op-Amps EOC sẽ về 0 dẫn đến kết thúc quá trình khởi động êm do cổng AND 3 ngõ vào hoạt động như một khoá điện tử. Rõ ràng, thay vì đột biến từ 0 đến VA, tín hiệu điện áp VAX tăng dần theo từng nấc nhỏ. Khoảng cách giữa 2 nấc chính là độ phân giải của DAC. 10.4.3. Mạch phát xung chỉnh được tần số và sóng dạng điện áp Nguyên lý làm việc của mạch này tương tự như mạch điều khiển đèn quảng cáo trong chương vi mạch nhớ nhưng thay vì các ngõ ra điều khiển đèn thì ở đây các tín hiệu này đưa vào DAC 0808. Khi thay đổi chương trình xuất ra từ vi mạch nhớ ta sẽ thay đổi được sóng dạng điện áp phát ra vout. Hình 10.25 142 Nếu muốn tín hiệu ngõ ra là sóng vuông, chỉ cần nạp trình vào EPROM như sau: Như vậy chỉ cần tính toán lại các mức điện áp tương ứng với các ngõ vào tín hiệu số lấy từ chương trình trong EPROM, ta có thể tạo ra bất kỳ sóng dạng điện áp nào ở ngõ ra. Khi muốn thay đổi tần số của sóng dạng điện áp vout, ta chỉ việc thay đổi tần số của mạch phát xung dùng vi mạch 555. Do đó, tần số của điện áp vout được chỉnh trong một khoảng rộng và trơn. 143 Phần đọc thêm: Mạch dao động đa hài phi ổn dùng IC 555 Vi mạch định thì 555 là mạch tích hợp Analog-Digital, được ứng dụng rất rộng rãi trong thực tế, đặc biệt trong lĩnh vực điều khiển, kết hợp với R,C nó có thể thực hiện nhiều chức năng như định thì, tạo xung chuẩn, tạo tín hiệu kích mở các linh kiện công suất. a. Sơ đồ chân và cấu trúc bên trong của vi mạch 555: + Cầu phân áp gồm 3 điện trở 5K nối từ nguồn +VCC xuống mass cho ra 02 điện áp chuẩn là: 1/3 VCC và 2/3 VCC. + OP-AMP1 là mạch khuếch đại so sánh có ngõ Iin- nhận điện áp chuẩn 2/3VCC còn ngõ Iin + thì nối ra ngoài chân số 6. + OP-AMP2 là mạch khuếch đại so sánh có ngõ Iin+ nhận điện áp chuẩn 1/3VCC còn ngõ Iin - thì nối ra ngoài chân số 2. + Mạch FF là loại mạch lưỡng ổn kích một bên. Q4 OP-AMP1 Q2 5K F/F OUTPUT 8 6 5 1 2 4 3 7 OP-AMP2 R S 5K 5K 2/3VCC 1/3VCC NOT Q Vr 1,4V OUTPUT Dircharge Reset Trigger input GND Control voltage Threshold +VCC Hình 2.3 Cấu trúc IC 555 144 + Mạch OUTPUT là mạch khuếch đại ngõ ra để tăng độ khuếch đại dòng cấp cho tải. + BJT Q1 có chân E nối vào một điện áp chuẩn khoảng 1,4V và loại PNP nên khi cực B nối ra ngoài bởi chân số 4 có điện áp cao hơn 1,4V thì Q1 ngưng dẫn nên Q1 không ảnh hưởng đến mạch: khi chân 4 có trị số nhỏ thích hợp với masse thì Q1 dẫn bão hòa đồng thời làm mạch ngõ ra OUTPUT cũng dẫn bão hòa và ngõ ra xuống mức thấp. + BJT Q2 là BJT có cực C để hở nối ra chân số 7 (Dicharge = xả). Do cực B được phân cực bởi mức điện áp ra Q’ của F/F nên khi Q’ ở mức cao thì Q2 bảo hòa và cực C của Q2 xem như nối masse, lúc đó ngõ ra của chân 3 cũng ở mức thấp; Khi Q’ ở mức thấp thì T2 ngưng dẫn cực C của Q2 bị hở, lúc đó ngõ ra chân 3 có điện áp cao. b. Mạch đa hài phi ổn cơ bản dùng IC 555: Sơ đồ mạch và nguyên lý hoạt động Hình 2.5 Sơ đồ mạch phi ổn LED R1 NE 555 1 5 3 7 6 2 8 4 RA RB .01 C +VCC Nạp Xả Trong mạch chân số 6 đựợc nối với chân số 2 nên hai chân này có chung điện áp trên tụ C để so sánh với điện áp chuẩn 2/3 VCC và 1/3 VCC bởi OP-AMP1 và OP-AMP2. Chân số 5 có tụ nhỏ, tụ .01 nối mass để lọc nhiễu tần số cao có thể làm ảnh hưởng điện áp chuẩn 2/3VCC. NE 555 1 2 3 4 5 6 7 8 Chân 1: GND (nối mass) Chân 2: Trigger Input (ngõ vào xung nảy) Chân 3: Output (ngõ ra) Chân4: Reset (hồi phục) Chân 5: Control Voltage(điện áp điều khiển) Chân 6: Threshold (thềm ngưỡng) Chân 7: Dicharge( xả điện) Chân 8: +VCC (Nguồn dương) Hình 2.4 Sơ đồ chân 145 Chân 4 nối nguồn VCC nên không dùng chức năng Reset, chân 7 xả điện được nối vào giữa 2 điện trở RA và RB tạo đường xả cho tụ. Ngõ ra chân 3 có điện trở giới hạn dòng 1,2K và Led để biểu thị mức điện áp ra. Khi mới đóng điện tụ C bắt đầu nạp từ 0V nên: - OP-AMP1 có Vi +< Vi - nên ngõ ra V01 mức thấp, ngõ ra R=0 (mức thấp). - OP-AMP2 có Vi +> Vi - nên ngõ ra V02 mức cao, ngõ ra S=1 (mức cao). - Mạch F/F có ngõ S=1 nên Q=1 và Q’=0. Lúc đó ngõ ra chân 3 có V0 VCC(do mạch đảo) làm Led sáng. - BJT Q2 có VB2 = 0v do Q ’=0 nên Q2 ngưng dẫn và để tụ C nạp điện. Tụ C nạp điện qua RA và RBvới hằng số thời gian khi nạp là: nạp = (RA + RB) .C Khi điện áp trên tụ tăng đến mức 1/3VCC thì OP-AMP2 đổi trạng thái, ngõ ra có V02 = mức thấp, ngõ ra S=0. Lúc này F/F không đổi trạng thái nên điện áp ngõ ra ở mức cao, Led vẫn sáng. Khi điện áp trên tụ tăng đến mức 2/3 VCC thì OP-AMP1 đỏi trạng thái, ngõ ra có V01= mức cao, ngõ R=1. Mạch F/F có ngõ R=1 nên Q’=1. Lúc đó ngõ ra chân 3 có V0 0V làm Led tắt. Khi ngõ Q’=1 sẽ làm Q2 dẫn bão hòa và chân số 7 nối mass làm tụ C không nạp tiếp điện áp được mà phải xả điện qua RB và BJT Q2 xuống masse. Tụ C xả điện qua RB với hằng số thời gian là: xả = RB .C Khi điện áp trên tụ, tức là chân 2 và chân 6 giảm xuồng dưới 2/3 VCC thì OP- AMP1 đổi trạng thái cũ là V01= mức thấp, ngõ R=0. Khi R xuống mức thấp thì F/F không đổi trạng thái nên điện áp ngõ ra vẫn ở mức thấp, Led vẫn tắt. Khi điện áp trên tụ giảm xuồng đến 1/3VCC thì OP-AMP2 có Vi+> Vi- nên ngõ ra V02 mức cao, ngõ ra S=1 (mức cao). Mạch F/F có ngõ S=1 và Q’=0. Lúc đó ngõ ra chân 3 có V0 VCC(do mạch đảo) làm Led sáng đồng thời Q2 lúc đó mất phân cực do Q’ =0 nên ngưng dẫn và chấm dứt giai đoạn xả điện của tụ. Như vậy mạch trở lại trạng thái ban đầu và tụ lại nạp từ mức 1/3 VCC lên đến 2/3 VCC, hiện tượng này cứ tiếp diễn liên tục và tuần hoàn. 146 Lưu ý: Khi mới cấp điện tụ C nạp từ 0V lên 2/3 VCC, sau đó tụ xả điện từ 2/3 VCC xuống 1/3VCC chứ không xả xuống 0V. Những chu kỳ sau, tụ sẽ nạp từ 1/3 VCC lên 2/3 VCC chứ không nạp từ 0V nữa. Thời gian tụ nạp là thời gian V0 +VCC, Led sáng. Thời gian tụ xả là thời gian V0 0, Led tắt. Thời gian nạp và xả của tụ được tính theo công thức: +Thời gian nạp: tnạp = 0,69 .nạp = 0,69 (RA + RB).C +Thời gian nạp: txả = 0,69 .xả = 0,69 RB.C Điện áp ở ngõ ra chân số 3 có dạng xung vuông với chu kỳ là: T= tnạp +txả = 0,69 (RA + 2RB).C Do thời gian nạp và thời gian xả không bằng nhau nên tín hiệu xung vuông không đối xứng. Tần số của tín hiệu hình vuông là: f=1/T = 1/0.69 (RA + 2RB).C Sơ đồ dạng sóng: t tnạp txả t t VC(2-6) VD(7) V0(3) Hình 2.6 Sơ đồ dạng sóng 2/3VCC 1/3VCC Sơ đồ hình 2.6 là dạng điện áp các chân 2-6, chân 7 và chân 3. Khi tụ nạp thì chân 7 có điện áp cao hơn chân 2-6, nhưng khi tụ xả thì chân 7 giảm nhanh xuống 0V do Q2 dẫn bão hòa, không giảm hàm mũ theo tụ. 147 TÀI LIỆU THAM KHẢO 1. Đề cương môđun/môn học nghề Sửa chữa thiết bị điện tử công nghiệp”, Dự án Giáo dục kỹ thuật và Dạy nghề (VTEP), Tổng cục Dạy Nghề, Hà Nội, 2003 2. Mạch số - Nguyễn Hữu Phương. NXB khoa học kỹ thuật 2004 3. Giáo trình kỹ thuật số - ĐH SPKT TP. HCM 4. Sổ tay vi mạch số TTL và CMOS. Dương Minh Trí. nxb khoa học kỹ thuật 1989 5. Điện tử công suất. Nguyễn Bính NXB Khoa học kỹ thuật 2005 6. Kỹ thuật xung số - NXB Khoa học và Kỹ thuật 2004

File đính kèm:

giao_trinh_ky_thuat_so_nguyen_thi_thanh_hang.pdf

giao_trinh_ky_thuat_so_nguyen_thi_thanh_hang.pdf