Giải thuật PWM cho nghịch lưu hình T ba bậc để triệt tiêu điện áp common - mode

Trong bài báo này, một kỹ thuật điều chế độ rộng xung cho nghịch lưu 3 bậc hình T để triệt

tiêu điện áp common-mode (CMV) được trình bày. So sánh với kỹ thuật điều chế độ rộng xung

(PWM) thông thường, kỹ thuật này chỉ sử dụng những vector mà những vector đó tạo ra điện

áp common mode bằng không. Như kết quả, điện áp common mode của bộ chuyển đổi được

triệt tiêu. Do đó, những ảnh hưởng tiêu cực do CMV gây ra được hạn chế đến mức tối đa.

Ngoài ra, nguyên lý lựa chọn phù hợp những tín hiệu sóng mang tần số cao cho cấu hình

nghịch lưu hình T được mô tả. Để kiểm chứng lý thuyết được trình bày trong bài báo này, các

kết quả mô phỏng và thực nghiệm được thực hiện bởi phần mềm PSIM và mô hình thực nghiệm.

Trang 1

Trang 2

Trang 3

Trang 4

Trang 5

Trang 6

Trang 7

Trang 8

Trang 9

Tóm tắt nội dung tài liệu: Giải thuật PWM cho nghịch lưu hình T ba bậc để triệt tiêu điện áp common - mode

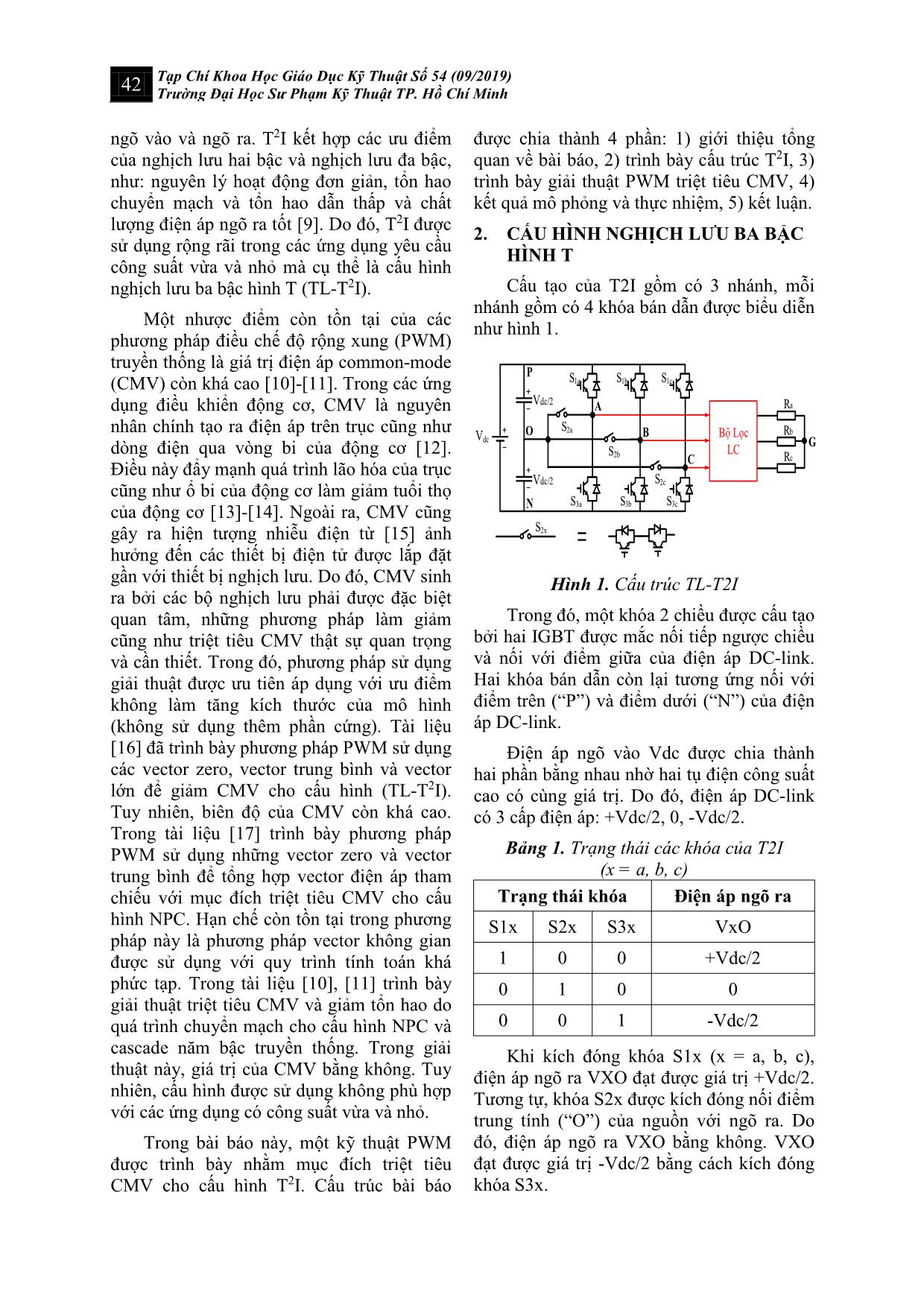

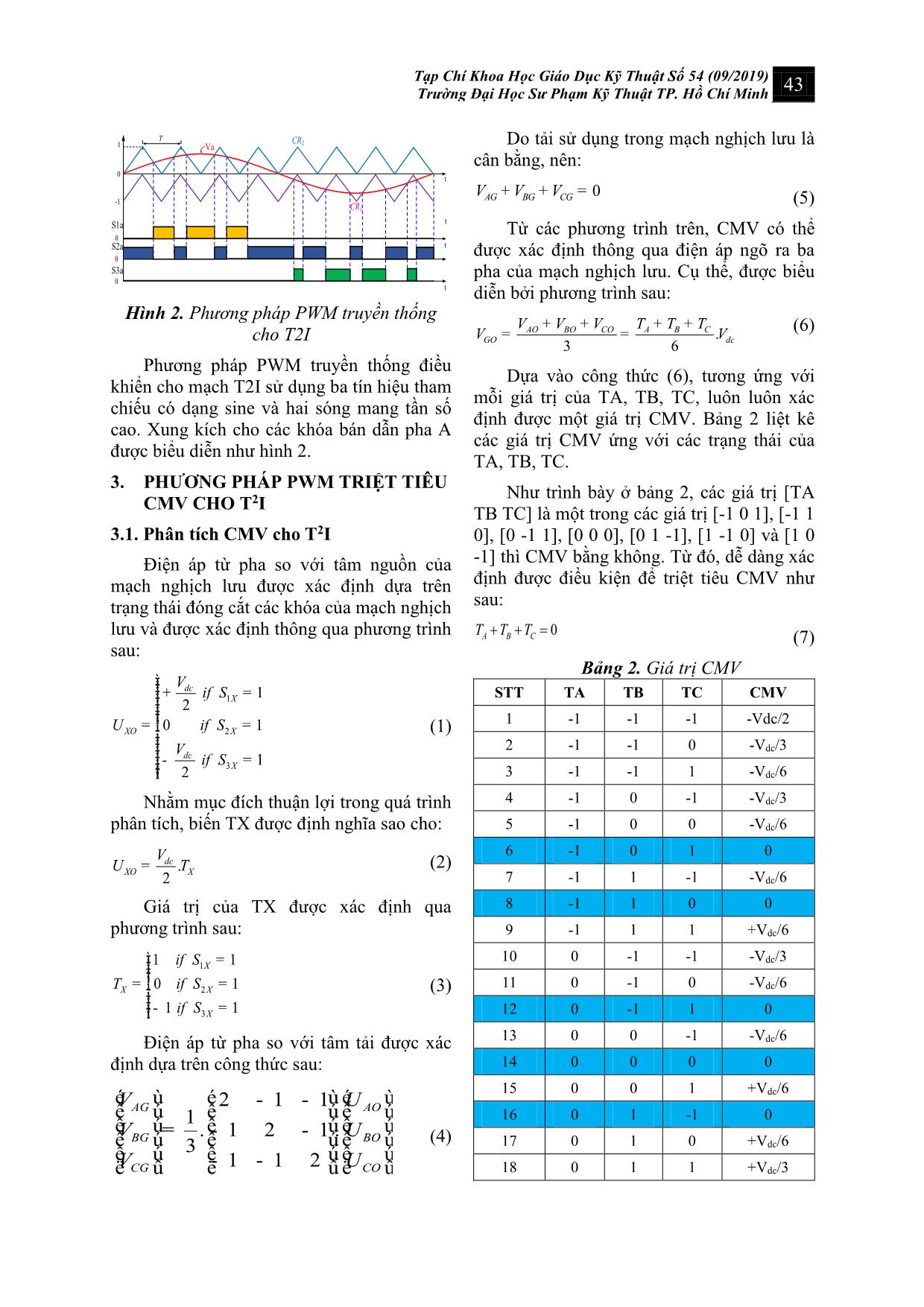

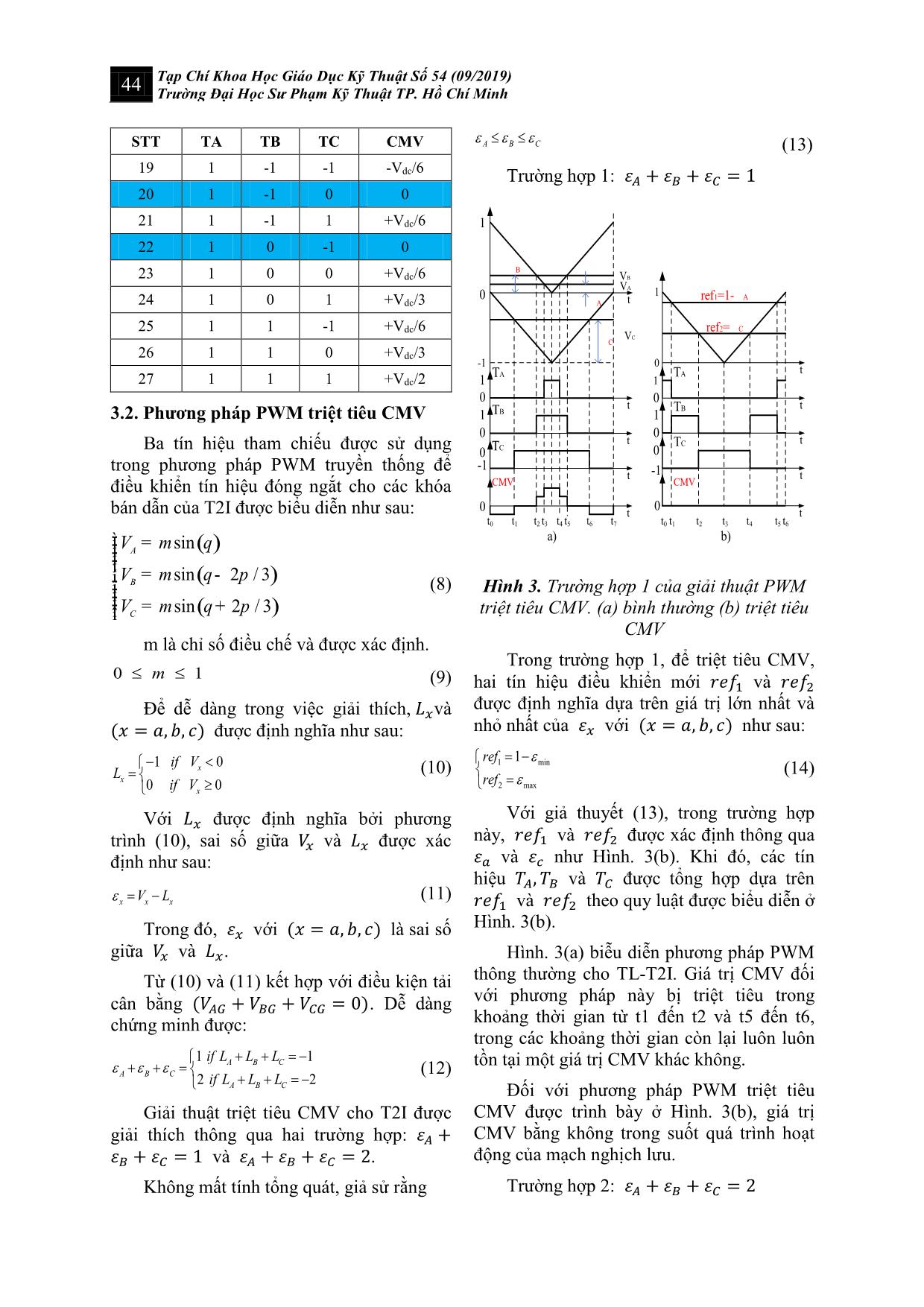

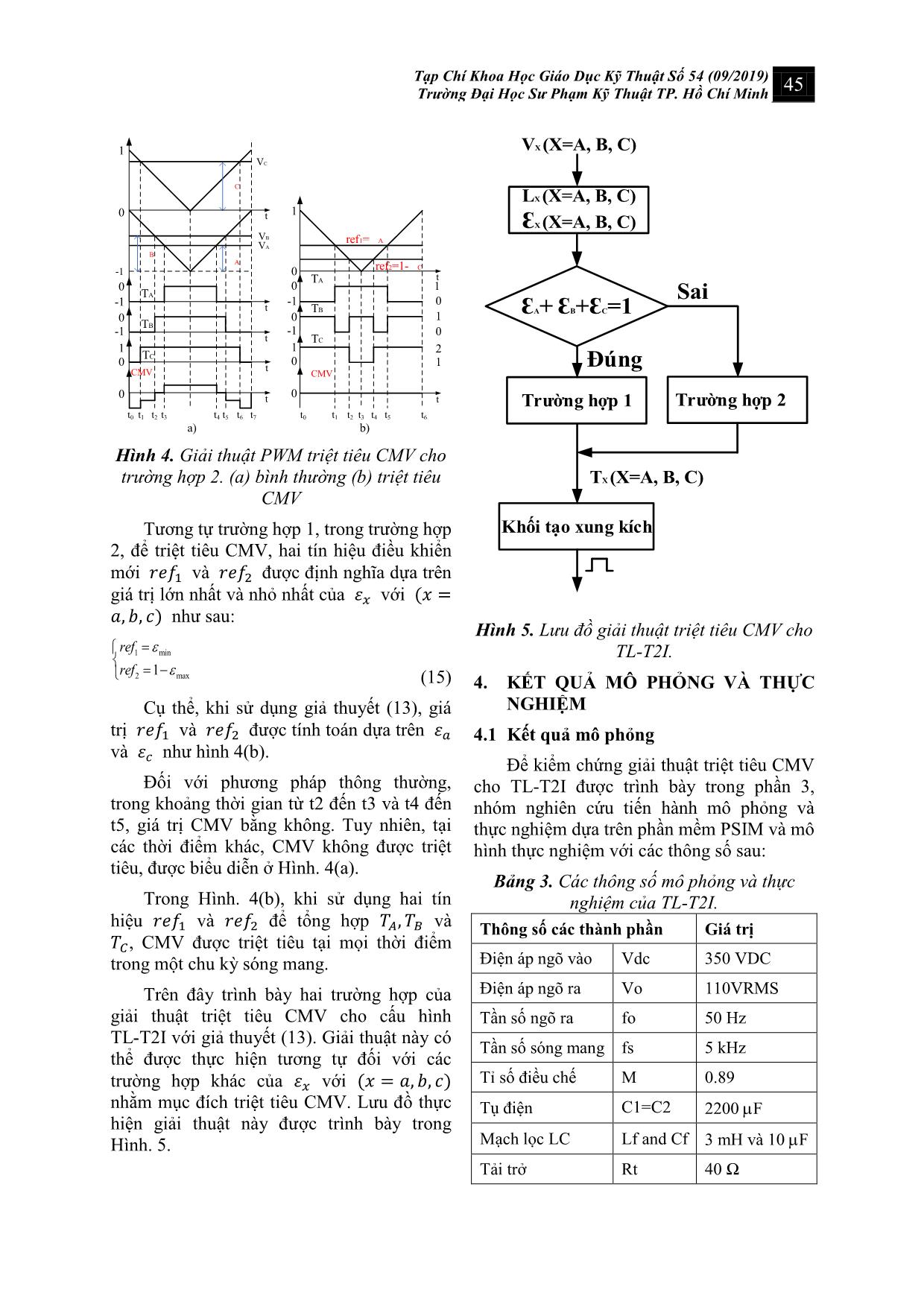

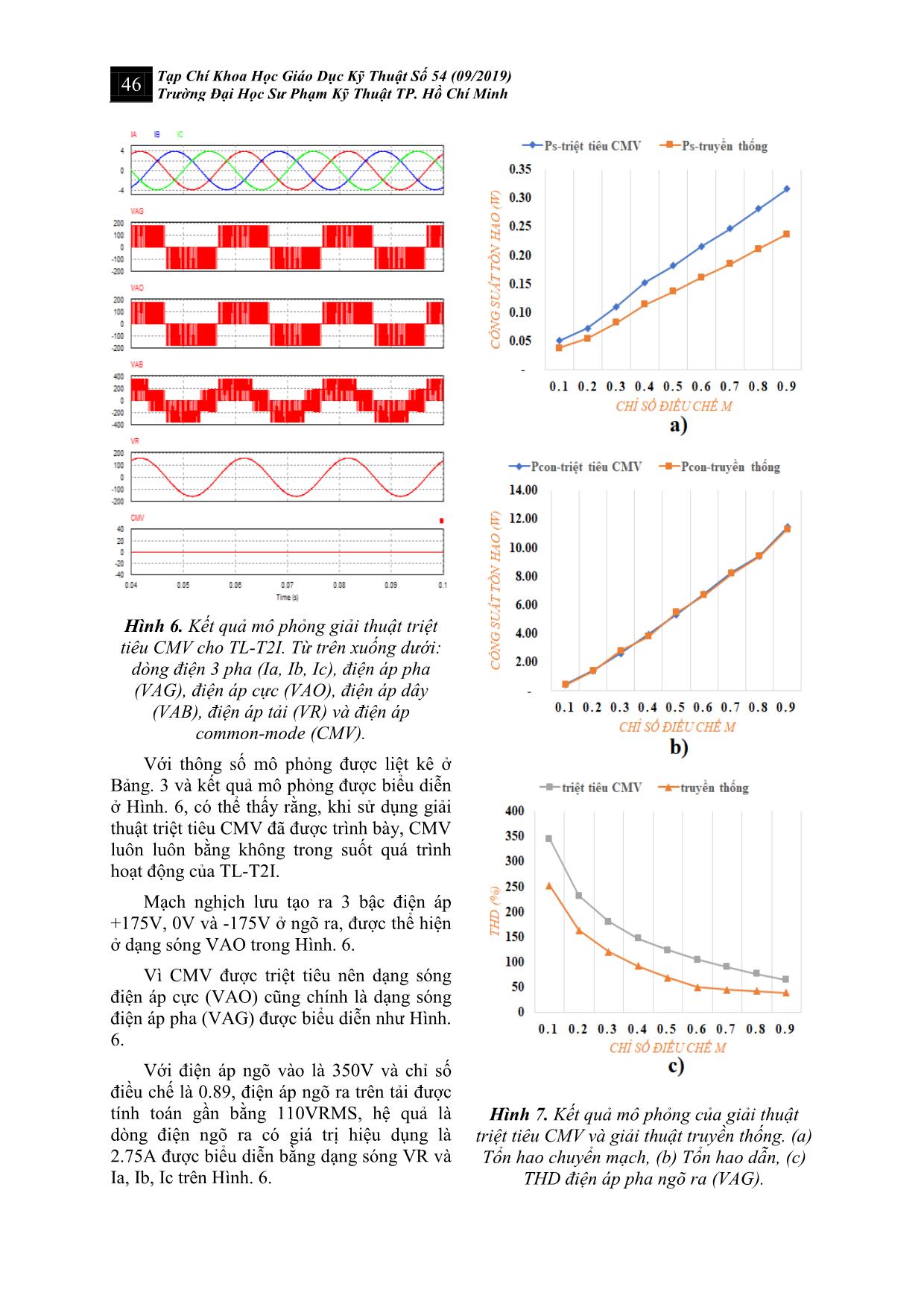

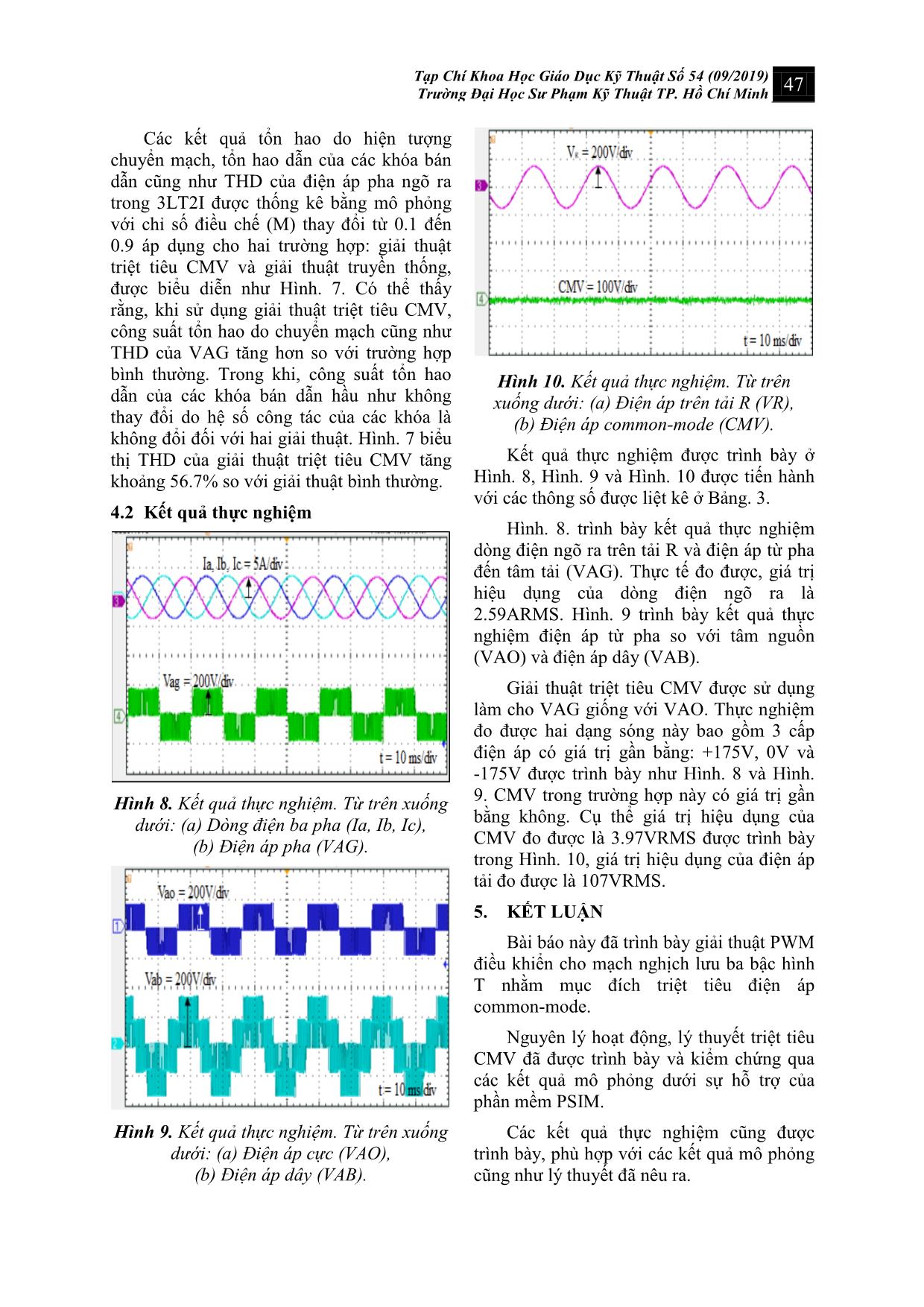

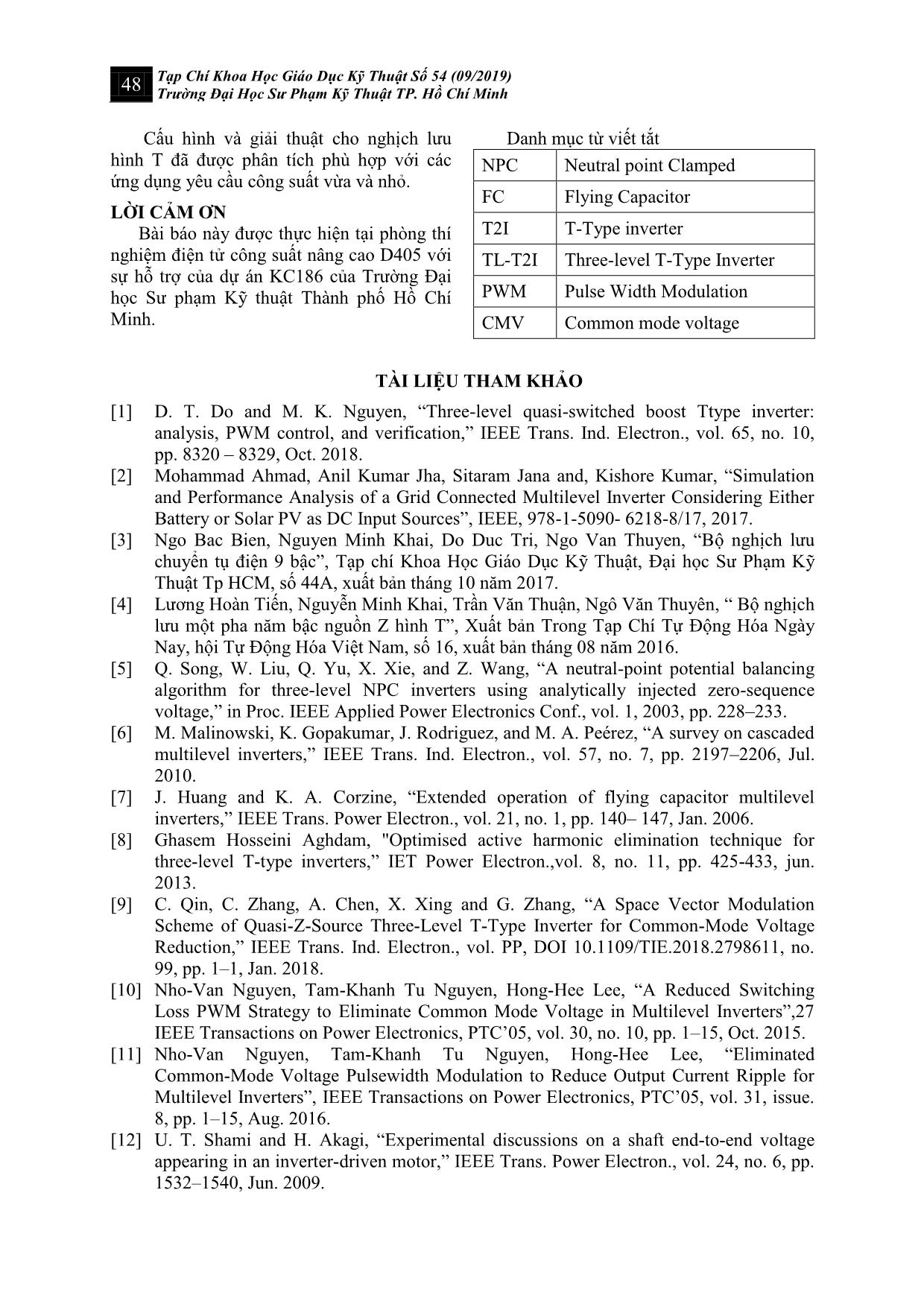

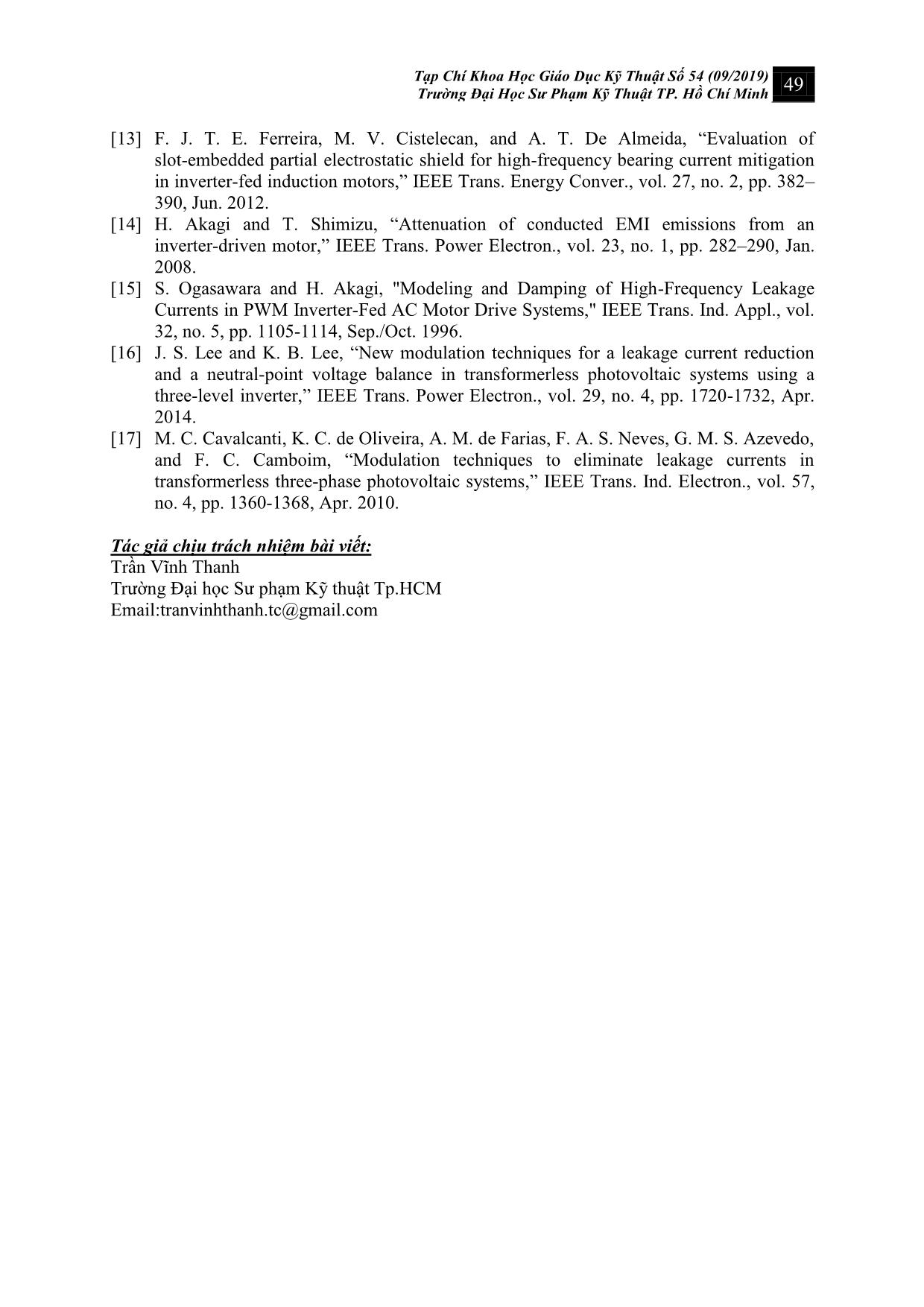

=í ïïïï - =ïïïî (1) Nhằm mục đích thuận lợi trong quá trình phân tích, biến TX được định nghĩa sao cho: . 2 dc XO X V U T= (2) Giá trị của TX được xác định qua phương trình sau: 1 2 3 1 1 0 1 1 1 X X X X if S T if S if S ì =ïïïï= =í ïïï - =ïî (3) Điện áp từ pha so với tâm tải được xác định dựa trên công thức sau: 2 1 1 1 . 1 2 1 . 3 1 1 2 AG AO BG BO CG CO V U V U V U é ù é ùé ù- - ê ú ê úê ú ê ú ê úê ú= - - ê ú ê úê ú ê ú ê úê ú- -ë ûë û ë û (4) Do tải sử dụng trong mạch nghịch lưu là cân bằng, nên: 0AG BG CGV V V+ + = (5) Từ các phương trình trên, CMV có thể được xác định thông qua điện áp ngõ ra ba pha của mạch nghịch lưu. Cụ thể, được biểu diễn bởi phương trình sau: . 3 6 AO BO CO A B C GO dc V V V T T T V V + + + + = = (6) Dựa vào công thức (6), tương ứng với mỗi giá trị của TA, TB, TC, luôn luôn xác định được một giá trị CMV. Bảng 2 liệt kê các giá trị CMV ứng với các trạng thái của TA, TB, TC. Như trình bày ở bảng 2, các giá trị [TA TB TC] là một trong các giá trị [-1 0 1], [-1 1 0], [0 -1 1], [0 0 0], [0 1 -1], [1 -1 0] và [1 0 -1] thì CMV bằng không. Từ đó, dễ dàng xác định được điều kiện để triệt tiêu CMV như sau: 0A B CT T T (7) Bảng 2. Giá trị CMV STT TA TB TC CMV 1 -1 -1 -1 -Vdc/2 2 -1 -1 0 -Vdc/3 3 -1 -1 1 -Vdc/6 4 -1 0 -1 -Vdc/3 5 -1 0 0 -Vdc/6 6 -1 0 1 0 7 -1 1 -1 -Vdc/6 8 -1 1 0 0 9 -1 1 1 +Vdc/6 10 0 -1 -1 -Vdc/3 11 0 -1 0 -Vdc/6 12 0 -1 1 0 13 0 0 -1 -Vdc/6 14 0 0 0 0 15 0 0 1 +Vdc/6 16 0 1 -1 0 17 0 1 0 +Vdc/6 18 0 1 1 +Vdc/3 44 Tạp Chí Khoa Học Giáo Dục Kỹ Thuật Số 54 (09/2019) Trường Đại Học Sư Phạm Kỹ Thuật TP. Hồ Chí Minh STT TA TB TC CMV 19 1 -1 -1 -Vdc/6 20 1 -1 0 0 21 1 -1 1 +Vdc/6 22 1 0 -1 0 23 1 0 0 +Vdc/6 24 1 0 1 +Vdc/3 25 1 1 -1 +Vdc/6 26 1 1 0 +Vdc/3 27 1 1 1 +Vdc/2 3.2. Phương pháp PWM triệt tiêu CMV Ba tín hiệu tham chiếu được sử dụng trong phương pháp PWM truyền thống để điều khiển tín hiệu đóng ngắt cho các khóa bán dẫn của T2I được biểu diễn như sau: ( ) ( ) ( ) sin sin 2 / 3 sin 2 / 3 A B C V m V m V m q q p q p ìï =ïïï = -í ïïï = +ïî (8) m là chỉ số điều chế và được xác định. 0 1m (9) Để dễ dàng trong việc giải thích, 𝐿𝑥và (𝑥 = 𝑎, 𝑏, 𝑐) được định nghĩa như sau: 1 0 0 0 x x x if V L if V (10) Với 𝐿𝑥 được định nghĩa bởi phương trình (10), sai số giữa 𝑉𝑥 và 𝐿𝑥 được xác định như sau: x x xV L (11) Trong đó, 𝜀𝑥 với (𝑥 = 𝑎, 𝑏, 𝑐) là sai số giữa 𝑉𝑥 và 𝐿𝑥. Từ (10) và (11) kết hợp với điều kiện tải cân bằng (𝑉𝐴𝐺 + 𝑉𝐵𝐺 + 𝑉𝐶𝐺 = 0). Dễ dàng chứng minh được: 1 1 2 2 A B C A B C A B C if L L L if L L L (12) Giải thuật triệt tiêu CMV cho T2I được giải thích thông qua hai trường hợp: 𝜀𝐴 + 𝜀𝐵 + 𝜀𝐶 = 1 và 𝜀𝐴 + 𝜀𝐵 + 𝜀𝐶 = 2. Không mất tính tổng quát, giả sử rằng A B C (13) Trường hợp 1: 𝜀𝐴 + 𝜀𝐵 + 𝜀𝐶 = 1 1 0 -1 1 0 1 0 0 -1 TA TB TC VC VB VA 1 ref1=1- A ref2= C 0 C A B t t t t t CMV 0 t0 t1 t2 t3 t4 t5 t6 t7 t t t t TA TB TC 1 0 1 0 0 -1 CMV t t0 t1 t2 t3 t4 t5 t6 0 a) b) Hình 3. Trường hợp 1 của giải thuật PWM triệt tiêu CMV. (a) bình thường (b) triệt tiêu CMV Trong trường hợp 1, để triệt tiêu CMV, hai tín hiệu điều khiển mới 𝑟𝑒𝑓1 và 𝑟𝑒𝑓2 được định nghĩa dựa trên giá trị lớn nhất và nhỏ nhất của 𝜀𝑥 với (𝑥 = 𝑎, 𝑏, 𝑐) như sau: 1 min 2 max 1ref ref (14) Với giả thuyết (13), trong trường hợp này, 𝑟𝑒𝑓1 và 𝑟𝑒𝑓2 được xác định thông qua 𝜀𝑎 và 𝜀𝑐 như Hình. 3(b). Khi đó, các tín hiệu 𝑇𝐴, 𝑇𝐵 và 𝑇𝐶 được tổng hợp dựa trên 𝑟𝑒𝑓1 và 𝑟𝑒𝑓2 theo quy luật được biểu diễn ở Hình. 3(b). Hình. 3(a) biễu diễn phương pháp PWM thông thường cho TL-T2I. Giá trị CMV đối với phương pháp này bị triệt tiêu trong khoảng thời gian từ t1 đến t2 và t5 đến t6, trong các khoảng thời gian còn lại luôn luôn tồn tại một giá trị CMV khác không. Đối với phương pháp PWM triệt tiêu CMV được trình bày ở Hình. 3(b), giá trị CMV bằng không trong suốt quá trình hoạt động của mạch nghịch lưu. Trường hợp 2: 𝜀𝐴 + 𝜀𝐵 + 𝜀𝐶 = 2 Tạp Chí Khoa Học Giáo Dục Kỹ Thuật Số 54 (09/2019) Trường Đại Học Sư Phạm Kỹ Thuật TP. Hồ Chí Minh 45 1 0 1 0 2 1 0 -1 0 -1 1 0 TA TB TC VC VB VA C B A t -1 1 0 t t t t CMV 0 t ref1= A ref2=1- C 0 -1 0 -1 1 0 0 1 t t0 t1 t2 t3 t4 t5 t6 t7 t0 t1 t2 t3 t4 t5 t6 a) b) TA TB TC CMV 0 Hình 4. Giải thuật PWM triệt tiêu CMV cho trường hợp 2. (a) bình thường (b) triệt tiêu CMV Tương tự trường hợp 1, trong trường hợp 2, để triệt tiêu CMV, hai tín hiệu điều khiển mới 𝑟𝑒𝑓1 và 𝑟𝑒𝑓2 được định nghĩa dựa trên giá trị lớn nhất và nhỏ nhất của 𝜀𝑥 với (𝑥 = 𝑎, 𝑏, 𝑐) như sau: 1 min 2 max1 ref ref (15) Cụ thể, khi sử dụng giả thuyết (13), giá trị 𝑟𝑒𝑓1 và 𝑟𝑒𝑓2 được tính toán dựa trên 𝜀𝑎 và 𝜀𝑐 như hình 4(b). Đối với phương pháp thông thường, trong khoảng thời gian từ t2 đến t3 và t4 đến t5, giá trị CMV bằng không. Tuy nhiên, tại các thời điểm khác, CMV không được triệt tiêu, được biểu diễn ở Hình. 4(a). Trong Hình. 4(b), khi sử dụng hai tín hiệu 𝑟𝑒𝑓1 và 𝑟𝑒𝑓2 để tổng hợp 𝑇𝐴, 𝑇𝐵 và 𝑇𝐶, CMV được triệt tiêu tại mọi thời điểm trong một chu kỳ sóng mang. Trên đây trình bày hai trường hợp của giải thuật triệt tiêu CMV cho cấu hình TL-T2I với giả thuyết (13). Giải thuật này có thể được thực hiện tương tự đối với các trường hợp khác của 𝜀𝑥 với (𝑥 = 𝑎, 𝑏, 𝑐) nhằm mục đích triệt tiêu CMV. Lưu đồ thực hiện giải thuật này được trình bày trong Hình. 5. Đúng VX (X=A, B, C) LX (X=A, B, C) ƐX (X=A, B, C) ƐA+ ƐB+ƐC=1 Trường hợp 1 Trường hợp 2 Sai TX (X=A, B, C) Khối tạo xung kích Hình 5. Lưu đồ giải thuật triệt tiêu CMV cho TL-T2I. 4. KẾT QUẢ MÔ PHỎNG VÀ THỰC NGHIỆM 4.1 Kết quả mô phỏng Để kiểm chứng giải thuật triệt tiêu CMV cho TL-T2I được trình bày trong phần 3, nhóm nghiên cứu tiến hành mô phỏng và thực nghiệm dựa trên phần mềm PSIM và mô hình thực nghiệm với các thông số sau: Bảng 3. Các thông số mô phỏng và thực nghiệm của TL-T2I. Thông số các thành phần Giá trị Điện áp ngõ vào Vdc 350 VDC Điện áp ngõ ra Vo 110VRMS Tần số ngõ ra fo 50 Hz Tần số sóng mang fs 5 kHz Tỉ số điều chế M 0.89 Tụ điện C1=C2 2200 F Mạch lọc LC Lf and Cf 3 mH và 10 F Tải trở Rt 40 Ω 46 Tạp Chí Khoa Học Giáo Dục Kỹ Thuật Số 54 (09/2019) Trường Đại Học Sư Phạm Kỹ Thuật TP. Hồ Chí Minh Hình 6. Kết quả mô phỏng giải thuật triệt tiêu CMV cho TL-T2I. Từ trên xuống dưới: dòng điện 3 pha (Ia, Ib, Ic), điện áp pha (VAG), điện áp cực (VAO), điện áp dây (VAB), điện áp tải (VR) và điện áp common-mode (CMV). Với thông số mô phỏng được liệt kê ở Bảng. 3 và kết quả mô phỏng được biểu diễn ở Hình. 6, có thể thấy rằng, khi sử dụng giải thuật triệt tiêu CMV đã được trình bày, CMV luôn luôn bằng không trong suốt quá trình hoạt động của TL-T2I. Mạch nghịch lưu tạo ra 3 bậc điện áp +175V, 0V và -175V ở ngõ ra, được thể hiện ở dạng sóng VAO trong Hình. 6. Vì CMV được triệt tiêu nên dạng sóng điện áp cực (VAO) cũng chính là dạng sóng điện áp pha (VAG) được biểu diễn như Hình. 6. Với điện áp ngõ vào là 350V và chỉ số điều chế là 0.89, điện áp ngõ ra trên tải được tính toán gần bằng 110VRMS, hệ quả là dòng điện ngõ ra có giá trị hiệu dụng là 2.75A được biểu diễn bằng dạng sóng VR và Ia, Ib, Ic trên Hình. 6. Hình 7. Kết quả mô phỏng của giải thuật triệt tiêu CMV và giải thuật truyền thống. (a) Tổn hao chuyển mạch, (b) Tổn hao dẫn, (c) THD điện áp pha ngõ ra (VAG). Tạp Chí Khoa Học Giáo Dục Kỹ Thuật Số 54 (09/2019) Trường Đại Học Sư Phạm Kỹ Thuật TP. Hồ Chí Minh 47 Các kết quả tổn hao do hiện tượng chuyển mạch, tổn hao dẫn của các khóa bán dẫn cũng như THD của điện áp pha ngõ ra trong 3LT2I được thống kê bằng mô phỏng với chỉ số điều chế (M) thay đổi từ 0.1 đến 0.9 áp dụng cho hai trường hợp: giải thuật triệt tiêu CMV và giải thuật truyền thống, được biểu diễn như Hình. 7. Có thể thấy rằng, khi sử dụng giải thuật triệt tiêu CMV, công suất tổn hao do chuyển mạch cũng như THD của VAG tăng hơn so với trường hợp bình thường. Trong khi, công suất tổn hao dẫn của các khóa bán dẫn hầu như không thay đổi do hệ số công tác của các khóa là không đổi đối với hai giải thuật. Hình. 7 biểu thị THD của giải thuật triệt tiêu CMV tăng khoảng 56.7% so với giải thuật bình thường. 4.2 Kết quả thực nghiệm Hình 8. Kết quả thực nghiệm. Từ trên xuống dưới: (a) Dòng điện ba pha (Ia, Ib, Ic), (b) Điện áp pha (VAG). Hình 9. Kết quả thực nghiệm. Từ trên xuống dưới: (a) Điện áp cực (VAO), (b) Điện áp dây (VAB). Hình 10. Kết quả thực nghiệm. Từ trên xuống dưới: (a) Điện áp trên tải R (VR), (b) Điện áp common-mode (CMV). Kết quả thực nghiệm được trình bày ở Hình. 8, Hình. 9 và Hình. 10 được tiến hành với các thông số được liệt kê ở Bảng. 3. Hình. 8. trình bày kết quả thực nghiệm dòng điện ngõ ra trên tải R và điện áp từ pha đến tâm tải (VAG). Thực tế đo được, giá trị hiệu dụng của dòng điện ngõ ra là 2.59ARMS. Hình. 9 trình bày kết quả thực nghiệm điện áp từ pha so với tâm nguồn (VAO) và điện áp dây (VAB). Giải thuật triệt tiêu CMV được sử dụng làm cho VAG giống với VAO. Thực nghiệm đo được hai dạng sóng này bao gồm 3 cấp điện áp có giá trị gần bằng: +175V, 0V và -175V được trình bày như Hình. 8 và Hình. 9. CMV trong trường hợp này có giá trị gần bằng không. Cụ thể giá trị hiệu dụng của CMV đo được là 3.97VRMS được trình bày trong Hình. 10, giá trị hiệu dụng của điện áp tải đo được là 107VRMS. 5. KẾT LUẬN Bài báo này đã trình bày giải thuật PWM điều khiển cho mạch nghịch lưu ba bậc hình T nhằm mục đích triệt tiêu điện áp common-mode. Nguyên lý hoạt động, lý thuyết triệt tiêu CMV đã được trình bày và kiểm chứng qua các kết quả mô phỏng dưới sự hỗ trợ của phần mềm PSIM. Các kết quả thực nghiệm cũng được trình bày, phù hợp với các kết quả mô phỏng cũng như lý thuyết đã nêu ra. 48 Tạp Chí Khoa Học Giáo Dục Kỹ Thuật Số 54 (09/2019) Trường Đại Học Sư Phạm Kỹ Thuật TP. Hồ Chí Minh Cấu hình và giải thuật cho nghịch lưu hình T đã được phân tích phù hợp với các ứng dụng yêu cầu công suất vừa và nhỏ. LỜI CẢM ƠN Bài báo này được thực hiện tại phòng thí nghiệm điện tử công suất nâng cao D405 với sự hỗ trợ của dự án KC186 của Trường Đại học Sư phạm Kỹ thuật Thành phố Hồ Chí Minh. Danh mục từ viết tắt NPC Neutral point Clamped FC Flying Capacitor T2I T-Type inverter TL-T2I Three-level T-Type Inverter PWM Pulse Width Modulation CMV Common mode voltage TÀI LIỆU THAM KHẢO [1] D. T. Do and M. K. Nguyen, “Three-level quasi-switched boost Ttype inverter: analysis, PWM control, and verification,” IEEE Trans. Ind. Electron., vol. 65, no. 10, pp. 8320 – 8329, Oct. 2018. [2] Mohammad Ahmad, Anil Kumar Jha, Sitaram Jana and, Kishore Kumar, “Simulation and Performance Analysis of a Grid Connected Multilevel Inverter Considering Either Battery or Solar PV as DC Input Sources”, IEEE, 978-1-5090- 6218-8/17, 2017. [3] Ngo Bac Bien, Nguyen Minh Khai, Do Duc Tri, Ngo Van Thuyen, “Bộ nghịch lưu chuyển tụ điện 9 bậc”, Tạp chí Khoa Học Giáo Dục Kỹ Thuật, Đại học Sư Phạm Kỹ Thuật Tp HCM, số 44A, xuất bản tháng 10 năm 2017. [4] Lương Hoàn Tiến, Nguyễn Minh Khai, Trần Văn Thuận, Ngô Văn Thuyên, “ Bộ nghịch lưu một pha năm bậc nguồn Z hình T”, Xuất bản Trong Tạp Chí Tự Động Hóa Ngày Nay, hội Tự Động Hóa Việt Nam, số 16, xuất bản tháng 08 năm 2016. [5] Q. Song, W. Liu, Q. Yu, X. Xie, and Z. Wang, “A neutral-point potential balancing algorithm for three-level NPC inverters using analytically injected zero-sequence voltage,” in Proc. IEEE Applied Power Electronics Conf., vol. 1, 2003, pp. 228–233. [6] M. Malinowski, K. Gopakumar, J. Rodriguez, and M. A. Peérez, “A survey on cascaded multilevel inverters,” IEEE Trans. Ind. Electron., vol. 57, no. 7, pp. 2197–2206, Jul. 2010. [7] J. Huang and K. A. Corzine, “Extended operation of flying capacitor multilevel inverters,” IEEE Trans. Power Electron., vol. 21, no. 1, pp. 140– 147, Jan. 2006. [8] Ghasem Hosseini Aghdam, "Optimised active harmonic elimination technique for three-level T-type inverters,” IET Power Electron.,vol. 8, no. 11, pp. 425-433, jun. 2013. [9] C. Qin, C. Zhang, A. Chen, X. Xing and G. Zhang, “A Space Vector Modulation Scheme of Quasi-Z-Source Three-Level T-Type Inverter for Common-Mode Voltage Reduction,” IEEE Trans. Ind. Electron., vol. PP, DOI 10.1109/TIE.2018.2798611, no. 99, pp. 1–1, Jan. 2018. [10] Nho-Van Nguyen, Tam-Khanh Tu Nguyen, Hong-Hee Lee, “A Reduced Switching Loss PWM Strategy to Eliminate Common Mode Voltage in Multilevel Inverters”,27 IEEE Transactions on Power Electronics, PTC’05, vol. 30, no. 10, pp. 1–15, Oct. 2015. [11] Nho-Van Nguyen, Tam-Khanh Tu Nguyen, Hong-Hee Lee, “Eliminated Common-Mode Voltage Pulsewidth Modulation to Reduce Output Current Ripple for Multilevel Inverters”, IEEE Transactions on Power Electronics, PTC’05, vol. 31, issue. 8, pp. 1–15, Aug. 2016. [12] U. T. Shami and H. Akagi, “Experimental discussions on a shaft end-to-end voltage appearing in an inverter-driven motor,” IEEE Trans. Power Electron., vol. 24, no. 6, pp. 1532–1540, Jun. 2009. Tạp Chí Khoa Học Giáo Dục Kỹ Thuật Số 54 (09/2019) Trường Đại Học Sư Phạm Kỹ Thuật TP. Hồ Chí Minh 49 [13] F. J. T. E. Ferreira, M. V. Cistelecan, and A. T. De Almeida, “Evaluation of slot-embedded partial electrostatic shield for high-frequency bearing current mitigation in inverter-fed induction motors,” IEEE Trans. Energy Conver., vol. 27, no. 2, pp. 382– 390, Jun. 2012. [14] H. Akagi and T. Shimizu, “Attenuation of conducted EMI emissions from an inverter-driven motor,” IEEE Trans. Power Electron., vol. 23, no. 1, pp. 282–290, Jan. 2008. [15] S. Ogasawara and H. Akagi, "Modeling and Damping of High-Frequency Leakage Currents in PWM Inverter-Fed AC Motor Drive Systems," IEEE Trans. Ind. Appl., vol. 32, no. 5, pp. 1105-1114, Sep./Oct. 1996. [16] J. S. Lee and K. B. Lee, “New modulation techniques for a leakage current reduction and a neutral-point voltage balance in transformerless photovoltaic systems using a three-level inverter,” IEEE Trans. Power Electron., vol. 29, no. 4, pp. 1720-1732, Apr. 2014. [17] M. C. Cavalcanti, K. C. de Oliveira, A. M. de Farias, F. A. S. Neves, G. M. S. Azevedo, and F. C. Camboim, “Modulation techniques to eliminate leakage currents in transformerless three-phase photovoltaic systems,” IEEE Trans. Ind. Electron., vol. 57, no. 4, pp. 1360-1368, Apr. 2010. Tác giả chịu trách nhiệm bài viết: Trần Vĩnh Thanh Trường Đại học Sư phạm Kỹ thuật Tp.HCM Email:tranvinhthanh.tc@gmail.com

File đính kèm:

giai_thuat_pwm_cho_nghich_luu_hinh_t_ba_bac_de_triet_tieu_di.pdf

giai_thuat_pwm_cho_nghich_luu_hinh_t_ba_bac_de_triet_tieu_di.pdf