Central Improvement of Voltage Sags in the IEEE 33-Bus Distribution System by a Number of D-STATCOMS

The paper introduces a novel method for “central improvement” of voltage sags due to short-circuits in

distribution system using multiples of D-Statcoms. D-Statcom’s effectiveness for voltage sag mitigation is

modeled basing on the method of Thevenin’s superimposition for the problem of short-circuit calculation in

distribution systems. The paper newly considers the case of using a multiple of D-Statcoms with a proposed

voltage compensating principle that can be practical for large size of distribution system. A multiple of DStatcoms are optimally located and sized on the basis of minimizing the system bus voltage deviation with

regard to the constraint of D-Statcom’s size. The paper uses the IEEE 33-buses distribution feeder as the test

system for voltage sag simulation and results discussion.

Trang 1

Trang 2

Trang 3

Trang 4

Trang 5

Trang 6

Tóm tắt nội dung tài liệu: Central Improvement of Voltage Sags in the IEEE 33-Bus Distribution System by a Number of D-STATCOMS

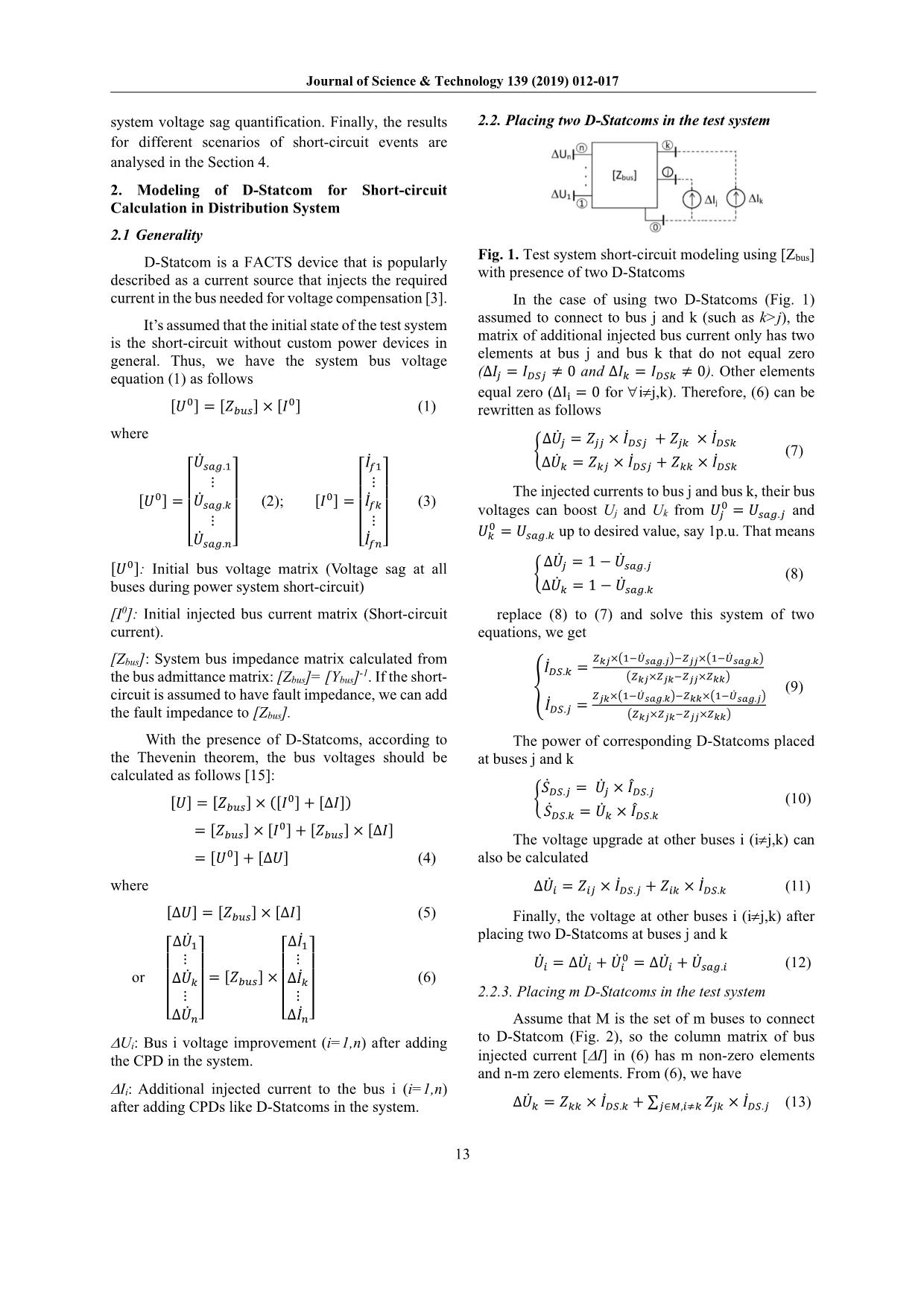

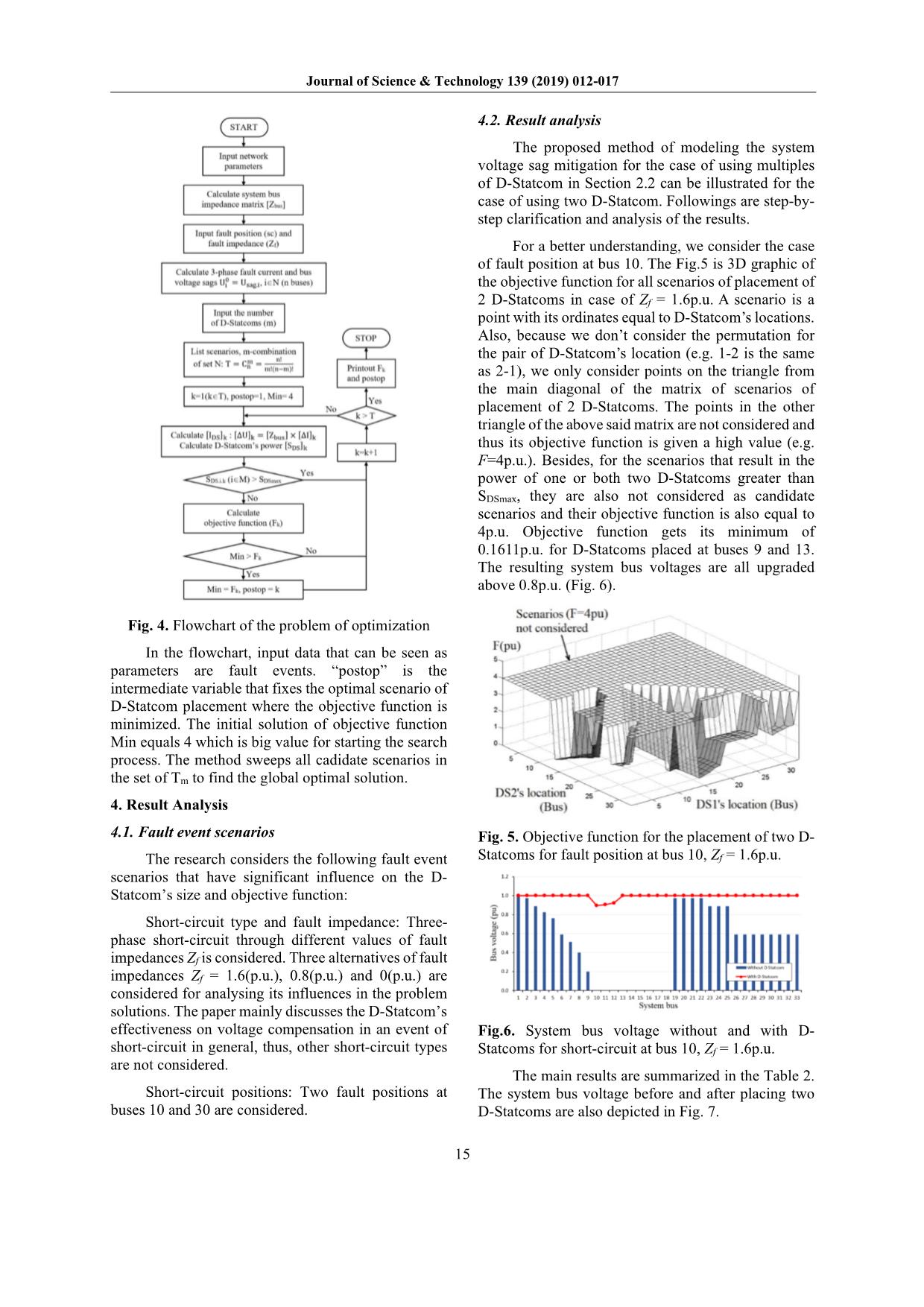

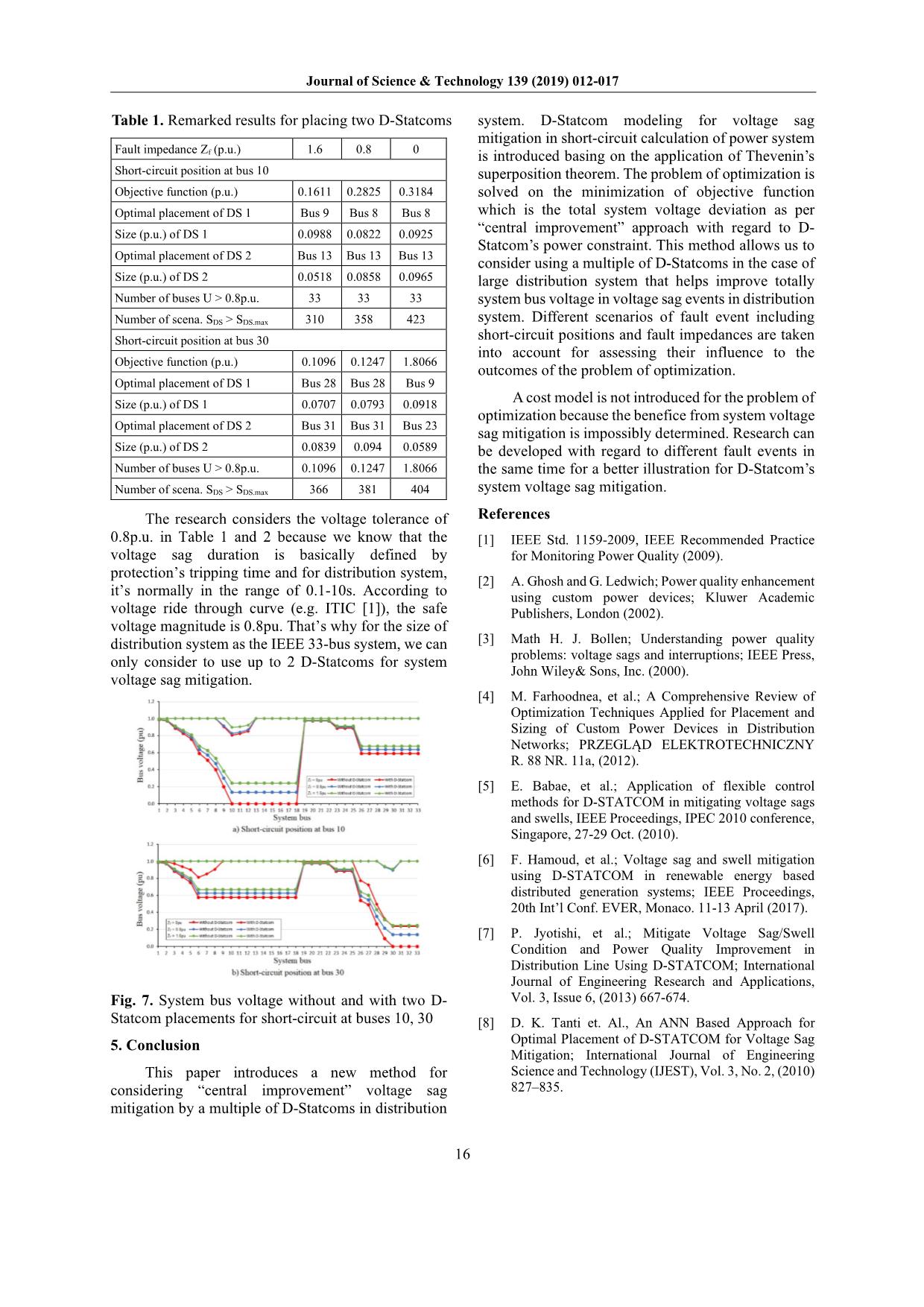

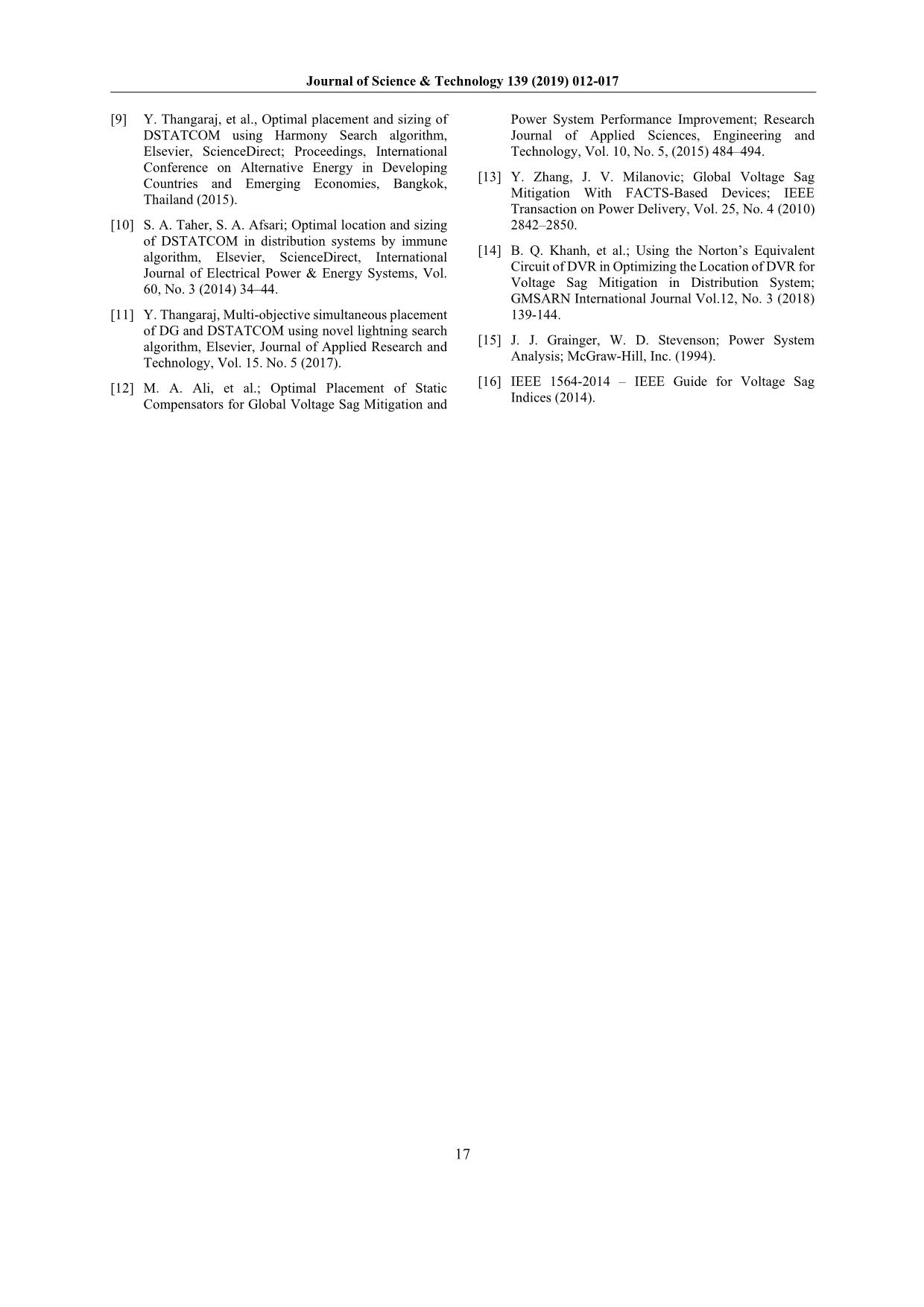

n the case of using two D-Statcoms (Fig. 1) assumed to connect to bus j and k (such as k>j), the matrix of additional injected bus current only has two elements at bus j and bus k that do not equal zero (∆𝐼𝐼𝑗𝑗 = 𝐼𝐼𝐷𝐷𝐷𝐷𝑗𝑗 ≠ 0 and ∆𝐼𝐼𝑘𝑘 = 𝐼𝐼𝐷𝐷𝐷𝐷𝑘𝑘 ≠ 0). Other elements equal zero (∆Ii = 0 for ∀i≠j,k). Therefore, (6) can be rewritten as follows � ∆�̇�𝑈𝑗𝑗 = 𝑍𝑍𝑗𝑗𝑗𝑗 × 𝐼𝐼�̇�𝐷𝐷𝐷𝑗𝑗 + 𝑍𝑍𝑗𝑗𝑘𝑘 × 𝐼𝐼�̇�𝐷𝐷𝐷𝑘𝑘 ∆�̇�𝑈𝑘𝑘 = 𝑍𝑍𝑘𝑘𝑗𝑗 × 𝐼𝐼�̇�𝐷𝐷𝐷𝑗𝑗 + 𝑍𝑍𝑘𝑘𝑘𝑘 × 𝐼𝐼�̇�𝐷𝐷𝐷𝑘𝑘 (7) The injected currents to bus j and bus k, their bus voltages can boost Uj and Uk from 𝑈𝑈𝑗𝑗0 = 𝑈𝑈𝑏𝑏𝑠𝑠𝑠𝑠.𝑗𝑗 and 𝑈𝑈𝑘𝑘 0 = 𝑈𝑈𝑏𝑏𝑠𝑠𝑠𝑠.𝑘𝑘 up to desired value, say 1p.u. That means � ∆�̇�𝑈𝑗𝑗 = 1 − �̇�𝑈𝑏𝑏𝑠𝑠𝑠𝑠.𝑗𝑗 ∆�̇�𝑈𝑘𝑘 = 1 − �̇�𝑈𝑏𝑏𝑠𝑠𝑠𝑠.𝑘𝑘 (8) replace (8) to (7) and solve this system of two equations, we get � 𝐼𝐼�̇�𝐷𝐷𝐷.𝑘𝑘 = 𝑍𝑍𝑘𝑘𝑘𝑘×�1−�̇�𝑈𝑠𝑠𝑠𝑠𝑠𝑠.𝑘𝑘�−𝑍𝑍𝑘𝑘𝑘𝑘×�1−�̇�𝑈𝑠𝑠𝑠𝑠𝑠𝑠.𝑘𝑘��𝑍𝑍𝑘𝑘𝑘𝑘×𝑍𝑍𝑘𝑘𝑘𝑘−𝑍𝑍𝑘𝑘𝑘𝑘×𝑍𝑍𝑘𝑘𝑘𝑘� 𝐼𝐼�̇�𝐷𝐷𝐷.𝑗𝑗 = 𝑍𝑍𝑘𝑘𝑘𝑘×�1−�̇�𝑈𝑠𝑠𝑠𝑠𝑠𝑠.𝑘𝑘�−𝑍𝑍𝑘𝑘𝑘𝑘×�1−�̇�𝑈𝑠𝑠𝑠𝑠𝑠𝑠.𝑘𝑘��𝑍𝑍𝑘𝑘𝑘𝑘×𝑍𝑍𝑘𝑘𝑘𝑘−𝑍𝑍𝑘𝑘𝑘𝑘×𝑍𝑍𝑘𝑘𝑘𝑘� (9) The power of corresponding D-Statcoms placed at buses j and k ��̇�𝑆𝐷𝐷𝐷𝐷.𝑗𝑗 = �̇�𝑈𝑗𝑗 × 𝐼𝐼𝐷𝐷𝐷𝐷.𝑗𝑗 �̇�𝑆𝐷𝐷𝐷𝐷.𝑘𝑘 = �̇�𝑈𝑘𝑘 × 𝐼𝐼𝐷𝐷𝐷𝐷.𝑘𝑘 (10) The voltage upgrade at other buses i (i≠j,k) can also be calculated ∆�̇�𝑈𝑖𝑖 = 𝑍𝑍𝑖𝑖𝑗𝑗 × 𝐼𝐼�̇�𝐷𝐷𝐷.𝑗𝑗 + 𝑍𝑍𝑖𝑖𝑘𝑘 × 𝐼𝐼�̇�𝐷𝐷𝐷.𝑘𝑘 (11) Finally, the voltage at other buses i (i≠j,k) after placing two D-Statcoms at buses j and k �̇�𝑈𝑖𝑖 = ∆�̇�𝑈𝑖𝑖 + �̇�𝑈𝑖𝑖0 = ∆�̇�𝑈𝑖𝑖 + �̇�𝑈𝑏𝑏𝑠𝑠𝑠𝑠.𝑖𝑖 (12) 2.2.3. Placing m D-Statcoms in the test system Assume that M is the set of m buses to connect to D-Statcom (Fig. 2), so the column matrix of bus injected current [∆I] in (6) has m non-zero elements and n-m zero elements. From (6), we have ∆�̇�𝑈𝑘𝑘 = 𝑍𝑍𝑘𝑘𝑘𝑘 × 𝐼𝐼�̇�𝐷𝐷𝐷.𝑘𝑘 + ∑ 𝑍𝑍𝑗𝑗𝑘𝑘 × 𝐼𝐼�̇�𝐷𝐷𝐷.𝑗𝑗𝑗𝑗∈𝑀𝑀,𝑖𝑖≠𝑘𝑘 (13) Journal of Science & Technology 139 (2019) 012-017 14 For bus k, k∈M, the rule of voltage compensation is as follows ∆�̇�𝑈𝑘𝑘 = �̇�𝑈𝑘𝑘 − �̇�𝑈𝑏𝑏𝑠𝑠𝑠𝑠.𝑘𝑘 = 1 − �̇�𝑈𝑏𝑏𝑠𝑠𝑠𝑠.𝑘𝑘 (14) Replace (14) to (13) we have m equations to calculate m variables IDS.k of m D-Statcoms. Solve this system of m equations, we get m values of IDS.k. Replace m values of IDS.k in (6), we can calculate the voltage upgrade of n-m buses without connecting to D-Statcoms ∆�̇�𝑈𝑖𝑖 = ∑ 𝑍𝑍𝑖𝑖𝑘𝑘 × 𝐼𝐼�̇�𝐷𝐷𝐷𝑘𝑘𝑛𝑛𝑖𝑖=1 (15) Finally, we calculate voltages of all buses in the system after placing m D-Statcoms similar to (12). Fig. 2. Test system short-circuit modeling using [Zbus] with the presence of m D-Statcoms (m<n) 3. Problem Definition 3.1. IEEE 33-Bus Distribution System This paper uses the IEEE 33-bus distribution feeder (Fig. 3) as the test system for the research. It features a balanced three-phase distribution system, with three-phase lines and loads. This research assumes: base values are 11kV; 100MVA. The system voltage is 1pu. System impedance is 0.1pu. Fig.3. IEEE 33-bus distribution feeder 3.2. Short-circuit calculation According to point 2.2a, Section 2, we assume the initial status of the test system is a short-circuit in the system. The paper considers a number of short- circuit positions with different fault impedance Zf. Three-phase short-circuit calculations are performed in Matlab using the method of bus impedance matrix and resulting bus voltage sags can be calculated. With the calculation of system bus voltage in the short-circuit event with the presence of D-Statcom, we can define the problem of optimization as follows. 3.3. The problem of optimization 3.3.1. Objective function and constraints In this research, the problem of optimizing the location and size of a multiple D-Statcoms in the test system where the objective function is to minimize the total system voltage deviation, is established. It’s seen as the index of system voltage sag energy [16]. 𝐹𝐹 = �∑ �𝑈𝑈𝑟𝑟𝑟𝑟𝑓𝑓 − 𝑈𝑈𝑖𝑖�2𝑛𝑛𝑖𝑖=1 ⇒ 𝑀𝑀𝑀𝑀𝑀𝑀 (16) where Uref: Reference system voltage, equals 1p.u. Ui: Bus i voltage calculated in (14). For this problem of optimization, the main variable is the scenario of positions (buses) where D- Statcoms are connected. We can see each main variable as a string of m bus numbers with D-Statcom connection out of n buses of the test system. Therefore, the total scenarios of D-Statcom placement to be tested is the m-combination of set N (n=33): 𝑇𝑇𝑚𝑚 = 𝐶𝐶𝑛𝑛𝑚𝑚 = 33!𝑚𝑚!×(33−𝑚𝑚)! (17) For example, if we consider the placement of 2 D-Statcoms in the test system, m=2, the total scenarios for placing these two D-Statcoms is as follows 𝑇𝑇2 = 𝐶𝐶332 = 33!2!×(33−2)! = 528. Each candidate scenario to be tested is a pair of buses number k and l out from 33 buses where the two D-Statcoms are connected (e.g. 1,2; 1,3;). The only constraint is that the size of D-Statcom is limited to a certain maximum value (SDS.max). In this research D-Statcom’s size is not greater than 0.1p.u. (or 10MVA). For each bus where D-Statcom can be connected, if SDS > SDS.max, this bus is not qualified for D-Statcom placement. 3.3.2. Problem solving For such a problem of optimization, under the assumption of a fault event, the objective function and the constraint are always determined. So, we use the method of direct search and testing all candidate scenarios in the set of scenarios of Tm. The flowchart of solving this problem in Matlab is given in Fig. 4. Each candidate scenario k defines positions where D-Statcoms are connected. According to this method, we have to determine the whole set of candidate scenarios Tm (17). For a candidate scenario k, we can calculate the D-Statcom’s power (size) and objective function Fk. We can sweep all candidate scenarios in Tm for constraint verification and minimization of the objective function. Journal of Science & Technology 139 (2019) 012-017 15 Fig. 4. Flowchart of the problem of optimization In the flowchart, input data that can be seen as parameters are fault events. “postop” is the intermediate variable that fixes the optimal scenario of D-Statcom placement where the objective function is minimized. The initial solution of objective function Min equals 4 which is big value for starting the search process. The method sweeps all cadidate scenarios in the set of Tm to find the global optimal solution. 4. Result Analysis 4.1. Fault event scenarios The research considers the following fault event scenarios that have significant influence on the D- Statcom’s size and objective function: Short-circuit type and fault impedance: Three- phase short-circuit through different values of fault impedances Zf is considered. Three alternatives of fault impedances Zf = 1.6(p.u.), 0.8(p.u.) and 0(p.u.) are considered for analysing its influences in the problem solutions. The paper mainly discusses the D-Statcom’s effectiveness on voltage compensation in an event of short-circuit in general, thus, other short-circuit types are not considered. Short-circuit positions: Two fault positions at buses 10 and 30 are considered. 4.2. Result analysis The proposed method of modeling the system voltage sag mitigation for the case of using multiples of D-Statcom in Section 2.2 can be illustrated for the case of using two D-Statcom. Followings are step-by- step clarification and analysis of the results. For a better understanding, we consider the case of fault position at bus 10. The Fig.5 is 3D graphic of the objective function for all scenarios of placement of 2 D-Statcoms in case of Zf = 1.6p.u. A scenario is a point with its ordinates equal to D-Statcom’s locations. Also, because we don’t consider the permutation for the pair of D-Statcom’s location (e.g. 1-2 is the same as 2-1), we only consider points on the triangle from the main diagonal of the matrix of scenarios of placement of 2 D-Statcoms. The points in the other triangle of the above said matrix are not considered and thus its objective function is given a high value (e.g. F=4p.u.). Besides, for the scenarios that result in the power of one or both two D-Statcoms greater than SDSmax, they are also not considered as candidate scenarios and their objective function is also equal to 4p.u. Objective function gets its minimum of 0.1611p.u. for D-Statcoms placed at buses 9 and 13. The resulting system bus voltages are all upgraded above 0.8p.u. (Fig. 6). Fig. 5. Objective function for the placement of two D- Statcoms for fault position at bus 10, Zf = 1.6p.u. Fig.6. System bus voltage without and with D- Statcoms for short-circuit at bus 10, Zf = 1.6p.u. The main results are summarized in the Table 2. The system bus voltage before and after placing two D-Statcoms are also depicted in Fig. 7. Journal of Science & Technology 139 (2019) 012-017 16 Table 1. Remarked results for placing two D-Statcoms Fault impedance Zf (p.u.) 1.6 0.8 0 Short-circuit position at bus 10 Objective function (p.u.) 0.1611 0.2825 0.3184 Optimal placement of DS 1 Bus 9 Bus 8 Bus 8 Size (p.u.) of DS 1 0.0988 0.0822 0.0925 Optimal placement of DS 2 Bus 13 Bus 13 Bus 13 Size (p.u.) of DS 2 0.0518 0.0858 0.0965 Number of buses U > 0.8p.u. 33 33 33 Number of scena. SDS > SDS.max 310 358 423 Short-circuit position at bus 30 Objective function (p.u.) 0.1096 0.1247 1.8066 Optimal placement of DS 1 Bus 28 Bus 28 Bus 9 Size (p.u.) of DS 1 0.0707 0.0793 0.0918 Optimal placement of DS 2 Bus 31 Bus 31 Bus 23 Size (p.u.) of DS 2 0.0839 0.094 0.0589 Number of buses U > 0.8p.u. 0.1096 0.1247 1.8066 Number of scena. SDS > SDS.max 366 381 404 The research considers the voltage tolerance of 0.8p.u. in Table 1 and 2 because we know that the voltage sag duration is basically defined by protection’s tripping time and for distribution system, it’s normally in the range of 0.1-10s. According to voltage ride through curve (e.g. ITIC [1]), the safe voltage magnitude is 0.8pu. That’s why for the size of distribution system as the IEEE 33-bus system, we can only consider to use up to 2 D-Statcoms for system voltage sag mitigation. Fig. 7. System bus voltage without and with two D- Statcom placements for short-circuit at buses 10, 30 5. Conclusion This paper introduces a new method for considering “central improvement” voltage sag mitigation by a multiple of D-Statcoms in distribution system. D-Statcom modeling for voltage sag mitigation in short-circuit calculation of power system is introduced basing on the application of Thevenin’s superposition theorem. The problem of optimization is solved on the minimization of objective function which is the total system voltage deviation as per “central improvement” approach with regard to D- Statcom’s power constraint. This method allows us to consider using a multiple of D-Statcoms in the case of large distribution system that helps improve totally system bus voltage in voltage sag events in distribution system. Different scenarios of fault event including short-circuit positions and fault impedances are taken into account for assessing their influence to the outcomes of the problem of optimization. A cost model is not introduced for the problem of optimization because the benefice from system voltage sag mitigation is impossibly determined. Research can be developed with regard to different fault events in the same time for a better illustration for D-Statcom’s system voltage sag mitigation. References [1] IEEE Std. 1159-2009, IEEE Recommended Practice for Monitoring Power Quality (2009). [2] A. Ghosh and G. Ledwich; Power quality enhancement using custom power devices; Kluwer Academic Publishers, London (2002). [3] Math H. J. Bollen; Understanding power quality problems: voltage sags and interruptions; IEEE Press, John Wiley& Sons, Inc. (2000). [4] M. Farhoodnea, et al.; A Comprehensive Review of Optimization Techniques Applied for Placement and Sizing of Custom Power Devices in Distribution Networks; PRZEGLĄD ELEKTROTECHNICZNY R. 88 NR. 11a, (2012). [5] E. Babae, et al.; Application of flexible control methods for D-STATCOM in mitigating voltage sags and swells, IEEE Proceedings, IPEC 2010 conference, Singapore, 27-29 Oct. (2010). [6] F. Hamoud, et al.; Voltage sag and swell mitigation using D-STATCOM in renewable energy based distributed generation systems; IEEE Proceedings, 20th Int’l Conf. EVER, Monaco. 11-13 April (2017). [7] P. Jyotishi, et al.; Mitigate Voltage Sag/Swell Condition and Power Quality Improvement in Distribution Line Using D-STATCOM; International Journal of Engineering Research and Applications, Vol. 3, Issue 6, (2013) 667-674. [8] D. K. Tanti et. Al., An ANN Based Approach for Optimal Placement of D-STATCOM for Voltage Sag Mitigation; International Journal of Engineering Science and Technology (IJEST), Vol. 3, No. 2, (2010) 827–835. Journal of Science & Technology 139 (2019) 012-017 17 [9] Y. Thangaraj, et al., Optimal placement and sizing of DSTATCOM using Harmony Search algorithm, Elsevier, ScienceDirect; Proceedings, International Conference on Alternative Energy in Developing Countries and Emerging Economies, Bangkok, Thailand (2015). [10] S. A. Taher, S. A. Afsari; Optimal location and sizing of DSTATCOM in distribution systems by immune algorithm, Elsevier, ScienceDirect, International Journal of Electrical Power & Energy Systems, Vol. 60, No. 3 (2014) 34–44. [11] Y. Thangaraj, Multi-objective simultaneous placement of DG and DSTATCOM using novel lightning search algorithm, Elsevier, Journal of Applied Research and Technology, Vol. 15. No. 5 (2017). [12] M. A. Ali, et al.; Optimal Placement of Static Compensators for Global Voltage Sag Mitigation and Power System Performance Improvement; Research Journal of Applied Sciences, Engineering and Technology, Vol. 10, No. 5, (2015) 484–494. [13] Y. Zhang, J. V. Milanovic; Global Voltage Sag Mitigation With FACTS-Based Devices; IEEE Transaction on Power Delivery, Vol. 25, No. 4 (2010) 2842–2850. [14] B. Q. Khanh, et al.; Using the Norton’s Equivalent Circuit of DVR in Optimizing the Location of DVR for Voltage Sag Mitigation in Distribution System; GMSARN International Journal Vol.12, No. 3 (2018) 139-144. [15] J. J. Grainger, W. D. Stevenson; Power System Analysis; McGraw-Hill, Inc. (1994). [16] IEEE 1564-2014 – IEEE Guide for Voltage Sag Indices (2014).

File đính kèm:

central_improvement_of_voltage_sags_in_the_ieee_33_bus_distr.pdf

central_improvement_of_voltage_sags_in_the_ieee_33_bus_distr.pdf