Câu hỏi và bài tập Cấu kiện điện tử

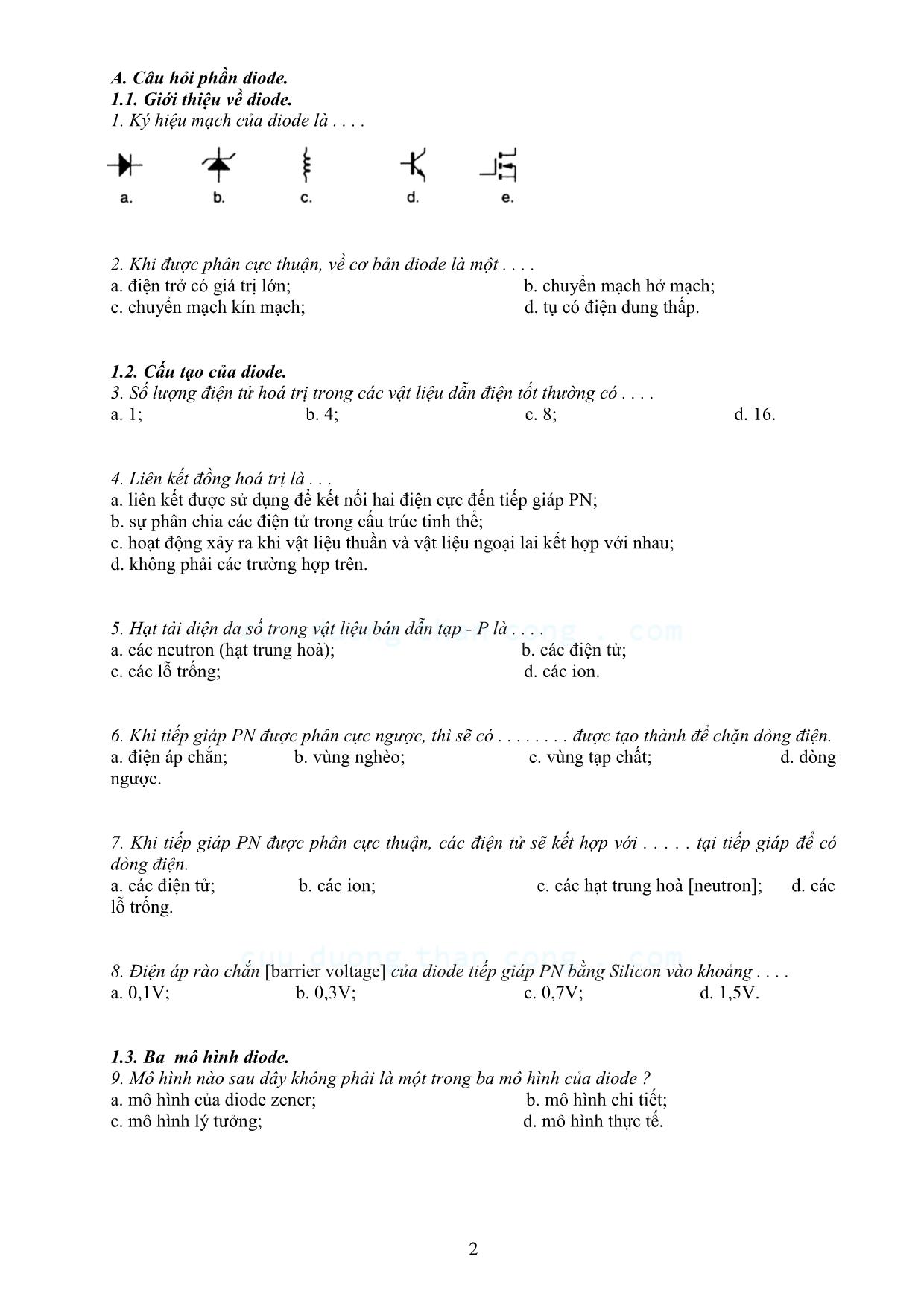

Cấu tạo của diode.

3. Số lượng điện tử hoá trị trong các vật liệu dẫn điện tốt thường có . . . .

a. 1; b. 4; c. 8; d. 16.

4. Liên kết đồng hoá trị là . . .

a. liên kết được sử dụng để kết nối hai điện cực đến tiếp giáp PN;

b. sự phân chia các điện tử trong cấu trúc tinh thể;

c. hoạt động xảy ra khi vật liệu thuần và vật liệu ngoại lai kết hợp với nhau;

d. không phải các trường hợp trên.

5. Hạt tải điện đa số trong vật liệu bán dẫn tạp - P là . . . .

a. các neutron (hạt trung hoà); b. các điện tử;

c. các lỗ trống; d. các ion.

6. Khi tiếp giáp PN được phân cực ngược, thì sẽ có . . . . . . . . được tạo thành để chặn dòng điện.

a. điện áp chắn; b. vùng nghèo; c. vùng tạp chất; d. dòng

ngược.

7. Khi tiếp giáp PN được phân cực thuận, các điện tử sẽ kết hợp với . . . . . tại tiếp giáp để có

dòng điện.

a. các điện tử; b. các ion; c. các hạt trung hoà [neutron]; d. các

lỗ trống

Trang 1

Trang 2

Trang 3

Trang 4

Trang 5

Trang 6

Trang 7

Trang 8

Trang 9

Trang 10

Tải về để xem bản đầy đủ

Tóm tắt nội dung tài liệu: Câu hỏi và bài tập Cấu kiện điện tử

ột trong số các điểm đề phòng sau là không đúng. a. Tất cả các thiết bị và các dụng cụ cần phải được tiếp đất. b. Các cực của MOSFET cần phải được nối với nhau khi chuyên chở và bảo quản. c. Không bao giờ tháo hoặc lắp MOSFET khi nguồn cung cấp tắt. d. Công nhân làm việc với các dụng cụ MOSFET cần phải có vòng nối đất ở cổ tay. 7.5. Các thông số của MOSFET. 17. Thông số nào sau đây nếu vượt quá sẽ làm cho FET bị đánh thủng và dẫn. a. V(BR)DSS; b. IDSS; c. VGS(th); d. VGS(on). 18. Điện áp phân cực cổng - nguồn để có dòng máng chảy trong E - MOSFET là . . . . . a. V(BR)DSS; b. IDSS; c. VGS(th); d. VGS(on). 7.6. Các ứng dụng của MOSFET. 19. Lý do khiến FET là cấu kiện lý tưởng để sử dụng ở các tầng đầu của máy thu là . . . . . a. FET phát sinh nhiễu nội thấp hơn so với BJT. b. không thể điều khiển hệ số khuyếch đại của FET bằng cách điều khiển điểm phân cực. c. FET có thể làm việc ở nhiệt độ trên 500oC. d. Cả a và b. 20. En - MOSFET là cấu kiện rất tốt để sử dụng trong các mạch chuyển mạch bởi vì . . . . . a. RDS(on) thường nhỏ hơn 10 ; b. En - MOSFET thường hở mạch cho đến khi có tín hiệu điều khiển làm cho En - MOSFET dẫn; c. Chỉ cần một mức công suất nhỏ cho mạch điều khiển; d. Tất cả các trường hợp trên. 21. Nhiều tín hiệu có thể được truyền trên cùng một đường dây là do sử dụng . . . . . a. ghép kênh theo thời gian; b. sản phẩm đường dây đơn; c. việc điều khiển MOSFET mắc nối tiếp; d. việc tách tạp âm. 22. Mạch chuyển đổi tín hiệu DC hay tín hiệu tần số thấp thành tín hiệu tần số cao là . . . . a. ghép kênh [multiplexing]; b. hạn chế [clipper]; c. ngắt quãng [chopper]; d. giải ghép [demultiplexing]. 50 23. Mạch được chế tạo bằng cả hai loại MOSFET kênh N và kênh P được gọi là mạch . . . . . . a. NP; b. PN; c. hai kênh; d. CMOS. 7. Sai hỏng trên các mạch FET. 24. Nếu nguồn tín hiệu có trở kháng vào 100k nối với mạch hình 7.33a, nguồn tín hiệu bị quá tải thì khả năng hư hỏng của mạch là do nguyên nhân nào ?. a. Điện trở Rg hở mạch; b. Điện trở Rd bị ngắn mạch; c. Điện trở Rd hở mạch; d. MOSFET hỏng. 25. Đối với mạch hình 7.33a, nếu điện áp trên cực máng là 9V và điện áp trên cực nguồn và cổng là 0V, thì sai hỏng có trong mạch là do: a. Điện trở Rg hở mạch; b. Điện trở Rg bị ngắn mạch; c. MOSFET bị hỏng; d. mạch làm việc đúng. 26. Đối với mạch hình 7.33a, nếu điện áp trên cực máng là 16V và điện áp trên cực cổng là 0V, thì sai hỏng có trong mạch là do: a. Điện trở Rd hở mạch; b. Điện trở Rd bị ngắn mạch; c. Điện trở Rg bị ngắn mạch; d. mạch làm việc đúng. 27. Đối với mạch hình 7.33b, nếu điện áp trên cực máng là 6V và điện áp trên cực nguồn và cổng là 6V, thì sai hỏng có trong mạch là do: a. Điện trở Rg hở mạch; b. Điện trở Rg bị ngắn mạch; c. MOSFET bị hỏng; d. mạch làm việc đúng. 28. Tất cả các điện áp DC đo được trong mạch hình 7.33b, đều phù hợp, nhưng điện áp tín hiệu trên cực máng là gần bằng 0. Sai hỏng có trong mạch là do: a. Điện trở Rd hở mạch; b. Điện trở Rd bị ngắn mạch; c. Điện trở RL bị ngắn mạch; d. Điện trở RL hở mạch. 51 29. Đối với mạch hình 7.34a, nếu điện áp trên đầu vào điều khiển là 5V và điện áp tín hiệu trên tải là 0V, thì sai hỏng có trong mạch là do: a. Điện trở Rg hở mạch; b. Điện trở Rg bị ngắn mạch; c. MOSFET bị hỏng; d. mạch hoạt động bình thường. 30. Đối với mạch hình 7.34b, nếu điện áp trên đầu vào điều khiển là 5V và điện áp tín hiệu trên tải gần bằng 0V, thì sai hỏng có trong mạch là do: a. Điện trở Rg hở mạch; b. Điện trở Rg bị ngắn mạch; c. MOSFET bị hỏng; d. mạch hoạt động bình thường. H. Bài tập phần MOSFET: 1. Hình 7.35, là đặc tuyến truyền đạt của một De - MOSFET. Từ đặc tuyến hãy xác định giá trị của VGS(off) và IDSS. VGS(off) = . . . . . . . IDSS = . . . . . . . . 2. Tính VG, VS, VD, và VDS ở mạch hình 7.36, nếu IDSS = 10mA. VG = . . . . . . . VS = . . . . . . . VD = . . . . . . . . VDS = . . . . . . . . 52 3. Tính trở kháng vào (zin), trở kháng ra (zout), hệ số khuyếch đại điện áp (Av), và mức điện áp ra (Vout) ở mạch hình 7.36. zin = . . . . . . . zout = . . . . . . . Av = . . . . . . . . Vout= . . . . . . . . 4. Tính trở kháng vào (zin), trở kháng ra (zout), hệ số khuyếch đại điện áp (Av), và mức điện áp ra (Vout) ở mạch hình 7.36, nếu biết gmo bằng 6mS. zin = . . . . . . . zout = . . . . . . . Av = . . . . . . . . Vout= . . . . . . . . 53 5. Tính VG, VS, VD, và VDS ở mạch hình 7.37, nếu IDSS = 2,5mA. VG = . . . . . . . VS = . . . . . . . VD = . . . . . . . . VDS = . . . . . . . . 6. Tính trở kháng vào (zin), trở kháng ra (zout), hệ số khuyếch đại điện áp (Av), và mức điện áp ra (Vout) ở mạch hình 7.37. zin = . . . . . . . zout = . . . . . . . Av = . . . . . . . . Vout = . . . . . . . . 54 7. Hình 7.38, là đặc tuyến truyền đạt của một En - MOSFET. Từ đặc tuyến hãy xác định giá trị của VGS(Th). VGS(Th) = . . . . . . . 8. Tính VG, VS, VD, và VDS ở mạch hình 7.39, cho ID(on) = 2mA. VG = . . . . . . . VS = . . . . . . . VD = . . . . . . . VDS = . . . . . . . 55 9. Tính trở kháng vào (zin), trở kháng ra (zout), hệ số khuyếch đại điện áp (Av), và mức điện áp ra (Vout) ở mạch hình 7.39, nếu biết gm tại điểm tĩnh - Q bằng 3mS. zin = . . . . . . . zout = . . . . . . . Av = . . . . . . . . Vout= . . . . . . . . 10. Hãy tính mức tín hiệu ra của mạch chuyển mạch ở hình 7.40, khi MOSFET ngưng dẫn (off), và khi MOSFET dẫn (on). Chuyển mạch mở (on) = . . . . . . . . . Chuyển mạch đóng (off) = . . . . . . . . . . . 11. Hãy tính mức tín hiệu ra của mạch chuyển mạch ở hình 7.41, khi MOSFET ngưng dẫn (off), và khi MOSFET dẫn (on). MOSFET ngưng dẫn (off) = . . . . . . . . . MOSFET dẫn (on) = . . . . . . . . . . . 56 12. Hãy thiết kế và vẽ một mạch chuyển mạch trong đó chuyển mạch mở (dẫn - on) và đóng (ngưng dẫn - off) điện áp nguồn cung cấp 15V đến tải 100 . Nguồn điều khiển sẽ nhìn mạch chuyển mạch như một trở kháng 100k . Đặc tuyến truyền đạt của En - MOSFET được sử dụng trong mạch cho ở hình 7.42. 57 Bài tập bổ sung phần FET D4.1 Thiết kế mạch khuyếch đại chung cực nguồn – Common Source (CS) bằng JFET để có RL = 10k , VDD = 12V, Rin = 500k , và Av = - 2. Sử dụng mạch ở hình 4.16a. Chọn điểm-Q là VDSQ = 6V, VGSQ = - 1V, IDQ = 1mA, và gm = 2500 A. Đs: RD = 4,78k ; RS = 1,22k ; R1 = 509k ; R2 = 27M ; và Ai = - 100. 58 D4.2 Thiết kế lại mạch khuyếch đại CS bằng JFET ở bài tập D4.1, cho transistor có VGSoff = - 4V và IDSS = 6mA. Đs: R1 = 500k ; R2 = ; RD = 1,61k ; RSdc = 390 ; RSac = 223 ; và Ai = - 100. D4.3 Thiết kế mạch khuyếch đại CD bằng JFET (hình 4.19) để cho hệ số khuyếch đại dòng điện bằng 15 cho tải là RL = 20k sử dụng VDD = 12V và Rin = 400k . Sử dụng JFET kênh-n có VGSoff = - 3V, và IDSS = 6mA. Giả sử VDSQ = VDD/2 và IDQ = 0,4IDSS. Tính trị số của các điện trở và hệ số khuyếch đại điện áp của mạch khuyếch đại. Đs: RSdc = 2,5k ; RSac =1,25k ; R1 = 676k ; R2 =980k ; Av = 0,75. 59 D4.4 Xác định trị số của các điện trở và hệ số khuyếch đại dòng điện cho mạch khuyếch đại bootstrap bằng JFET kiểu SF theo các yêu cầu là Rin = 200k , RL = 20k , và VDD = 10V. Điểm- Q được chọn tại: VDSQ = 5V, IDQ= 0,5mA, VGSQ = - 1,5V, gm = 4mS. Sử dụng kiểu mạch ở hình 4.22. Đs: RG = 62,8k ; RS1 = 3k ; RS2 = 7k ; Ai = 9,3. 60 4.1 Họ đặc tuyến cho vùng làm việc của transistor hiệu ứng trường kênh-n cụ thể có thể gần đúng bằng phương trình: mA450 2 GSv,iD , khi duy trì các điều kiện: RS = 500 , RD = 2k , Rin = 100k , IDQ= 5mA, và VDD = 20V. Hãy xác định các thông số sau: a) VGSQ; b) VD; c) VDSQ; d) R1 + R2. Tham khảo hình P4.1. 4.2 Trong mạch ở hình 4.16a, khi có R1 = 21k , R2 = 450k , RS = 500 , RD = 1,5k , RL = 4k , và VDD = 12V, xác định các thông số sau khi VDSQ = 4V: a) IDQ; b) VGSQ; c) Rin; d) Av khi gm = 3,16mS; e) Ai. 61 4.3 Trong mạch ở hình 4.16a, RD = 2k , RL = 5k , Rin = 100 , RS = 300 , và VDD = 15V. Xác định các trị số của R1 và R2 cần thiết để transistor làm việc ở mức 4mA khi VGSoff = - 4V và IDSS = 8mA. Tính hệ số khuyếch đại điện áp và dòng điện của mạch khuyếch đại. 62 4.4 a) Thiết kế mạch khuyếch đại chung cực nguồn [Common-Source tức CS] (hình P4.1) sử dụng JFET kênh-p đáp ứng các thông số yêu cầu là Av = - 10 và Rin = 20k . Giả thiết là điểm-Q được chọn tại IDQ = - 1mA, VDSQ = -10V, VGSQ = 0,5V. b) Tính Ai, R1, R2, RS, và RD. (Dựa vào đặc tuyến ở hình P4.2. Lưu ý rằng có thể có chia tách RS và mạch rẽ cho RS). 4.5 Lặp lại bài tập 4.4 khi RL là 20k được ghép vào cực máng qua một tụ. Chú ý là có thể cần phải chọn điểm-Q khác. 63 4.6 Thiết kế mạch khuyếch đại CS sử dụng MOSFET như mạch ở hình P4.3. Cho RL = 1k , Av = - 1, Rin = 15k . Điểm-Q được chọn tại VGSQ = 3V, IDQ = 7mA, VDSQ = 10V, trong đó gm = 2300 S. Xác định các trị số cho tất cả các cấu kiện còn lại. 4.7 Thiết kế mạch khuyếch đại CS sử dụng JFET kênh-n cho kiểu mạch như ở hình P4.4, với Av = - 1, VDD = 12V, RL = 1k , Rin = 15k , IDSS = 10mA, và VGSoff = - 4V. Sử dụng IDQ = IDSS / 2. 64 4.8 Thiết kế mạch khuyếch đại CS sử dụng JFET kênh-n khi có RL = 4k , Av = - 3, và Rin = 50k . Giả sử là transistor sử dụng có VGSoff = - 4,2V và IDSS = 6mA. Sử dụng mạch ở hình P4.4 với VDD = 20V. Xác định Ai. 4.9 Thiết kế mạch khuyếch đại CS bằng JFET kênh-n có AV = -2, Ai = -20, VDD = 12V, và RL = 5k . Xác định trị số của tất cả các cấu kiện và mức công suất định mức của transistor. (mạch có thể cần phải thay đổi để đáp ứng thiết kế). Transistor được chọn có VGSoff = - 5V và IDSS = 8mA. Sử dụng IDQ = 0,4IDSS và VDSQ = VDD/2. Xem mạch ở hình P4.4. 4.10 Thiết kế mạch khuyếch đại CS bằng JFET kênh-p với AV = - 4, Ai = - 40, RL = 8k , và VDD = - 16V. Transistor được chọn có VGSoff = 3V và IDSS = - 7mA, sử dụng IDQ = 0,3IDSS và VDSQ = VDD/2. Sử dụng mạch ở hình P4.4. Xác định công suất định mức của transistor. 65 4.11 Thiết kế mạch khuyếch đại CS bằng JFET kênh-p với tải là 5k , sử dụng mạch ở hình P4.4. Cho VDD = - 20V, AV = - 2, Ai = - 20, VGSoff = 6V và IDSS = - 5mA. Xác định công suất định mức của transistor. 4.12 Thiết kế mạch khuyếch đại chung cực nguồn (CS) bằng MOSFET kênh-n, sử dụng transistor 3N128 (phụ lục D) cho tải là 10k với hệ số khuyếch đại điện áp Av = - 10. Sử dụng mạch ở hình P4.3. Chọn điểm-Q khi Rin > 10k , bằng cách sử dụng họ đặc tuyến thể hiện theo các thông số kỹ thuật cuối phần bài tập. 66 4.13 Thiết kế mạch khuyếch đại bằng MOSFET kênh-n, chung cực nguồn (CS) sử dụng transistor 3N128 (phụ lục D) cho tải là 2k với Av = - 4 và Rin > 100k . Giả sử rằng, điểm-Q đã được chọn là VGSQ = - 0,6V, VDSQ = 10V, IDQ = 10mA, VDD = 20V. Tham khảo mạch ở hình P4.3. 4.14 Phân tích mạch khuyếch đại CS bằng JFET kênh-n như mạch ở hình P4.5, khi có tải là 20k , RD = 8k , VDD = 24V, và Rin = 50k . Chọn điểm-Q có VGSQ = - 1,5V, VDSQ = 12V, IDQ = 1mA, và gm = 2,83mS. Hãy tính tất cả trị số của các cấu kiện, Ai, và Av. 67 4.15 Nếu RS ở mạch hình P4.4, được rẽ mạch bằng tụ, thì hệ số khuyếch đại điện áp là bao nhiêu ? Giả sử rằng điểm-Q đã được chọn để có gm = 1,5mS, RD = 3,2k , và RL = 5k . Xác định hệ số khuyếch đại dòng điện khi RS = 500 , R1 = 200k , và R2 = 800k . 4.16 Hệ số khuyếch đại điện áp Av của mạch ở hình P4.4, là bao nhiêu nếu tín hiệu được cung cấp vào mạch khuyếch đại có điện trở của nguồn điện áp là Ri = 10k ? Cho RD = 10k , và RL = 10k , RS = 500 , gm = 2mS, R1 = 25k , và R2 = 120k . 68 4.17 Cho mạch như ở hình P4.6, giả sử rằng RS được rẽ mạch bằng một tụ điện. VDD = 15V, RD = 2k , RL = 3k , RS = 200 , R1 = 500k , IDSS = 8mA, và VGSoff = - 4V. Hãy xác định Av, Ai, Rin, và điểm-Q cho mạch khuyếch đại. 4.18 Cho mạch hình P4.6, giả sử rằng VDD = 20V, RD = 2k , RL = 10k , RS = 200 , R1 = 1M , IDSS = 10mA, và VGSoff = - 5V. Hãy xác định điểm-Q, Av, Ai, Rin, và cho mạch khuyếch đại. 69 4.19 Cho mạch hình P4.6, giả sử rằng VDD = 20V, RD = 2k , RL = 6k , RS = 100 , R1 = 1M , IDSS = 10mA, và VGSoff = - 5V. Hãy xác định điểm-Q, Av, Ai, Rin, và cho mạch khuyếch đại. 4.20 Cho mạch khuyếch đại CS như ở hình P4.1, sử dụng JFET có IDSS = 2mA, và gm0 = 2000 S. Nếu trị số của RD = 10k , RS = 200 , thì hệ số khuyếch đại điện áp Av là bao nhiêu đối với các giá trị của VGSQ sau đây ? (a) – 1V; (b) – 0,5V; (c) 0V. 70 4.21 Mạch khuyếch đại CS ở hình P4.6, với transistor có VGSoff = - 4V, IDSS = 4mA, và rDS = 500 . Nếu RD = 2k , RL = 4k , và RS = 200 , thì hệ số khuyếch đại điện áp Av của mạch là bao nhiêu với VGSQ = - 1V ? Av sẽ như thế nào khi rDS đạt đến vô cùng ? 4.22 Thiết kế mạch khuyếch đại CS bằng MOSFET kênh-n như mạch ở hình P4.3, khi có RL = 4k , Av = - 5, và Ai = - 10. Giả sử rằng, điểm-Q đã chọn có VDSQ = 10V, VGSQ = 4V, IDQ = 2mA, và gm = 4000 S. 71 4.23 Cho mạch như ở hình P4.7, có Ri = 50k , R1 = 100k , R2 = 800k , RD = 4k , RL = 6k , RS = 200 , và VDD = 20V, xác định các thông số sau khi sử dụng FET có VDSQ = 6V, gm = 2,5mS: a) IDQ, VGG, và VGSQ b) Av, Rin, và Ai. 4.24 Cho mạch như ở hình P4.7, nếu loại bỏ R2, transistor FET làm việc ở mức dòng là 2mA. Trị số của các cấu kiện là Ri = 100k , R1 = 400k , RD = 3k , RL = 5k , và VDD = 12V. Xác định các thông số sau khi sử dụng transistor có IDSS = 8mA, và VGSoff = - 4V: (a) RS; (b) Av, Rin, và Ai. 72 4.25 Thiết kế mạch khuyếch đại lặp lại-cực nguồn (SF) bằng JFET kênh-p như ở hình P4.8, với Rin = 20k , để nhận được hệ số khuyếch đại điện áp Av gần bằng 1. Tính Ai, R1, R2, và RS. Sử dụng họ đặc tuyến cho ở hình P4.2. 4.26 Lặp lại bài tập 4.25, khi có tải là 20k được ghép tụ với mạch khuyếch đại. 73 4.27 Thiết kế mạch khuyếch đại bằng MOSFET kiểu máng-chung (CD) khi có RL = 100 , Ai = 200, và Rin = 100k . Sử dụng transistor có VGSoff = - 6V và IDSS = 20mA. Xác định Av và giá trị của tất cả các điện trở. Mạch sử dụng ở hình P4.9. 4.28 Thiết kế mạch khuyếch đại CD bằng MOSFET kênh-n, trong đó Rin = 120k , Ai = 100, RL = 500 , VDD = 20V, và chọn transistor có VGSoff = - 5V và IDSS = 15mA. Sử dụng mạch ở hình P4.9, với IDQ = 0,6IDSS và VDSQ = VDD/2. 74 4.29 Thiết kế mạch khuyếch đại lặp lại cực nguồn (SF) sử dụng JFET kênh-n để cho hệ số khuyếch đại dòng là 100 và điện trở vào là 500k . Tải là 2k . Chọn điểm-Q theo các tham số là: VDSQ = 8V, IDQ = 5mA, VGSQ = - 1V, và gm = 4mS. Xác định các điện trở, hệ số khuyếch đại điện áp và vẽ mạch khi VDD = 10V. 4.30 Lặp lại bài tập 4.29 nhưng bằng transistor khác với giá trị của các thông số là: VGSoff = -3V, IDSS = 10mA. 75 4.31 Thiết kế mạch như ở hình 4.21, khi có VDD = 16V và RL = 8k . Sử dụng transistor có VGSoff = - 3,33V, IDSS = 10mA. Xác định toàn bộ trị số của cấu kiện, Ai, và Av khi có Rin = 12k . 4.32 Dựa vào bài tập 4.31, xác định toàn bộ trị số của cấu kiện, Ai, và Av khi có Rin = 200k . 76 Phụ lục D: Trang số liệu của hãng chế tạo (Appendix D: Manufacturers’ Data Sheets) 77 78 79 Đáp số các bài tập có gạch dưới dòng.

File đính kèm:

cau_hoi_va_bai_tap_cau_kien_dien_tu.pdf

cau_hoi_va_bai_tap_cau_kien_dien_tu.pdf