Bài giảng Nhập môn mạch số - Chương 5: Mạch tổ hợp. Các mạch khác (Tiếp theo)

Mạch tạo/kiểm tra Parity bit

Chức năng: Kiểm tra chuỗi bit dữ liệu truyền đúng hay

sai tại đầu thu

Phương pháp:

Tại đầu phát: một Parity bit được tạo ra từ chuỗi dữ liệu muốn

truyền đi, sau đó Parity bit này được chèn vào cuối chuỗi bit

dữ liệu này.

Tại đầu thu: Kiểm tra Parity bit để xác nhận choỗi dữ liệu nhận

được có bị sai hay không

Mạch tạo/kiểm tra Parity bit

Hai loại Parity bit:

Bit chẵn (Even parity bit - Be): Be = 1 khi tổng số bit 1 trong

chuỗi bit (kể cả Be) là số chẵn.

Bit lẻ (Odd parity bit - Bo): Bo = 1 khi tổng số bit 1 trong

chuỗi bit (kể cả Bo) là số lẻ

Trang 1

Trang 2

Trang 3

Trang 4

Trang 5

Trang 6

Trang 7

Trang 8

Trang 9

Trang 10

Tải về để xem bản đầy đủ

Bạn đang xem 10 trang mẫu của tài liệu "Bài giảng Nhập môn mạch số - Chương 5: Mạch tổ hợp. Các mạch khác (Tiếp theo)", để tải tài liệu gốc về máy hãy click vào nút Download ở trên

Tóm tắt nội dung tài liệu: Bài giảng Nhập môn mạch số - Chương 5: Mạch tổ hợp. Các mạch khác (Tiếp theo)

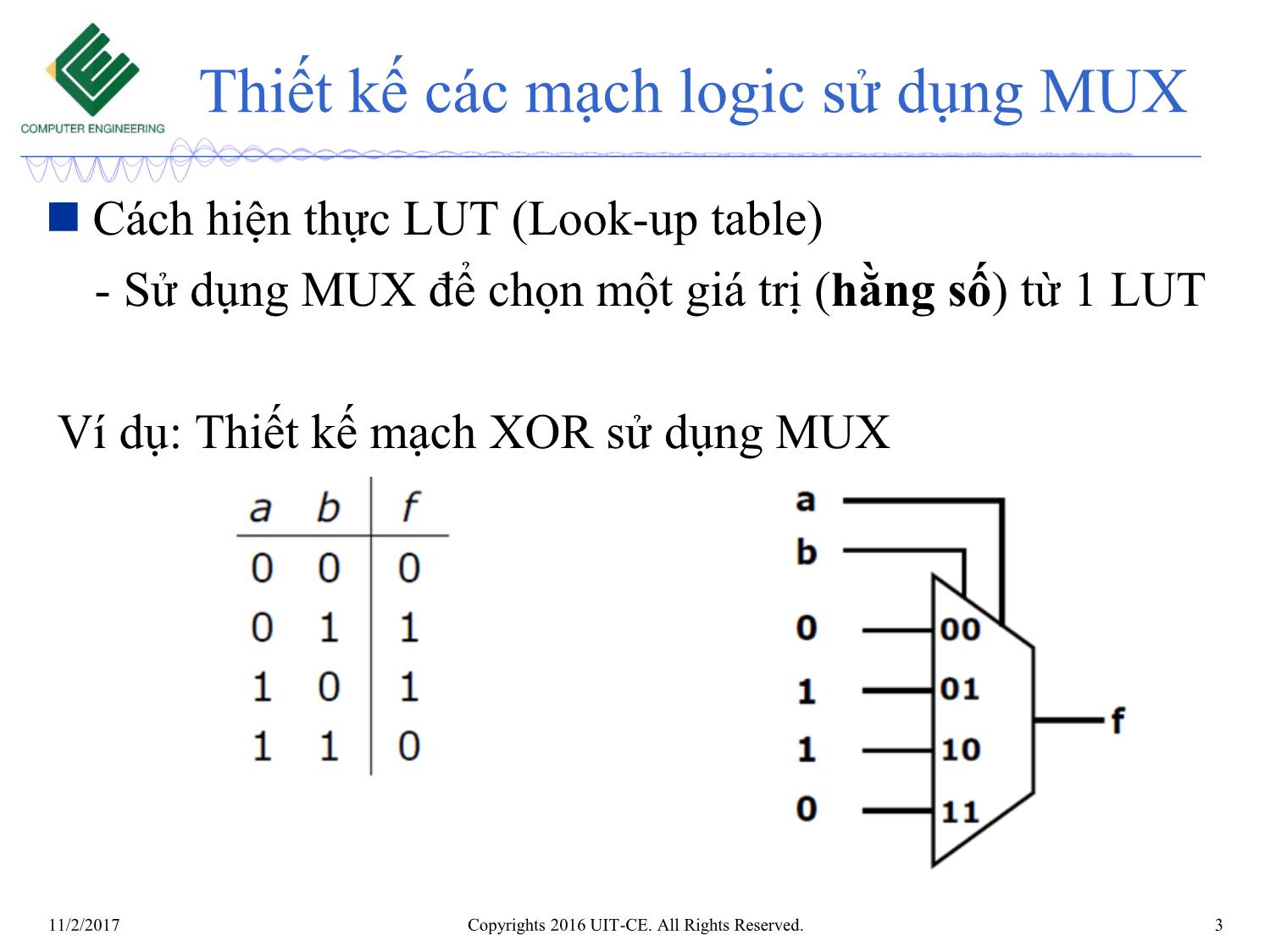

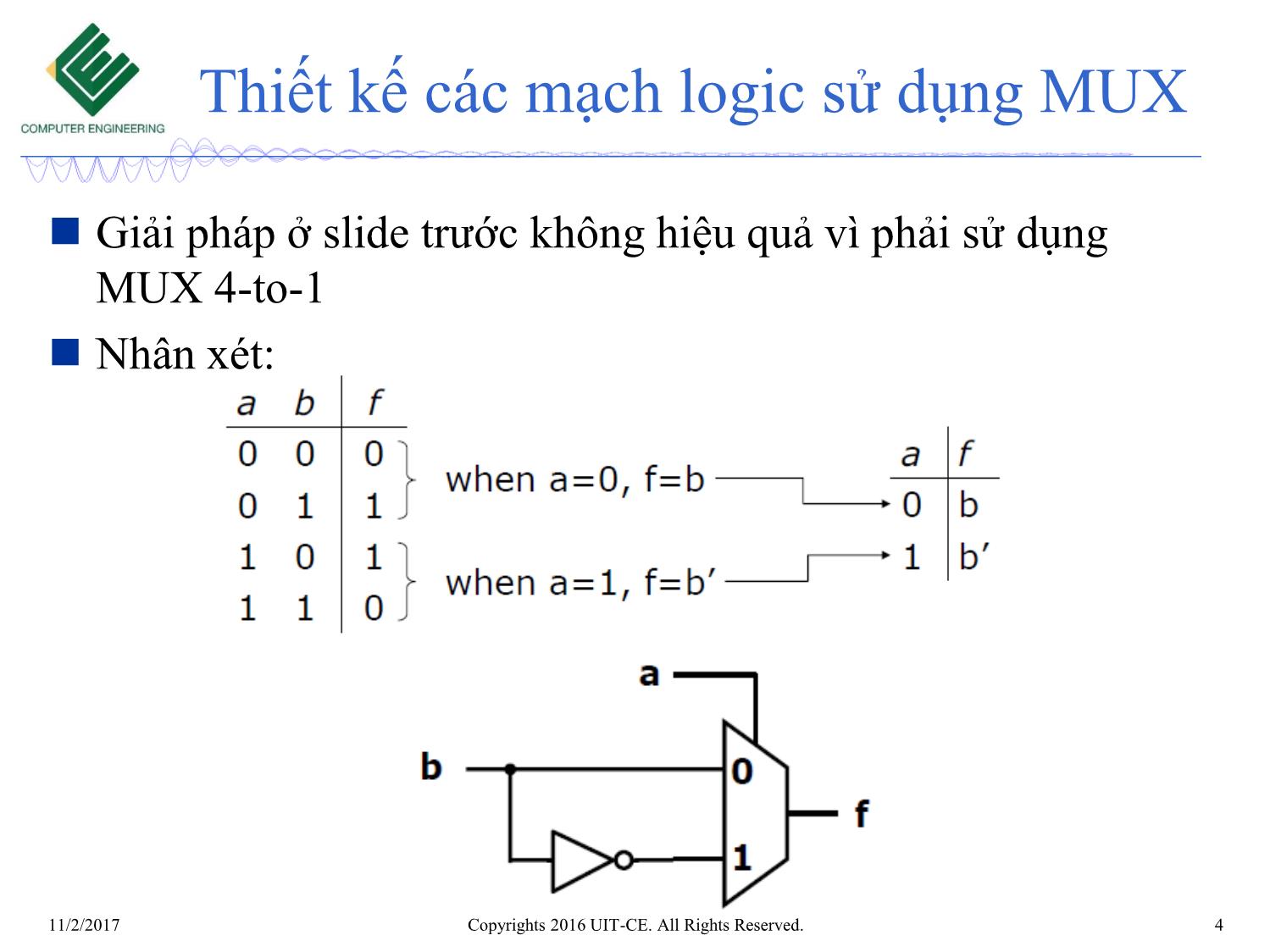

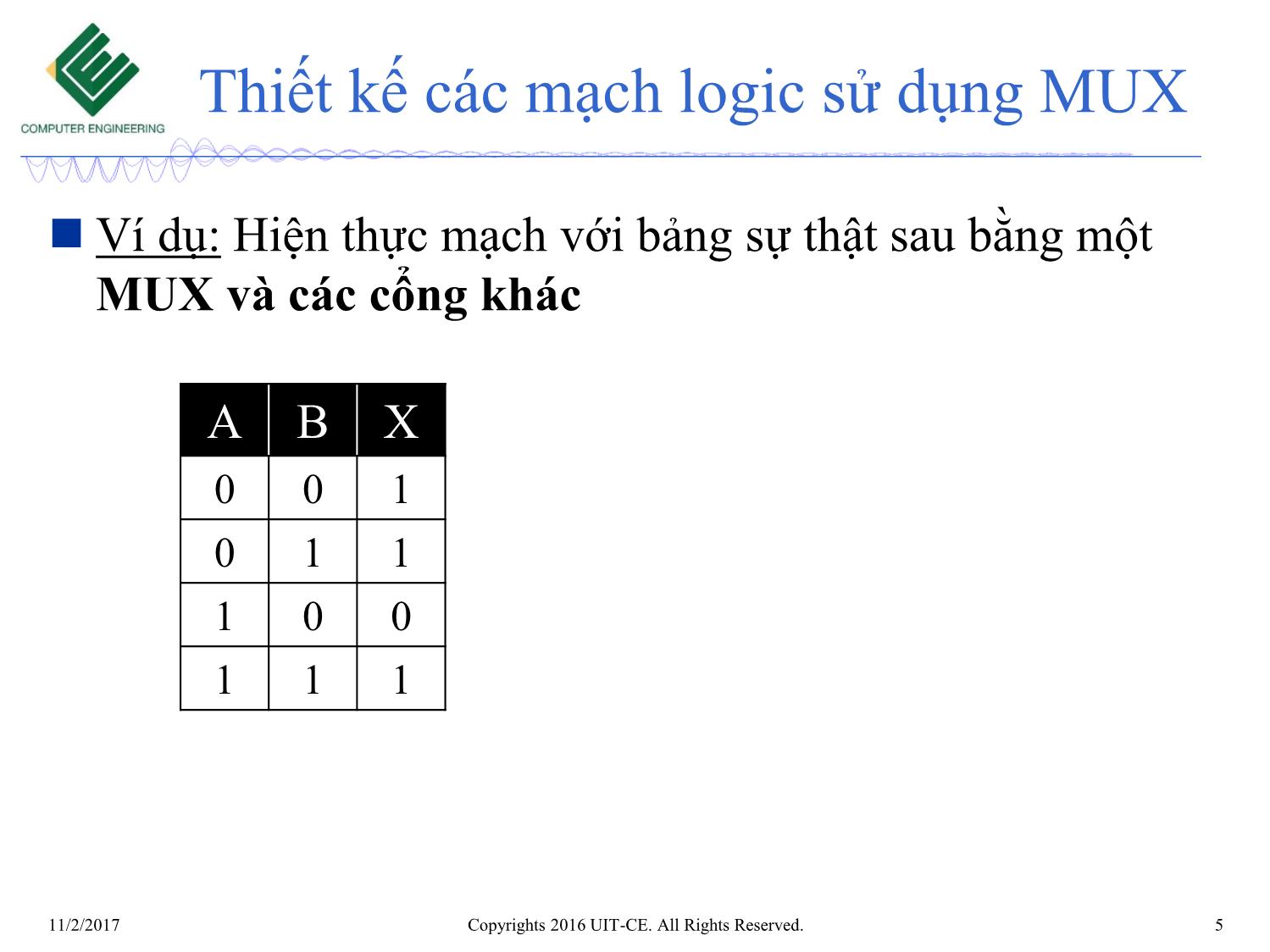

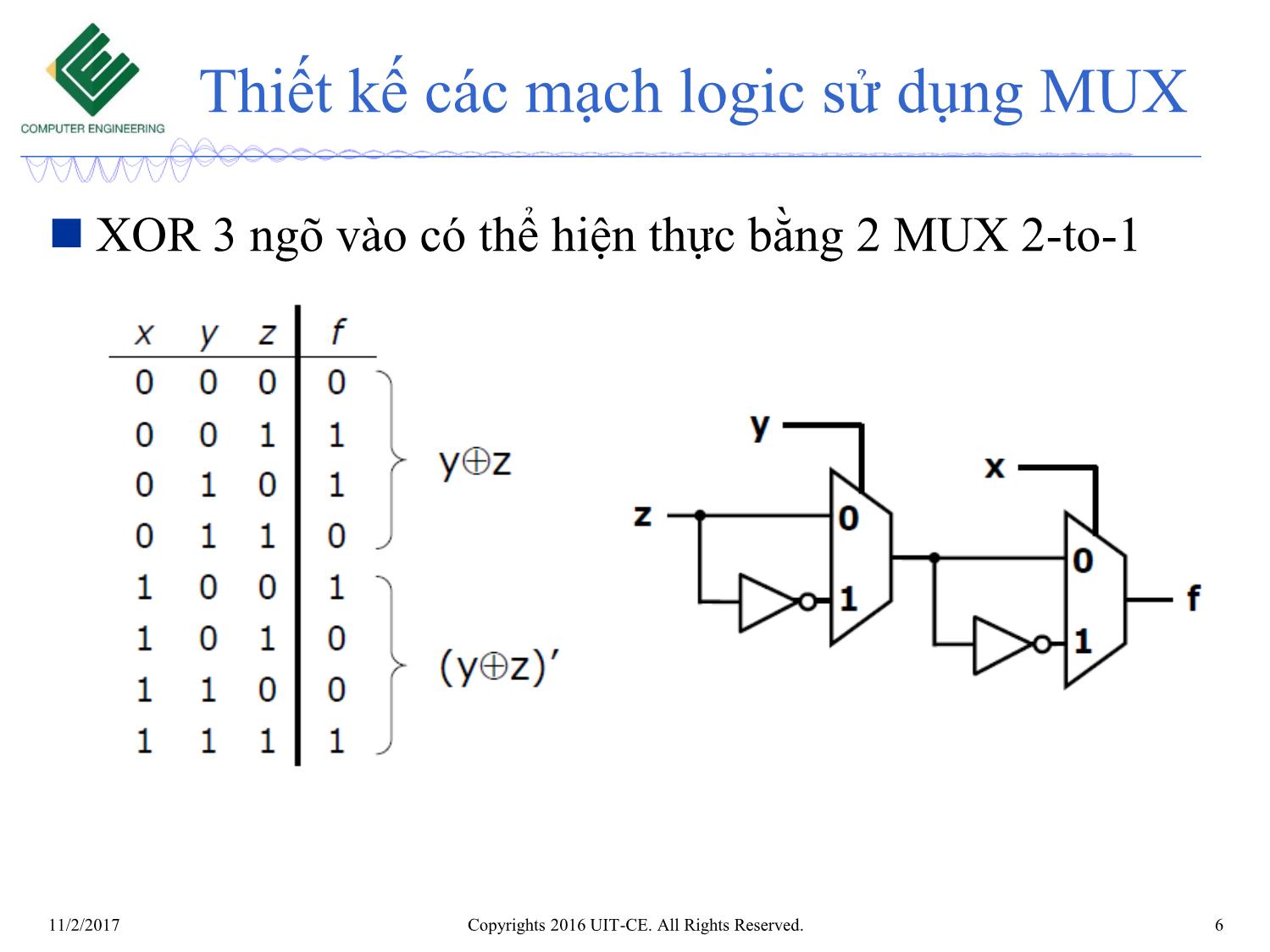

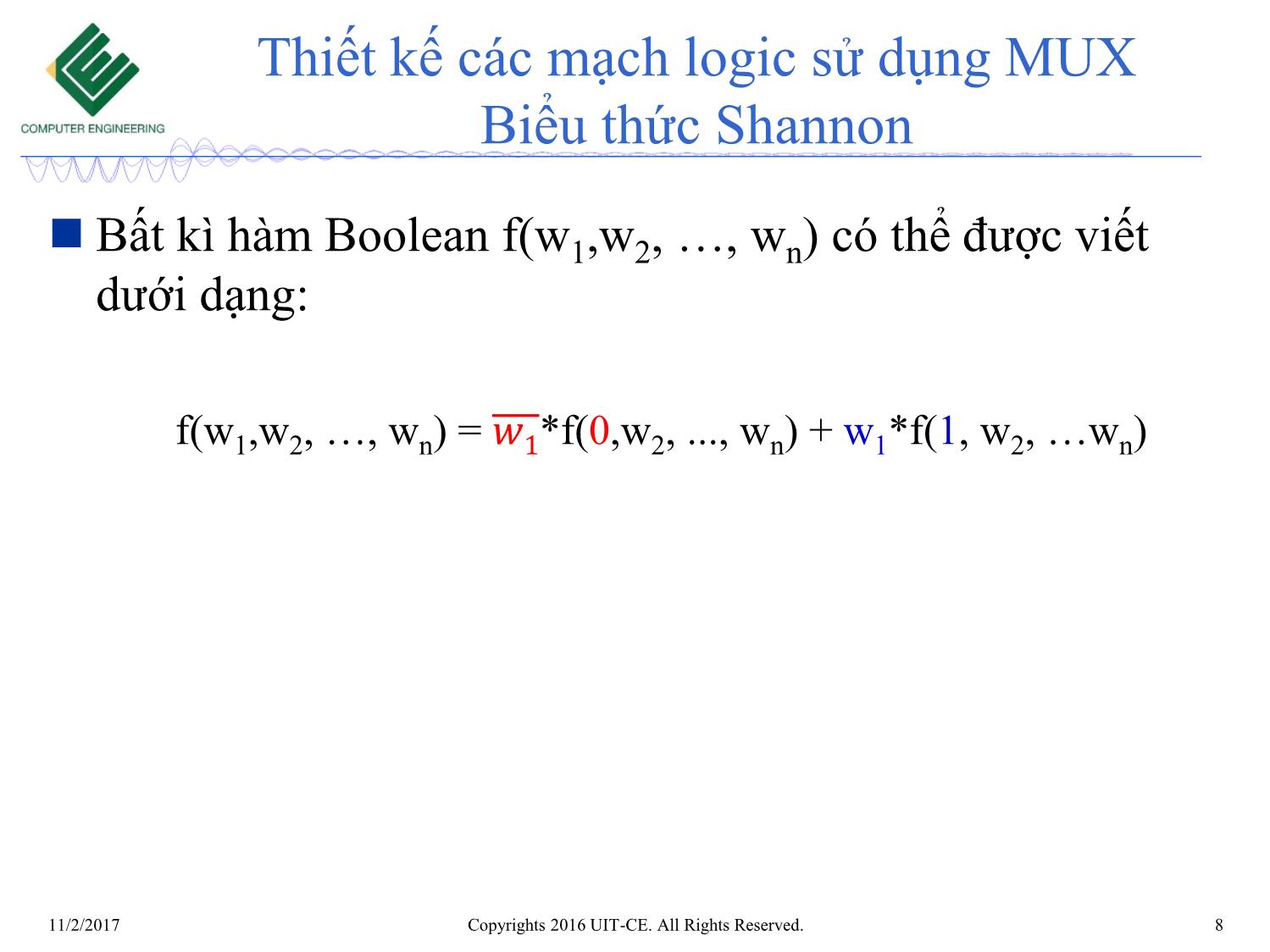

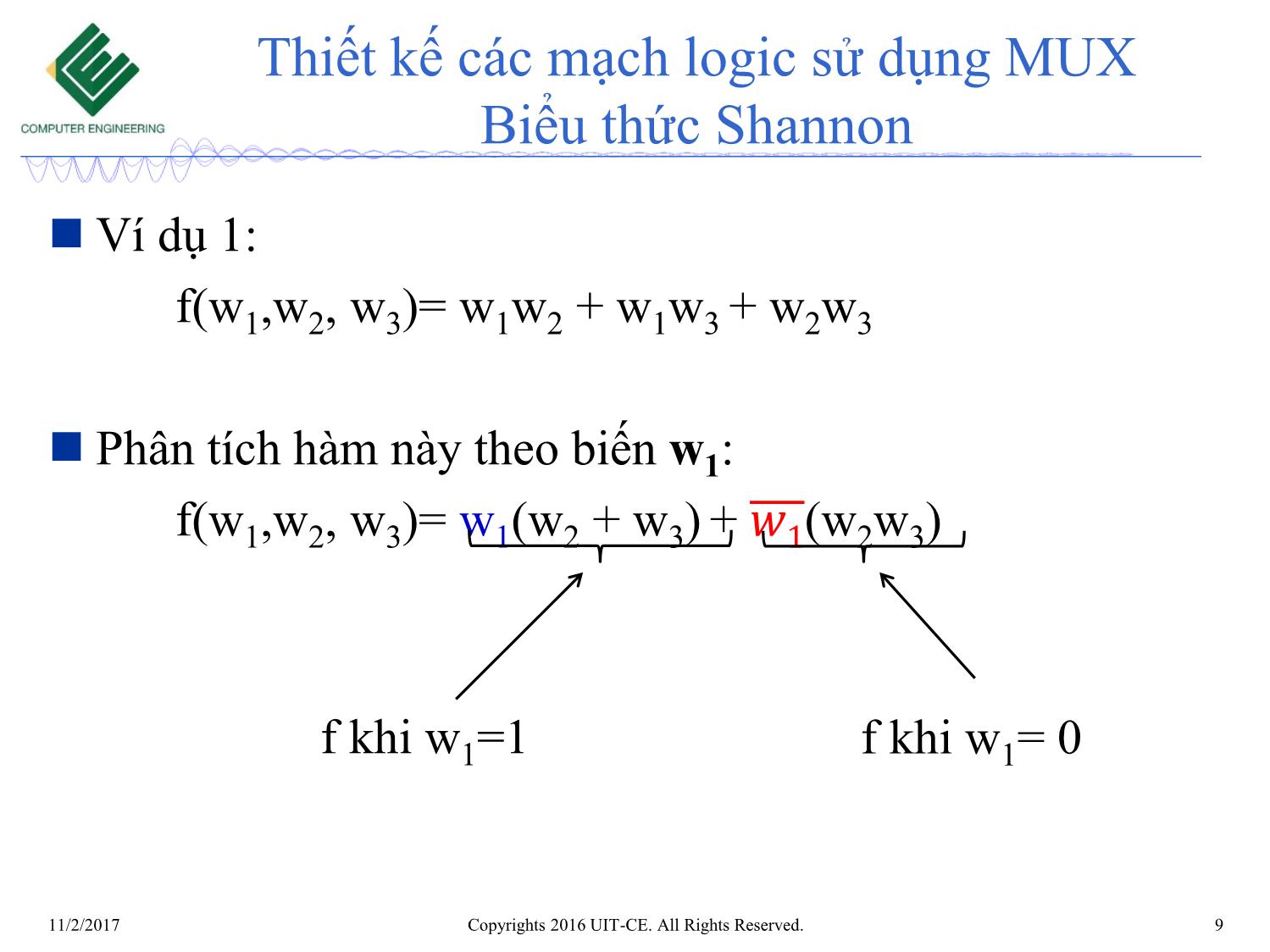

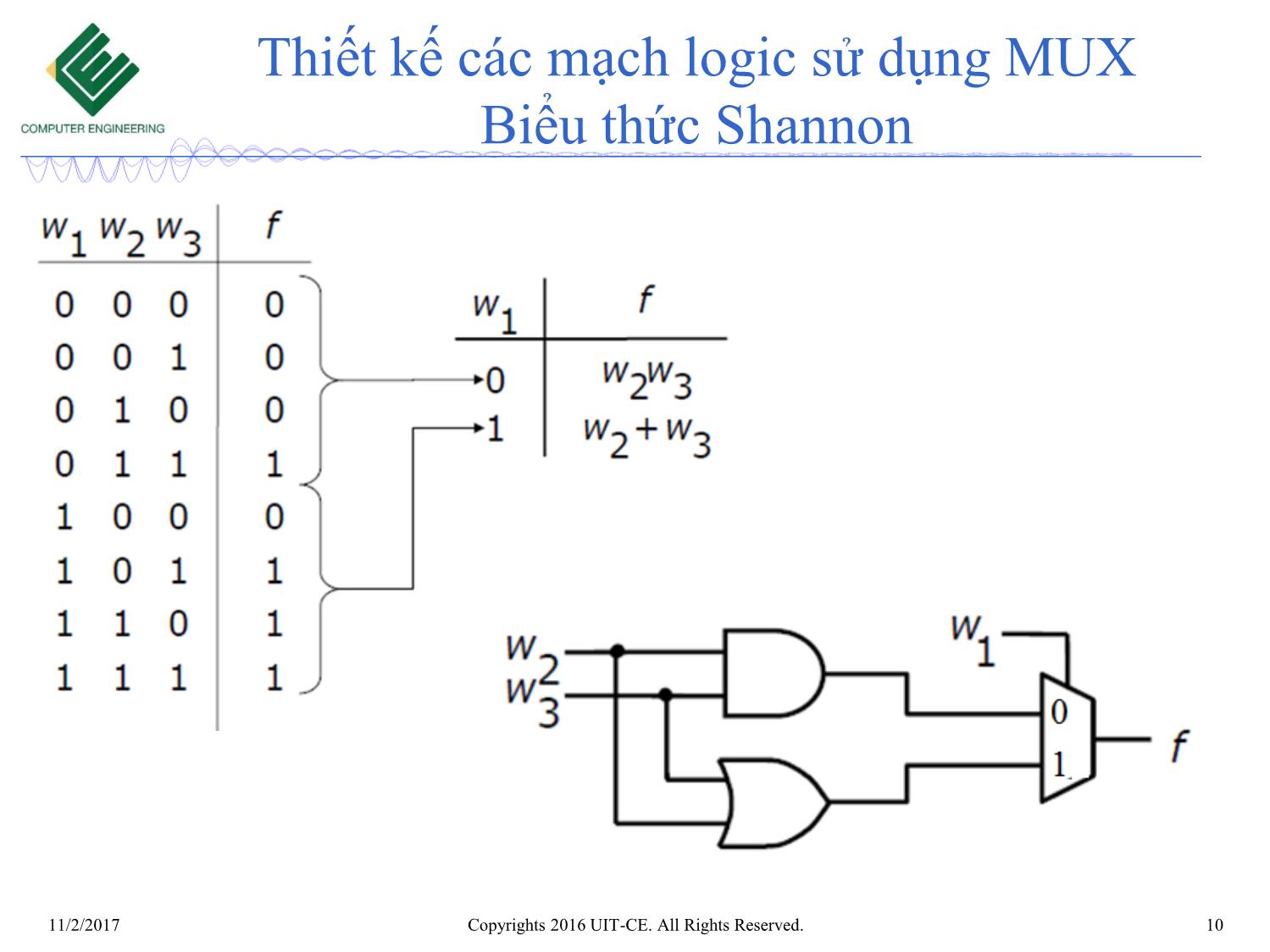

CHƯƠNG 5: MẠCH TỔ HỢP – CÁC MẠCH KHÁC NHẬP MÔN MẠCH SỐ 11/2/2017 Copyrights 2016 UIT-CE. All Rights Reserved. 2 Mạch giải mã (Decoder)/ Mạch mã hoá (Encoder) Mạch dồn kênh (Multiplexer)/ Mạch chia kênh (Demultiplexer) Thiết kế mạch logic sử dụng Mux Mạch tạo Parity/ Mạch kiểm tra Parity Mạch so sánh (Comparator) Nội dung Thiết kế các mạch logic sử dụng MUX Cách hiện thực LUT (Look-up table) - Sử dụng MUX để chọn một giá trị (hằng số) từ 1 LUT Ví dụ: Thiết kế mạch XOR sử dụng MUX 11/2/2017 Copyrights 2016 UIT-CE. All Rights Reserved. 3 Giải pháp ở slide trước không hiệu quả vì phải sử dụng MUX 4-to-1 Nhận xét: 11/2/2017 Copyrights 2016 UIT-CE. All Rights Reserved. 4 Thiết kế các mạch logic sử dụng MUX Ví dụ: Hiện thực mạch với bảng sự thật sau bằng một MUX và các cổng khác A B X 0 0 1 0 1 1 1 0 0 1 1 1 11/2/2017 Copyrights 2016 UIT-CE. All Rights Reserved. 5 Thiết kế các mạch logic sử dụng MUX XOR 3 ngõ vào có thể hiện thực bằng 2 MUX 2-to-1 11/2/2017 Copyrights 2016 UIT-CE. All Rights Reserved. 6 Thiết kế các mạch logic sử dụng MUX Ví dụ: Hiện thực mạch với bảng sự thật sau bằng một MUX và các cổng logic khác A B C X 0 0 0 1 0 0 1 1 0 1 0 0 0 1 1 1 1 0 0 1 1 0 1 0 1 1 0 0 1 1 1 1 - Với A là ngõ vào điều khiển - Với C là ngõ vào điều khiển 11/2/2017 Copyrights 2016 UIT-CE. All Rights Reserved. 7 Thiết kế các mạch logic sử dụng MUX Thiết kế các mạch logic sử dụng MUX Biểu thức Shannon Bất kì hàm Boolean f(w1,w2, , wn) có thể được viết dưới dạng: f(w1,w2, , wn) = 𝑤1*f(0,w2, ..., wn) + w1*f(1, w2, wn) 11/2/2017 Copyrights 2016 UIT-CE. All Rights Reserved. 8 Ví dụ 1: f(w1,w2, w3)= w1w2 + w1w3 + w2w3 Phân tích hàm này theo biến w1: f(w1,w2, w3)= w1(w2 + w3) + 𝑤1(w2w3) f khi w1=1 f khi w1= 0 11/2/2017 Copyrights 2016 UIT-CE. All Rights Reserved. 9 Thiết kế các mạch logic sử dụng MUX Biểu thức Shannon 11/2/2017 Copyrights 2016 UIT-CE. All Rights Reserved. 10 Thiết kế các mạch logic sử dụng MUX Biểu thức Shannon Ví dụ 2: Chọn x làm biến mở rộng 11/2/2017 Copyrights 2016 UIT-CE. All Rights Reserved. 11 Thiết kế các mạch logic sử dụng MUX Biểu thức Shannon Ví dụ 3: Chọn z làm biến mở rộng 11/2/2017 Copyrights 2016 UIT-CE. All Rights Reserved. 12 Thiết kế các mạch logic sử dụng MUX Biểu thức Shannon Bài tập 1: Dùng MUX 4-to-1 và các cổng luận lý cần thiết để hiện thực hàm sau: F (a, b, c, d) = SOP (1, 3, 5, 6, 8, 11, 15) Yêu cầu: c và d là các ngõ vào điều khiển của MUX 4-ra-1 11/2/2017 Copyrights 2016 UIT-CE. All Rights Reserved. 13 Thiết kế các mạch logic sử dụng MUX Biểu thức Shannon Bài tập 2: Dùng MUX 4-to-1 và các cổng luận lý cần thiết để hiện thực hàm sau: F (a, b, c, d) = SOP (1, 3, 5, 6, 8, 11, 15) Yêu cầu: b và c là các ngõ vào điều khiển của MUX 4-to-1 11/2/2017 Copyrights 2016 UIT-CE. All Rights Reserved. 14 Thiết kế các mạch logic sử dụng MUX Biểu thức Shannon 11/2/2017 Copyrights 2016 UIT-CE. All Rights Reserved. 15 Mạch giải mã (Decoder)/ Mạch mã hoá (Encoder) Mạch dồn kênh (Multiplexer)/ Mạch chia kênh (Demultiplexer) Thiết kế mạch logic sử dụng Mux Mạch tạo Parity/ Mạch kiểm tra Parity Mạch so sánh (Comparator) Nội dung Mạch tạo/kiểm tra Parity bit Chức năng: Kiểm tra chuỗi bit dữ liệu truyền đúng hay sai tại đầu thu Phương pháp: Tại đầu phát: một Parity bit được tạo ra từ chuỗi dữ liệu muốn truyền đi, sau đó Parity bit này được chèn vào cuối chuỗi bit dữ liệu này. Tại đầu thu: Kiểm tra Parity bit để xác nhận choỗi dữ liệu nhận được có bị sai hay không 11/2/2017 16Copyrights 2016 UIT-CE. All Rights Reserved. Mạch tạo/kiểm tra Parity bit Hai loại Parity bit: Bit chẵn (Even parity bit - Be): Be = 1 khi tổng số bit 1 trong chuỗi bit (kể cả Be) là số chẵn. Bit lẻ (Odd parity bit - Bo): Bo = 1 khi tổng số bit 1 trong chuỗi bit (kể cả Bo) là số lẻ 11/2/2017 17Copyrights 2016 UIT-CE. All Rights Reserved. XOR = Exclusive OR Ngõ ra bằng 1 khi số ngõ vào bằng 1 là lẻ X = A B XNOR = Exclusive NOR Ngõ ra bằng 1 khi số ngõ vào bằng 1 là chẵn X = A B 11/2/2017 Copyrights 2016 UIT-CE. All Rights Reserved. 18 Nhắc lại: Cổng logic XOR, XNOR Mạch tạo Parity bit Tạo Even Parity bit 11/2/2017 19Copyrights 2016 UIT-CE. All Rights Reserved. A2 A1 A0 Be 0 0 0 0 0 0 1 1 0 1 0 1 0 1 1 0 1 0 0 1 1 0 1 0 1 1 0 0 1 1 1 1 Be = f(A2,A1,A0) ? A2 A1 A0 Bo 0 0 0 1 0 0 1 0 0 1 0 0 0 1 1 1 1 0 0 0 1 0 1 1 1 1 0 1 1 1 1 0 Tạo Odd Parity bit Bo = f(A2,A1,A0) ? Mạch kiểm tra Even Parity bit Bảng sự thật: 11/2/2017 20Copyrights 2016 UIT-CE. All Rights Reserved. A2 A1 A0 Be fe A2 A1 A0 Be fe 0 0 0 0 0 1 0 0 0 1 0 0 0 1 1 1 0 0 1 0 0 0 1 0 1 1 0 1 0 0 0 0 1 1 0 1 0 1 1 1 0 1 0 0 1 1 1 0 0 0 0 1 0 1 0 1 1 0 1 1 0 1 1 0 0 1 1 1 0 1 0 1 1 1 1 1 1 1 1 0 fe = f(A2,A1,A0,Be) ? fe = 1 Transmission failed Bảng sự thật: Mạch kiểm tra Odd Parity bit fo = 1 Transmission failed 11/2/2017 21Copyrights 2016 UIT-CE. All Rights Reserved. A2 A1 A0 Bo fo A2 A1 A0 Bo fo 0 0 0 0 1 1 0 0 0 0 0 0 0 1 0 1 0 0 1 1 0 0 1 0 0 1 0 1 0 1 0 0 1 1 1 1 0 1 1 0 0 1 0 0 0 1 1 0 0 1 0 1 0 1 1 1 1 0 1 0 0 1 1 0 1 1 1 1 0 0 0 1 1 1 0 1 1 1 1 1 fo = f(A2,A1,A0,Bo) ? 11/2/2017 Copyrights 2016 UIT-CE. All Rights Reserved. 22 Mạch giải mã (Decoder)/ Mạch mã hoá (Encoder) Mạch dồn kênh (Multiplexer)/ Mạch chia kênh (Demultiplexer) Thiết kế mạch logic sử dụng Mux Mạch tạo Parity/ Mạch kiểm tra Parity Mạch so sánh (Comparator) Nội dung Mạch so sánh (Comperator) Mạch so sánh 2 số Xuất ra 1 nếu chúng bằng nhau Xuất ra 0 nếu chúng khác nhau • Dựa trên cổng XOR, trả về 0 nếu ngõ vào giống nhau và 1 nếu chúng khác nhau • Dựa trên cổng XNOR, trả về 1 nếu ngõ vào giống nhau và 0 nếu chúng khác nhau 11/2/2017 Copyrights 2016 UIT-CE. All Rights Reserved. 23 Mạch so sánh 1 bit a b gt eq lt 0 0 0 1 0 0 1 0 0 1 1 0 1 0 0 1 1 0 1 0 11/2/2017 Copyrights 2016 UIT-CE. All Rights Reserved. 24 Mạch so sánh 4 bit a0 b3 a3 b2 a2 b1 a1 b0 eq 11/2/2017 Copyrights 2016 UIT-CE. All Rights Reserved. 25 Mạch so sánh 4 bit a0 b3 a3 b2 a2 b1 a1 b0 gt 11/2/2017 Copyrights 2016 UIT-CE. All Rights Reserved. 26 Mạch so sánh 4 bit lt 11/2/2017 Copyrights 2016 UIT-CE. All Rights Reserved. 27 Mạch so sánh 4-bit 74x85 là mạch so sánh tiêu chuẩn với những đặc tính sau: if (A>B) lt=0, eq=0, gt=1 if (A<B) lt=1, eq=0, gt=0 if (A=B) lt=l, eq=e, gt=g Chý ý: 3 ngõ vào l, e và g được sử dụng khi ghép nối để tạo mạch so sánh với số bit nhiều hơn 4 4 B A g e l gt eq lt 11/2/2017 Copyrights 2016 UIT-CE. All Rights Reserved. 28 Ví dụ Thiết kế mạch tìm số lớn nhất, số nhỏ nhất trong 4 số 4- bit sử dụng mạch so sánh và MUXs 11/2/2017 Copyrights 2016 UIT-CE. All Rights Reserved. 29 30 11/2/2017 Copyrights 2016 UIT-CE. All Rights Reserved. Tóm tắt nội dung chương học Qua Phần 3 - Chương 5, sinh viên cần nắm những nội dung chính sau: Một số giải pháp thiết kế mạch số sử dụng mạch chọn kênh, mạch giải mã Chức năng, ứng dụng và thiết kế của mạch có độ ưu tiên Chức năng, ứng dụng và thiết kế của mạch tạo và kiểm tra Parity chẵn, lẻ. Chức năng, ứng dụng và thiết kế của mạch tạo và kiểm tra Parity chẵn, lẻ. Chức năng, ứng dụng và thiết kế của mạch so sánh Any question?

File đính kèm:

bai_giang_nhap_mon_mach_so_chuong_5_mach_to_hop_cac_mach_kha.pdf

bai_giang_nhap_mon_mach_so_chuong_5_mach_to_hop_cac_mach_kha.pdf