Bài giảng Kỹ thuật số - Chương 8: Đặc điểm của IC số - Đặng Ngọc Khoa

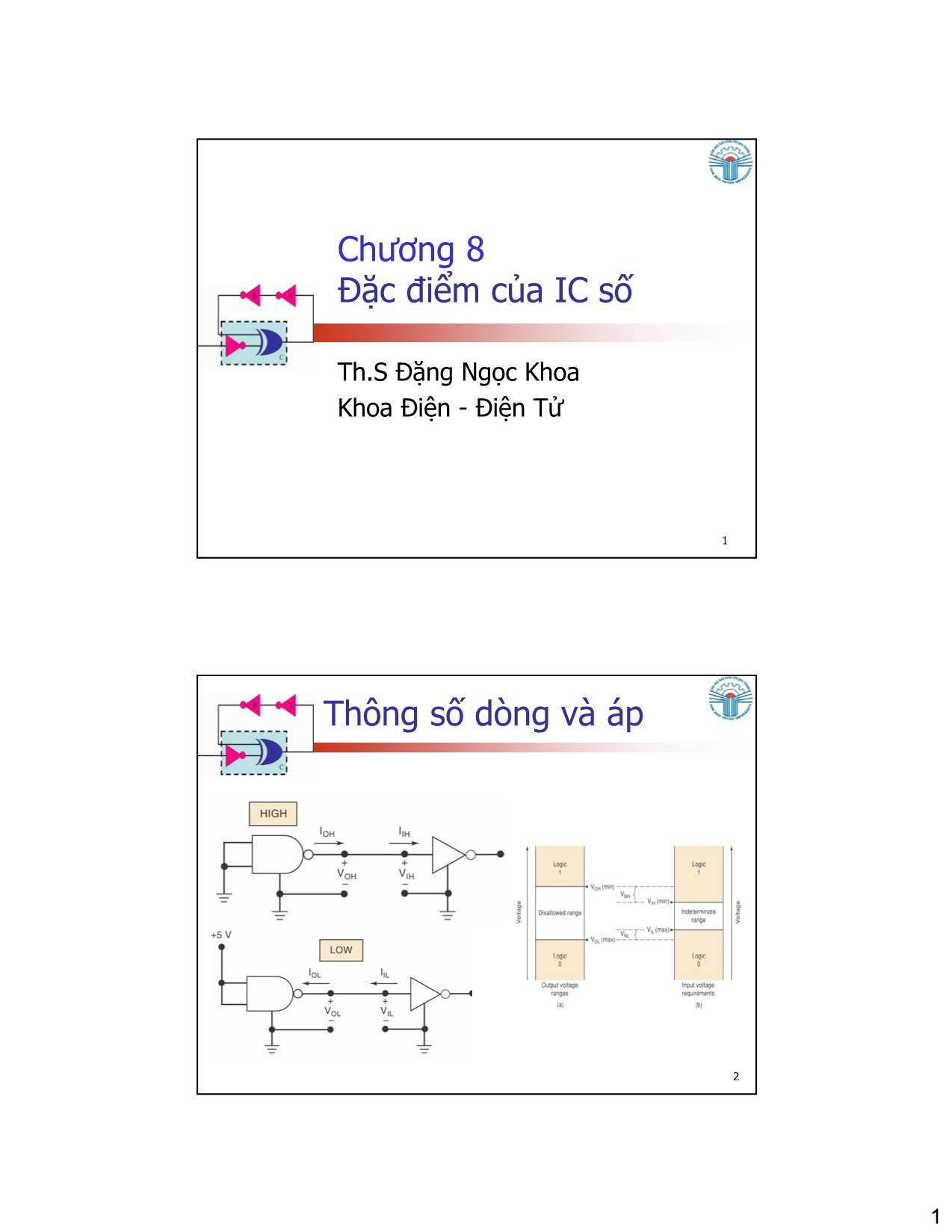

Thông số dòng và áp

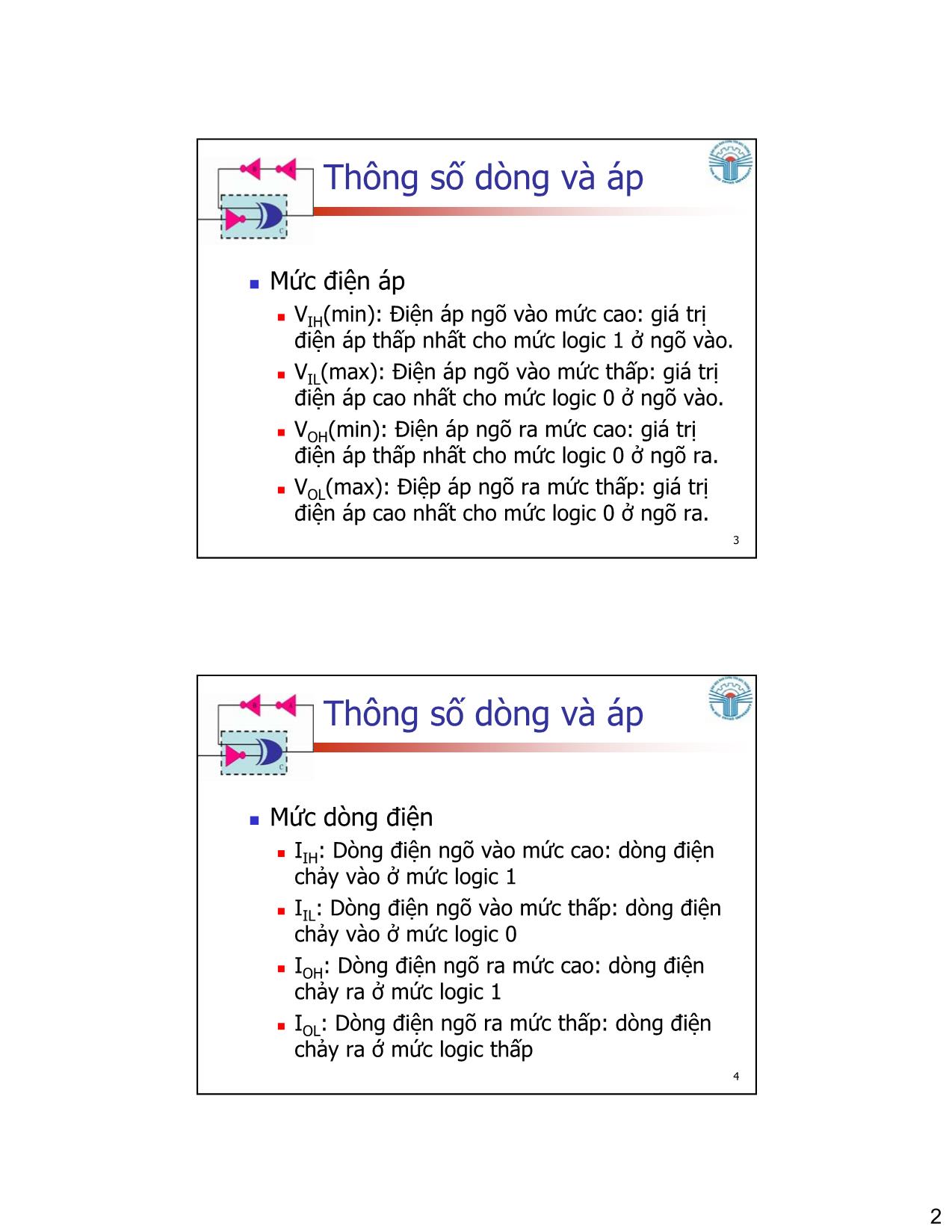

Mức điện áp

V

IH(min): Điện áp ngõ vào mức cao: giá trị

điện áp thấp nhất cho mức logic 1 ở ngõ vào.

V

IL(max): Điện áp ngõ vào mức thấp: giá trị

điện áp cao nhất cho mức logic 0 ở ngõ vào.

V

OH(min): Điện áp ngõ ra mức cao: giá trị

điện áp thấp nhất cho mức logic 0 ở ngõ ra.

V

OL(max): Điệp áp ngõ ra mức thấp: giá trị

điện áp cao nhất cho mức logic 0 ở ngõ ra.

Thông số dòng và áp

Mức dòng điện

I

IH: Dòng điện ngõ vào mức cao: dòng điện

chảy vào ở mức logic 1

I

IL: Dòng điện ngõ vào mức thấp: dòng điện

chảy vào ở mức logic 0

I

OH: Dòng điện ngõ ra mức cao: dòng điện

chảy ra ở mức logic 1

I

OL: Dòng điện ngõ ra mức thấp: dòng điện

chảy ra ớ mức logic thấp

Trang 1

Trang 2

Trang 3

Trang 4

Trang 5

Trang 6

Trang 7

Trang 8

Trang 9

Trang 10

Tải về để xem bản đầy đủ

Tóm tắt nội dung tài liệu: Bài giảng Kỹ thuật số - Chương 8: Đặc điểm của IC số - Đặng Ngọc Khoa

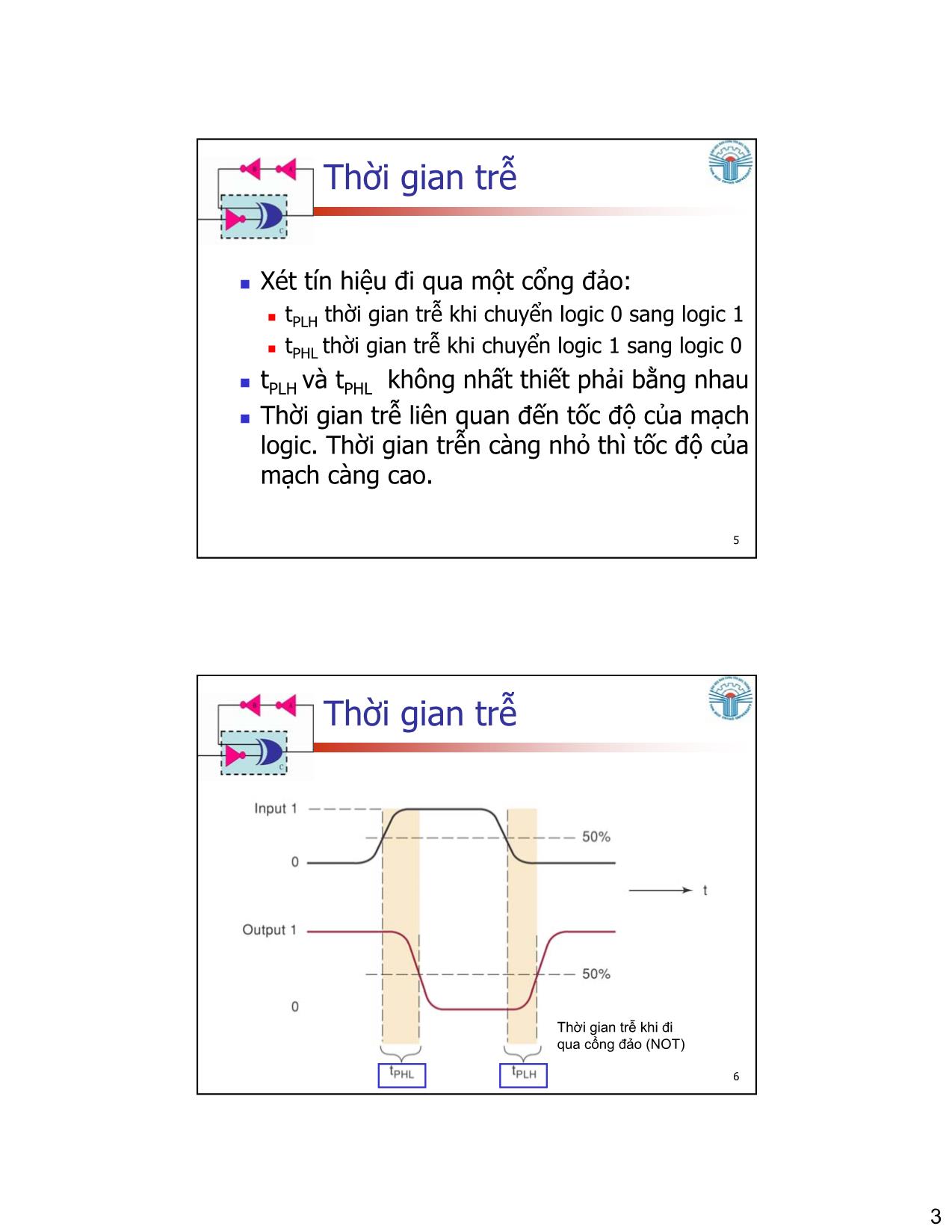

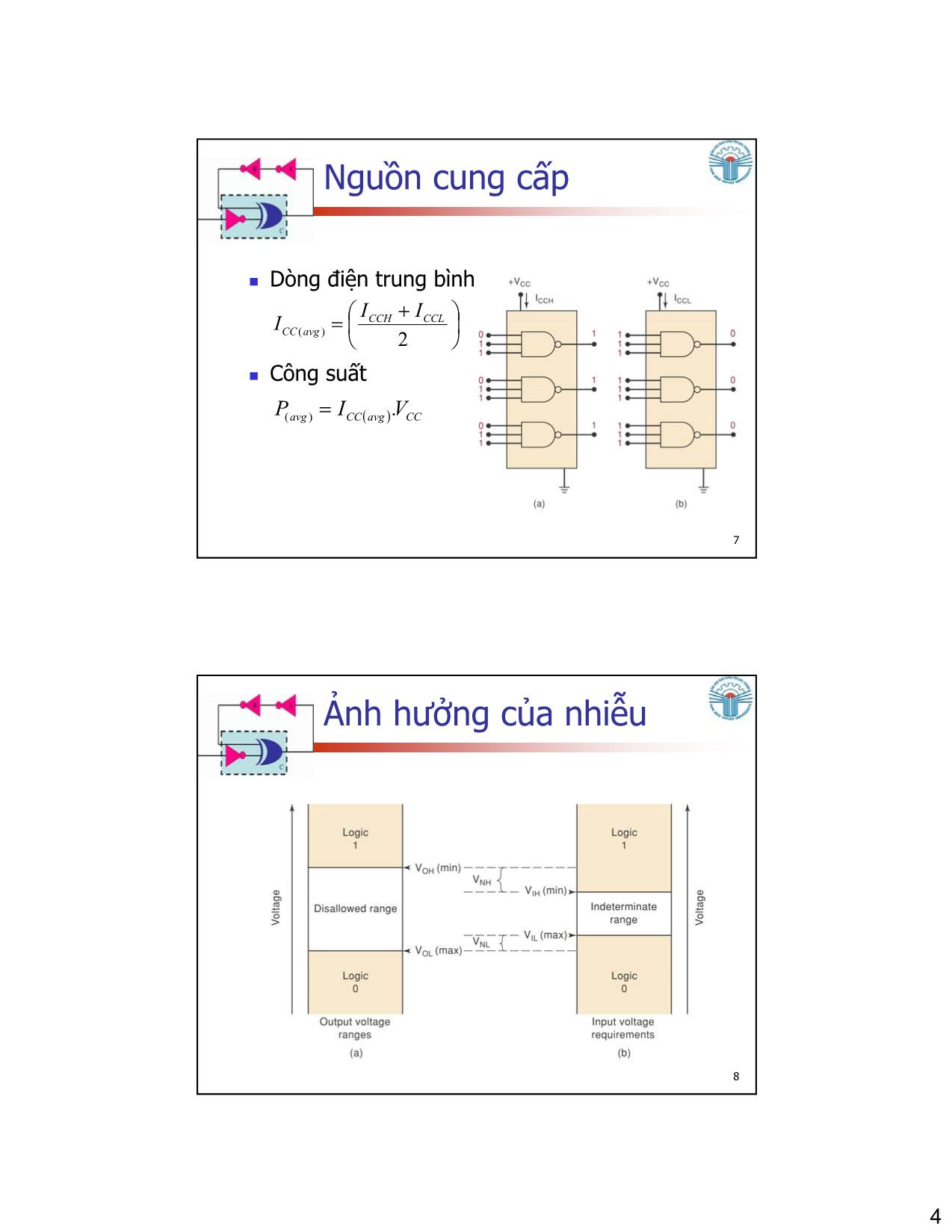

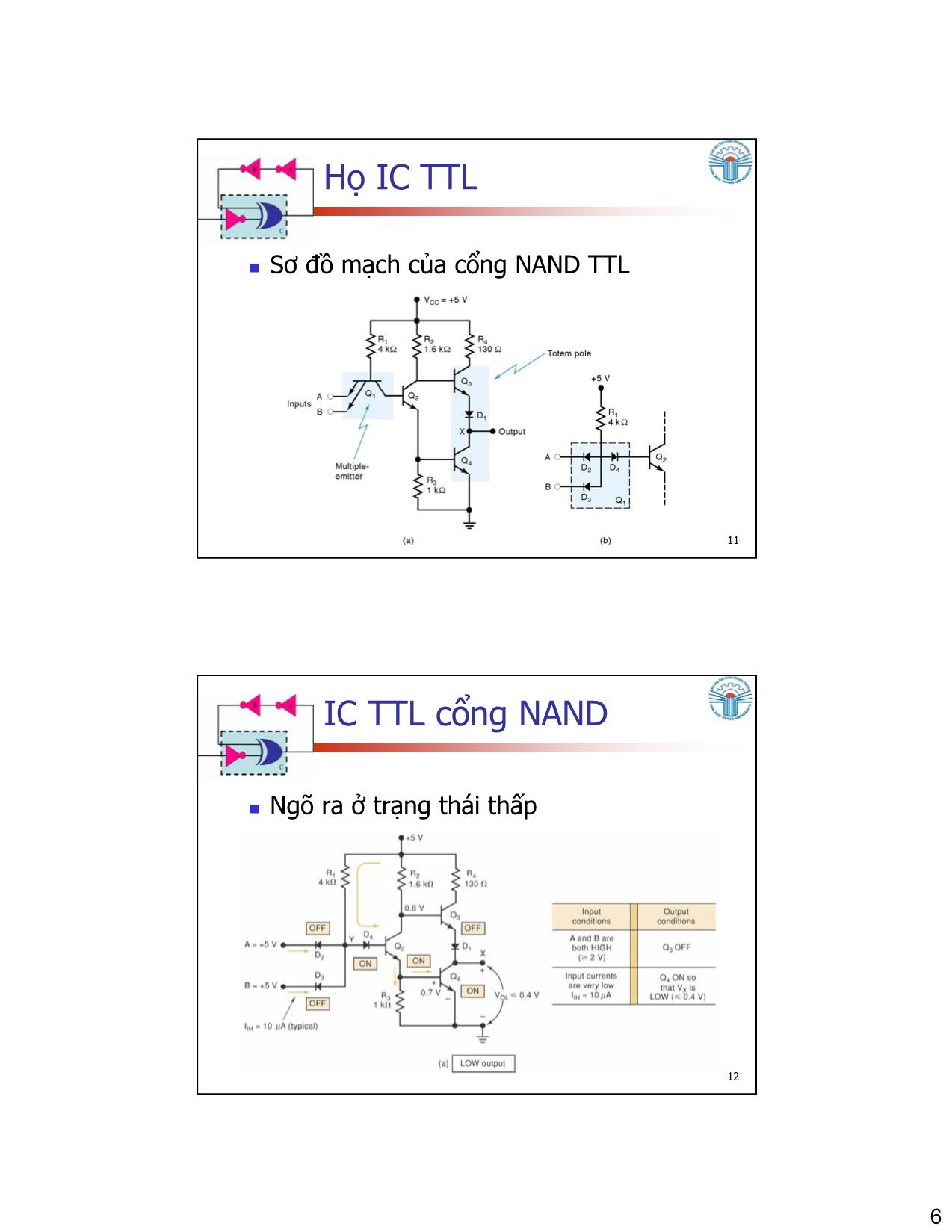

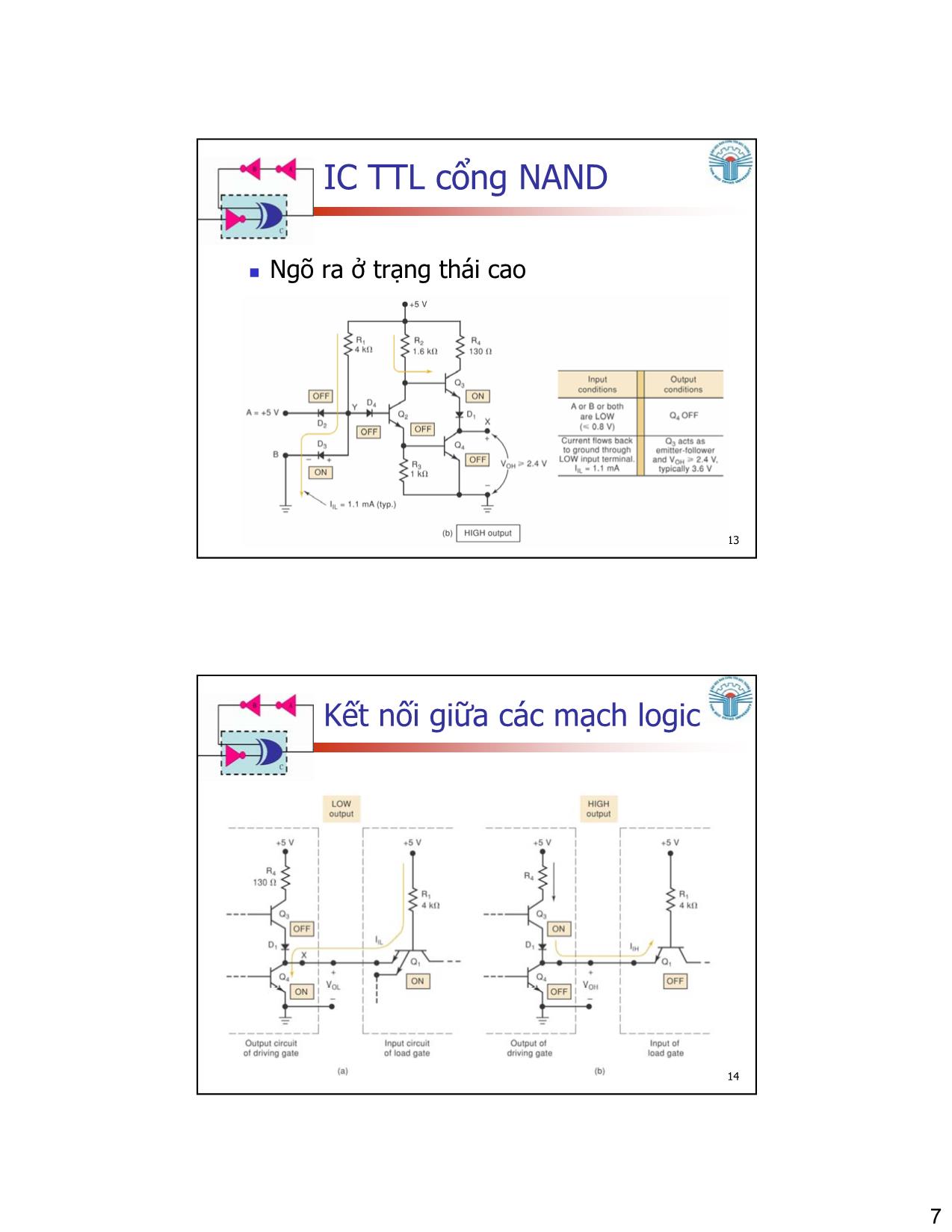

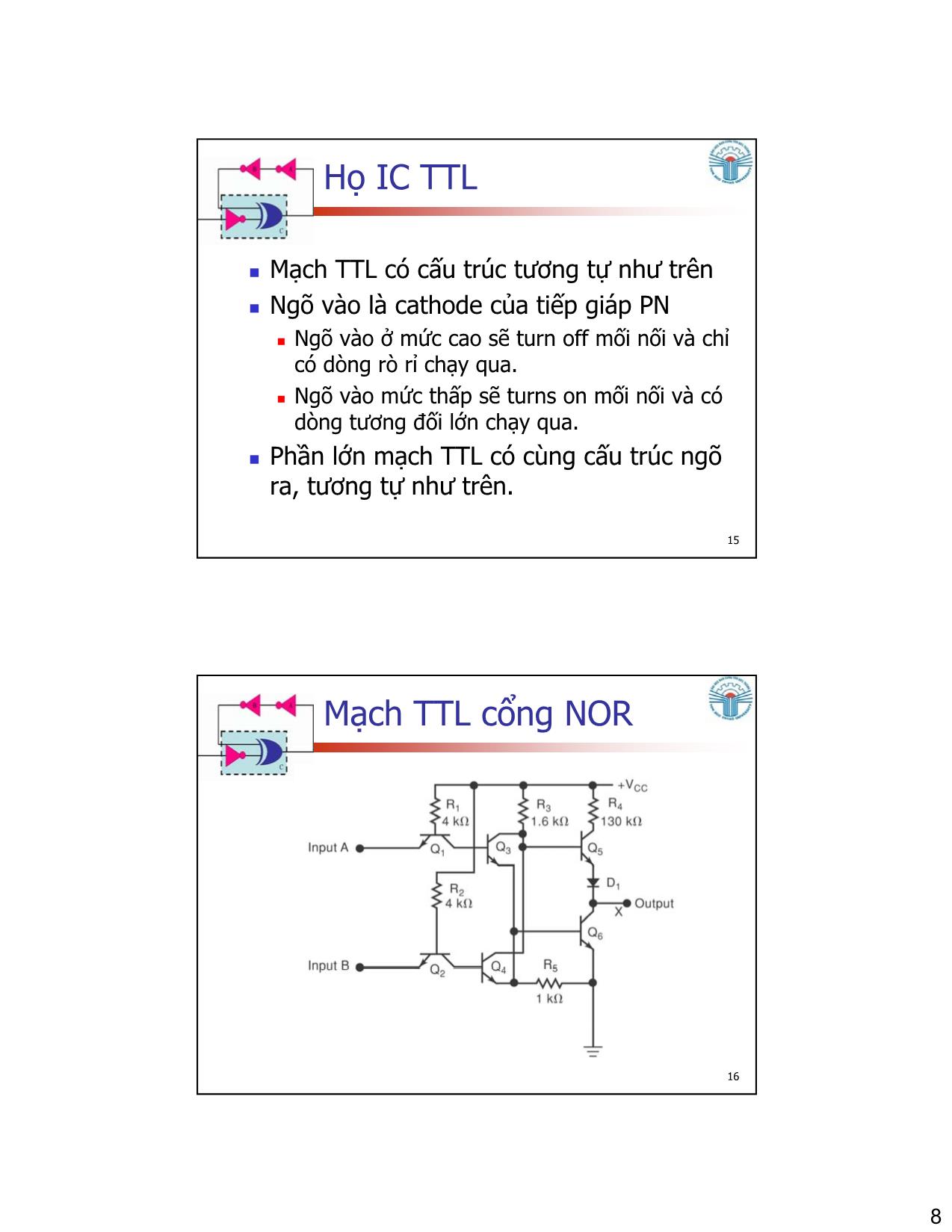

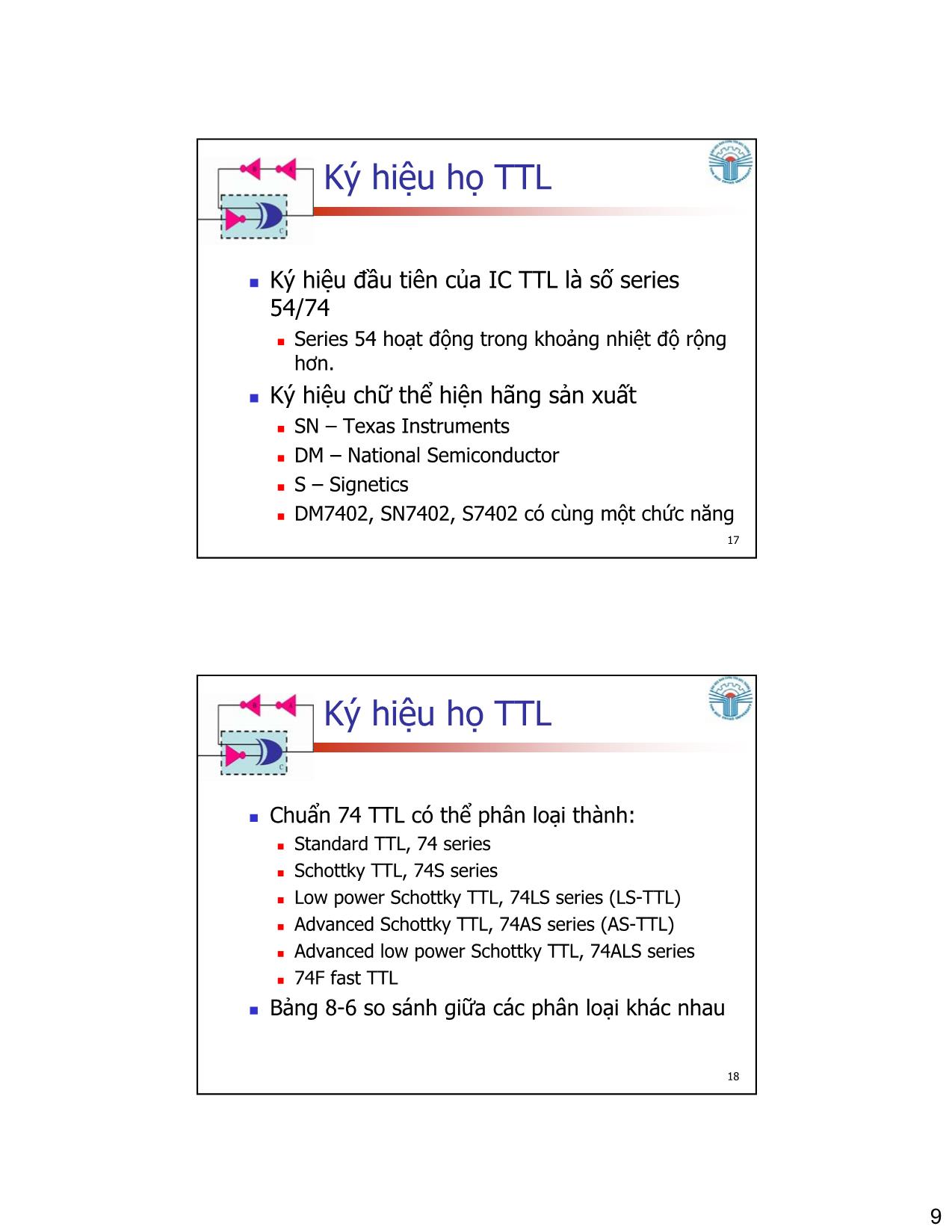

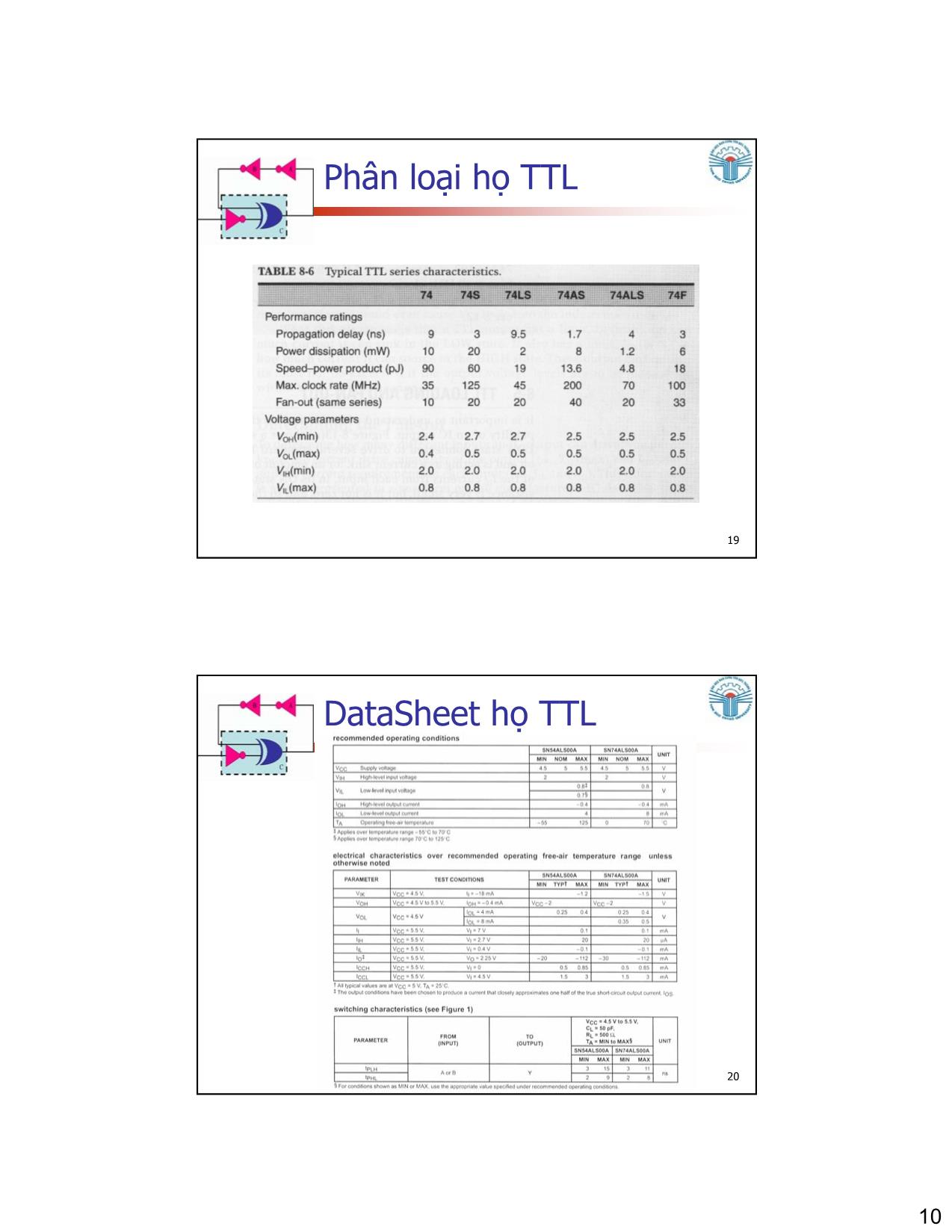

11 Chương 8 Đặc điểm của IC số Th.S Đặng Ngọc Khoa Khoa Điện - Điện Tử 2 Thông số dòng và áp 23 Thông số dòng và áp Mức điện áp VIH(min): Điện áp ngõ vào mức cao: giá trị điện áp thấp nhất cho mức logic 1 ở ngõ vào. VIL(max): Điện áp ngõ vào mức thấp: giá trị điện áp cao nhất cho mức logic 0 ở ngõ vào. VOH(min): Điện áp ngõ ra mức cao: giá trị điện áp thấp nhất cho mức logic 0 ở ngõ ra. VOL(max): Điệp áp ngõ ra mức thấp: giá trị điện áp cao nhất cho mức logic 0 ở ngõ ra. 4 Thông số dòng và áp Mức dòng điện IIH: Dòng điện ngõ vào mức cao: dòng điện chảy vào ở mức logic 1 IIL: Dòng điện ngõ vào mức thấp: dòng điện chảy vào ở mức logic 0 IOH: Dòng điện ngõ ra mức cao: dòng điện chảy ra ở mức logic 1 IOL: Dòng điện ngõ ra mức thấp: dòng điện chảy ra ớ mức logic thấp 35 Thời gian trễ Xét tín hiệu đi qua một cổng đảo: tPLH thời gian trễ khi chuyển logic 0 sang logic 1 tPHL thời gian trễ khi chuyển logic 1 sang logic 0 tPLH và tPHL không nhất thiết phải bằng nhau Thời gian trễ liên quan đến tốc độ của mạch logic. Thời gian trễn càng nhỏ thì tốc độ của mạch càng cao. 6 Thời gian trễ Thời gian trễ khi đi qua cổng đảo (NOT) 47 Nguồn cung cấp Dòng điện trung bình Công suất ⎟⎠ ⎞⎜⎝ ⎛ += 2)( CCLCCH avgCC III ( ) CCavgCCavg VIP .)( = 8 Ảnh hưởng của nhiễu 59 Mức điện áp Mạch hoạt động đúng yêu cầu điện áp ngõ vào nằm trong khoảng xác định nhỏ hơn VIL(max) hoặc lớn hơn VIH(min) Điện áp ngõ ra có thể nằm ngoài khoảng xác định phụ thuộc vào nhà sản xuất hoặc trong trường hợp quá tải. Nguồn cung cấp có mức điện áp không đúng có thể sẽ gây ra mức điện áp ngõ ra không đúng. 10 Current-Sourcing và Current- Sinking Ở trạng thái logic cao, cổng lái cung cấp dòng cho cổng tải Ở trạng thái logic thấp, cổng lái nhận dòng từ cổng tải 611 Họ IC TTL Sơ đồ mạch của cổng NAND TTL 12 IC TTL cổng NAND Ngõ ra ở trạng thái thấp 713 IC TTL cổng NAND Ngõ ra ở trạng thái cao 14 Kết nối giữa các mạch logic 815 Họ IC TTL Mạch TTL có cấu trúc tương tự như trên Ngõ vào là cathode của tiếp giáp PN Ngõ vào ở mức cao sẽ turn off mối nối và chỉ có dòng rò rỉ chạy qua. Ngõ vào mức thấp sẽ turns on mối nối và có dòng tương đối lớn chạy qua. Phần lớn mạch TTL có cùng cấu trúc ngõ ra, tương tự như trên. 16 Mạch TTL cổng NOR 917 Ký hiệu họ TTL Ký hiệu đầu tiên của IC TTL là số series 54/74 Series 54 hoạt động trong khoảng nhiệt độ rộng hơn. Ký hiệu chữ thể hiện hãng sản xuất SN – Texas Instruments DM – National Semiconductor S – Signetics DM7402, SN7402, S7402 có cùng một chức năng 18 Ký hiệu họ TTL Chuẩn 74 TTL có thể phân loại thành: Standard TTL, 74 series Schottky TTL, 74S series Low power Schottky TTL, 74LS series (LS-TTL) Advanced Schottky TTL, 74AS series (AS-TTL) Advanced low power Schottky TTL, 74ALS series 74F fast TTL Bảng 8-6 so sánh giữa các phân loại khác nhau 10 19 Phân loại họ TTL 20 DataSheet họ TTL 11 21 Tải và Fan-Out Fan out thể hiện khả năng ngõ ra của một IC có thể lái được bao nhiên ngõ vào của những IC khác. Một ngõ ra TTL bị giới hạn dòng chảy vào nó khi ở trạng thái thấp. Một ngõ ra TTL bị giới hạn dòng cung cấp (dòng chảy ra) khi nó ở trạng thái cao. Nếu dòng điện vượt quá những giới hạn trên thì điện áp ngõ ra sẽ nằm ngoài khoảng cho phép. 22 Tải và Fan-Out 12 23 Tải và Fan-Out Xác định fan out Cộng IIH của tất cả các ngõ vào có kết nối đến ngõ ra đang xét. Tổng phải nhỏ hơn IOH. Cộng IIL của tất cả các ngõ vào có kết nối đến ngõ ra đang xét. Tổng phải nhỏ hơn IOL. 24 Tải và Fan-Out Ví dụ: ngõ ra của 74ALS00 có thể lái bao nhiêu ngõ vào 74ALS00? 13 25 DataSheet của 74ALS00 26 Tính Fan - out IOHMAX IIHMAX = 20uAmps IOHMAX = -400 uAmps FanoutHIGH = 400uAmp / 20 uAmp = 20 High Output IOHMAX IILMAX = - 0.1 mAmps IOLMAX = 8 mAmps FanoutLOW = 8 mAmp / 0.4 mAmp = 80 Low Output 14 27 Công nghệ MOS MOSFETs - Metal Oxide Semiconductor Field Effect Transistors Sản xuất đơn giản và rẻ hơn Tiêu tốn ít năng lượng Có thể thực hiện được nhiều mạch hơn Dễ bị tác động bởi tĩnh điện 28 Công nghệ MOS Ký hiệu MOSFET kênh N và kênh P 15 29 Công nghệ MOS Trạng thái của MOSFET 30 Logic MOSFET kênh N 16 31 Logic MOSFET kênh P 32 Cổng đảo CMOS 17 33 Cổng NAND CMOS 34 Cổng NOR CMOS 18 35 Ký hiệu họ CMOS 4000/1400 74C 74HC/HCT (high-speed CMOS) 74AC/ACT (advanced CMOS) 74AHC/AHCT (advanced high-speed CMOS) 36 IC điện áp thấp Họ CMOS : 74LVC (low voltage CMOS) 74ALVC (advanced low voltage CMOS) 74LV (low voltage) 74AVC (advanced very low voltage CMOS) 74AUC (advanced ultra-low voltage CMOS) 74AUP (advanced ultra-low power) 74CBT (cross bar technology) 74CBTLV (cross bar technology low voltage) 74GTLP (gunning transceiver logic plus) 74SSTV (stub series terminated logic) 74TVC (translation voltage clamp) 19 37 Cổng Tristate Ba trạng thái đó là: HIGH, LOW và tổng trở cao. 38 Cổng Tristate Tristate được sử dụng làm bộ đệm 20 39 Cổng Tristate Bộ đệm Tristate được sử dụng khi nhiều tín hiệu sử dụng chung bus 40 Giao tiếp giữa các IC Lái (driver) – cung cấp tín hiệu ngõ ra. Tải (load) – nhận tín hiệu. Mạch giao tiếp (interface circuit) – kết nối giữa thiết bị lái và tải. Kết nối giữa những họ IC khác nhau trong cùng một mạch. 21 41 Giao tiếp giữa các IC 42 TTL lái CMOS Về dòng điện, TTL hoàn toàn có thể lái được CMOS. Về điện áp, cần phải có điện trở kéo lên khi 22 43 CMOS lái TTL Trạng thái HIGH Không có vấn đề gì xảy ra khi CMOS lái TTL Trạng thái LOW Không có vấn đề với họ 74HC, 74HCT Những họ khác tùy theo từng trường hợp mà có sự tương thích với nhau 44 Câu hỏi?

File đính kèm:

bai_giang_ky_thuat_so_chuong_8_dac_diem_cua_ic_so_dang_ngoc.pdf

bai_giang_ky_thuat_so_chuong_8_dac_diem_cua_ic_so_dang_ngoc.pdf