Bài giảng Kỹ thuật số - Chương 5: Mạch tuần tự

MẠCH TUẦN TỰ

Mạch tuần tự: Trạng thái ngõ ra không những phụ thuộc vào trạng thái của ngõ

vào mà còn phụ thuộc vào trạng thái của ngõ ra trước đó (được hồi tiếp trở thành

ngõ vào thông qua phần tử nhớ) ta nói mạch tuần tự có tính nhớ.

Q+=f(Q, A, B, C, D, )

Ngõ ra Q+ là hàm logic của các biến ngõ vào và ngõ ra Q trước đó.

Mạch tuần tự: Chia làm 2 loại

• Mạch đồng bộ: Xung đồng hồ CK tác động đồng thời, trạng thái ngõ ra không

thay đổi ngay sau khi trạng thái ngõ vào thay đổi mà phải đợi đến khi xuất

hiện một xung lệnh.

• Mạch không đồng bộ: Xung đồng hồ CK tác động không đồng thời, trạng thái

ngõ ra thay đổi ngay sau khi trạng thái ngõ vào thay đổi (với độ trì hoãn

truyền nào đó).

* Phần tử cơ bản tạo thành mạch tuần tự là Flip-Flop (FF – Mạch lật).

FLIPFLOP

- FF được tạo nên từ mạch chốt (Latch): Chốt là cài lại, giữ lại.

- Điểm khác nhau giữa mạch chốt và FF: FF thì chịu sự tác động

của xung CK, còn mạch chốt thì không.

Mạch chốt + Xung CK Mạch Flip-Flop

Trang 1

Trang 2

Trang 3

Trang 4

Trang 5

Trang 6

Trang 7

Trang 8

Trang 9

Trang 10

Tải về để xem bản đầy đủ

Tóm tắt nội dung tài liệu: Bài giảng Kỹ thuật số - Chương 5: Mạch tuần tự

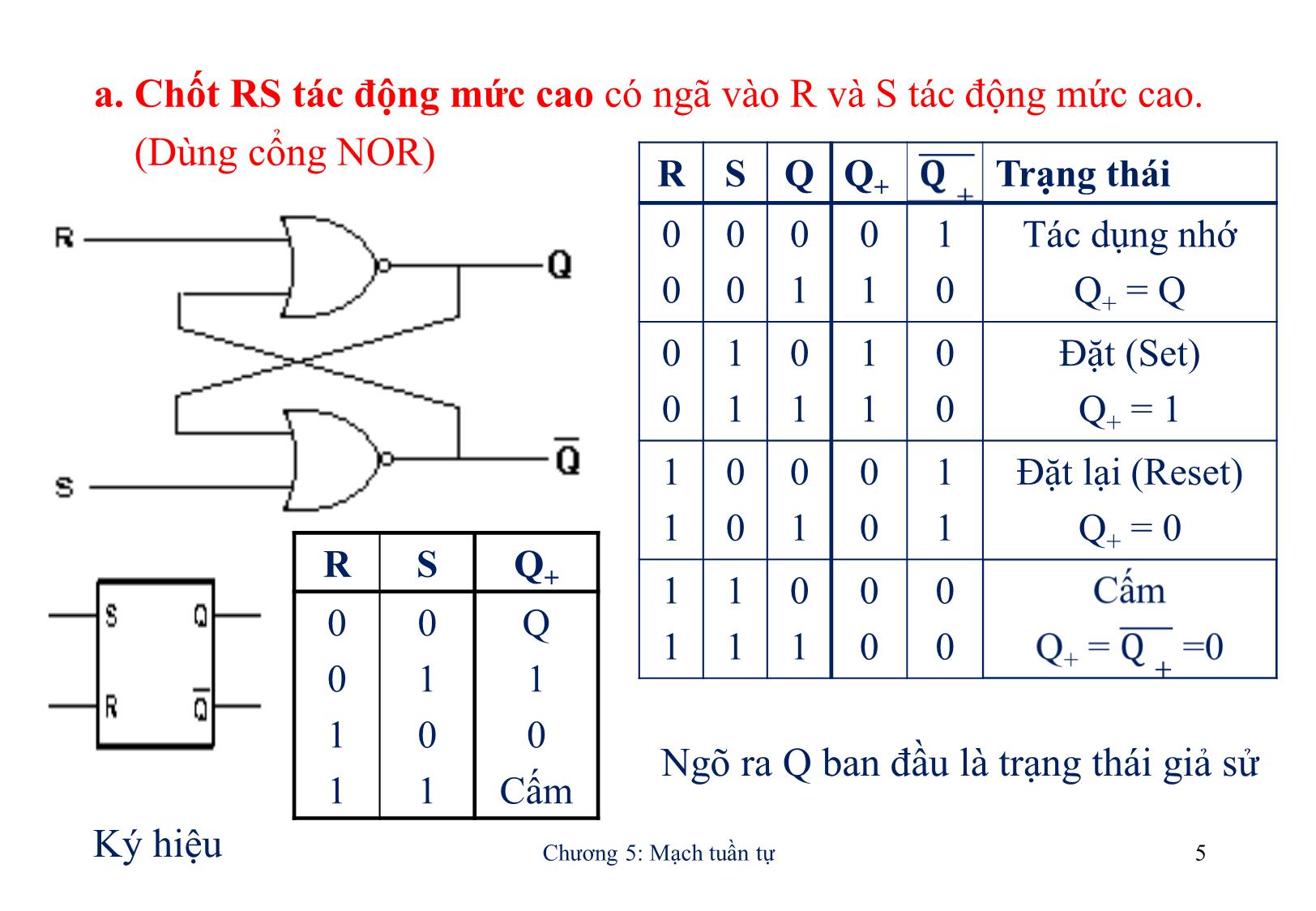

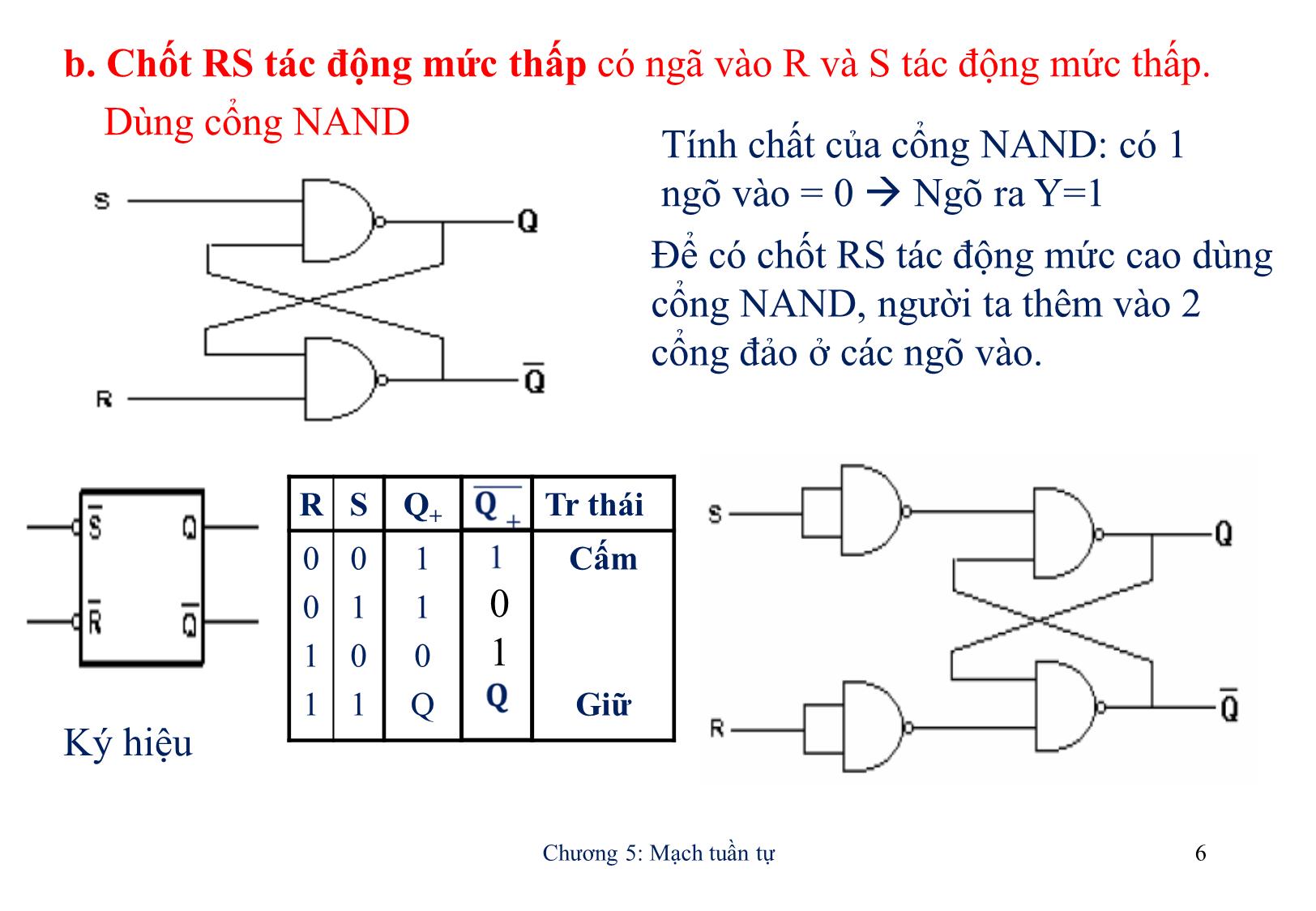

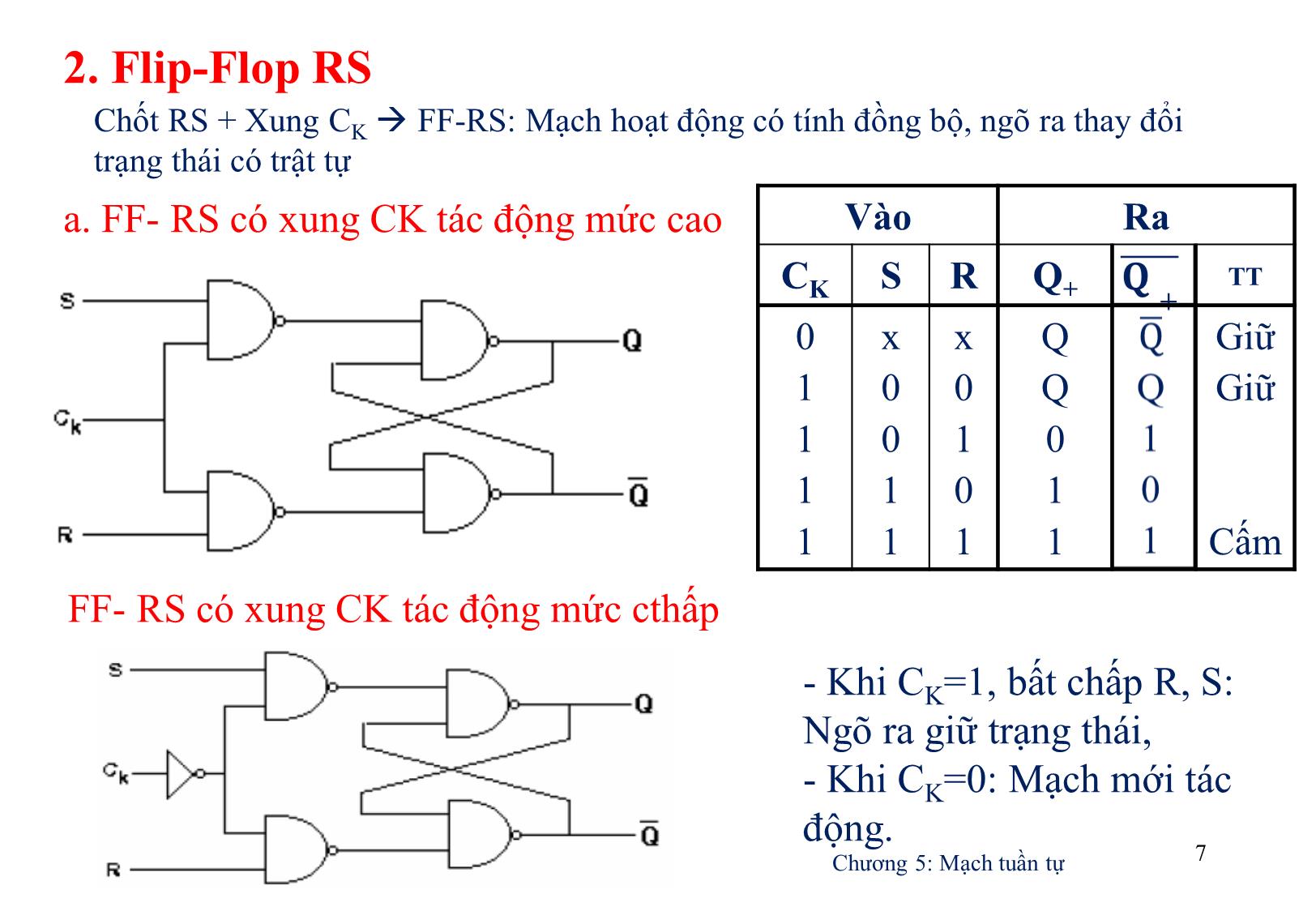

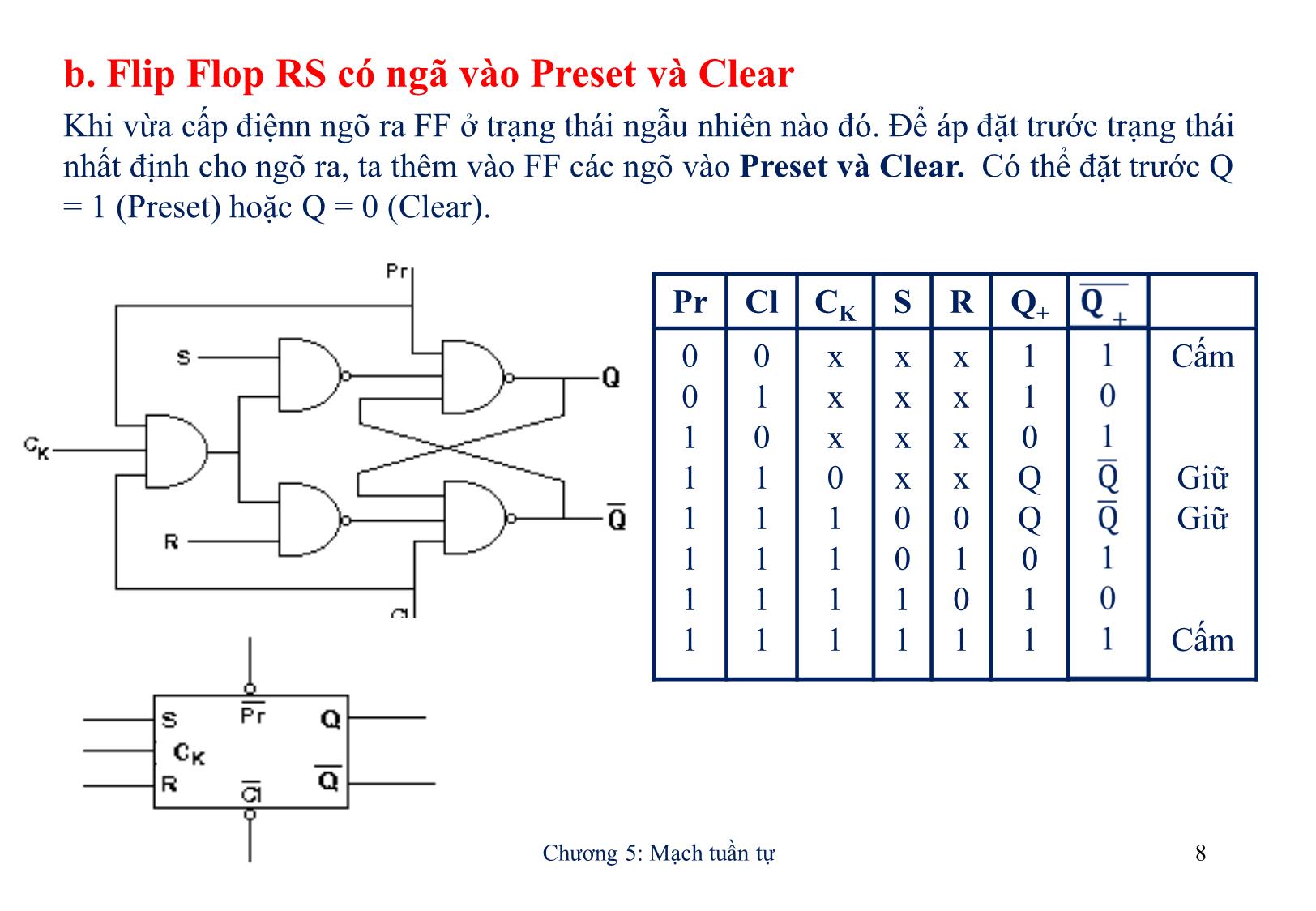

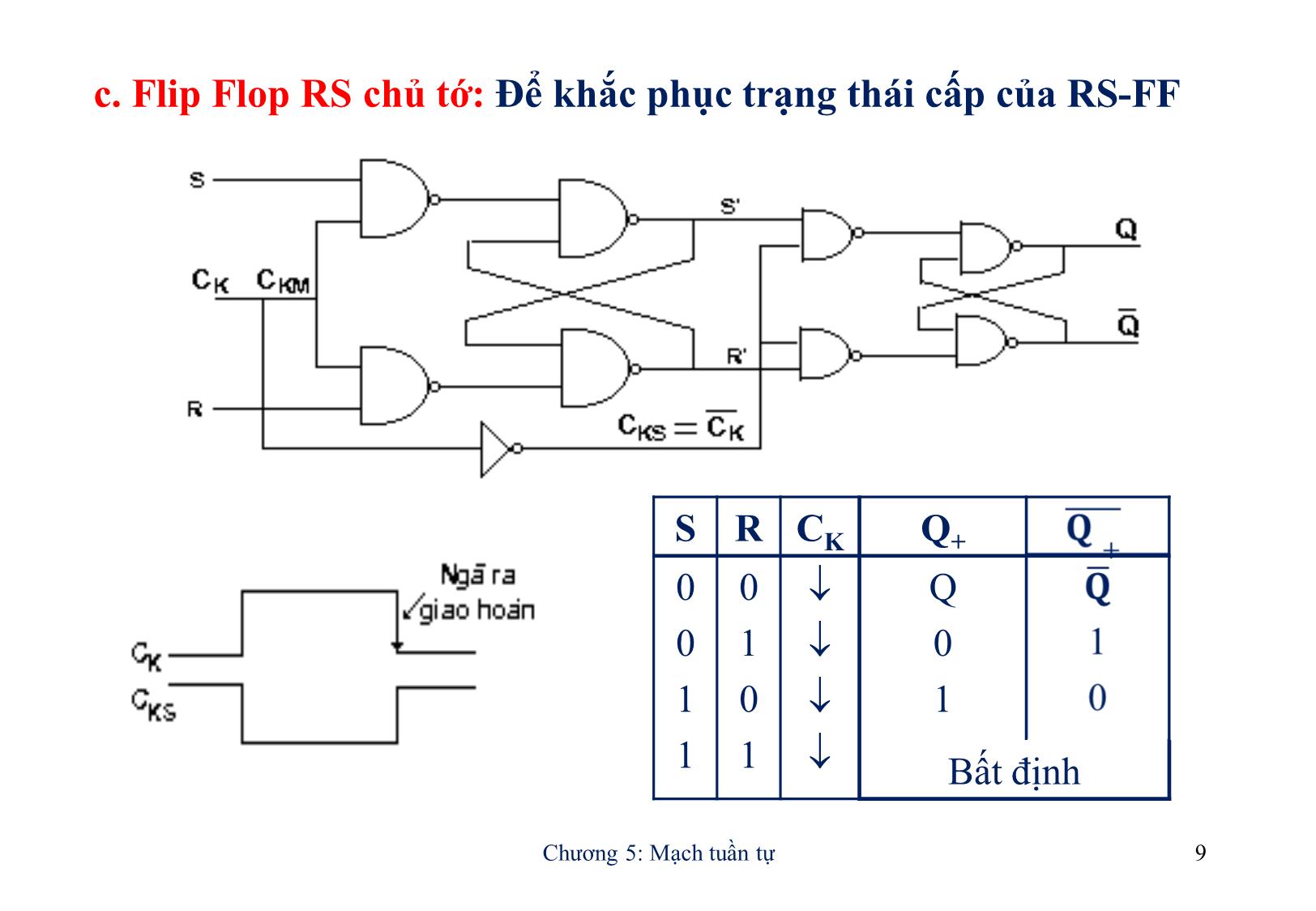

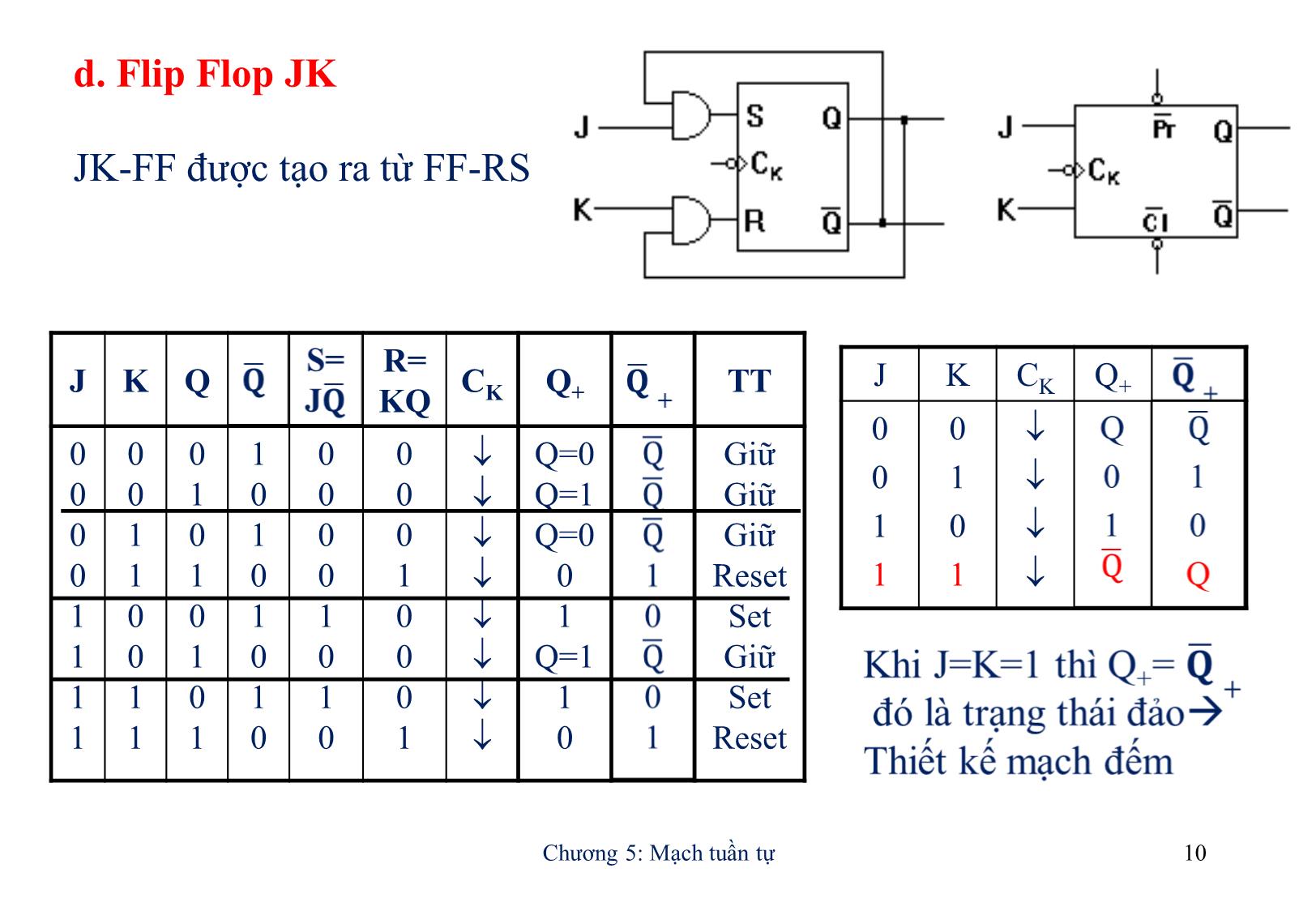

Chương 5: Mạch tuần tự 1 MẠCH TUẦN TỰ CHỐT RS FLIPFLOP MẠCH GHI DỊCH MẠCH ĐẾM CHƢƠNG 5 Chương 5: Mạch tuần tự 2 MẠCH TUẦN TỰ Mạch tuần tự: Trạng thái ngõ ra không những phụ thuộc vào trạng thái của ngõ vào mà còn phụ thuộc vào trạng thái của ngõ ra trước đó (được hồi tiếp trở thành ngõ vào thông qua phần tử nhớ) ta nói mạch tuần tự có tính nhớ. Q+=f(Q, A, B, C, D,) Ngõ ra Q+ là hàm logic của các biến ngõ vào và ngõ ra Q trước đó. Mạch tuần tự: Chia làm 2 loại • Mạch đồng bộ: Xung đồng hồ CK tác động đồng thời, trạng thái ngõ ra không thay đổi ngay sau khi trạng thái ngõ vào thay đổi mà phải đợi đến khi xuất hiện một xung lệnh. • Mạch không đồng bộ: Xung đồng hồ CK tác động không đồng thời, trạng thái ngõ ra thay đổi ngay sau khi trạng thái ngõ vào thay đổi (với độ trì hoãn truyền nào đó). * Phần tử cơ bản tạo thành mạch tuần tự là Flip-Flop (FF – Mạch lật). Chương 5: Mạch tuần tự 3 FLIPFLOP - FF cũng có thể có thêm ngõ vào với chức năng khác Chương 5: Mạch tuần tự 4 FLIPFLOP - FF được tạo nên từ mạch chốt (Latch): Chốt là cài lại, giữ lại. - Điểm khác nhau giữa mạch chốt và FF: FF thì chịu sự tác động của xung CK, còn mạch chốt thì không. Mạch chốt + Xung CK Mạch Flip-Flop 1. Chốt RS Có 2 loại: Chốt cổng NOR và chốt cổng NAND Chương 5: Mạch tuần tự 5 a. Chốt RS tác động mức cao có ngã vào R và S tác động mức cao. (Dùng cổng NOR) R S Q Q+ Trạng thái 0 0 0 0 0 1 0 1 1 0 Tác dụng nhớ Q+ = Q 0 0 1 1 0 1 1 1 0 0 Đặt (Set) Q+ = 1 1 1 0 0 0 1 0 0 1 1 Đặt lại (Reset) Q+ = 0 1 1 1 1 0 1 0 0 0 0 R S Q+ 0 0 1 1 0 1 0 1 Q 1 0 Cấm Ký hiệu Ngõ ra Q ban đầu là trạng thái giả sử Chương 5: Mạch tuần tự 6 b. Chốt RS tác động mức thấp có ngã vào R và S tác động mức thấp. Dùng cổng NAND R S Q+ Tr thái 0 0 1 1 0 1 0 1 1 1 0 Q Cấm Giữ Ký hiệu Tính chất của cổng NAND: có 1 ngõ vào = 0 Ngõ ra Y=1 Để có chốt RS tác động mức cao dùng cổng NAND, người ta thêm vào 2 cổng đảo ở các ngõ vào. 0 1 Chương 5: Mạch tuần tự 7 2. Flip-Flop RS Vào Ra CK S R Q+ TT 0 1 1 1 1 x 0 0 1 1 x 0 1 0 1 Q Q 0 1 1 Giữ Giữ Cấm Chốt RS + Xung CK FF-RS: Mạch hoạt động có tính đồng bộ, ngõ ra thay đổi trạng thái có trật tự a. FF- RS có xung CK tác động mức cao FF- RS có xung CK tác động mức cthấp - Khi CK=1, bất chấp R, S: Ngõ ra giữ trạng thái, - Khi CK=0: Mạch mới tác động. Chương 5: Mạch tuần tự 8 b. Flip Flop RS có ngã vào Preset và Clear Khi vừa cấp điệnn ngõ ra FF ở trạng thái ngẫu nhiên nào đó. Để áp đặt trước trạng thái nhất định cho ngõ ra, ta thêm vào FF các ngõ vào Preset và Clear. Có thể đặt trước Q = 1 (Preset) hoặc Q = 0 (Clear). Pr Cl CK S R Q+ 0 0 1 1 1 1 1 1 0 1 0 1 1 1 1 1 x x x 0 1 1 1 1 x x x x 0 0 1 1 x x x x 0 1 0 1 1 1 0 Q Q 0 1 1 Cấm Giữ Giữ Cấm Chương 5: Mạch tuần tự 9 c. Flip Flop RS chủ tớ: Để khắc phục trạng thái cấp của RS-FF S R CK Q+ 0 0 1 1 0 1 0 1 Q 0 1 Bất định Chương 5: Mạch tuần tự 10 d. Flip Flop JK J K Q R= KQ CK Q+ TT 0 0 0 0 1 1 1 1 0 0 1 1 0 0 1 1 0 1 0 1 0 1 0 1 1 0 1 0 1 0 1 0 0 0 0 0 1 0 1 0 0 0 0 1 0 0 0 1 Q=0 Q=1 Q=0 0 1 Q=1 1 0 Giữ Giữ Giữ Reset Set Giữ Set Reset J K CK Q+ 0 0 1 1 0 1 0 1 JK-FF được tạo ra từ FF-RS Chương 5: Mạch tuần tự 11 e. Flip Flop D D CK Q+ 0 1 0 1 1 0 f. Flip Flop T T CK Q+ TT 0 1 Giữ Đảo g. Mạch chốt D G D Q+ 0 1 1 x 0 1 Q 0 1 Chốt D giống FF-D, Xung CK được thay bằng ngõ vào cho phép G Chương 5: Mạch tuần tự 12 3. Mạch ghi dịch(Shift Register) Do mỗi FF có khả năng nhớ 1 bit ở ngõ ra cho đến khi có 1 xung CK tác động nên người ta mắc nối tiếp nhiều FF lại để tạo thành mạch ghi dịch sẽ nhớ được nhiều bit. - Mạch dịch phải: Ta mắc mạch gồm 4 FF D nối thành chuỗi (ngã ra Q của FF trước nối vào ngã vào D của FF sau) và các ngã vào CK được nối chung lại (các FF chịu tác động đồng thời). Mạch ghi dịch này có khả năng dịch phải. Ngã vào DA của FF đầu tiên được gọi là ngã vào dữ liệu nối tiếp, các ngã ra QA, QB, QC, QD là các ngã ra song song, ngã ra của FF cuối cùng (FF D) là ngã ra nối tiếp. Chương 5: Mạch tuần tự 13 Vào Ra Cl CK DA QA QB QC QD 0 1 1 1 1 1 1 1 x x 1 1 1 0 0 1 0 0 1 1 1 0 0 1 0 0 0 1 1 1 0 0 1 0 0 0 1 1 1 0 0 0 0 0 0 1 1 1 0 Mạch dịch phải Chương 5: Mạch tuần tự 14 Vào Ra Cl CK D4 QA QB QC QD 0 1 1 1 1 1 1 1 x x 1 1 1 0 0 1 0 0 0 0 0 1 1 1 0 0 0 0 1 1 1 0 0 0 0 1 1 1 0 0 1 0 1 1 1 0 0 1 0 Mạch dịch trái Chương 5: Mạch tuần tự 15 IC 7 4 1 6 4 IC 7 4 9 5 Chương 5: Mạch tuần tự 16 - Mạch đếm được thiết kế từ JK-FF hoặc T-FF. Lợi dụng tính đảo trạng thái của FF JK khi J=K=1. - Chức năng của mạch đếm là đếm số xung CK đưa vào ngã vào hoặc thể hiện số trạng thái có thể có của các ngã ra. - Về lĩnh vực tần số của tín hiệu thì mạch đếm có chức năng chia tần, nghĩa là tần số của tín hiệu ở ngã ra là kết quả của phép chia tần số của tín hiệu CK ở ngã vào cho số đếm của mạch. - Ta có các loại: mạch đếm đồng bộ, không đồng bộ và đếm vòng. MẠCH ĐẾM Chương 5: Mạch tuần tự 17 - Tất cả các FF chịu tác động đồng thời của xung CK Mạch đếm đồng bộ (Synchonous Counter - còn gọi là mạch đếm song song) 1. Mạch đếm đồng bộ n tẩng (đếm 2n trạng thái), đếm lên (count up). - Thiết kế mạch đếm n tầng, đếm lên (n=3) • Xác định số FF cần dùng, Lập bảng trạng thái suy ra cách mắc các ngõ vào JK của các FF sao cho khi có xung CK tác động thì các ngõ ra của FF thay đổi trạng thái giống như bảng trạng thái đã lập • Với n=3 Cần 3 FF, mạch sẽ đếm được 2n=8 trạng thái từ 0 7. Giả sử dùng FF tác động ở cạnh xuống của xung CK Chương 5: Mạch tuần tự 18 CK7 QC QB QA Số đếm Xóa 1 2 3 4 5 6 7 8 9 0 1 1 1 1 0 0 0 0 1 0 1 1 0 0 1 1 0 0 1 0 1 0 1 0 1 0 1 0 1 0 7 6 5 4 3 2 1 0 7 Lập bảng trạng thái – với QC là MSB Chương 5: Mạch tuần tự 19 Từ kết quả trên vẽ mạch đếm đồng bộ 3 bit như sau: * TA=JA=KA=1 * TB=JB=KB=QA * TC=JC=KC=QA.QB Chương 5: Mạch tuần tự 20 2. Mạch đếm đồng bộ n tẩng (đếm 2n trạng thái), đếm xuống (count down). - TK mạch đếm n tầng, đếm xuống (n=3) Lập bảng trạng thái – với QC là MSB CK QC QB QA Số đếm Xóa 1 2 3 4 5 6 7 8 0 1 1 1 1 0 0 0 0 0 1 1 0 0 1 1 0 0 0 1 0 1 0 1 0 1 0 0 7 6 5 4 3 2 1 0 Chương 5: Mạch tuần tự 21 Từ kết quả trên vẽ mạch đếm đồng bộ 3 bit như sau: Chương 5: Mạch tuần tự 22 3. Mạch đếm đồng bộ Modulo–N (N 2n) – Không theo số nhị phân Thiết kế: Trước tiên phải chọn số tầng (Số FF). Số tầng n phải thỏa điều kiện: 2n-1 < N < 2n CK J K Q Q+ H 0 0 0 0 1 1 1 1 0 0 1 1 0 0 1 1 0 1 0 1 0 1 0 1 0 1 0 0 1 1 1 0 0 0 0 1 1 0 1 1 KQQJH P.P dùng hàm Chuyển: Cho thấy sự thay đổi trạng thái của FF, mỗi loại FF sẽ có hàm chuyển riêng. (dùng hàm chuyển của FF-JK). Hàm Chuyển có giá trị H=1 khi Q+ Q và trị H=0 khi Q+ = Q KQ J 00 01 11 10 0 1 1 1 1 1 H Chương 5: Mạch tuần tự 23 3. Mạch đếm đồng bộ Modulo–N (N 2n) – Không theo số nhị phân Để thiết kế mạch đếm cụ thể ta sẽ xác định hàm H của từng FF, sau đó đem so sánh với biểu thức hàm H của FF-JK Từ đó suy J, K của các FF của mạch cần thiết kế. KQQJH VD: Thiết kế mạch đếm 10 đồng bộ dùng FF JK Bước 1: Chọn số tầng: 2n-1 < N < 2n có nghĩa 24-1 < 10 < 24 Số FF là 4, Dùng FF-JK (A, B, C, D với D là MSB) có xung CK tác động bằng cạnh xuống. PP thiết kế: dùng hàm chuyển của JK-FF: KQQJH Chương 5: Mạch tuần tự 24 Bước 2: Lập bảng trạng thái của mạch đếm 10 và giá trị của hàm H CK QD QC QB QA QD+ QC+ QB+ QA+ HD HC HB HA 1 2 3 4 5 6 7 8 9 10 0 0 0 0 0 0 0 0 1 1 0 0 0 0 1 1 1 1 0 0 0 0 1 1 0 0 1 1 0 0 0 1 0 1 0 1 0 1 0 1 0 0 0 0 0 0 0 1 1 0 0 0 0 1 1 1 1 0 0 0 0 1 1 0 0 1 1 0 0 0 1 0 1 0 1 0 1 0 1 0 0 0 0 0 0 0 0 1 0 1 0 0 0 1 0 0 0 1 0 0 0 1 0 1 0 1 0 1 0 0 1 1 1 1 1 1 1 1 1 1 Chương 5: Mạch tuần tự 25 Bước 3: Lập bảng Karnaugh, so sánh với hàm chuyển KQQJH KQQJH Chương 5: Mạch tuần tự 26 Lập bảng Karnaugh, so sánh với hàm chuyển KQQJH Chương 5: Mạch tuần tự 27 CK QD QC QB QA HD HC HB HA QD+ QC+ QB+ QA+ 10 11 12 13 14 15 1 1 1 1 1 1 0 0 1 1 1 1 1 1 0 0 1 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 0 0 1 0 0 0 0 0 0 1 1 1 1 1 1 1 0 1 0 1 0 0 1 1 1 1 0 1 1 0 0 1 1 1 0 1 0 1 0 AD ABCD ABCC ADBB AA QK Q.Q.QJ Q.QKJ Q.QKJ 1KJ Chương 5: Mạch tuần tự 28 - Là các mạch đếm mà các FF chịu sự tác động của xung CK không đồng thời. - Cần quan tâm đến chiều tác động của xung CK Mạch đếm không đồng bộ 1. Mạch đếm không đồng bộ n tẩng (đếm 2n trạng thái), đếm lên - Thiết kế mạch đếm n tầng, đếm lên (n=4) • Lập bảng trạng thái suy ra cách mắc các ngõ vào JK của các FF sao cho khi có xung CK tác động thì các ngõ ra của FF thay đổi trạng thái giống như bảng trạng thái đã lập • Với n=4 Cần 4 FF, mạch sẽ đếm được 2n=16 trạng thái từ 0 15. Giả sử dùng FF tác động ở cạnh xuống của xung CK • Do xung CK tác động bởi cạnh xuống có thể lấy ngõ ra của tầng trước làm xung CK của tầng sau. Chương 5: Mạch tuần tự 29 Lập bảng trạng thái CK QD QC QB QA Số đếm Xóa 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 0 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1 0 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 0 Chương 5: Mạch tuần tự 30 Chương 5: Mạch tuần tự 31 2. Mạch đếm không đồng bộ n tẩng (đếm 2n trạng thái), đếm xuống Chương 5: Mạch tuần tự 32 Chương 5: Mạch tuần tự 33 3. Mạch đếm không đồng bộ modulo – N (N = 10) Kiểu Reset: Số xung CK vào Số nhị phân ra Số thập phân tƣơng ứng QD QC QB QA Xoá 1 2 3 4 5 6 7 8 9 10 0 0 0 0 0 0 0 0 1 1 0(1) 0 0 0 0 1 1 1 1 0 0 0 0 0 1 1 0 0 1 1 0 0 0(1) 0 1 0 1 0 1 0 1 0 1 0 0 1 2 3 4 5 6 7 8 9 10 34 Mạch đếm không đồng bộ modulo – N kiểu Preset: - Phân tích số đếm N = 2n.N’ (N’<N) kết hợp hai mạch đếm n bit và N’ Thiết kế mạch đếm 10 = 2 x 5 mạch đếm 5 kết hợp với một FF Số xung CK vào Số nhị phân ra Số thập phân tƣơng ứng QD QC QB Xóa 1 2 3 4 5 0 0 0 0 1 0 0 0 1 1 0 0 0 1 0 1 0 0 0 1 2 3 4 0 Chương 5: Mạch tuần tự 35 Dùng hàm Chuyển CK QD QC QB HD HB 1 2 3 4 5 0 0 0 0 1 0 0 0 1 1 0 0 0 1 0 1 0 0 0 0 0 1 1 1 1 1 1 0 1K Q.QJ QC 1KJ 1K QJ D BCD BKC CC B DB 36 IC7490 Reset Inputs Outputs R0(1) R0(2) R0(3) R0(4) QD QC QB QA 1 1 0 x x 0 0 x 1 1 x 0 0 x x 0 0 x 1 1 x 0 x 0 x 0 1 1 0 x 0 x 0 0 1 1 Đếm nt nt nt 0 0 0 0 Đếm nt nt Nt 0 0 0 0 Đếm nt nt Nt 0 0 1 1 Đếm nt nt nt 37 QD QC QB QA 0 0 0 0 0 0 0 0 1 1 0 0 0 0 1 1 1 1 0 0 0 0 1 1 0 0 1 1 0 0 0 1 0 1 0 1 0 1 0 1 QD QC QB QA 0 0 0 0 1 0 0 0 0 1 0 0 1 1 0 0 0 1 1 0 0 1 0 1 0 1 0 1 0 1 0 0 0 0 0 1 1 1 1 1 Đếm 2x5 Đếm 5x2 Chương 5: Mạch tuần tự 38 Mạch đếm vòng: Hồi tiếp từ QD JA và QD KA CK QD Q C QB QA Số TP Preset 1 2 3 4 : 0 0 0 1 0 : 0 0 1 0 0 : 0 1 0 0 0 : 1 0 0 0 1 : 1 2 4 8 1 : CK QD Q C QB QA Số TP Preset 1 2 3 4 : 0 0 1 1 0 : 0 1 1 0 0 : 1 1 0 0 1 : 1 0 0 1 1 : 3 6 12 9 3 : Đặt trước QA = 1 Đặt trước QA = QB = 1 Mạch đếm vòng Chương 5: Mạch tuần tự 39 CK QD QC QB QA Số TP Preset 1 2 3 4 5 6 7 8 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1 0 0 0 0 0 1 3 7 15 14 12 8 0 Chương 5: Mạch tuần tự 40 CK QD QC QB QA Số TP Preset 1 2 3 4 5 6 7 0 0 0 0 1 1 1 0 0 0 0 1 1 1 0 0 0 0 1 1 1 0 0 0 0 1 1 1 0 0 0 0 0 1 3 7 14 12 8 0

File đính kèm:

bai_giang_ky_thuat_so_chuong_5_mach_tuan_tu.pdf

bai_giang_ky_thuat_so_chuong_5_mach_tuan_tu.pdf