Bài giảng Kỹ thuật số - Chương 4: Mạch tổ hợp

CÁC BƢỚC THIẾT KẾ MẠCH TỔ HỢP

B1: Dựa vào yêu cầu của bài toán, xác định số biến ngõ vào và

số biến ngõ ra (đặt tên biến).

B2: Lập bảng sự thật cho mối quan hệ giữa ngõ vào và ngõ ra

(hoạt động của mạch).

B3: Rút gọn hàm bằng PP tối ƣu nhất.

B4: Vẽ sơ đồ nguyên lý của mạch.

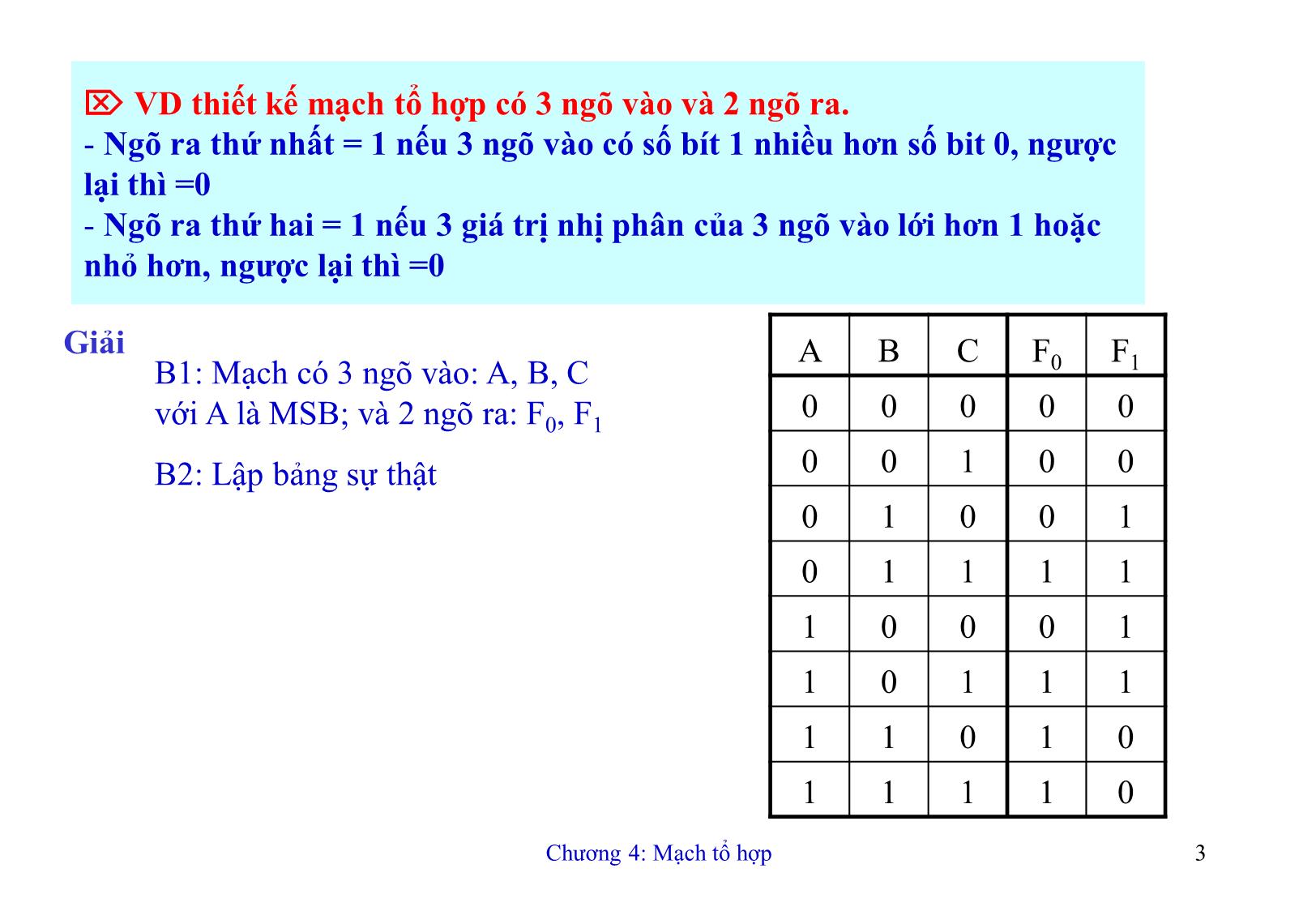

VD thiết kế mạch tổ hợp có 3 ngõ vào và 2 ngõ ra.

- Ngõ ra thứ nhất = 1 nếu 3 ngõ vào có số bít 1 nhiều hơn số bit 0, ngƣợc

lại thì =0

- Ngõ ra thứ hai = 1 nếu 3 giá trị nhị phân của 3 ngõ vào lới hơn 1 hoặc

nhỏ hơn, ngƣợc lại thì =0

Trang 1

Trang 2

Trang 3

Trang 4

Trang 5

Trang 6

Trang 7

Trang 8

Trang 9

Trang 10

Tải về để xem bản đầy đủ

Bạn đang xem 10 trang mẫu của tài liệu "Bài giảng Kỹ thuật số - Chương 4: Mạch tổ hợp", để tải tài liệu gốc về máy hãy click vào nút Download ở trên

Tóm tắt nội dung tài liệu: Bài giảng Kỹ thuật số - Chương 4: Mạch tổ hợp

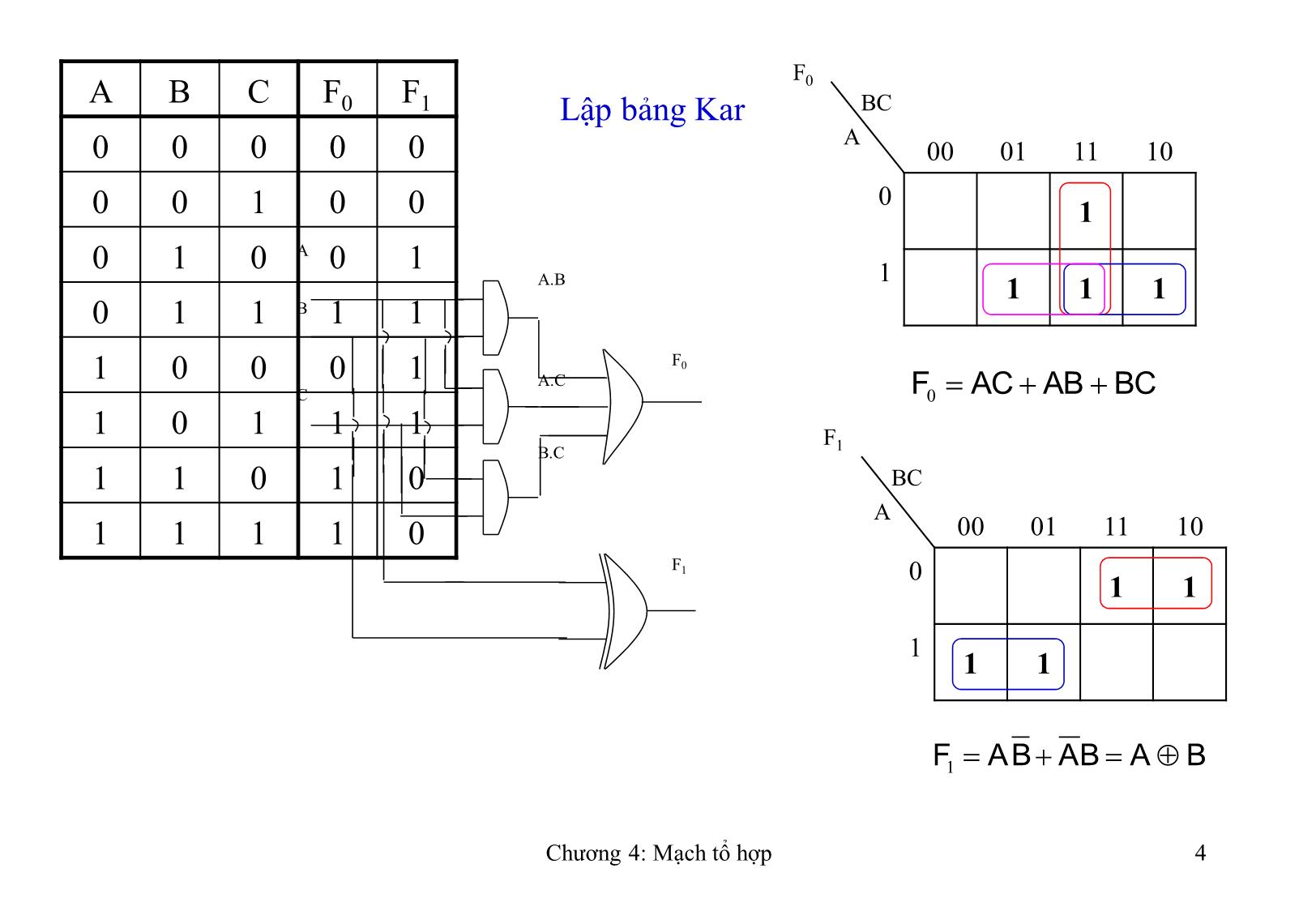

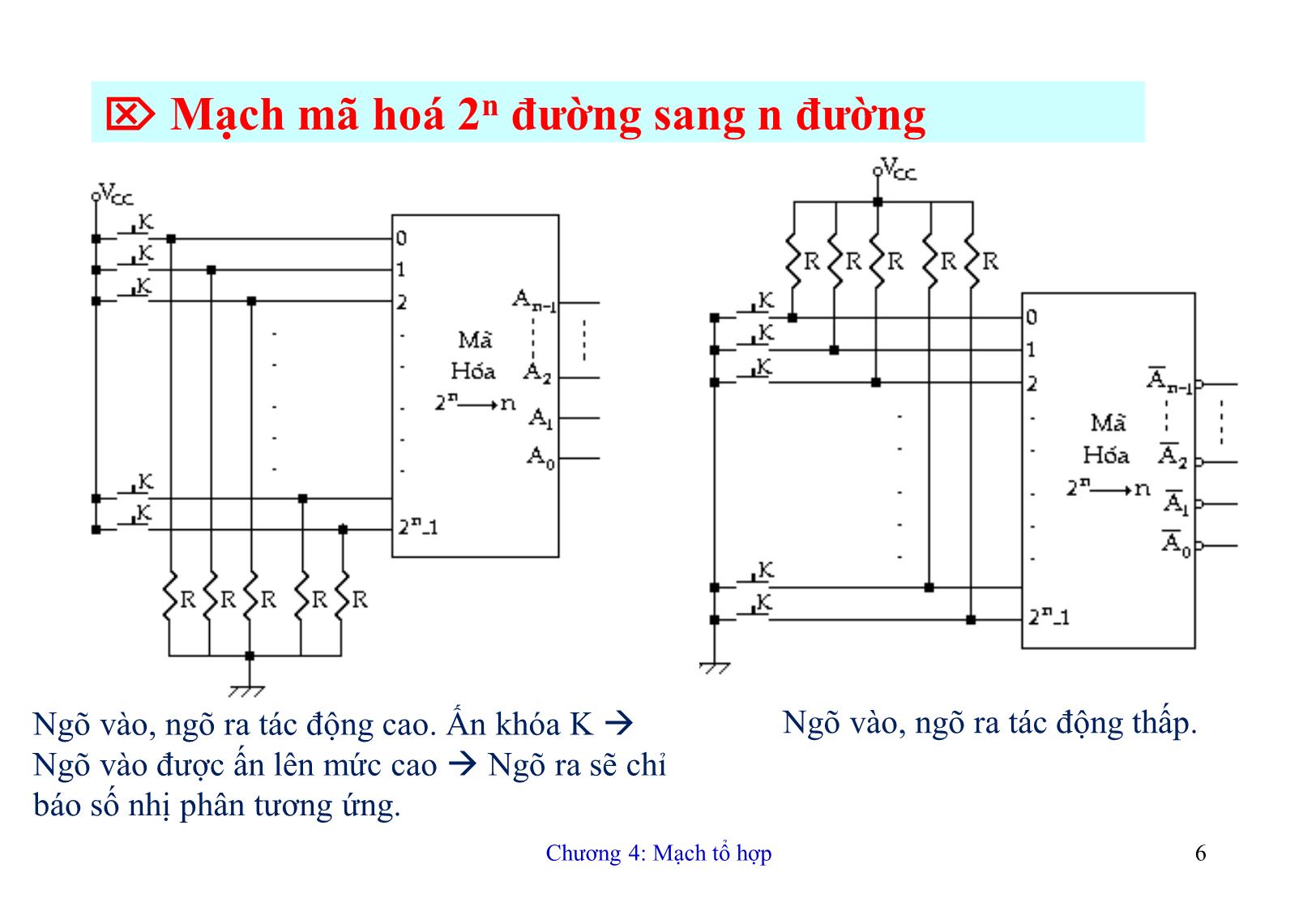

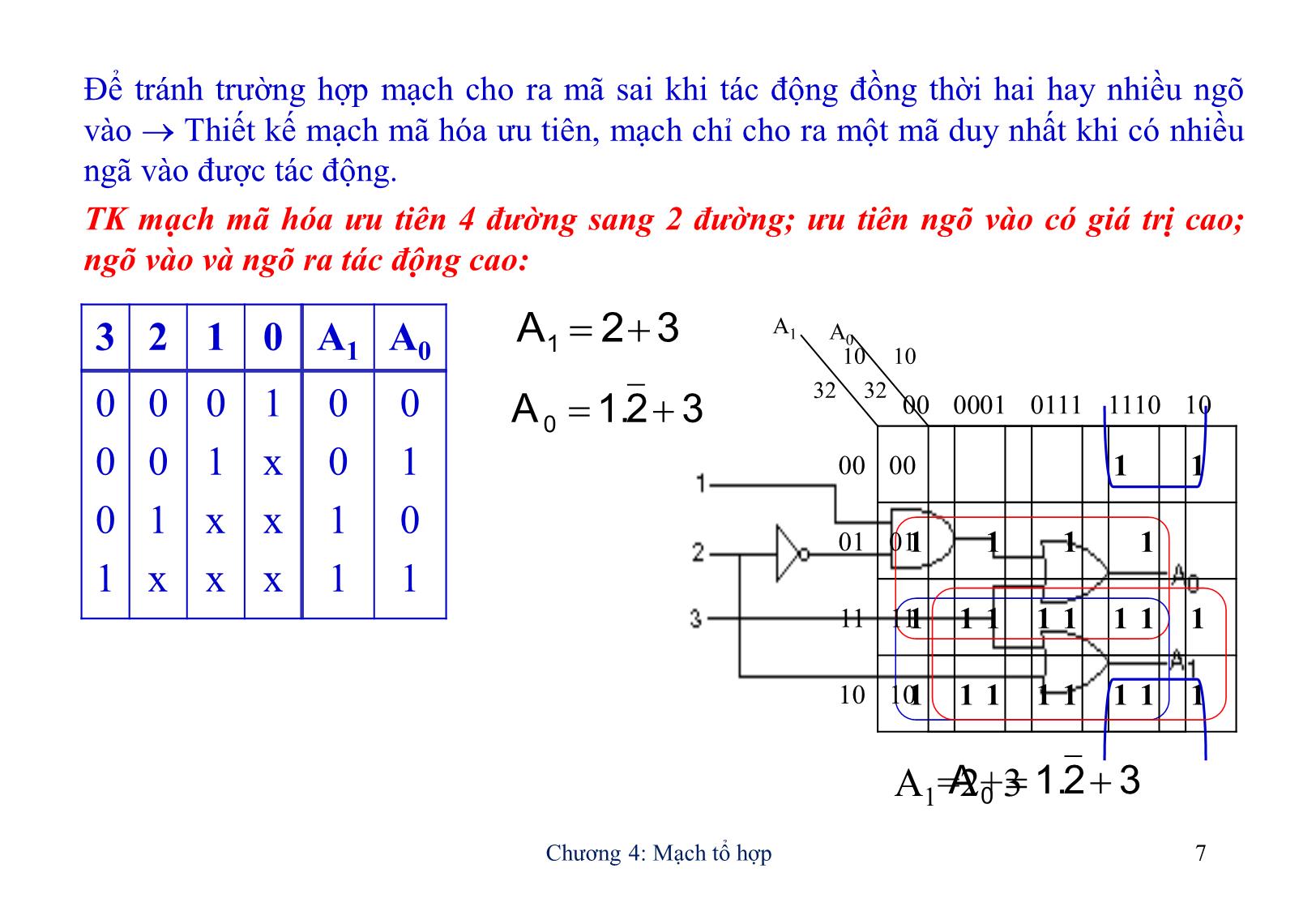

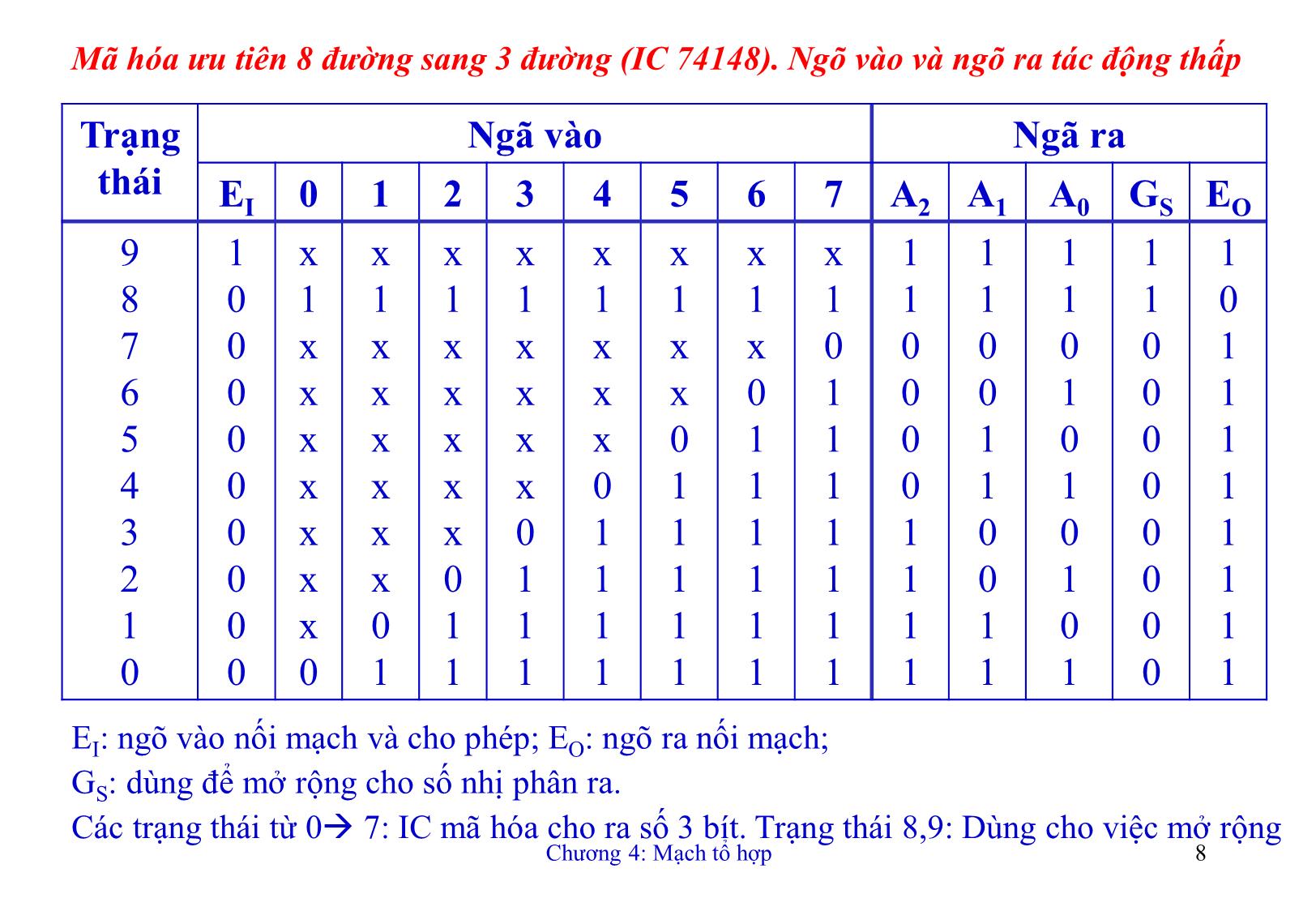

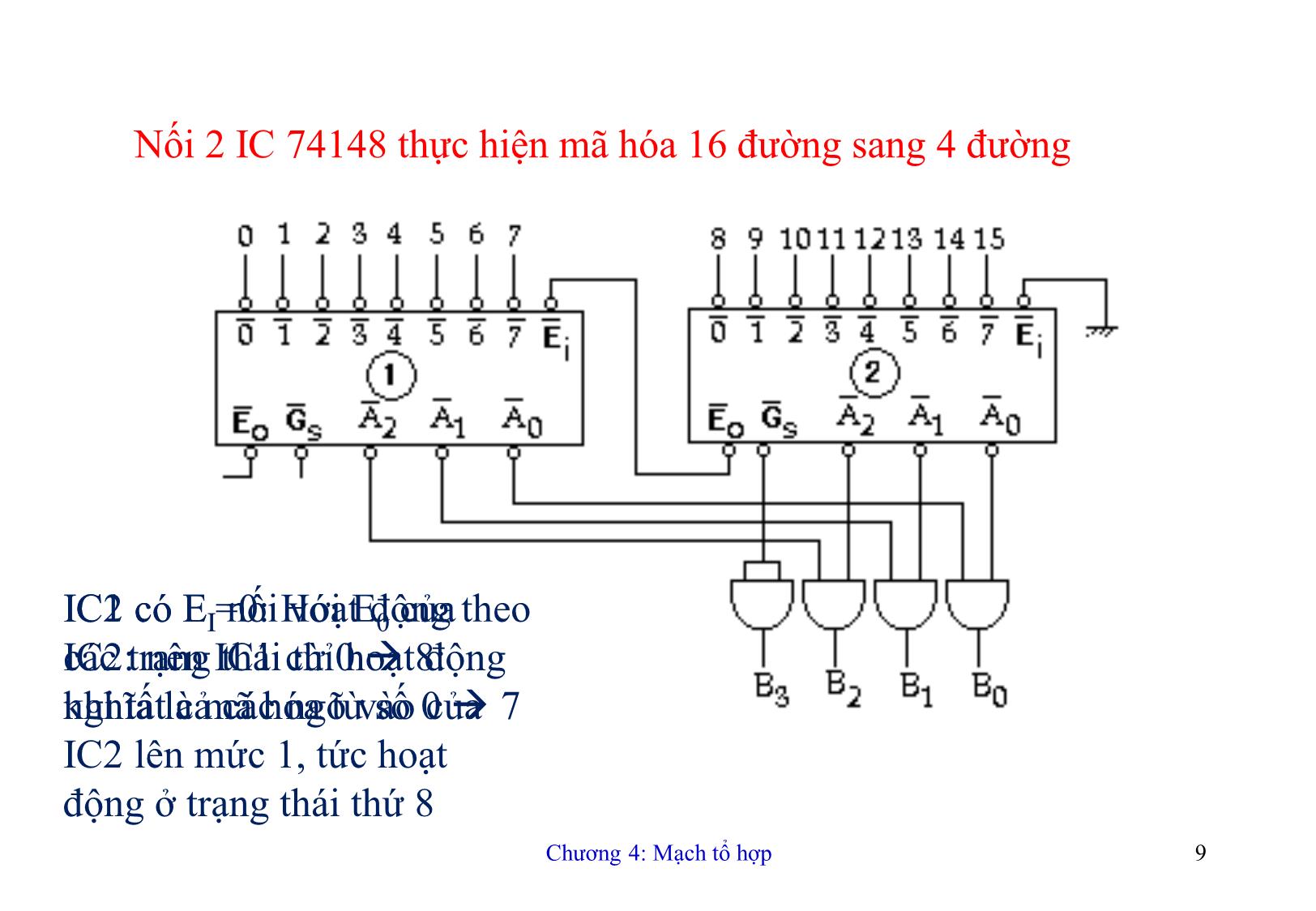

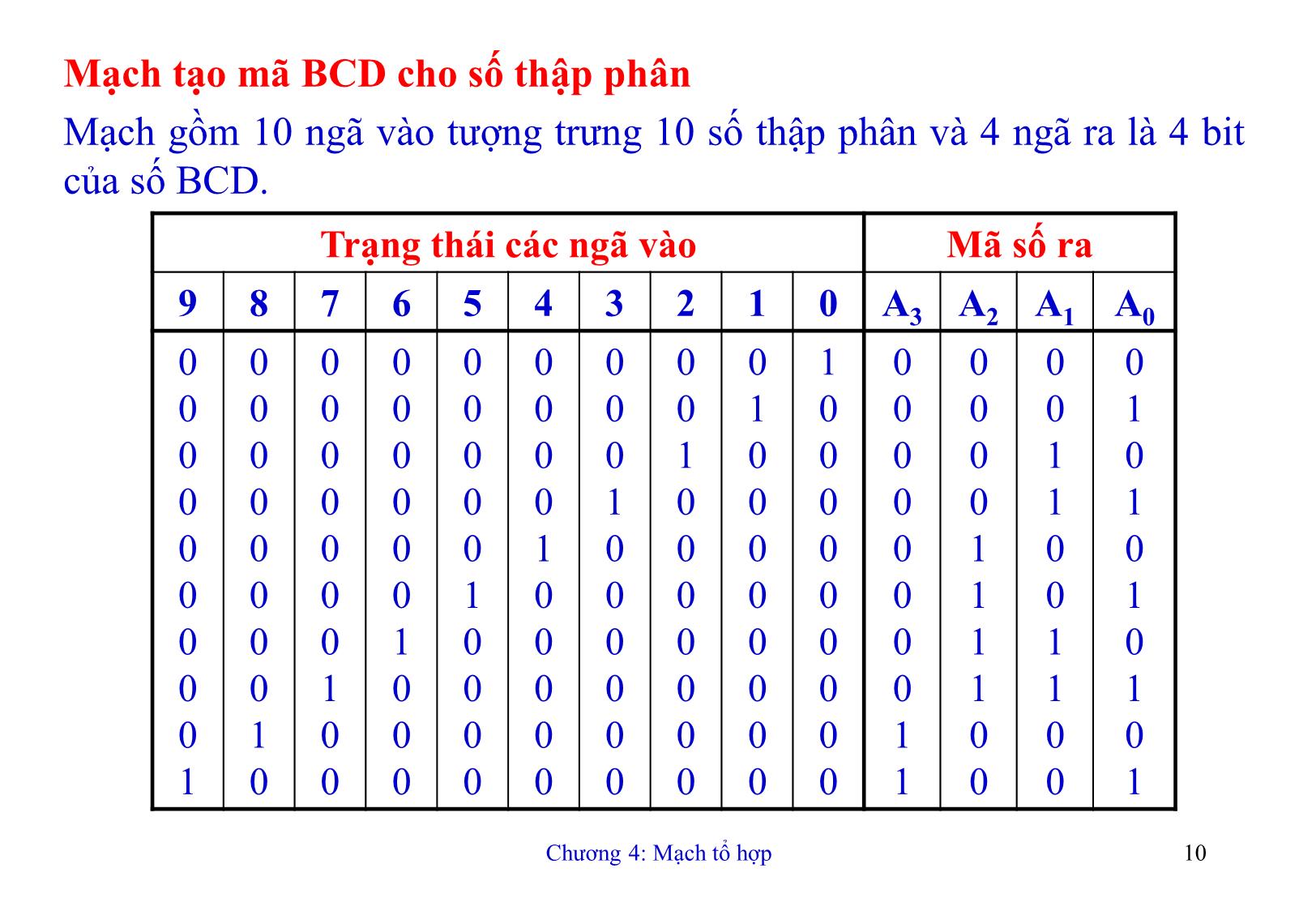

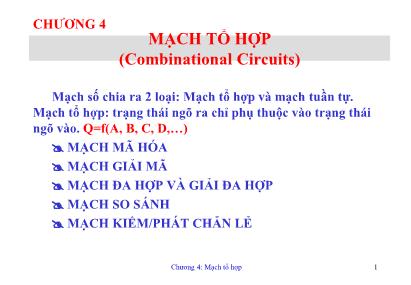

Chương 4: Mạch tổ hợp 1 MẠCH TỔ HỢP (Combinational Circuits) Mạch số chia ra 2 loại: Mạch tổ hợp và mạch tuần tự. Mạch tổ hợp: trạng thái ngõ ra chỉ phụ thuộc vào trạng thái ngõ vào. Q=f(A, B, C, D,) MẠCH MÃ HÓA MẠCH GIẢI MÃ MẠCH ĐA HỢP VÀ GIẢI ĐA HỢP MẠCH SO SÁNH MẠCH KIỂM/PHÁT CHẴN LẺ CHƢƠNG 4 Chương 4: Mạch tổ hợp 2 CÁC BƢỚC THIẾT KẾ MẠCH TỔ HỢP B1: Dựa vào yêu cầu của bài toán, xác định số biến ngõ vào và số biến ngõ ra (đặt tên biến). B2: Lập bảng sự thật cho mối quan hệ giữa ngõ vào và ngõ ra (hoạt động của mạch). B3: Rút gọn hàm bằng PP tối ƣu nhất. B4: Vẽ sơ đồ nguyên lý của mạch. Chương 4: Mạch tổ hợp 3 VD thiết kế mạch tổ hợp có 3 ngõ vào và 2 ngõ ra. - Ngõ ra thứ nhất = 1 nếu 3 ngõ vào có số bít 1 nhiều hơn số bit 0, ngƣợc lại thì =0 - Ngõ ra thứ hai = 1 nếu 3 giá trị nhị phân của 3 ngõ vào lới hơn 1 hoặc nhỏ hơn, ngƣợc lại thì =0 Giải B1: Mạch có 3 ngõ vào: A, B, C với A là MSB; và 2 ngõ ra: F0, F1 B2: Lập bảng sự thật A B C F0 F1 0 0 0 0 0 0 0 1 0 0 0 1 0 0 1 0 1 1 1 1 1 0 0 0 1 1 0 1 1 1 1 1 0 1 0 1 1 1 1 0 Chương 4: Mạch tổ hợp 4 A B C F0 F1 0 0 0 0 0 0 0 1 0 0 0 1 0 0 1 0 1 1 1 1 1 0 0 0 1 1 0 1 1 1 1 1 0 1 0 1 1 1 1 0 Lập bảng Kar BC A 00 01 11 10 0 1 1 1 1 1 F0 BC A 00 01 11 10 0 1 1 1 1 1 F1 BCABACF 0 BABABAF 1 A B C A.B A.C B.C F0 F1 Chương 4: Mạch tổ hợp 5 MỨC TÁC ĐỘNG - Khi không vòng tròn nhỏ ở đƣờng vào hay đƣờng ra trên ký hiệu mạch logic Tác động mức cao (active high). - Khi có vòng tròn nhỏ ở đƣờng vào hay đƣờng ra trên ký hiệu mạch logic Tác động mức thấp (active low). MẠCH MÃ HÓA (ENCODER) - Mã hóa là gán 1 ký hiệu cho một đối tƣợng nhằm một mục đích. - Mạch mã hóa là khi có một ngõ vào đƣợc tác động ngõ ra sẽ chỉ báo số nhị phân tƣơng ứng. Có nghĩa là mạch mã hóa có một số ngõ vào nhƣng vào một thời điểm chỉ có một ngõ vào ở trạng thái tích cực. - Nhƣ vậy ta dùng số nhị phân n bít để mã cho 2n ngõ vào khác nhau. - Mã hóa ƣu tiên: Trƣờng hợp có nhiều ngõ vào ở trạng thái tích cực thì ngõ ra sẽ tƣơng ứng với ngõ vào có trọng số cao nhất Chương 4: Mạch tổ hợp 6 Mạch mã hoá 2n đƣờng sang n đƣờng Ngõ vào, ngõ ra tác động cao. Ấn khóa K Ngõ vào được ấn lên mức cao Ngõ ra sẽ chỉ báo số nhị phân tương ứng. Ngõ vào, ngõ ra tác động thấp. Chương 4: Mạch tổ hợp 7 Để tránh trường hợp mạch cho ra mã sai khi tác động đồng thời hai hay nhiều ngõ vào Thiết kế mạch mã hóa ưu tiên, mạch chỉ cho ra một mã duy nhất khi có nhiều ngã vào được tác động. TK mạch mã hóa ưu tiên 4 đường sang 2 đường; ưu tiên ngõ vào có giá trị cao; ngõ vào và ngõ ra tác động cao: 3 2 1 0 A1 A0 0 0 0 1 0 0 1 x 0 1 x x 1 x x x 0 0 1 1 0 1 0 1 10 32 00 01 11 10 00 01 1 1 1 1 11 1 1 1 1 10 1 1 1 1 A1 A1=2+3 32A1 321.A 0 10 32 00 01 11 10 00 1 1 01 11 1 1 1 1 10 1 1 1 1 A0 321.A 0 Chương 4: Mạch tổ hợp 8 Mã hóa ưu tiên 8 đường sang 3 đường (IC 74148). Ngõ vào và ngõ ra tác động thấp Trạng thái Ngã vào Ngã ra EI 0 1 2 3 4 5 6 7 A2 A1 A0 GS EO 9 8 7 6 5 4 3 2 1 0 1 0 0 0 0 0 0 0 0 0 x 1 x x x x x x x 0 x 1 x x x x x x 0 1 x 1 x x x x x 0 1 1 x 1 x x x x 0 1 1 1 x 1 x x x 0 1 1 1 1 x 1 x x 0 1 1 1 1 1 x 1 x 0 1 1 1 1 1 1 x 1 0 1 1 1 1 1 1 1 1 1 0 0 0 0 1 1 1 1 1 1 0 0 1 1 0 0 1 1 1 1 0 1 0 1 0 1 0 1 1 1 0 0 0 0 0 0 0 0 1 0 1 1 1 1 1 1 1 1 EI: ngõ vào nối mạch và cho phép; EO: ngõ ra nối mạch; GS: dùng để mở rộng cho số nhị phân ra. Các trạng thái từ 0 7: IC mã hóa cho ra số 3 bít. Trạng thái 8,9: Dùng cho việc mở rộng Chương 4: Mạch tổ hợp 9 Nối 2 IC 74148 thực hiện mã hóa 16 đường sang 4 đường IC2 có EI=0: Hoạt động theo các trạng thái từ 0 8: nghĩa là mã hóa từ số 0 7 1 nối với E0 của IC2: nên IC1 chỉ hoạt động khi tất cả các ngõ vào của IC2 lên mức 1, tức hoạt động ở trạng thái thứ 8 Chương 4: Mạch tổ hợp 10 Mạch tạo mã BCD cho số thập phân Mạch gồm 10 ngã vào tượng trưng 10 số thập phân và 4 ngã ra là 4 bit của số BCD. Trạng thái các ngã vào Mã số ra 9 8 7 6 5 4 3 2 1 0 A3 A2 A1 A0 0 0 0 0 0 0 0 0 0 1 0 0 0 0 0 0 0 0 1 0 0 0 0 0 0 0 0 1 0 0 0 0 0 0 0 0 1 0 0 0 0 0 0 0 0 1 0 0 0 0 0 0 0 0 1 0 0 0 0 0 0 0 0 1 0 0 0 0 0 0 0 0 1 0 0 0 0 0 0 0 0 1 0 0 0 0 0 0 0 0 1 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 1 1 0 0 0 0 1 1 1 1 0 0 0 0 1 1 0 0 1 1 0 0 0 1 0 1 0 1 0 1 0 1 Chương 4: Mạch tổ hợp 11 A0 = 1 + 3 + 5 + 7 + 9 A1 = 2 + 3 + 6 + 7 A2 = 4 + 5 + 6 + 7 A3 = 8 + 9 Chương 4: Mạch tổ hợp 12 Mạch tạo mã BCD ƣu tiên cho số lớn Trạng thái các ngã vào Mã số ra 9 8 7 6 5 4 3 2 1 0 A3 A2 A1 A0 0 0 0 0 0 0 0 0 0 1 0 0 0 0 0 0 0 0 1 x 0 0 0 0 0 0 0 1 x x 0 0 0 0 0 0 1 x x x 0 0 0 0 0 1 x x x x 0 0 0 0 1 x x x x x 0 0 0 1 x x x x x x 0 0 1 x x x x x x x 0 1 x x x x x x x x 1 x x x x x x x x x 0 0 0 0 0 0 0 0 1 1 0 0 0 0 1 1 1 1 0 0 0 0 1 1 0 0 1 1 0 0 0 1 0 1 0 1 0 1 0 1 Chương 4: Mạch tổ hợp 13 Chương 4: Mạch tổ hợp 14 Mạch chuyển mã nhị phân (A: MSB) sang Gray A B C D X Y Z T 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 0 0 0 0 1 1 1 1 1 1 1 1 0 0 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1 0 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 0 DCDCDCT CBCBCBZ BABABAY AX Chương 4: Mạch tổ hợp 15 Lập Bảng Karnaugh: Mạch chuyển mã nhị phân sang Gray AB 00 01 11 10 00 01 11 1 1 1 1 10 1 1 1 1 X CD AB 00 01 11 10 00 01 1 1 1 1 11 10 1 1 1 1 Y CD AB 00 01 11 10 00 1 1 01 1 1 11 1 1 10 1 1 Z CD AB 00 01 11 10 00 1 1 01 1 1 11 1 1 10 1 1 T CD DCDCDCT CBCBCBZ BABABAY AX Chương 4: Mạch tổ hợp 16 Mạch chuyển mã Gray (X: MSB) sang Nhị phân A B C D X Y Z T 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 0 0 0 0 1 1 1 1 1 1 1 1 0 0 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1 0 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 0 TZYX )TZY).((XT)).(ZYX(D ZYX)ZYX(Z)(YXC YXYAYXB XA YX ZYX TZYX Chương 4: Mạch tổ hợp 17 Lập Bảng Karnaugh: Mạch chuyển mã Gray sang Nhị phân XY 00 01 11 10 00 01 11 1 1 1 1 10 1 1 1 1 A ZT XY 00 01 11 10 00 01 1 1 1 1 11 10 1 1 1 1 B ZT XY 00 01 11 10 00 1 1 01 1 1 11 1 1 10 1 1 C ZT XY 00 01 11 10 00 1 1 01 1 1 11 1 1 10 1 1 D ZT TZYX )TZY).((XT)).(ZYX(D ZYX)ZYX(Z)(YXC YXYXYXB XA Chương 4: Mạch tổ hợp 18 MẠCH GIẢI MÃ (DECODER) Ngƣợc lại của mã hóa. Giải mã n đƣờng sang 2n đƣờng Mạch giải mã 2 đƣờng sang 4 đƣờng, ngõ vào cho phép G Vào Ra G A1 A0 Y0 Y1 Y2 Y3 0 x x 0 0 0 0 1 1 1 1 0 0 1 1 0 1 0 1 1 0 0 0 0 1 0 0 0 0 1 0 0 0 0 1 013012 011010 A.A.GY A.A.GY A.A.GY A.A.GY Chương 4: Mạch tổ hợp 19 Mạch giải mã 3 đƣờng sang 8 đƣờng (Dùng 2 mạch giải mã 2 4 có ngõ vào cho phép) Vào Ra A2 A1 A0 Y0 Y1 Y2 Y3 Y4 Y5 Y6 Y7 0 0 0 0 0 0 1 1 0 1 0 1 1 0 0 0 0 1 0 0 0 0 1 0 0 0 0 1 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 1 1 1 1 0 0 1 1 0 1 0 1 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 1 0 0 0 0 1 0 0 0 0 1 0 0 0 0 1 Chương 4: Mạch tổ hợp 20 Vào Ra Cho phép Dữ liệu G1 G2 C B A Y0 Y1 Y2 Y3 Y4 Y5 Y6 Y7 x L H H H H H H H H H x L L L L L L L L x x L L L L H H H H x x L L H H L L H H x x L H L H L H L H H H L H H H H H H H H H H L H H H H H H H H H H L H H H H H H H H H H L H H H H H H H H H H L H H H H H H H H H H L H H H H H H H H H H L H H H H H H H H H H L G2 = G2A + G2B; H = 1; L = 0, x: bất chấp Bảng sự thật IC74138 (IC giải mã 3 8 ngõ vào tác động cao, ngõ ra tác động thấp) Chương 4: Mạch tổ hợp 21 Mở rộng lên mạch giải mã 4 đƣờng sang 16 đƣờng Chương 4: Mạch tổ hợp 22 Giải mã BCD sang 7 đoạn Đèn 7 đoạn: LED – Light Emitting Diode Phát sáng khi có dòng điện chạy qua nó Catod chung – dùng cho giải mã có ngõ ra tác động cao Anod chung – dùng cho giải mã có ngõ ra tác động thấp Chương 4: Mạch tổ hợp 23 Số TP Ngã vào Ngã ra D C B A a b c d e f g 0 1 2 3 4 5 6 7 8 9 0 0 0 0 0 0 0 0 1 1 0 0 0 0 1 1 1 1 0 0 0 0 1 1 0 0 1 1 0 0 0 1 0 1 0 1 0 1 0 1 0 1 0 0 1 0 0 0 0 0 0 0 0 0 0 1 1 0 0 0 0 0 1 0 0 0 0 0 0 0 0 1 0 0 1 0 0 1 0 0 0 1 0 1 1 1 0 1 0 1 0 1 1 1 0 0 0 1 0 0 1 1 0 0 0 0 0 1 0 0 Bảng sự thật mạch giải mã 7 đoạn, ngã ra tác động thấp CBADCBg ADCBABCf BCAe CBABACADCBd ABDCc ACBABCb )ACAC(DBa Chương 4: Mạch tổ hợp 24 Vào Ra Số/ Hàm LT RBI D C B A BI (1) RBO a b c d e f g 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 (2) (3) (4) 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 x 1 0 1 x x x x x x x x x x x x x x x x 0 x 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 x 0 x 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1 x 0 x 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 x 0 x 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 x 0 x 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 0 0 1 0 1 0 0 1 0 1 0 0 0 1 1 1 0 1 1 1 1 0 0 0 0 0 0 1 1 0 0 0 1 1 0 1 1 1 1 1 0 0 0 1 0 0 0 0 0 0 0 1 0 1 1 1 1 1 1 0 0 1 0 0 1 0 0 1 0 1 0 0 1 0 0 1 1 1 0 0 1 0 1 1 1 0 1 0 1 0 1 1 1 0 1 1 1 0 0 1 1 1 0 0 0 1 0 0 1 1 0 0 0 1 1 1 0 1 1 0 0 0 0 0 1 0 0 0 0 0 0 0 1 1 1 0 IC g iả i m ã B C D s a n g 7 đ o ạ n – I C 7 4 4 7 Chương 4: Mạch tổ hợp 25 A B Y 0 0 1 1 0 1 0 1 D0 D1 D2 D3 Mạch đa hợp 4 1 Mạch hiển thị kết quả 3 chữ số Chương 4: Mạch tổ hợp 26 A B C Y 0 0 0 0 1 1 1 1 0 0 1 1 0 0 1 1 0 1 0 1 0 1 0 1 D0 D1 D2 D3 D4 D5 D6 D7 Mạch đa hợp 8 1 7654 3210 D.C.B.AD.C.B.AD.C.B.AD.C.B.A D.C.B.AD.C.B.AD.C.B.AD.C.B.AY Ứng dụng mạch đa hợp Chương 4: Mạch tổ hợp 27 Mạch giải đa hợp thực chất là mạch giải mã, ngã vào cho phép trở thành ngã vào dữ liệu và ngã vào tổ hợp số nhị phân là ngã vào địa chỉ. Dùng IC 74138 làm mạch giải đa hợp 1 8 Chương 4: Mạch tổ hợp 28 MẠCH SO SÁNH Mạch so sánh hai số 1 bit G a b S (a>b) I (a<b) E (a=b) 0 x x 0 0 0 1 1 1 1 0 0 1 1 0 1 0 1 0 0 1 0 0 1 0 0 1 0 0 1 Mạch so sánh hai số 3 bit Chương 4: Mạch tổ hợp 29 Trạng thái Ngã vào so sánh Ngã vào nối mạch Ngã ra A3,B3 A2,B2 A1,B1 A0,B0 A’>B’ A’B A<B A=B 1 2 3 4 5 6 7 8 9 10 11 A3>B3 A3<B3 A3=B3 A3=B3 A3=B3 A3=B3 A3=B3 A3=B3 A3=B3 A3=B3 A3=B3 x x A2>B2 A2<B2 A2=B2 A2=B2 A2=B2 A2=B2 A2=B2 A2=B2 A2=B2 x x x x A1>B1 A1<B1 A1=B1 A1=B1 A1=B1 A1=B1 A1=B1 x x x x x x A0>B0 A0<B0 A0=B0 A0=B0 A0=B0 x x x x x x x x 0 1 0 x x x x x x x x 0 0 1 x x x x x x x x 1 0 0 1 0 1 0 1 0 1 0 0 1 0 0 1 0 1 0 1 0 1 0 0 1 0 0 0 0 0 0 0 0 1 0 0 Bảng sự thật IC 7485 Chương 4: Mạch tổ hợp 30 Mạch so sánh hai số nhị phân 8 bit MẠCH KIỂM PHÁT CHẴN LẺ 1 0 1 1 0 0 1 1 1 1 0 0 1 0 1 0 Bit chẵn lẽ thêm vào (KT lẻ) Bit chẵn lẽ thêm vào (KT chẵn) Chương 4: Mạch tổ hợp 31 Mạch phát chẵn lẻ Xét trường hợp mạch 4 bit dữ liệu. Mạch có 4 ngõ vào dữ liệu A, B, C, D và 1 ngã vào chọn chẵn lẻ S. - Gđ1: Thiết kế mạch ghi nhận số bit 1 là chẵn hay lẻ )DC()BA(Y - Gđ2: Thiết kế mạch tạo bit chẵn lẻ P theo S S Số bit 1 của ABCD Y P 0 0 1 1 Lẻ Chẵn Lẻ Chẵn 1 0 1 0 1 0 0 1 YSP Chương 4: Mạch tổ hợp 32 Mạch kiểm chẵn lẻ Từ quan hệ ngõ ra P với số lượng bit 1 ở 5 ngã vào ABCDS, ta có thể dùng mạch phát làm mạch kiểm chẵn lẻ. Số bit 1 của ABCDS P Lẻ Chẵn 1 0 Bảng sự thật của IC 74180 Ngõ vào Ngõ ra số 1 từ A-H Chẵn Lẻ Chẳn Lẻ Chẳn Lẻ Chẳn Lẻ x x 1 1 0 0 1 0 0 0 1 1 1 0 1 0 0 1 0 1 0 1 1 0 0 1

File đính kèm:

bai_giang_ky_thuat_so_chuong_4_mach_to_hop.pdf

bai_giang_ky_thuat_so_chuong_4_mach_to_hop.pdf