Bài giảng Điện tử số - Chương 7: Bộ nhớ bán dẫn - Nguyễn Trung Hiếu

Khái niệm chung

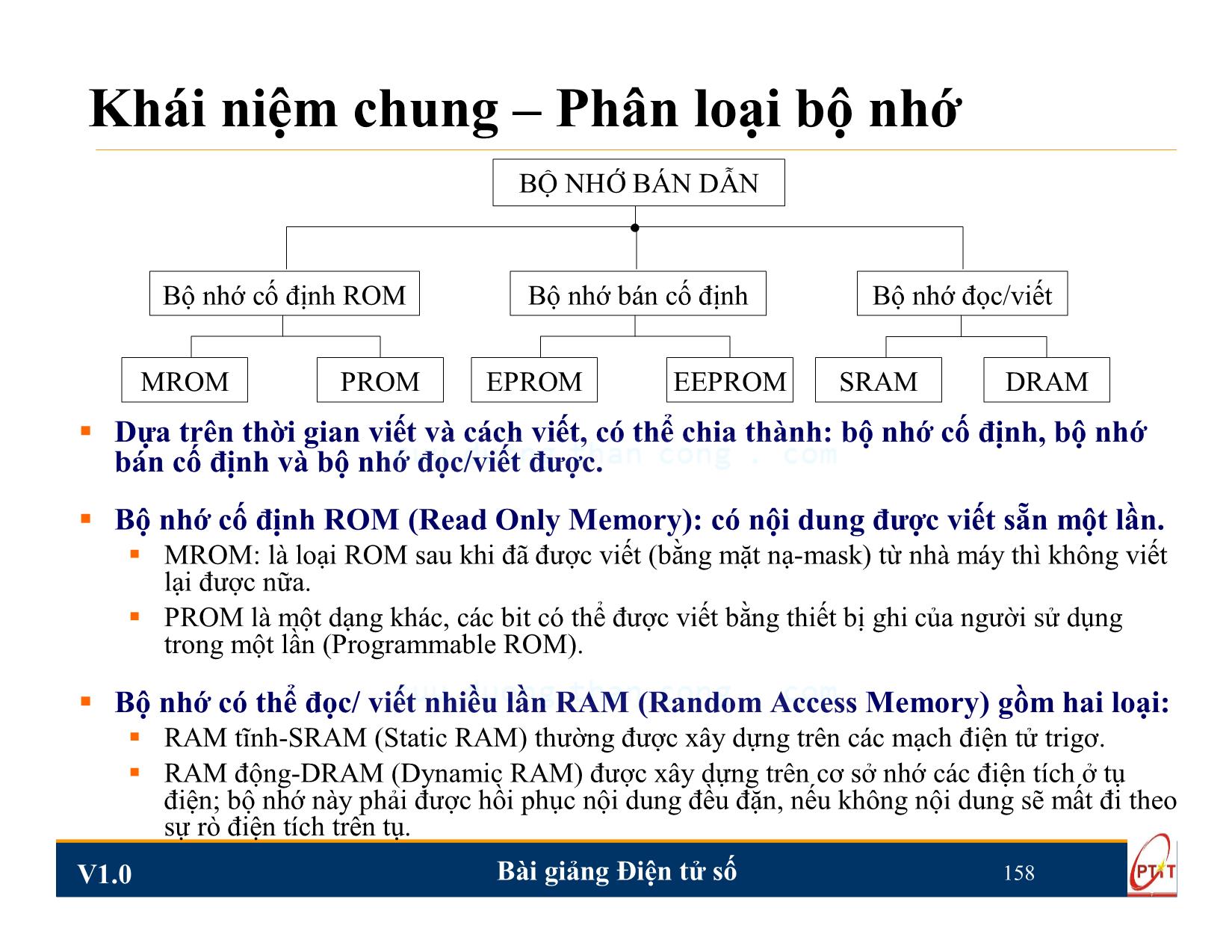

Khái niệm:

Bộ nhớ là một thiết bị có khả năng lưu trữ thông tin (nhị phân). Muốn sử dụng bộ nhớ,

trước tiên ta phải ghi dữ liệu và các thông tin cần thiết vào nó, sau đó lúc cần thiết phải lấy

dữ liệu đã ghi trước đó để sử dụng. Thủ tục ghi vào và đọc ra phải được kiểm soát chặt chẽ,

tránh nhầm lẫn nhờ định vị chính xác từng vị trí ô nhớ và nội dung của nó theo một mã địa

chỉ duy nhất.

Những đặc trưng chính của bộ nhớ

Dung lượng của bộ nhớ.

Dung lượng bộ nhớ là số bit thông tin tối đa có thể lưu giữ trong nó. Dung lượng cũng có thể biểu

thị bằng số từ nhớ n bit. Từ nhớ n bit là số bit (n) thông tin mà ta có thể đọc hoặc ghi đồng thời vào

bộ nhớ. Ví dụ: Một bộ nhớ có dung lượng là 256 bit; nếu nó có cấu trúc để có thể truy cập cùng một

lúcc 8 bit thông tin, thì ta cũng có thể biểu thị dung lượng bộ nhớ là 32 từ nhớ x 8 bit = 32 byte.

Cách truy cập thông tin: Có 2 cách là trực tiếp và gián tiếp

Truy cập trực tiếp, hay còn gọi là truy cập ngẫu nhiên (random access). Ở cách này, không gian bộ

nhớ được chia thành nhiều ô nhớ. Mỗi ô nhớ chứa được 1 từ nhớ n bit và có một địa chỉ xác định,

mã hoá bằng số nhị phân k bit. Như vậy, người sử dụng có thể truy cập trực tiếp thông tin ở ô nhớ

có địa chỉ nào đó trong bộ nhớ. Mỗi bộ nhớ có k bit địa chỉ sẽ có 2k ô nhớ và có thể ghi được 2k từ

nhớ n bit.

Truy cập tuần tự (serial access) hay còn gọi là kiểu truy cập tuần tự. Các đĩa từ, băng từ, trống từ,

thanh ghi dịch có kiểu truy cập này. Các bit thông tin được đưa vào và lấy ra một cách tuần tự.

Tốc độ truy cập thông tin.

Đây là thông số rất quan trọng của bộ nhớ. Nó được đặc trưng bởi thời gian cần thiết để truy cập

thông tin.

Trang 1

Trang 2

Trang 3

Trang 4

Trang 5

Trang 6

Trang 7

Trang 8

Trang 9

Trang 10

Tải về để xem bản đầy đủ

Tóm tắt nội dung tài liệu: Bài giảng Điện tử số - Chương 7: Bộ nhớ bán dẫn - Nguyễn Trung Hiếu

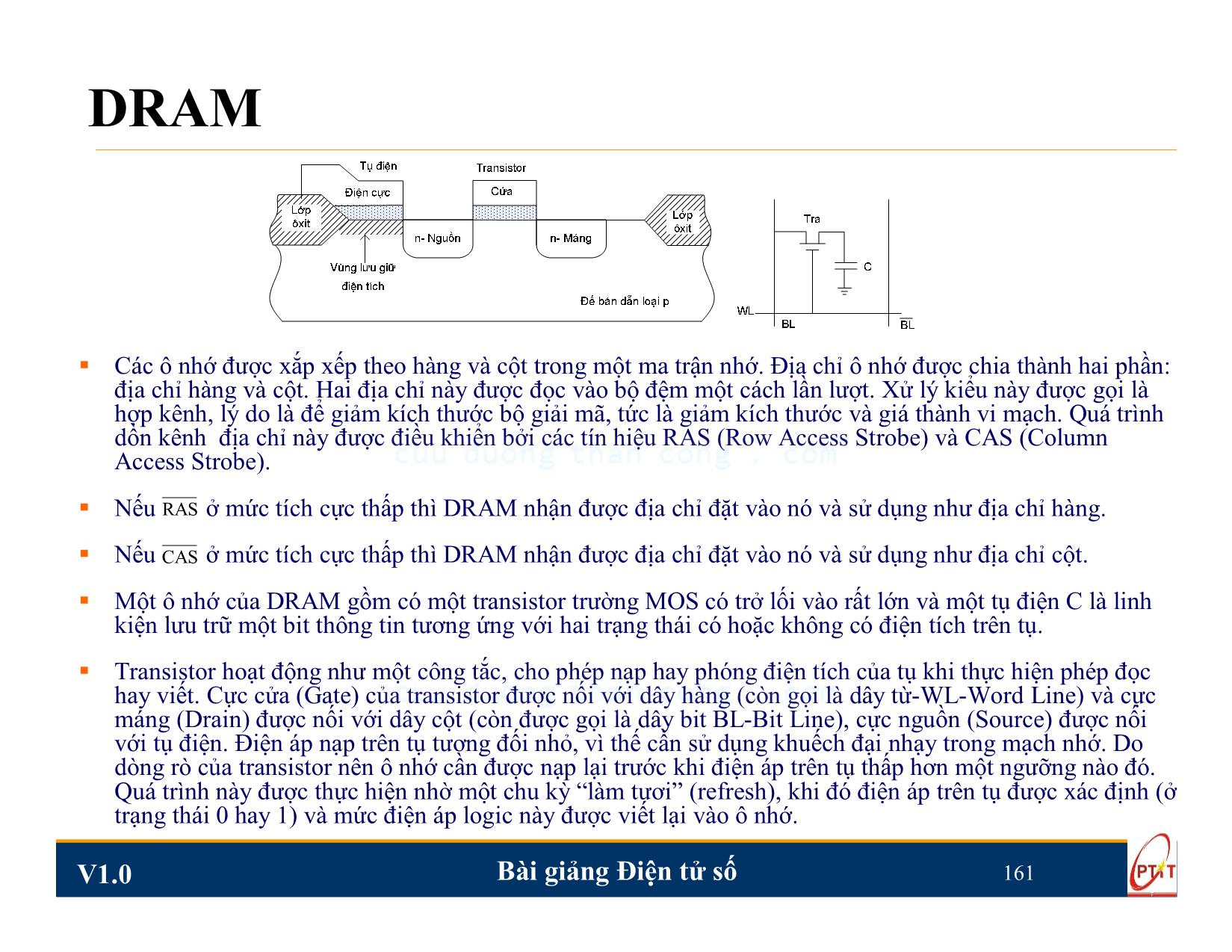

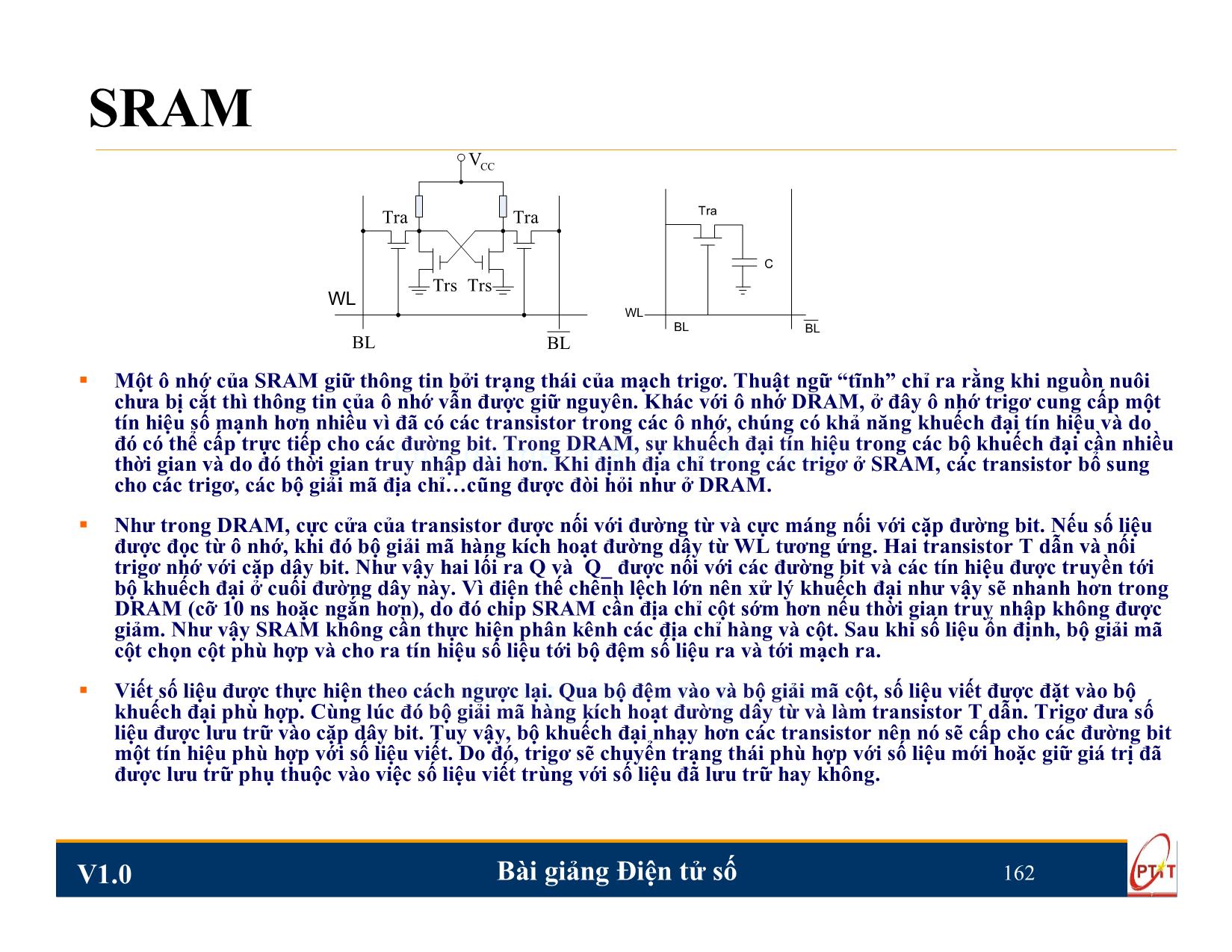

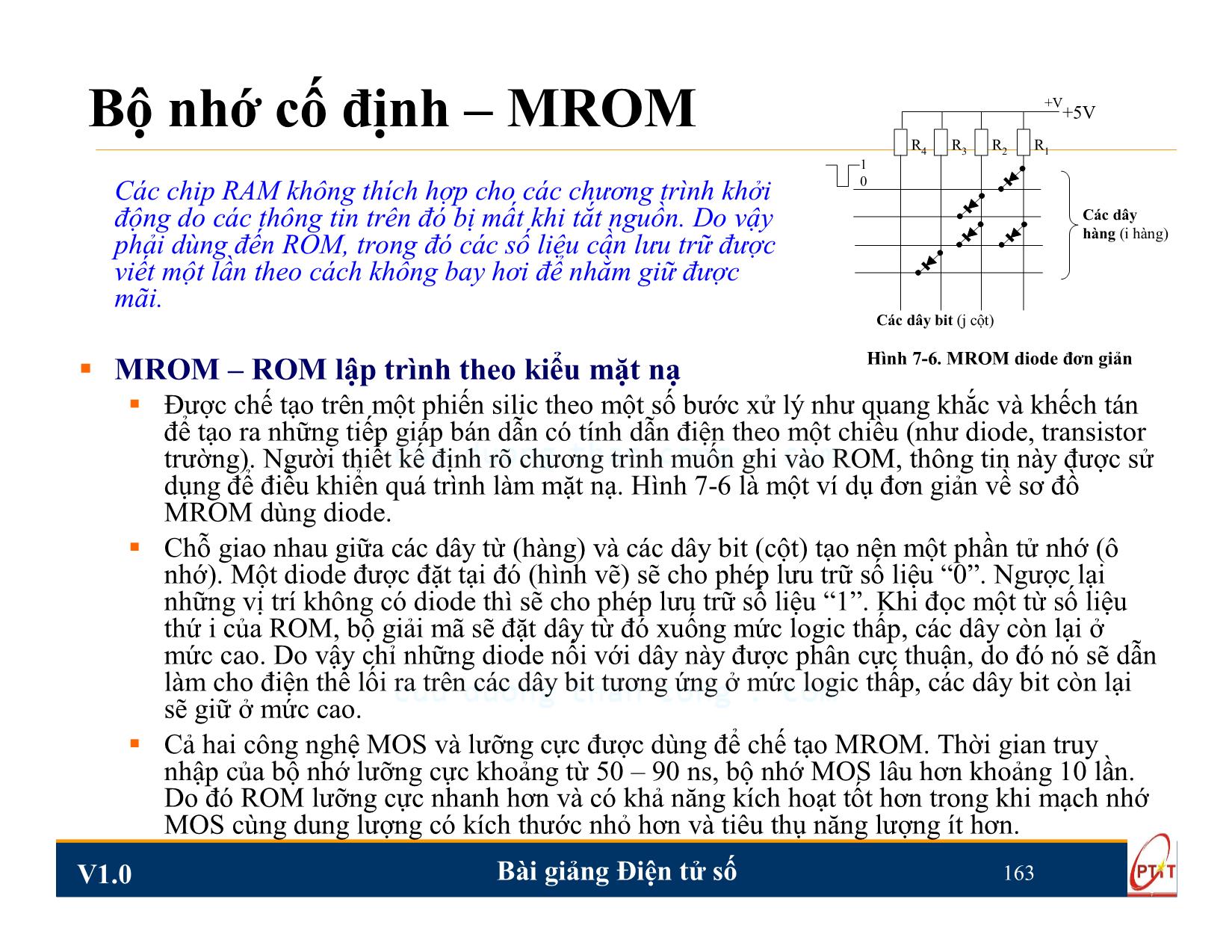

i với các đường bit và các tín hiệu được truyền tới bộ khuếch đại ở cuối đường dây này. Vì điện thế chênh lệch lớn nên xử lý khuếch đại như vậy sẽ nhanh hơn trong DRAM (cỡ 10 ns hoặc ngắn hơn), do đó chip SRAM cần địa chỉ cột sớm hơn nếu thời gian truy nhập không được giảm. Như vậy SRAM không cần thực hiện phân kênh các địa chỉ hàng và cột. Sau khi số liệu ổn định, bộ giải mã cột chọn cột phù hợp và cho ra tín hiệu số liệu tới bộ đệm số liệu ra và tới mạch ra. Viết số liệu được thực hiện theo cách ngược lại. Qua bộ đệm vào và bộ giải mã cột, số liệu viết được đặt vào bộ khuếch đại phù hợp. Cùng lúc đó bộ giải mã hàng kích hoạt đường dây từ và làm transistor T dẫn. Trigơ đưa số liệu được lưu trữ vào cặp dây bit. Tuy vậy, bộ khuếch đại nhạy hơn các transistor nên nó sẽ cấp cho các đường bit một tín hiệu phù hợp với số liệu viết. Do đó, trigơ sẽ chuyển trạng thái phù hợp với số liệu mới hoặc giữ giá trị đã được lưu trữ phụ thuộc vào việc số liệu viết trùng với số liệu đã lưu trữ hay không. CCV Tra Tra TrsTrs WL BLBL Tra WL BL BL C Bài giảng Điện tử sốV1.0 163 Bộ nhớ cố định – MROM MROM – ROM lập trình theo kiểu mặt nạ Được chế tạo trên một phiến silic theo một số bước xử lý như quang khắc và khếch tán để tạo ra những tiếp giáp bán dẫn có tính dẫn điện theo một chiều (như diode, transistor trường). Người thiết kế định rõ chương trình muốn ghi vào ROM, thông tin này được sử dụng để điều khiển quá trình làm mặt nạ. Hình 7-6 là một ví dụ đơn giản về sơ đồ MROM dùng diode. Chỗ giao nhau giữa các dây từ (hàng) và các dây bit (cột) tạo nên một phần tử nhớ (ô nhớ). Một diode được đặt tại đó (hình vẽ) sẽ cho phép lưu trữ số liệu “0”. Ngược lại những vị trí không có diode thì sẽ cho phép lưu trữ số liệu “1”. Khi đọc một từ số liệu thứ i của ROM, bộ giải mã sẽ đặt dây từ đó xuống mức logic thấp, các dây còn lại ở mức cao. Do vậy chỉ những diode nối với dây này được phân cực thuận, do đó nó sẽ dẫn làm cho điện thế lối ra trên các dây bit tương ứng ở mức logic thấp, các dây bit còn lại sẽ giữ ở mức cao. Cả hai công nghệ MOS và lưỡng cực được dùng để chế tạo MROM. Thời gian truy nhập của bộ nhớ lưỡng cực khoảng từ 50 – 90 ns, bộ nhớ MOS lâu hơn khoảng 10 lần. Do đó ROM lưỡng cực nhanh hơn và có khả năng kích hoạt tốt hơn trong khi mạch nhớ MOS cùng dung lượng có kích thước nhỏ hơn và tiêu thụ năng lượng ít hơn. R4 R3 R2 R1 Các dây bit (j cột) +5V 1 0 +V Các dây hàng (i hàng) Hình 7-6. MROM diode đơn giản Các chip RAM không thích hợp cho các chương trình khởi động do các thông tin trên đó bị mất khi tắt nguồn. Do vậy phải dùng đến ROM, trong đó các số liệu cần lưu trữ được viết một lần theo cách không bay hơi để nhằm giữ được mãi. Bài giảng Điện tử sốV1.0 164 Bộ nhớ cố định – PROM PROM cũng gồm có các diode như ở MROM nhưng chúng có mặt đầy đủ tạo các vị trí giao nhau giữa dây từ và dây bit. Mỗi diode được nối với một cầu chì. Bình thường khi chưa lập trình, các cầu chì còn nguyên vẹn, nội dung của PROM sẽ toàn là 0. Khi định vị đến một bit bằng cách đặt một xung điện ở lối ra tương ứng, cầu chì sẽ bị đứt và bit này sẽ bằng 1. Bằng cách đó ta có thể lập trình toàn bộ các bit trong PROM. Như vậy, việc lập trình đó có thể được thực hiện bởi người sử dụng chỉ một lần duy nhất, không thể sửa đổi được. Bài giảng Điện tử sốV1.0 165 Bộ nhớ bán cố định - EPROM (Erasable PROM) Số liệu vào có thể được viết vào bằng xung điện nhưng được lưu giữ theo kiểu không bay hơi. Đó là loại ROM có thể lập trình được và xóa được. Hình 7- 7 chỉ ra cấu trúc của một transistor dùng để làm một ô nhớ gọi là FAMOST (Floating gate avalanche injection MOS transistor). Trong ô nhớ dùng transistor này, cực cửa được nối với đường từ, cực máng được nối với đường bit và cực nguồn được nối với nguồn chuẩn được coi là nguồn cho mức logic 1. Khác với transistor MOS bình thường, transistor loại này còn có thêm một cửa gọi là cửa nổi (floating gate); đó là một vùng vật liệu được thêm vào vào giữa lớp cách điện cao như ở hình 7-7. Nếu cửa nổi không có điện tích thì nó không ảnh hưởng gì đến cực cửa điều khiển và transistor hoạt động như bình thường. Tức là khi dây từ được kích hoạt (cực cửa có điện thế dương) thì transtor dẫn, cực máng và nguồn được nối với nhau qua kênh dẫn và dây bit có mức logic 1. Nếu cửa nổi có các điện tử trong đó với điện tích âm thì chúng sẽ ngăn trường điều khiển của cửa cửa và dù dây từ được kích hoạt thì cũng không thể phát ra trường đủu mạnh với cực cửa điều khiển để làm thông transistor. Lúc này đường bit không được nối với nguồn chuẩn và ô nhớ coi như được giữ giá trị 0. 0v 1v DI GSv Hình 7-7. Cấu trúc của một EPROM Bài giảng Điện tử sốV1.0 166 Bộ nhớ bán cố định - EPROM (Erasable PROM) Việc nạp các điện tử vào vùng cửa nổi, tức là tạo ra các ô nhớ mang giá trị 0 được thực hiện bởi xung điện có độ dài cỡ 50 ms và độ lớn + 20 V đặt giữa cực cửa va cực máng. Lúc đó những điện tích mang năng lượng lớn sẽ đi qua lớp cách điện giữa đế và cửa nổi. Chúng tích tụ trong vùng cửa nổi và được giữ ở đây sau khi xung lập trình tắt. Đó là do cửa nổi được cách điện cao với xung quanh và các điện tử không còn đủ năng lượng sau khi lạnh đi, để có thể vượt ra ngoài lớp cách điện đó nữa. Chúng sẽ được giữ ở đây trong một thời gian rất dài (ít nhất là 10 năm). Để xoá các thông tin, tức là làm mất các điện tích điện tử trong vùng cửa nổi, phải chiếu ánh sáng tử ngoại UV vào chíp nhớ. Lúc này, những điện tử hấp thụ đượ năng lượng và sẽ nhảy lên các mức năng lượng cao và rời khỏi cửa nổi giống như cách mà chúng đã thâm nhập vào. Trong chip EPROM có một cửa sổ làm bằng thuỷ tinh thạch anh chỉ để cho ánh sáng tử ngoại đi qua khi cần xoá số liệu trong bộ nhớ. Bài giảng Điện tử sốV1.0 167 Bộ nhớ bán cố định - EEPROM (Electrically Erasable PROM) Cửa sổ thạch anh có giá thành khá đắt và không tiện lợi nên những năm gần đây xuất hiện các chip PROM có thể xoá số liệu bằng phương pháp điện. Cấu trúc của ô nhớ giống như hình 7-8. Việc nạp các điện tử cho cửa nổi được thực hiện như cách ở EPROM. Bằng một xung điện tương đối dài, các điện tích mang năng lượng cao được phát ra trong đế sẽ thấm qua lớp cửa ôxit và tích tụ trong cửa nổi. Để xoá EEPROM, một lớp kênh màng mỏng ôxit giữa vùng cửa nổi trải xuống dưới đế và cực máng giữ vai trò quan trọng. Các lớp cách điện không thể là lý tưởng được, các điện tích có thể thấm qua lớp phân cách với một xác suất thấp. Xác suất này tăng lên khi bề dày của lớp giảm đi và điện thế giữa hai điện cực ở hai mặt lớp cách điện tăng lên. Muốn phóng các điện tích trong vùng cửa nổi một điện thế (-20 V) được đặt vào cực cửa điều khiển và cực máng. Lúc này các điện tử âm trong cửa nổi được chảy về cực máng qua kênh màng mỏng ôxit và số liệu lưu giữ được xoá đi. Điều lưu ý là phải làm sao cho dòng điện tích này chảy không quá lâu vì nếu không vùng cửa nổi này lại trở nên tích điện dương làm cho hoạt động của transistor không được trạng thái bình thường (mức nhớ 1) Lớp ôxit n- Nguồn n- Máng Đế bán dẫn loại p Lớp ôxit Nguồn MángCửa - - - - - - Cửa nổi Cửa điều khiển - -- - Đường hầm ôxít Lớp ôxit Hình 7-8. Cấu trúc của một EEPROM Bài giảng Điện tử sốV1.0 168 Bộ nhớ bán cố định - Bộ nhớ FLASH Trong những năm gần đây, một loại bộ nhớ không bay hơi mới đã xuất hiện trên thị trường, thường được sử dụng thay thế cho các ổ đĩa mềm và cứng trong những máy tính. Đó là bộ nhớ flash. Cấu trúc của chúng cơ bản như EEPROM, chỉ có lớp kênh ôxit ở các ô nhớ mỏng hơn. Do vậy chỉ cần điện thế cỡ 12 V là có thể cho phép thực hiện 10 000 chu trình xoá và lập trình. Bộ nhớ flash có thể hoạt động gần mềm dẻo như DRAM và SRAM nhưng lại không bị mất số liệu khi bị cắt điện. Hình 7- 9 chỉ ra sơ đồ khối của nó. Phần chính là mạng nhớ bao gồm các ô nhớ FAMOST như được mô tả ở mục trên. Giống như SRAM, bộ nhớ flash không dồn phân kênh địa chỉ. Các bộ giải mã hàng và cột chọn một đường từ và một hoặc nhiều cặp đường bit. Số liệu đọc được đưa ra ngoài bộ đệm số liệu I/O hoặc được viết vào ô nhớ đã được định địa chỉ bởi bộ đệm này qua cổng I/O. Xử lý đọc được thực hiện với điện thế MOS thông thường là 5V. Để lập trình một ô nhớ, đơn vị điều khiển flash đặt một xung điện thế ngắn cỡ 10 s và 12 V gây nên một sự chọc thủng thác lũ vào transistor nhớ để nạp vào cửa nổi. Một chip nhớ flash 1 Mb có thể được lập trình trong khoảng 2 sec, nhưng khác với EEPROM việc xoá được thực hiện từng chip một. Thời gian xoá cho toàn bộ bộ nhớ flash khoảng 1 sec. Xử lý đọc, lập trình và xoá được điều khiển bởi các lệnh có độ dài 2 byte được bộ xử lý viết vào các thanh ghi lệnh của mạch điều khiển flash. Bài giảng Điện tử sốV1.0 169 Bộ nhớ bán cố định - Bộ nhớ FLASH Mục đích sử dụng chính của bộ nhớ flash là để thay thế cho các ổ đĩa mềm và ổ đĩa cứng dung lượng nhỏ. Do nó là mạch tích hợp nên có ưu điểm là kích thước nhỏ và tiêu thụ năng lượng thấp, không bị ảnh hưởng của va đập. Các đĩa cứng chất rắn dựa trên cơ sở các bộ nhớ flash có lợi thế về công suất tiêu thụ cũng như giá thành có dung lượng tới vài Mbyte. Các card nhớ loại này có ưu điểm là không gặp phải vấn đề mất thông tin như trường hợp RAM CMOS khi pin Ni-Cd bị hỏng. Thời gian lưu trữ thông tin trong bộ nhớ flash ít nhất là 10 năm, thông thường là 100 năm, với khoảng thời gian này thì các đĩa mềm và cứng đã bị hỏng rồi. Nhược điểm của bộ nhớ flash là chỉ có thể xoá theo kiểu lần lượt từng chip hoặc lần lượt từng trang. PPV WE CE OE Hình 7-9. Sơ đồ bộ nhớ FLASH Bài giảng Điện tử sốV1.0 170 Bộ nhớ bán cố định - Bộ nhớ CACHE Việc nạp các điện tử vào vùng cửa nổi, tức là tạo ra các ô nhớ mang giá trị 0 được thực hiện bởi xung điện có độ dài cỡ 50 ms và độ lớn + 20 V đặt giữa cực cửa va cực máng. Lúc đó những điện tích mang năng lượng lớn sẽ đi qua lớp cách điện giữa đế và cửa nổi. Chúng tích tụ trong vùng cửa nổi và được giữ ở đây sau khi xung lập trình tắt. Đó là do cửa nổi được cách điện cao với xung quanh và các điện tử không còn đủ năng lượng sau khi lạnh đi, để có thể vượt ra ngoài lớp cách điện đó nữa. Chúng sẽ được giữ ở đây trong một thời gian rất dài (ít nhất là 10 năm). Để xoá các thông tin, tức là làm mất các điện tích điện tử trong vùng cửa nổi, phải chiếu ánh sáng tử ngoại UV vào chíp nhớ. Lúc này, những điện tử hấp thụ đượ năng lượng và sẽ nhảy lên các mức năng lượng cao và rời khỏi cửa nổi giống như cách mà chúng đã thâm nhập vào. Trong chip EPROM có một cửa sổ làm bằng thuỷ tinh thạch anh chỉ để cho ánh sáng tử ngoại đi qua khi cần xoá số liệu trong bộ nhớ. Bài giảng Điện tử sốV1.0 171 Bộ nhớ bán cố định - EPROM (Erasable PROM) Với các máy tính có tốc độ nhanh (trên 33MHz), cần phải xen các trạng thái đợi khi truy xuất dữ liệu tới các DRAM rẻ tiền nhưng có thời gian thâm nhập chậm (60-120ns). Điều này làm giảm hiệu suất của máy. Có thể giải quyết bằng cách dùng các SRAM có thời gian thâm nhập ngắn hơn (20-25 ns, thậm chí 12 ns) nhưng giá thành lại rất đắt. Bộ nhớ Cache kết hợp được các lợi điểm nhanh của SRAM và rẻ của DRAM. Giữa CPU và bộ nhớ chính bằng DRAM, người ta xen vào một bộ nhớ SRAM nhanh có dung lượng nhỏ bằng 1/10 hoặc 1/100 lần bộ nhớ chính gọi là cache; dưới sự điều khiển của mạch điều khiển cache, bộ nhớ này sẽ lưu trữ tạm thời các số liệu thường được gọi và cung cấp nó cho CPU trong thời gian ngắn. Cache chứa các thông tin mới vừa được CPU sử dụng gần đây nhất. Khi CPU đọc số liệu nó sẽ đưa ra một địa chỉ tới bộ điều khiển cache. Sau đó một trong hai quá trình sau sẽ xảy ra: Cache hit: nếu địa chỉ đó đã có sẵn trong RAM cache. Cache miss: ngược lại, nếu địa chỉ đó không có sẵn trong RAM cache. Bài giảng Điện tử sốV1.0 172 Mở rộng dung lượng bộ nhớ Các vi mạch nhớ bán dẫn chỉ có dung lượng xác định. Muốn có bộ nhớ có dung lượng lớn hơn, ta tìm cách ghép nhiều vi mạch nhớ nhằm một trong ba mục đích sau: Tăng độ dài nhớ, nhưng không làm tăng số lượng từ nhớ. Tăng số lượng từ nhớ nhưng không làm tăng độ dài từ nhớ. Tăng cả số lượng và độ dài từ nhớ. Bài giảng Điện tử sốV1.0 173 Mở rộng độ dài từ Trên một chíp nhớ, có thể có được 1 đến một số hữu hạn lối ra, thường là 4 hoặc 8 bit. Muốn có độ dài từ lớn hơn, chẳng hạn từ 4 lên 8 hoặc 16 bit, ta tiến hành ghép nhiều chíp nhớ như chỉ ở hình 7-10 đối với RAM. Đối với ROM cách làm cũng tương tự, chỉ khác trong trường hợp này, có thể không có lối vào R/W. D0 Dn-1 RAM I BUS địa chỉ A0 An-1 RAM II BUS dữ liệu BUS dữ liệu Hình 7-10. Sơ đồ mở rộng độ dài từ. Bài giảng Điện tử sốV1.0 174 Mở rộng dung lượng (1) Muốn mở rộng dung lượng, ta cũng ghép nhiều chíp lại với nhau. Như đã biết, dung lượng có liên quan đến số lối vào địa chỉ (C = 2N x độ dài từ, với N là số lối vào địa chỉ). Cứ tăng 1 chíp thì cần có thêm một lối vào địa chỉ. Khác với trường hợp mở rộng độ dài từ, khi mở rộng dung lượng các lối vào/ra dữ liệu D và R/ được nối song song. Một phần dung lượng được trữ vào mỗi chíp. Sự phân chia này dựa trên cơ sở tổ hợp địa chỉ vào và lối vào điều khiển. Hình 7-11 là một sơ đồ ví dụ. A0 A11 A12 A13 Bộ giải mã vào 2 ra 4 Hình 7-11. Phương pháp mở rộng dung lượng. IC 1 A0 A11 2k IC 2 A0 A11 2k IC 3 A0 A11 2k IC 4 A0 A11 2k Bài giảng Điện tử sốV1.0 175 Mở rộng dung lượng (2) Để thực hiện phép mở rộng ta phải sử dụng một số lối vào địa chỉ dành riêng cho bộ giải mã (thường là các địa chỉ có trọng số cao). Ở sơ đồ trên ta chọn 2 địa chỉ A12 và A13 để giải mã. Do đó ta có thể nhận được 4 giá trị ra tương ứng. Các giá trị này tác động lên các lối vào CS để mở tuần tự các IC nhớ. Các IC nhớ này có thể làm ROM hoặc RAM hoặc cả hai là tùy chọn. Tuần tự mở các IC theo A12, A13 như chỉ ra ở bảng hoạt động sau. A0 A11 A12 A13 Bộ giải mã vào 2 ra 4 Hình 7-11. Phương pháp mở rộng dung lượng. IC 1 A0 A11 2k IC 2 A0 A11 2k IC 3 A0 A11 2k IC 4 A0 A11 2k 1 0 1 0 A12 300016 - 3FFF16IC IV_CS41 IC III IC II IC I IC mở 200016 - 2FFF16 100016 - 1FFF16 000016 - 0FFF16 Khoảng địa chỉ _CS31 _CS20 _CS10 _CSA13 Bài giảng Điện tử sốV1.0 176 Câu hỏi Bài giảng Điện tử sốV1.0 177 Tài liệu tham khảo Giáo trình Kỹ thuật số - Trần Văn Minh, NXB Bưu điện 2002. Cơ sở kỹ thuật điện tử số, Đại học Thanh Hoa, Bắc Kinh, NXB Giáo dục 1996. Kỹ thuật số, Nguyễn Thúy Vân, NXB Khoa học và kỹ thuật 1994. Lý thuyết mạch logic và Kỹ thuật số, Nguyễn Xuân Quỳnh, NXB Bưu điện 1984. Fundamentals of logic design, fourth edition, Charles H. Roth, Prentice Hall 1991. Digital engineering design, Richard F.Tinder, Prentice Hall 1991. Digital design principles and practices, John F.Wakerly, Prentice Hall 1990. VHDL for Programmable Logic by Kevin Skahill, Addison Wesley, 1996 The Designer's Guide to VHDL by Peter Ashenden, Morgan Kaufmann, 1996. Analysis and Design of Digital Systems with VHDL by Dewey A., PWS Publishing, 1993. Bài giảng Điện tử sốV1.0 178 Phụ lục

File đính kèm:

bai_giang_dien_tu_so_chuong_7_bo_nho_ban_dan_nguyen_trung_hi.pdf

bai_giang_dien_tu_so_chuong_7_bo_nho_ban_dan_nguyen_trung_hi.pdf