Bài giảng Điện tử số - Chương 4: Mạch logic tổ hợp - Nguyễn Trung Hiếu

Khái niệm chung

Đặc điểm cơ bản của mạch tổ hợp

Trong mạch số, mạch tổ hợp là mạch mà trị số ổn định của tín hiệu đầu ra

ở thời điểm đang xét chỉ phụ thuộc vào tổ hợp các giá trị tín hiệu đầu vào.

Đặc điểm cấu trúc mạch tổ hợp là được cấu trúc nên từ các cổng logic.

Vậy các mạch điện cổng ở chương 2 và các mạch logic ở chương 3 đều là

các mạch tổ hợp.

Phương pháp biểu diễn chức năng logic

Các phương pháp thường dùng để biểu diễn chức năng logic của mạch tổ

hợp là hàm số logic, bảng trạng thái, bảng Cac nô (Karnaugh), cũng có

khi biểu thị bằng đồ thị thời gian dạng xung.

Đối với vi mạch cỡ nhỏ (SSI) thường biểu diễn bằng hàm logic. Đối với

vi mạch cỡ vừa (MSI) thường biểu diễn bằng bảng trạng thái.

Phương pháp biểu diễn chức năng logic (tiếp)

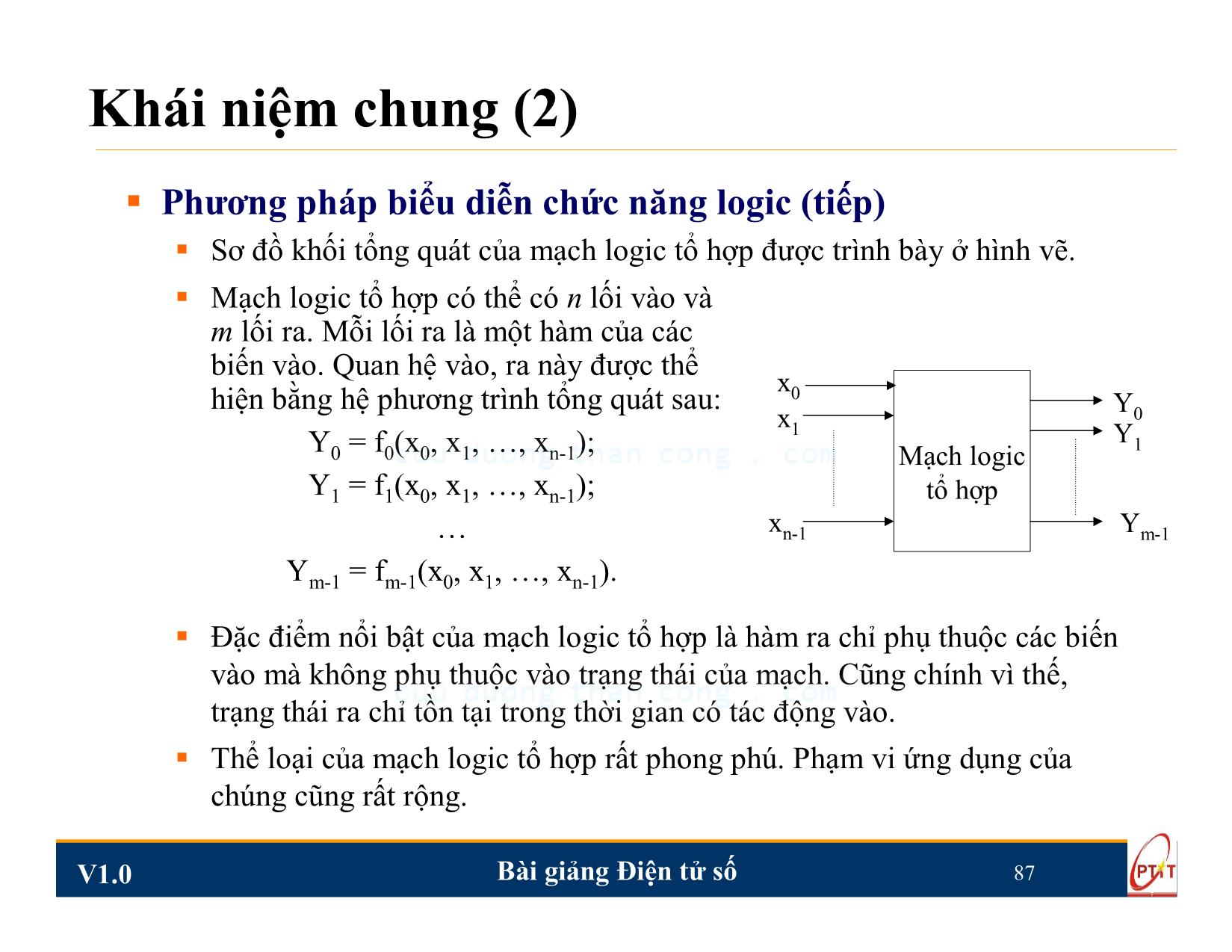

Sơ đồ khối tổng quát của mạch logic tổ hợp được trình bày ở hình vẽ.

Mạch logic

tổ hợp

Đặc điểm nổi bật của mạch logic tổ hợp là hàm ra chỉ phụ thuộc các biến

vào mà không phụ thuộc vào trạng thái của mạch. Cũng chính vì thế,

trạng thái ra chỉ tồn tại trong thời gian có tác động vào.

Thể loại của mạch logic tổ hợp rất phong phú. Phạm vi ứng dụng của

chúng cũng rất rộng.

Mạch logic tổ hợp có thể có n lối vào và

m lối ra. Mỗi lối ra là một hàm của các

biến vào. Quan hệ vào, ra này được thể

Trang 1

Trang 2

Trang 3

Trang 4

Trang 5

Trang 6

Trang 7

Trang 8

Trang 9

Trang 10

Tải về để xem bản đầy đủ

Tóm tắt nội dung tài liệu: Bài giảng Điện tử số - Chương 4: Mạch logic tổ hợp - Nguyễn Trung Hiếu

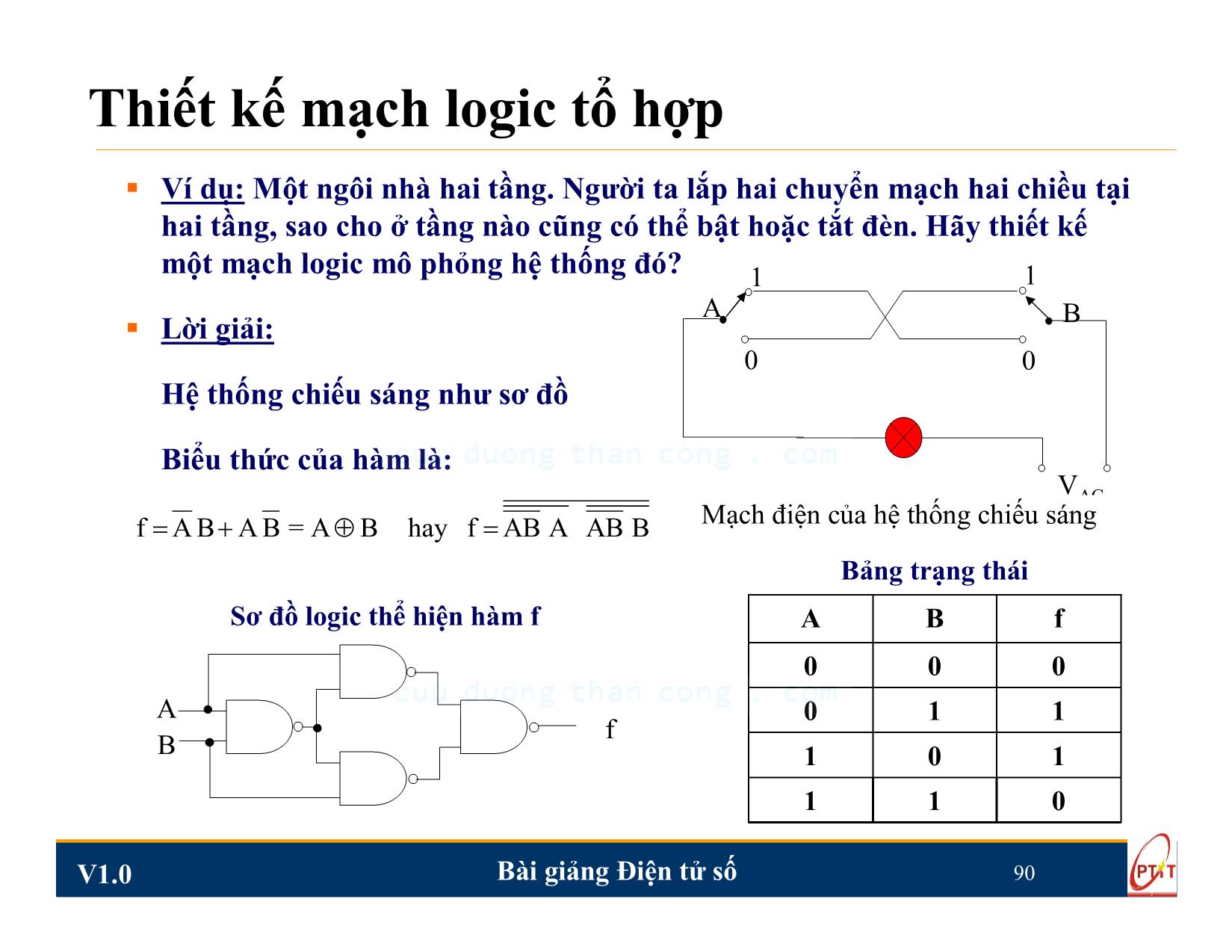

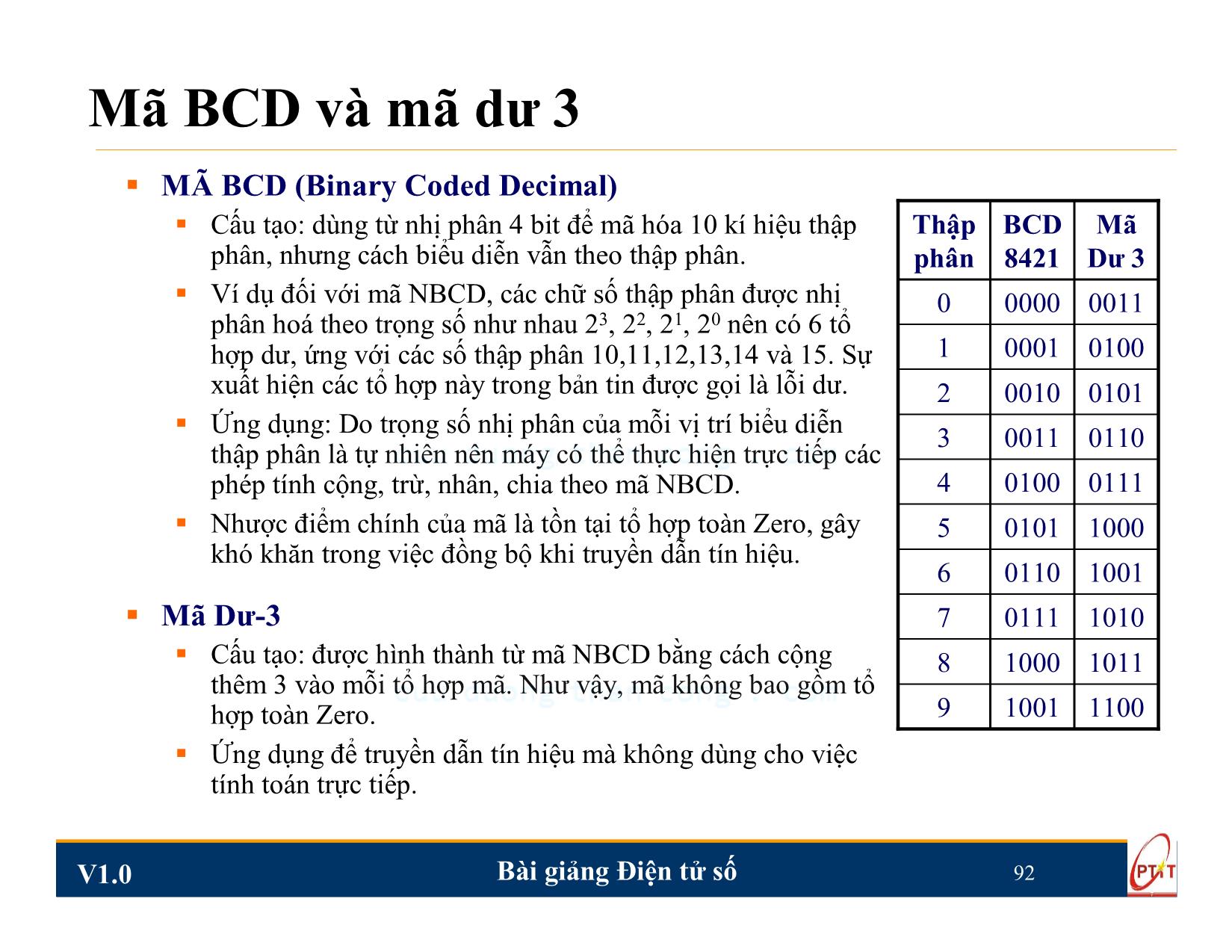

2, 21, 20 nên có 6 tổ hợp dư, ứng với các số thập phân 10,11,12,13,14 và 15. Sự xuất hiện các tổ hợp này trong bản tin được gọi là lỗi dư. Ứng dụng: Do trọng số nhị phân của mỗi vị trí biểu diễn thập phân là tự nhiên nên máy có thể thực hiện trực tiếp các phép tính cộng, trừ, nhân, chia theo mã NBCD. Nhược điểm chính của mã là tồn tại tổ hợp toàn Zero, gây khó khăn trong việc đồng bộ khi truyền dẫn tín hiệu. Mã Dư-3 Cấu tạo: được hình thành từ mã NBCD bằng cách cộng thêm 3 vào mỗi tổ hợp mã. Như vậy, mã không bao gồm tổ hợp toàn Zero. Ứng dụng để truyền dẫn tín hiệu mà không dùng cho việc tính toán trực tiếp. 011101004 100001015 100101106 101001117 101110008 110010019 011000113 010100102 010000011 001100000 Mã Dư 3 BCD 8421 Thập phân Bài giảng Điện tử sốV1.0 93 Mã Gray Mã Gray còn được gọi là mã cách 1, là loại mã mà các tổ hợp mã kế nhau chỉ khác nhau duy nhất 1 bit. Loại mã này không có tính trọng số. Do đó, giá trị thập phân đã được mã hóa chỉ được giải mã thông qua bảng mã mà không thể tính theo tổng trọng số như đối với mã BCD. Mã Gray có thể được tổ chức theo nhiều bit. Bởi vậy, có thể đếm theo mã Gray. Cũng tương tự như mã BCD, ngoài mã Gray chính còn có mã Gray dư-3. 0011100015 0001100114 0000101113 1000101012 1001111011 1011111110 010001104 110001115 110101016 111101007 111011008 101011019 010100103 011100112 011000011 001000000 Gray Dư 3GrayThập phân Bài giảng Điện tử sốV1.0 94 Mã chẵn, lẻ BCD 8421 lẻ PL BCD 8421chẵn PC BCD 8421 1001 1000 0111 0110 0101 0100 0011 0010 0001 0000 0 1 1 0 0 1 0 1 1 0 1001 1000 0111 0110 0101 0100 0011 0010 0001 0000 00100 10101 10110 00111 01000 11001 10011 00010 00001 10000 Mã chẵn và mã lẻ là hai loại mã có khả năng phát hiện lỗi hay dùng nhất. Để thiết lập loại mã này ta chỉ cần thêm một bit chẵn/ lẻ (bit parity) vào tổ hợp mã đã cho, nếu tổng số bit 1 trong từ mã (bit tin tức + bit chẵn/lẻ) là chẵn thì ta được mã chẵn và ngược lại ta được mã lẻ. Bài giảng Điện tử sốV1.0 95 Mạch mã hoá từ thập phân sang BCD 8421 Sơ đồ khối tổng quát của mạch mã hoá Gồm 9 lối vào (biến) ứng Với các chữ số thập phân từ 1 đến 9. Lối vào zero là không cần thiết, vì khi tất cả các lối vào khác bằng 0 thì lối ra cũng bằng 0. Bốn lối ra A, B, C, D (hàm) thể hiện tổ hợp mã tương ứng với mỗi chữ số thập phân trên lối vào theo trọng số 8421. 1 0 0 19 1 0 0 08 0 1 1 17 0 1 1 06 0 1 0 15 0 1 0 04 Bảng trạng thái 0 0 1 13 0 0 1 02 0 0 0 11 Ra BCD 8 4 2 1 Vào thập phân Sơ đồ khối của mạch mã hóa Vào Thập phân Ra BCD 8421 1 2 3 4 Mạch 5 mã hoá 6 7 8 9 A 8 B 4 C 2 D 1 Từ bảng trạng thái ta viết được các hàm ra: A = 8 +9 = (8,9) B = 4 + 5 + 6 + 7 = ( 4,5,6,7) C = 2 + 3 + 6 + 7 = (2,3,6,7) D = 1 + 3 + 5 + 7 + 9 = (1,3,5,7,9) Bài giảng Điện tử sốV1.0 96 Mạch mã hoá từ thập phân sang BCD 8421 Căn cứ hệ phương trình, ta xây dựng được mạch điện của bộ mã hoá. Hoặc dùng ma trận diode (cổng OR) để xây dựng Hoặc có thể được viết lại như sau (dùng định lý DeMorgan) và dùng ma trận diode (cổng AND) để xây dựng mạch: 9.7.5.3.197531D 7.6.3.27632C 7.6.5.47654B 9.898A R4 R3 R2 R1 +5V 9 8 7 6 5 4 3 2 1 DCBA Mạch điện của bộ mã hoá dùng diode Bài giảng Điện tử sốV1.0 97 Mạch mã hóa ưu tiên Trong bộ mã hoá vừa xét trên, tín hiệu vào tồn tại độc lập, (không có trường hợp có 2 tổ hợp trở lên đồng thời tác động). Để giải quyết trường hợp có nhiều đầu vào tác động đồng thời ta có Bộ mã hoá ưu tiên. Trong các trường hợp này thì bộ mã hoá ưu tiên chỉ tiến hành mã hoá tín hiệu vào nào có cấp ưu tiên cao nhất ở thời điểm xét. Việc xác định cấp ưu tiên cho mỗi tín hiệu vào là do người thiết kế mạch. Xét nguyên tắc hoạt động và quá trình thiết kế của bộ mã hoá ưu tiên 9 lối vào, 4 lối ra. Bài giảng Điện tử sốV1.0 98 Mạch mã hóa ưu tiên (tiếp) D = 1.2.4.6.8 + 3.4.6.8 + 5.6.8 + 7.8 + 9 10011XXXXXXXX 000101XXXXXXX 1110001XXXXXX 01100001XXXXX 101000001XXXX 0010000001XXX 11000000001XX 010000000001X 1000000000001 0000000000000 1248987654321 Ra BCDVào thập phân D sẽ lấy logic 1 ứng với đầu vào là 1, 3, 5, 7, 9. Tuy nhiên, lối vào 1 chỉ hiệu lực khi tất cả các lối vào cao hơn đều bằng 0; lối vào 3 chỉ có hiệu lực khi 4, 6, 8 đều bằng 0 và tương tự đối với 5, 7, 9, nghĩa là: Lý luận tương tự ta có: 9=“1” 8 bằng “0”7=“1” và 6,8 bằng “0”5=“1” vàD=“1” nếu 4,6,8 bằng “0”3=“1” và 2,4,6,8 bằng “0”1=“1” và C = 2.4.5.8.9 + 3.4.5.8.9 + 6.8.9 + 7.8.9 B = 4.8.9 + 5.8.9 + 6.8.9 + 7.8.9 A = 8 + 9 Bài giảng Điện tử sốV1.0 99 Mạch giải mã 7 đoạn Dụng cụ 7 đoạn Để hiển thị chữ số của một hệ đếm phân bất kỳ, ta có thể dùng dụng cụ 7 đoạn. Cấu tạo của nó như chỉ ở hình 4-15. Các đoạn được hình thành bằng nhiều loại vật liệu khác nhau, nhưng phải có khả năng hiển thị được trong các điều kiện ánh sáng khác nhau và tốc độ chuyển mạch phải đủ lớn. Trong kĩ thuật số, các đoạn thường được dùng là LED hoặc tinh thể lỏng (LCD). Đối với LED, mỗi đoạn là một Diode phát quang và khi có dòng điện đi qua đủ lớn (5 đến 30 mA) thì đoạn tương ứng sẽ sáng. Ngoài 7 đoạn sáng chính, mỗi LED cũng có thêm Diode để hiển thị dấu phân số khi cần thiết. LED có hai loại chính: LED Anôt chung và Ktốt chung. Do đó, logic của tín hiệu điều khiển hai loại này là ngược nhau. a b c d e f g Cấu tạo dụng cụ 7 đoạn sáng Bài giảng Điện tử sốV1.0 100 Mạch giải mã 7 đoạn Mạch giải mã 7 đoạn Nhiệm vụ của ta là phải thiết kế một mạch logic liên hợp với 4 lối vào và 7 lối ra để chuyển mã NBCD thành mã 7 đoạn. Sơ đồ khối tổng quát của bộ giải mã như hình b). Từ hình a) dễ nhận thấy rằng, đoạn a sẽ sáng khi hiển thị chữ số : 0 hoặc 2, hoặc 3, hoặc 5, hoặc 7, hoặc 8, hoặc 9. Do đó, ta có thể viết: a = (0,2,3,5,6,7,8,9). Tương tự, ta có: b = (0,1,2,3,4,7,8,9), c = (0,1,3,4,5,6,7,8,9), d = (0,2,3,5,6,8,9), e = (0,2,6,8), f = (0,4,5,6,8,9), g = (2,3,4,5,6,8,9). IC 7447, 74247 (Anốt chung), 7448 (K chung ), 4511 (CMOS) là các IC giải mã từ NBCD sang thập phân theo phương pháp hiển thị 7 đoạn. Mạch giải mã 7 đoạn a b c d e f g D C B A 1 2 4 8 b) Sơ đồ khối của mạch giải mã 7 đoạn sáng a b c d e f g a) Cấu tạo dụng cụ 7 đoạn sáng Bài giảng Điện tử sốV1.0 101 Mạch giải mã nhị phân Bộ giải mã nhị phân còn có tên là bộ giải mã "1 từ n", bộ giải mã địa chỉ hoặc bộ chọn địa chỉ nhị phân. Chức năng của nó là lựa chọn duy nhất một lối ra (lấy giá trị 1 hoặc 0), khi tác động tới đầu vào một số nhị phân. Như vậy, nếu số nhị phân là n bit (n lối vào) sẽ nhận diện được 2n địa chỉ khác nhau (trên 2n lối ra). Nói khác đi, mạch chọn địa chỉ nhị phân là một mạch logic tổ hợp có n lối vào và 2n lối ra, nếu tác động tới đầu vào một số nhị phân thì chỉ duy nhất một lối ra được lựa chọn, lấy giá trị 1 (tích cực cao) hoặc 0 (tích cực thấp), các lối ra còn lại đều không được lựa chọn, lấy giá trị 0 hoặc 1. Bộ giải mã nhị phân A0 A1 D0 D1 D2n- 1 An-1 Sơ đồ khối của bộ giải mã nhị phân Bài giảng Điện tử sốV1.0 102 Bộ hợp kênh và phân kênh Bộ hợp kênh (MUX-Multiplexer) Định nghĩa: Bộ hợp kênh là mạch có 2n lối vào dữ liệu, n lối vào điều khiển, 1 lối vào chọn mạch và 1 lối ra. Tuỳ theo giá trị của n lối vào điều khiển mà lối ra sẽ bằng một trong những giá trị ở lối vào (Xj). Nếu giá trị thập phân của n lối vào điều khiển bằng j thì Y = Xj. Bộ phân kênh (DEMUX-DeMultiplexer) Định nghĩa: Bộ phân kênh là mạch có 1 lối vào dữ liệu, n lối vào điều khiển, 1 lối vào chọn mạch và 2n lối ra. Tuỳ theo giá trị của n lối vào điều khiển mà lối ra thứ i (Yi) sẽ bằng giá trị của lối vào. Cụ thể nếu gọi n lối vào điều khiển là An-1An-2A0 thì Yi = X khi (An-1An-2A0)2 = (i)10. Bài giảng Điện tử sốV1.0 103 Bộ hợp kênh (MUX-Multiplexer) Phương trình tín hiệu ra của MUX 2n 1: Thực chất, MUX là chuyển mạch điện tử dùng các tín hiệu điều khiển (An-1An-2A0) để điều khiển sự nối mạch của lối ra với 1 trong số 2n lối vào. MUX được dùng như 1 phần tử vạn năng để xây dựng những mạch tổ hợp khác. IC 74151 là bộ MUX 8 lối vào dữ liệu - 1 lối ra. MUX 2n 1 En X0 X1 Xj X2n-1 Y- Lối ra An-1 An-2 A0 n lối vào điều khiển (a) Sơ đồ khối X0 X1 Xj X2n-1 Y (b). MUX là một chuyển mạch điện tử Bộ hợp kênh MUX 2n 1 74151 Vào điều khiển Vào dữ liệu Vào cho phép A0 A1 A2 1 2 E E n0 n 1 n 2 i 0 1 n 1 n 2 i 0 n 1 n 2 i 1 02 1Y X (A A ...A ...A ) X (A A ...A ...A ) ... X (A A ...A ...A A ) Bài giảng Điện tử sốV1.0 104 Bộ phân kênh (DEMUX-DeMultiplexer) Phương trình tín hiệu ra của DEMUX 1 2n : Bộ phân kênh còn được gọi là bộ giải mã 1 trong 2n. Tại một thời điểm chỉ có 1 trong số 2n lối ra ở mức tích cực. IC 74138 là bộ DEMUX 1 lối vào dữ liệu - 8 lối ra. MUX 2n 1 En Lối vào An-1 An-2 A0 n lối vào điều khiển (a) Sơ đồ khối X (b). DEMUX là một chuyển mạch điện tử Hình 4-19. Bộ phân kênh DEMUX 1 2n Y0 Y1 Yj Y2n-1 Y0 Y1 Yj Y2n-1 Lối vào XChọn mạch n n 1 n 2 i 00 n 1 n 2 i 11 0 n 1 n 2 i 02 1 Y X.A A ...A ...A Y X.A A ...A ...A A .............. Y X.A .A ...A ...A 74138 Vào điều khiển Vào dữ liệu Vào cho phép A0 A1 A2 Bài giảng Điện tử sốV1.0 105 Mạch cộng: Mạch toàn tổng Định nghĩa: Mạch logic thực hiện phép cộng hai số nhị phân 1 bit có lối nhớ đầu vào được gọi là mạch toàn tổng. Theo sơ đồ khối tổng quát của mạch toàn tổng và nguyên lý cộng hai số nhị phân một bit có trọng số bất kỳ, ta có thể lập bảng trạng thái và các hàm ra Si, Ci. Bảng trạng thái 1 0 1 0 1 0 1 0 bi 1 0 0 1 0 1 1 0 Si 001 101 111 111 110 010 000 000 CiaiCi-1 Ci bi ai Si Ci-1 Gi Pi a) Mạch điện TT Si Ci-1 Pi Ci Gi ai bi b) Ký hiệu 1 1 1 1 1 i i i i i i i i i i i i i i i i i i i i S a b C C a bC a b C a b C C a b a b C Bài giảng Điện tử sốV1.0 106 Mạch cộng: Mạch cộng nhị phân song song Ta có thể ghép nhiều bộ cộng hai số nhị một bit lại với nhau để thực hiện phép cộng hai số nhị phân nhiều bit. Sơ đồ khối của bộ cộng được trình bày ở dưới, được gọi là bộ cộng song song Để giảm bớt mức độ phức tạp của mạch, trong thực tế người ta thường sản xuất bộ tổng 4 bit. Muồn cộng nhiều bit, có thể hợp nối tiếp một vài bộ tổng một bit theo phương pháp nêu trên. Một trong những bộ cộng thông dụng hiện nay là 7483. IC này được sản xuất theo hai loại: 7483 và 7483A với logic vào, ra khác nhau. S0 CV0 a0b0 CR0 Bộ toàn tổng S1 CV1 a1b1 CR1 Bộ toàn tổng S2 CV2 a2b2 CR2 Bộ toàn tổng Si CVi aibi CRi Bộ toàn tổng Hình 4-22 Sơ đồ khối của bộ cộng nhị phân song song Bài giảng Điện tử sốV1.0 107 Mạch so sánh Trong các hệ thống số, đặc biệt là trong máy tính, thường thực hiện việc so sánh hai số. Hai số cần so sánh có thể là các số nhị phân, có thể là các ký tự đã mã hoá nhị phân. Mạch so sánh có thể hoạt động theo kiểu nối tiếp hoặc theo kiểu song song. Trong phần này ta sẽ nghiên cứu bộ so sánh theo kiểu song song. Bộ so sánh bằng nhau Bộ so sánh bằng nhau 1 bit Bộ so sánh bằng nhau 4 bit Bộ so sánh Bộ so sánh 1 bit Bộ so sánh 4 bit (So sánh lớn hơn) Bài giảng Điện tử sốV1.0 108 Bộ so sánh bằng nhau Bộ so sánh bằng nhau 1 bit Xét 2 bit ai và bi, gọi gi là kết quả so sánh. Ta có: Bộ so sánh bằng nhau 4 bit So sánh hai số nhị phân 4 bit A = a3a2a1a0 với B = b3b2b1b0. Có A = B a3 = b3, a2 = b2, a1 = b1, a0 = b0. Biểu thức đầu ra tương ứng là: G = g3g2g1g0 với: ib ia ig . .i i i i i i ig a b a b a b 111 Bảng trạng thái của bộ so sánh bằng 1 bit 001 010 100 gibiai 3 3 3 2 2 2 1 1 1 0 0 0, , ,g a b g a b g a b g a b Bài giảng Điện tử sốV1.0 109 Bộ so sánh 1 bit Biểu thức đầu ra: Bảng trạng thái của mạch so sánh 0 0 1 0 f< 1 0 0 1 f= 011 101 010 000 f>biai ai bi f< f= f> Mạch điện của bộ so sánh 1 bit ii ii ii b.af baf b.af Bài giảng Điện tử sốV1.0 110 Bộ so sánh 4 bit (So sánh lớn hơn) So sánh hai số nhị phân 4 bit A = a3a2a1a0 với B = b3b2b1b0. Có A > B khi: hoặc a3 > b3, hoặc a3 = b3, và a2 > b2, hoặc a3 = b3, và a2 = b2, và a1 = b1, hoặc a3 = b3, và a2 = b2, và a1 = b1, và a0 = b0. Từ đó ta có biểu thức hàm ra là: 3 3 3 3 2 2 3 3 2 2 1 1 3 3 2 2 1 1 0 0 . . . . . . . . . . f a b a b a b a b a b a b a b a b a b a b a0 b0 a1 b1 a2 b2 a3 b3 f> Mạch điện của bộ so sánh lớn hơn 4 bit Bài giảng Điện tử sốV1.0 111 Mạch tạo và kiểm tra chẵn lẻ Có nhiều phương pháp mã hoá dữ liệu để phát hiện lỗi và sửa lỗi khi truyền dữ liệu từ nơi này sang nơi khác. Phương pháp đơn giản nhất là thêm một bit vào dữ liệu được truyền đi sao cho số chữ số 1 trong dữ liệu luôn là chẵn hoặc lẻ. Bit thêm vào đó được gọi là bit chẵn/lẻ. Để thực hiện được việc truyền dữ liệu theo kiểu đưa thêm bit chẵn, lẻ vào dữ liệu chúng ta phải: Xây dựng sơ đồ tạo được bit chẵn, lẻ để thêm vào n bit dữ liệu. Xây dựng sơ đồ kiểm tra hệ xem đó là hệ chẵn hay lẻ với (n + 1) bit ở đầu vào (n bit dữ liệu, 1 bit chẵn/lẻ). Bài giảng Điện tử sốV1.0 112 Mạch tạo bit chẵn/lẻ Xét trường hợp 3 bit dữ liệu d1, d2, d3 Gọi Xe, X0 là 2 bit chẵn, lẻ thêm vào dữ liệu. Từ bảng trạng thái ta thấy Và biểu thức của X0 và Xe là Tạo bit chẵn/lẻn bit dữ liệu Xo Xe Sơ đồ khối tổng quát của mạch tạo bit chẵn/lẻ o e e oX X hay X X e 1 2 3 o e 1 2 3 X d d d X X d d d RaVào Bảng trạng thái của mạch tạo bit chẵn lẻ 1 0 1 0 1 0 1 0 d3 1 0 0 1 0 1 1 0 Xe 001 101 111 011 110 010 000 100 Xod2d1 Bài giảng Điện tử sốV1.0 113 Mạch kiểm tra chẵn/lẻ Từ bảng trạng thái của mạch kiểm tra tính chẵn/lẻ ta thấy: Fe = 1 nếu hệ là chẵn (Fe chỉ ra tính chẵn của hệ). Fo = 1 nếu hệ là lẻ (Fo chỉ ra tính lẻ của hệ). Hai hàm kiểm tra chẵn/lẻ luôn là phủ định của nhau. Mặt khác do tính chất của hàm cộng XOR, ta có: Fo = d1 d2 d3 X Fe = Fo 101111 010111 011011 100011 011101 100101 101001 010001 0 0 0 0 0 0 0 0 d1 RaVào 1 0 1 0 1 0 1 0 X 1 0 0 1 0 1 1 0 Fo 001 101 111 011 110 010 000 100 Fed3d2 Kiểm tra hệ chẵn/lẻn bit dữ liệu Bit chẵn lẻ (Xo, Xe) Fo Fe Sơ đồ khối của mạch kiểm tra chẵn/lẻ Bài giảng Điện tử sốV1.0 114 Đơn vị số học và logic (ALU) Đơn vị số học và logic (Arithmetic – Logic Unit) là một thành phần cơ bản không thể thiếu được trong các máy tính. Nó bao gồm 2 khối chính là khối logic và khối số học và một khối ghép kênh. Khối logic: Thực hiện các phép tính logic như là AND, OR, NOT, XOR. Khối số học: Thực hiện các phép tính số học như là: cộng, trừ, tăng 1, giảm 1. ALU Thanh ghi A Thanh ghi B 4 4 4 4 4 Ghi trạng thái 4 Cin M (Mode) F0 F1 Chọn chức năng (Phép tính) Sơ đồ khối của ALU 4 bit Bài giảng Điện tử sốV1.0 115 Câu hỏi

File đính kèm:

bai_giang_dien_tu_so_chuong_4_mach_logic_to_hop_nguyen_trung.pdf

bai_giang_dien_tu_so_chuong_4_mach_logic_to_hop_nguyen_trung.pdf